Ordering number : EN7257B

# LB11872H

## Monolithic Digital IC For Polygonal Mirror Motors Three-Phase Brushless Motor Driver

http://onsemi.com

#### Overview

The LB11872H is a three-phase brushless motor driver developed for driving the motors used for the polygonal mirror in laser printers and similar applications. It can implement, with a single IC chip, all the circuits required for polygonal mirror drive, including speed control and driver functions. The LB11872H can implement motor drive within minimal drive noise due to its use of current linear drive.

#### **Features**

- Three-phase bipolar current linear drive + midpoint control circuit.

- PLL speed control circuit.

- Speed is controlled by an external clock signal.

- Supports Hall FG operation.

- Built-in output saturation prevention circuit.

- Phase lock detection output (with masking function).

- Includes current limiter, thermal protection, rotor constraint protection, and low-voltage protection circuits on chip.

- On-chip output diodes.

## **Specifications**

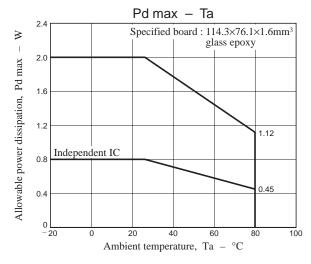

### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol              | Conditions                | Ratings     | Unit |

|-----------------------------|---------------------|---------------------------|-------------|------|

| Supply voltage              | V <sub>CC</sub> max |                           | 30          | V    |

| Output current              | I <sub>O</sub> max  | T ≤ 500ms                 | 1.2         | А    |

| Allowable power dissipation | Pd max1             | Independent IC            | 0.8         | W    |

|                             | Pd max2             | *With specified substrate | 2.0         | W    |

| Operating temperature       | Topr                |                           | -20 to +80  | °C   |

| Storage temperature         | Tstg                |                           | -55 to +150 | °C   |

<sup>\*</sup> When mounted on the specified printed circuit board : 114.3mm × 76.1mm × 1.6mm, glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## Allowable Operating Conditions at Ta = 25°C

| Parameter                              | Symbol | Conditions | Ratings  | Unit |

|----------------------------------------|--------|------------|----------|------|

| Supply voltage range                   | VCC    |            | 10 to 28 | V    |

| 6.3 V regulator-voltage output current | IREG   |            | 0 to -20 | mA   |

| LD pin applied voltage                 | VLD    |            | 0 to 28  | V    |

| LD pin output current                  | ILD    |            | 0 to 15  | mA   |

| FGS pin applied voltage                | VFG    |            | 0 to 28  | V    |

| FGS pin output current                 | IFG    |            | 0 to 10  | mA   |

## **Electrical Characteristics** at $Ta = 25^{\circ}C$ , $V_{CC} = VM = 24V$

| _                                      | Ratings               |                                              |          |          |                      |       |

|----------------------------------------|-----------------------|----------------------------------------------|----------|----------|----------------------|-------|

| Parameter                              | Symbol                | Conditions                                   | min      | typ max  |                      | Unit  |

| Supply current 1                       | I <sub>CC</sub> 1     | Stop mode                                    |          | 5        | 7                    | mA    |

| Supply current 2                       | I <sub>CC</sub> 2     | Start mode                                   |          | 17       | 22                   | mA    |

| Output saturation voltages VAGC =      | 3.5V                  |                                              |          |          |                      |       |

| SOURCE (1)                             | VSAT1-1               | $I_{O} = 0.5A, RF = 0\Omega$                 |          | 1.7      | 2.2                  | V     |

| SOURCE (2)                             | VSAT1-2               | $I_{O} = 1.0A, RF = 0\Omega$                 |          | 2.0      | 2.7                  | V     |

| SINK (1)                               | VSAT2-1               | $I_{O} = 0.5A, RF = 0\Omega$                 |          | 0.4      | 0.9                  | V     |

| SINK (2)                               | VSAT2-2               | $I_O = 1.0A$ , RF = $0\Omega$                |          | 1.0      | 1.7                  | V     |

| Output leakage current                 | I <sub>O</sub> (LEAK) | V <sub>CC</sub> = 28V                        |          |          | 100                  | μΑ    |

| 6.3V Regulator-voltage output          |                       |                                              |          |          |                      |       |

| Output voltage                         | VREG                  |                                              | 5.90     | 6.25     | 6.60                 | V     |

| Voltage regulation                     | ΔVREG1                | V <sub>CC</sub> = 9.5 to 28V                 |          | 50       | 100                  | mV    |

| Load regulation                        | ΔVREG2                | Iload = -5 to -20mA                          |          | 10       | 60                   | mV    |

| Temperature coefficient                | ΔVREG3                | Design target value*1                        |          | 0        |                      | mV/°C |

| Hall amplifier block                   | •                     |                                              |          |          |                      |       |

| Input bias current                     | IB (HA)               | Differential input : 50mVp-p                 |          | 2        | 10                   | μΑ    |

| Differential input voltage range       | VHIN                  | SIN wave input                               | 50       |          | *600                 | mVp-p |

| Common-phase input voltage range       | VICM                  | Differential input : 50mVp-p                 | 2.0      |          | V <sub>CC</sub> -2.5 | V     |

| Input offset voltage                   | VIOH                  | Design target value*1                        | -20      |          | 20                   | mV    |

| FG amplifier and schmitt block (IN1)   |                       |                                              |          |          |                      |       |

| Input amplifier gain                   | GFG                   |                                              |          | 5        |                      | Times |

| Input hysteresis (high to low)         | VSHL                  |                                              |          | 0        |                      | mV    |

| Input hysteresis (low to high)         | VSLH                  |                                              |          | -10      |                      | mV    |

| Hysteresis width                       | VFGL                  | Input conversion                             | 4        | 7        | 12                   | mV    |

| Low-voltage protection circuit         |                       |                                              |          |          |                      |       |

| Operating voltage                      | VSD                   |                                              | 8.4      | 8.8      | 9.2                  | V     |

| Hysteresis width                       | ΔVSD                  |                                              | 0.2      | 0.4      | 0.6                  | V     |

| Thermal protection circuit             |                       |                                              |          |          |                      |       |

| Thermal shutdown operating temperature | TSD                   | Design target value*1 (junction temperature) | 150      | 180      |                      | °C    |

| Hysteresis width                       | ΔTSD                  | Design target value*1 (junction temperature) |          | 40       |                      | °C    |

| Current limiter operation              |                       |                                              |          |          |                      |       |

| Acceleration limit voltage             | VRF1                  |                                              | 0.53     | 0.59     | 0.65                 | V     |

| Deceleration limit voltage             | VRF2                  |                                              | 0.32     | 0.37     | 0.42                 | V     |

| Error amplifier                        |                       |                                              |          | 1        |                      |       |

| Input offset voltage                   | VIO (ER)              | Design target value*1                        | -10      |          | 10                   | mV    |

| Input bias current                     | IB (ER)               |                                              | -1       |          | 1                    | μΑ    |

| High-level output voltage              | V <sub>OH</sub> (ER)  | I <sub>OH</sub> = -500μA                     | VREG-1.2 | VREG-0.9 |                      | V     |

| Low-level output voltage               | V <sub>OL</sub> (ER)  | I <sub>OL</sub> = 500μA                      |          | 0.9      | 1.2                  | V     |

| DC bias level                          | VB (ER)               |                                              | -5%      | 1/2VREG  | 5%                   | V     |

Note\*: Since kickback can occur in the output waveform if the Hall input amplitude is too large, the Hall input. amplitudes should be held to under 350mVp-p.

Continued on next page.

<sup>\*1 :</sup> This parameter is a design target value and is not measured.

Continued from preceding page.

| Parameter                                     | Symbol                | Conditions                    |          | Ratings  |       | Unit  |

|-----------------------------------------------|-----------------------|-------------------------------|----------|----------|-------|-------|

| Phase comparator authorit                     |                       |                               | min      | typ      | max   |       |

| Phase comparator output                       | VDDU                  | 100                           | VDEC 0.3 | VDEC 0.4 |       | V     |

| High-level output voltage                     | VPDH                  | Ι <sub>ΟΗ</sub> = -100μΑ      | VREG-0.2 | VREG-0.1 | 0.0   |       |

| Low-level output voltage                      | VPDL                  | I <sub>OL</sub> = 100μA       |          | 0.2      | 0.3   | V     |

| Output source current                         | IPD+                  | VPD = VREG/2                  | 4.5      |          | -500  | μA    |

| Output sink current                           | IPD-                  | VPD = VREG/2                  | 1.5      |          |       | mA    |

| Cutout seturation voltage                     | \/LD (\$AT)           | ILD = 10mA                    |          | 0.15     | 0.5   | V     |

| Output saturation voltage                     | VLD (SAT)             | VLD = 28V                     |          | 0.15     | 10    |       |

| Output leakage current                        | ILD (LEAK)            | VLD = 28V                     |          |          | 10    | μΑ    |

| FG output                                     | VEC (CAT)             | IFC FmA                       |          | 0.45     | 0.5   | V     |

| Output saturation voltage                     | VFG (SAT)             | IFG = 5mA                     |          | 0.15     | 0.5   |       |

| Output leakage current                        | IFG (LEAK)            | VFG = 28V                     |          |          | 10    | μΑ    |

| Drive block                                   | \/D7                  | NAVAL 4b a rabasas in landand | 50       | 400      | 200   | \/    |

| Dead zone width                               | VDZ                   | With the phase is locked      | 50       | 100      | 300   | mV    |

| Output idling voltage                         | VID                   | Make the sector to            |          | 0.5      | 6     | mV    |

| Forward gain 1                                | GDF+1                 | With phase locked             | 0.4      | 0.5      | 0.6   | Time  |

| Forward gain 2                                | GDF+2                 | With phase unlocked           | 0.8      | 1.0      | 1.2   | Time  |

| Reverse gain 1                                | GDF-1                 | With phase locked             | -0.6     | -0.5     | -0.4  | Time  |

| Reverse gain 2                                | GDF-2                 | With phase unlocked           | -0.8     | -1.0     | -1.2  | Time  |

| Acceleration command voltage                  | VSTA                  |                               | 5.0      | 5.6      |       | V     |

| Deceleration command voltage                  | VSTO                  |                               |          | 0.8      | 1.5   | V     |

| Forward limiter voltage                       | VL1                   | $Rf = 22\Omega$               | 0.53     | 0.59     | 0.65  | V     |

| Reverse limiter voltage                       | VL2                   | $Rf = 22\Omega$               | 0.32     | 0.37     | 0.42  | V     |

| CSD oscillator circuit                        |                       | 1                             |          | I I      |       |       |

| Oscillation frequency                         | fosc                  | C = 0.022μF                   |          | 31       |       | Hz    |

| High-level pin voltage                        | VCSDH                 |                               | 4.3      | 4.8      | 5.3   | V     |

| Low-level pin voltage                         | VCSDL                 |                               | 0.75     | 1.15     | 1.55  | V     |

| External capacitor charge and                 | ICHG                  |                               | 3        | 5        | 7     | μΑ    |

| discharge current  Lock detection delay count | CSDCT1                |                               |          | 7        |       |       |

| Clock cutoff protection operating             | CSDCT2                |                               |          | 2        |       |       |

| count                                         | 000012                |                               |          |          |       |       |

| Lock protection count                         | CSDCT3                |                               |          | 31       |       |       |

| Initial reset voltage                         | V <sub>RES</sub>      |                               |          | 0.60     | 0.80  | V     |

| Clock input block                             | <b>-</b>              |                               | <b>'</b> |          |       |       |

| External input frequency                      | fCLK                  |                               | 400      |          | 10000 | Hz    |

| High-level input voltage                      | V <sub>IH</sub> (CLK) | Design target value*1         | 2.0      |          | VREG  | V     |

| Low-level input voltage                       | V <sub>IL</sub> (CLK) | Design target value*1         | 0        |          | 1.0   | V     |

| Input open voltage                            | V <sub>IO</sub> (CLK) |                               | 2.7      | 3.0      | 3.3   | V     |

| Hysteresis width                              | V <sub>IS</sub> (CLK) | Design target value*1         | 0.1      | 0.2      | 0.3   | V     |

| High-level input current                      | I <sub>IH</sub> (CLK) | V (CLK) = VREG                |          | 140      | 185   | μΑ    |

| Low-level input current                       | I <sub>IL</sub> (CLK) | V (CLK) = 0V                  | -185     | -140     |       | μA    |

| S/S pin                                       |                       | ı                             | <u> </u> | ı        |       | · · · |

| High-level input voltage                      | V <sub>IH</sub> (S/S) |                               | 2.0      |          | VREG  | V     |

| Low-level input voltage                       | V <sub>IL</sub> (S/S) |                               | 0        |          | 1.0   | V     |

| Input open voltage                            | V <sub>IO</sub> (S/S) |                               | 2.7      | 3.0      | 3.3   | V     |

| Hysteresis width                              | V <sub>IS</sub> (S/S) |                               | 0.1      | 0.2      | 0.3   | V     |

| High-level input current                      | I <sub>IH</sub> (S/S) | V (S/S) = VREG                | 1        | 140      | 185   | μА    |

| Low-level input current                       | I <sub>IL</sub> (S/S) | V (S/S) = 0V                  | -185     | -140     |       | μА    |

<sup>\*1:</sup> This parameter is a design target value and is not measured.

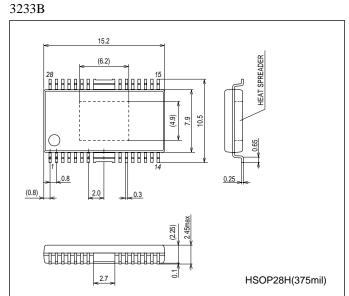

## **Package Dimensions**

unit: mm (typ)

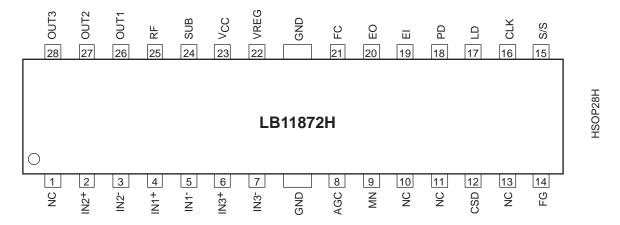

## **Pin Assignment**

Top view

## **Truth Table**

OUT1 to OUT3 (H : Source, L : Sink)

| IN1 | IN2 | IN3 | OUT1 | OUT2 | OUT3 |

|-----|-----|-----|------|------|------|

| Н   | L   | Н   | L    | Н    | М    |

| Н   | L   | L   | L    | М    | Н    |

| Н   | Н   | L   | М    | L    | Н    |

| L   | Н   | L   | Н    | L    | М    |

| L   | Н   | Н   | Н    | М    | L    |

| L   | L   | Н   | М    | Н    | Ĺ    |

For IN1 to IN3, "H" means that IN<sup>+</sup> is greater than IN<sup>-</sup>, and "L" means IN<sup>-</sup> is greater than IN<sup>+</sup>. For OUT1 to OUT3, "H" means the output is a source, and "L" means that it is a sink.

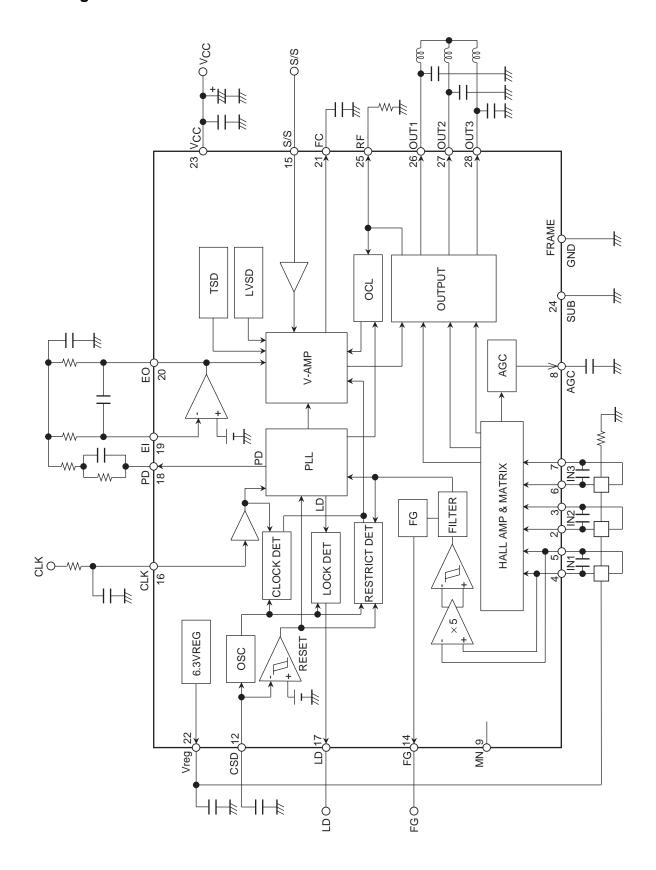

## **Block Diagram**

### Pin Functions

| Pin Fu  | nctions          |                                                     |                                              |

|---------|------------------|-----------------------------------------------------|----------------------------------------------|

| Pin No. | Pin name         | Function                                            | Equivalent circuit                           |

| 2       | IN2+             | Hall effect sensor signal inputs.                   |                                              |

| 3       | IN2              | These inputs are high when IN+ is greater than      | VCC                                          |

| 4       | IN1+             | IN- and low when IN- is greater than IN+.           | <b>\</b>                                     |

| 5       | IN1 <sup>-</sup> | Insert capacitors between the IN+ and IN- pins to   | _ [.   _                                     |

| 6       | IN3+             | reduce noise.                                       | <b>A P</b>   <b>A</b>                        |

| 7       | IN3-             | An amplitude of over 50mVp-p and under              |                                              |

|         |                  | 350mVp-p is desirable for the Hall input signals.   |                                              |

|         |                  | Kickback can occur in the output waveform if the    | $300\Omega$                                  |

|         |                  | Hall input amplitude is over 350mVp-p.              | $(3)(5)(7) \longrightarrow W$ $(2)(4)(6)$    |

|         |                  |                                                     |                                              |

|         |                  |                                                     | <b>↑ ⊻  ▼ ↑</b>                              |

|         |                  |                                                     | <del> </del>                                 |

|         |                  |                                                     | <i>""</i>                                    |

|         |                  |                                                     | $\Psi$                                       |

|         |                  |                                                     | 7//                                          |

|         |                  |                                                     | ///                                          |

| 8       | AGC              | AGC amplifier frequency characteristics             | VREG                                         |

|         |                  | correction.                                         |                                              |

|         |                  | Insert a capacitor (about 0.022μF) between this     | _ <b>K</b>                                   |

|         |                  | pin and ground.                                     |                                              |

|         |                  |                                                     | 300Ω<br>W 8                                  |

|         |                  |                                                     |                                              |

|         |                  |                                                     | <b>*</b>                                     |

|         |                  |                                                     | <b>T</b>                                     |

|         |                  |                                                     | <u>                                     </u> |

|         |                  |                                                     | ///                                          |

| 9       | MN               | Monitor pin.                                        |                                              |

| 40      | CCD              | This pin should be left open in normal operation.   |                                              |

| 12      | CSD              | Used for both initial reset pulse generation and as | VREG                                         |

|         |                  | the reference time for constraint protection        | ŢŢŢ                                          |

|         |                  | circuits.                                           |                                              |

|         |                  | Insert a capacitor between this pin and ground.     |                                              |

|         |                  |                                                     | 2000                                         |

|         |                  |                                                     | $300\Omega$ $12$                             |

|         |                  |                                                     |                                              |

|         |                  |                                                     | '   <b> </b>                                 |

|         |                  |                                                     |                                              |

|         |                  |                                                     |                                              |

|         |                  |                                                     |                                              |

| 14      | FG               | FG pulse output.                                    | VREG_                                        |

|         |                  | This is an open-collector output.                   | VILLO                                        |

|         |                  |                                                     |                                              |

|         |                  |                                                     | 14)                                          |

|         |                  |                                                     |                                              |

|         |                  |                                                     |                                              |

|         |                  |                                                     | $\bot$                                       |

|         |                  |                                                     |                                              |

|         | <u> </u>         |                                                     | <i>\frac{1}{11}</i>                          |

| 15      | S/S              | Start/stop control.                                 | VREG                                         |

|         |                  | Low : Start 0 to 1.0V                               | - VICEO                                      |

|         |                  | High: Stop 2.0V to VREG                             |                                              |

|         |                  | This pin goes to the high level when open.          | ₩ 33kΩ <b>Ş ★</b>                            |

|         |                  |                                                     |                                              |

|         |                  |                                                     | $5k\Omega$                                   |

|         |                  |                                                     | (15)                                         |

|         |                  |                                                     | 2010 > 1                                     |

|         |                  |                                                     | 30kΩ ₹ <b>★</b>                              |

|         |                  |                                                     |                                              |

|         |                  |                                                     |                                              |

|         |                  |                                                     | 111 111 111                                  |

Continued on next page.

## Continued from preceding page.

| Pin No. | from precedir | Function                                                                                                                                                              | Equivalent circuit                                  |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 16      | CLK           | Clock input. Low: 0 to 1.0V High: 2.0V to VREG This pin goes to the high level when open.                                                                             | VREG $33k\Omega$ $5k\Omega$ $30k\Omega$ $30k\Omega$ |

| 17      | LD            | Phase locked state detection output. This output goes to the on state when the PLL locked state is detected. This is an open-collector output.                        | VREG 17                                             |

| 18      | PD            | Phase comparator output (PLL output).  This pin output the phase error as a pulse signal with varying duty. The output current increases as the duty becomes smaller. | VREG 18                                             |

| 19      | EI            | Error amplifier in put pin.                                                                                                                                           | VREG 300Ω 19                                        |

| 20      | EO            | Error amplifier output pin. The output current increases when this output is high.                                                                                    | VREG 20 40kΩ                                        |

Continued on next page.

## Continued from preceding page.

| 21 FC Control amplifier frequency correction. Inserting a capacitor (about 5600pF) between this pin and ground will stop closed loop oscillation in the current control system. The output current response characteristics will be degraded if the capacitor is too large.  22 VREG Stabilized power supply (6.3V) Insert a capacitor (about 0.1µF) between this pin and ground for stabilization.  23 VCC Power supply.  24 SUB SUB pin. Connect this pin to ground.  25 RF Output current detection. Insert low-valued resistors (Rf) between these pins and ground. The output current will be limited to the value set by the equation IouT = VL/Rf.  26 OUT1 Motor drive outputs.  27 OUT2 Motor drive outputs. |                | Equivalent circuit | Function                                                                                                                                                                                                                                       | from precedir<br>Pin name | Pin No.  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|

| Insert a capacitor (about 0.1µF) between this pin and ground for stabilization.  23 V <sub>CC</sub> Power supply.  24 SUB SUB pin.  Connect this pin to ground.  25 RF Output current detection.  Insert low-valued resistors (Rf) between these pins and ground. The output current will be limited to the value set by the equation I <sub>OUT</sub> = V <sub>L</sub> /Rf.  26 OUT1 Motor drive outputs.  27 OILT2 If the output scrillates insert a capacitor (about                                                                                                                                                                                                                                               | —(21)          | VREG 21            | Control amplifier frequency correction.  Inserting a capacitor (about 5600pF) between this pin and ground will stop closed loop oscillation in the current control system. The output current response characteristics will be degraded if the |                           |          |

| 24 SUB SUB pin.  Connect this pin to ground.  25 RF Output current detection. Insert low-valued resistors (Rf) between these pins and ground. The output current will be limited to the value set by the equation IouT = VL/Rf.  26 OUT1 Motor drive outputs.  27 OUT3 If the output persillates insert a conscitor (about                                                                                                                                                                                                                                                                                                                                                                                            |                | 222                | Insert a capacitor (about 0.1µF) between this pin                                                                                                                                                                                              | VREG                      | 22       |

| 24 SUB SUB pin.  Connect this pin to ground.  25 RF Output current detection. Insert low-valued resistors (Rf) between these pins and ground. The output current will be limited to the value set by the equation IouT = VL/Rf.  26 OUT1 Motor drive outputs.  27 OUT3 If the output oscillates insert a conscitor (about                                                                                                                                                                                                                                                                                                                                                                                             |                |                    | Power supply.                                                                                                                                                                                                                                  | VCC                       | 23       |

| 25 RF Output current detection. Insert low-valued resistors (Rf) between these pins and ground. The output current will be limited to the value set by the equation I <sub>OUT</sub> = V <sub>L</sub> /Rf.  26 OUT1 Motor drive outputs.  27 OUT3 If the output oscillates insert a consciter (about                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                    |                                                                                                                                                                                                                                                |                           | 24       |

| 27 OUT2 If the output assillator, insert a capacitor (about                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                    | Output current detection. Insert low-valued resistors (Rf) between these pins and ground. The output current will be limited                                                                                                                   | RF                        | 25       |

| 28 OUT3 0.1μF) between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26 27 28<br>25 | 300Ω               | If the output oscillates, insert a capacitor (about                                                                                                                                                                                            | OUT2                      | 27       |

| 1 NC No connection (NC) pins. 10 These pins may be used for wiring connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                    |                                                                                                                                                                                                                                                | NC                        | 10<br>11 |

| 13   FRAME GND Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 1                  | Ground.                                                                                                                                                                                                                                        | GND                       |          |

### **LB11920 Description**

#### 1. Speed Control Circuit

This IC adopts a PLL speed control technique and provides stable motor operation with high precision and low jitter. This PLL circuit compares the phase error at the edges of the CLK signal (falling edges) and FG signal (rising edges (low to high transitions) on the IN1 input), and the IC uses the detected error to control the motor speed. During this control operation, the FG servo frequency will be the same as the CLK frequency.

$$f_{FG}$$

(servo) =  $f_{CLK}$

#### 2. Output Drive Circuit

To minimize motor noise, this IC adopts three-phase full-wave current linear drive. This IC also adopts a midpoint control technique to prevent ASO destruction of the output transistors.

Reverse torque braking is used during motor deceleration during speed switching and lock pull-in. In stop mode, the drive is cut and the motor is left in the free-running state.

Since the output block may oscillate depending on the motor actually used, capacitors (about  $0.1\mu F$ ) must be inserted between the OUT pins and ground.

#### 3. Hall Input Signals

This IC includes an AGC circuit that minimizes the influence on the output of changes in the Hall signal input amplitudes due to the motor used. However, note that if there are discrepancies in the input amplitudes between the individual phases, discrepancies in the output phase switching timing may occur.

An amplitude (differential) of at least 50mVp-p is required in the Hall input signals. However, if the input amplitude exceeds 350mVp-p, the AGC circuit control range will be exceeded and kickback may occur in the output.

If Hall signal input frequencies in excess of 1kHz (the frequency in a single Hall input phase) are used, internal IC heating during startup and certain other times (that is, when the output transistors are saturated) may increase. Reducing the number of magnetic poles can be effective in dealing with problem.

The IN1 Hall signal is used as the FG signal for speed control internally to the IC. Since noise can easily become a problem, a capacitor must be inserted across this input. However, since this could result in differences between the signal amplitudes of the three phases, capacitors must be inserted across all of the three input phases.

Although V<sub>CC</sub> can be used as the Hall element bias power supply, using VREG can reduce the chances of problems occurring during noise testing and at other times. If VREG is used, since there is no longer any need to be concerned with the upper limit of the Hall amplifier common-mode input voltage range, bias setting resistors may be used only on the low side.

#### 4. Power Saving Circuit

This IC goes into a power saving state that reduces the current drain in the stop state. The power saving state is implemented by removing the bias current from most of the circuits in the IC. However, the 6.3V regulator output is provided in the power saving state.

#### 5. Reference Clock

Care must be taken to assure that no chattering or other noise is present on the externally input clock signal. Although the input circuit does have hysteresis, if problems do occur, the noise must be excluded with a capacitor. This IC includes an internal clock cutoff protection circuit. If a signal with a frequency below that given by the formula below is input, the IC will not perform normal control, but rather will operate in intermittent drive mode.

$f(Hz) \approx 0.64 \div C_{CSD}$   $C_{CSD}(\mu F)$ : The capacitor inserted between the CSD pin and ground.

When a capacitor of 0.022µF is used, the frequency will be about 29Hz.

If the IC is set to the start state when the reference clock signal is completely absent, the motor will turn somewhat and then motor drive will be shut off. After the motor stops and the rotor constraint protection time elapses, drive will not be restarted, even if the clock signal is then reapplied. However, drive will restart if the clock signal is reapplied before the rotor constraint protection time elapses.

#### 6. Rotor Constraint Protection Circuit

This IC provides a rotor constraint protection circuit to protect the IC itself and the motor when the motor is constrained physically, i.e. prevented from turning. If the FG signal (edges of one type (rising or falling edges) on the IN1 signal) does not switch within a fixed time, output drive will be turned off. The time constant is determined by the capacitor connected to the CSD pin.

$$<$$

time constant (in seconds)  $> \approx 30.5 \times 1.57 \times C_{CSD}$  ( $\mu F$ )

If a 0.02µF capacitor is used, the protection time will be about 1.05 seconds.

To clear the rotor constraint protection state, the IC must be set to the stopped state or the power must be turned off and reapplied. If there is noise present on the FG signal during the constraint time, the rotor constraint protection circuit may not operate normally.

### 7. Phase Lock Signal

#### (1) Phase lock range

Since this IC does not include a counter or similar functionality in the speed control system, the speed error range in the phase locked state cannot be determined solely by IC characteristics. (This is because the acceleration of the changes in the FG frequency influences the range.) When it is necessary to stipulate this characteristic for the motor, the designer must determine this by measuring the actual motor state. Since speed errors occur easily in states where the FG acceleration is large, it is thought that the speed errors will be the largest during lock pull-in at startup and when unlocked due to switching clock frequencies.

#### (2) Masking function for the phase lock state signal

A stable lock signal can be provided by masking the short-term low-level signals due to hunting during lock pull-in. However, this results in the lock state signal output being delayed by the masking time.

The masking time is determined by the capacitor inserted between the CSD pin and ground.

```

< masking time (seconds) > \approx 6.5 \times 1.57 \times C_{CSD} (\mu F)

```

When a 0.022µF capacitor is used, the masking time will be about 225ms. In cases where complete masking is required, a masking time with fully adequate margin must be used.

#### 8. Initial Reset

To initially reset the logic circuits in start mode, the IC goes to the reset state when the CSD pin voltage goes to zero until it reaches 0.63V. Drive output starts after the reset state is cleared. The reset time can be calculated to a good approximation using the following formula.

$$<$$

reset time (seconds)  $> \approx 0.13 \times C_{CSD}$  ( $\mu F$ )

A reset time of over 100µs is required.

#### 9. Current Limiter Circuit

The current limit value is determined by the resistor Rf inserted between the RF pin and ground.

$$I_{LIM} = V_L/Rf$$

$V_L = 0.59V$  (typical) (during acceleration) and 0.37V (typical) (during deceleration)

### 10. Power Supply Stabilization

An adequately large capacitor must be inserted between the V<sub>CC</sub> pin and ground for power supply stabilization. If diodes are inserted in the power supply lines to prevent destruction of the device if the power supply is connected with reverse polarity, the power supply line levels will be even more easily disrupted, and even larger capacitors must be used.

If high-frequency noise is a problem, a ceramic capacitor of about  $0.1 \mu F$  must also be inserted in parallel.

#### 11. VREG Stabilization

A capacitor of at least  $0.1\mu F$  must be used to stabilize the VREG voltage, which is the control circuit power supply. The capacitor must be connected as close as possible to the pins.

#### 12. Error Amplifier External Component Values

To prevent adverse influence from noise, the error amplifier external components must be located as close to the IC as possible.

#### 13. FRAME Pin and Heat sink Area

The FRAME pin and the heat sink area function as the control circuit ground terminal. It is desirable that this ground line and the Rf resistor ground line be grounded at a single point at the ground for the electrolytic capacitor.

Thermal dissipation can be improved significantly by tightly bonding the metallic surface of the back of the IC package to the PCB with, for example, a solder with good thermal conductivity.

#### 14. CSD Pin

The capacitor connected to the CSD pin influences several operational aspects of this IC, including the rotor constraint protection time and the phase lock signal mask time. The following are possible ways of determining the value of this capacitor.

- (1) If removing chattering from the phase lock state signal is most important : Select a capacitance that can assure an adequate mask time.

- (2) If startup time is more important than chattering:

Select a capacitance such that the rotor constraint protection circuit does not operate at startup time and verify that there are no problems with the clock cutoff protection circuit and initial reset time.

Operation of the rotor constraint protection circuit may hinder the study of motor characteristics in the uncontrolled state. It is possible to only operate the initial reset function and not operate the rotor constraint protection circuit by inserting a resistor (about  $390k\Omega$ ) in parallel with the capacitor between the CSD pin and ground.

#### 15. FC Pin

The capacitor connected to the FC pin is required for current limiter loop phase compensation. If the value is too low, the output will oscillate. If the value is too large, it will be easier for currents in excess of the limit value to flow during the current limit time (time before the circuit operates) in states where the output is saturated. (This is because the control response characteristics become worse.)

#### 16. AGC Pin

A capacitance that allows a certain amount of smoothing of the AGC pin voltage in the motor speed range used must be selected for the capacitor connected to the AGC pin. It is also desirable to use a capacitance that allows the AGC voltage to reach an essentially stabilized voltage before the initial reset is cleared. (If the capacitance is too large, the rate of change of the AGC voltage will become slower.)

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa