www.ti.com

## ADC08B200 / ADC08B200Q 8-Bit, 200 MSPS A/D Converter with Capture Buffer

Check for Samples: ADC08B200

## **FEATURES**

- Single-Ended Input

- Selectable Capture Buffer Size

- PLL for Clock Multiplication

- Reference Ladder Top and Bottom Accessible

- Linear Power Scaling with Sample Rate

- FPGA Training Pattern

- AEC-Q100 Grade 2 Qualified

- Power-Down Feature

### **APPLICATIONS**

- Laser Ranging

- RADAR

- Pulse Capturing

### **KEY SPECIFICATIONS**

(PLL Bypassed)

- Resolution 8 Bits

- Maximum Sampling Frequency 200 MSPS (min)

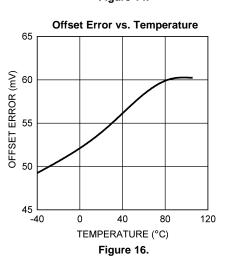

- DNL ±0.4 LSB (typ)

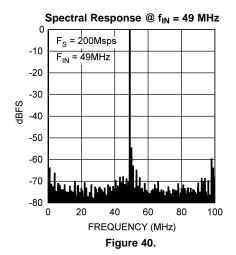

- ENOB (f<sub>IN</sub>= 49 MHz) 7.2 bits (typ)

- THD (f<sub>IN</sub>= 49 MHz) −53 dBc (typ)

- Power Consumption

- Operating (50 MHz) Input 2 mW / Msps (typ)

- Power Down 2.15 mW (typ)

### DESCRIPTION

The ADC08B200 is a high speed analog-to-digital converter (ADC) with an integrated capture buffer. The 8-bit, 200 MSPS A/D core is based upon the proven ADC08200 with integrated track-and-hold and is optimized for low power consumption. This device contains a selectable size capture buffer of up to 1,024 bytes that allows fast capture of an input signal with a slower readout rate. An on-chip clock PLL circuit provides the option of on-chip clock rate multiplication to provide the high speed sampling clock.

The ADC08B200 is resistant to latch-up and the outputs are short-circuit proof. The top and bottom of the ADC08B200's reference ladder are available for connections, enabling a wide range of input possibilities. The digital outputs are TTL/CMOS compatible with a separate output power supply pin to support interfacing with 2.7V to 3.3V logic. The digital inputs and outputs are low voltage TTL/CMOS compatible and the output data format is straight binary.

The ADC08B200Q runs on an Automotive Grade Flow and is AEC-Q100 Grade 2 Qualified.

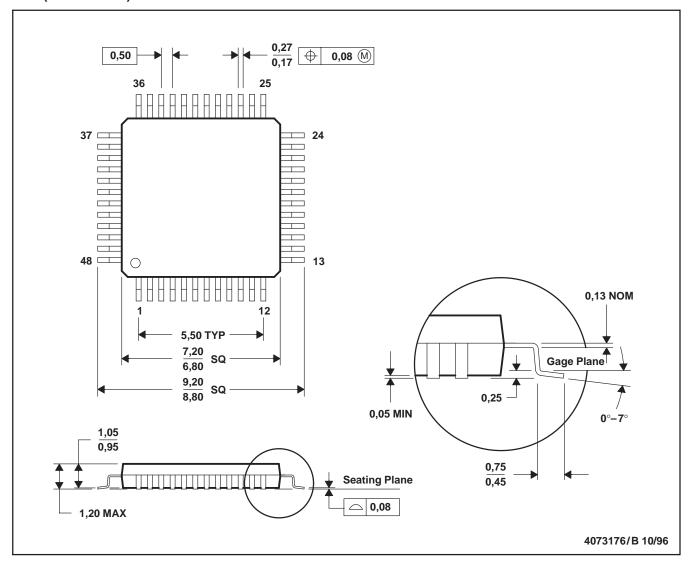

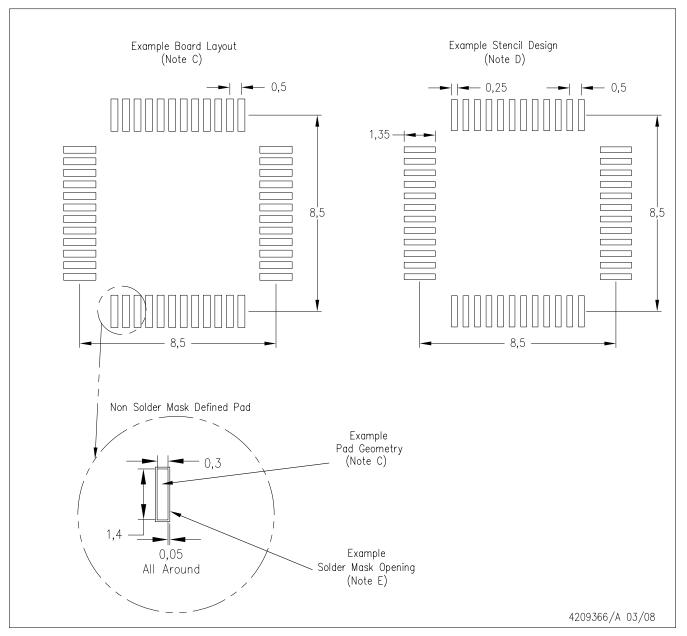

The ADC08B200 is offered in a 48-pin plastic package (TQFP) and is specified over the extended industrial temperature range of -40°C to +105°C. An evaluation board is available to assist in the easy evaluation of the ADC08B200.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

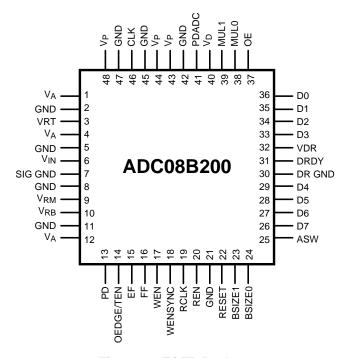

### **PIN CONFIGURATION**

Figure 1. TQFP Package See Package Number PFB0048A

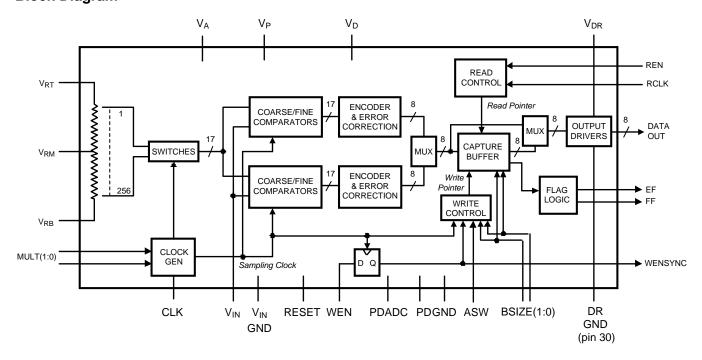

## **Block Diagram**

## **Pin Descriptions and Equivalent Circuits**

| Pin No. | Symbol          | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                             |

|---------|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6       | V <sub>IN</sub> | S GND              | Analog signal input. Conversion range is $V_{RB}$ to $V_{RT}. \label{eq:range}$                                                                                                                                                                                                                                                         |

| 3       | V <sub>RT</sub> | V <sub>A</sub>     | Analog Input that is the high (top) side of the reference ladder of the ADC. Voltage on $V_{RT}$ and $V_{RB}$ inputs define the $V_{IN}$ conversion range. $V_{RT}$ should be more positive than $V_{RB}$ . Bypass well.                                                                                                                |

| 9       | V <sub>RM</sub> | 3 + W + W + + 10   | Analog input that is the mid-point of the reference ladder. This pin should be bypassed to a quiet point in the ground plane with a 0.1 $\mu$ F capacitor. DO NOT LOAD this pin.                                                                                                                                                        |

| 10      | $V_{RB}$        | GND                | Analog Input that is the low side (bottom) of the reference ladder of the ADC. The voltages on $V_{RT}$ and $V_{RB}$ inputs define the $V_{IN}$ conversion range. Bypass well.                                                                                                                                                          |

| 13      | PD              |                    | Chip Power Down input. When this pin is high, the entire chip is in the Power Down mode. Any data in the capture buffer is lost and the output pins hold the last byte that was output.                                                                                                                                                 |

| 41      | PDADC           |                    | ADC Power Down Input. When this pin is high, the ADC is powered down. The capture buffer is active and the data within it may be clocked out.                                                                                                                                                                                           |

| 46      | CLK             | V <sub>D</sub>     | CMOS/TTL compatible digital clock Input. When the PLL is bypassed, the clock signal at this pin is the ADC sampling clock and $V_{\rm IN}$ is sampled on the rising edge of this clock input. When the PLL is enabled, the signal at this input is the reference clock, which is multiplied to provide a higher frequency sample clock. |

| 19      | RCLK            |                    | Buffer Read Clock input. When the capture buffer is enabled, this input signal is used to read the data from the internal buffer. The data output and the buffer empty flag (EF) transition with the rise of this clock.                                                                                                                |

| 17      | WEN             |                    | Write Enable input. A high level at this input causes a byte of data to be written into the capture buffer with the rise of each sample clock.                                                                                                                                                                                          |

| 20      | REN             | GND                | Read Enable input. A high level at this input causes a byte of data to be read from the capture buffer with the rise of each RCLK input. This rise of the REN input should be synchronous with the RCLK input and should not be high while the WEN input is high.                                                                       |

| 22      | RESET           |                    | Device Reset Input. A high level at this input resets all control logic on the chip.                                                                                                                                                                                                                                                    |

| 37      | OE              |                    | Output Enable input. A high level at this input enables the output buffers. A low level at this input puts the digital data output pins into a high impedance state.                                                                                                                                                                    |

Copyright © 2007–2013, Texas Instruments Incorporated

## SNAS388F - MARCH 2007 - REVISED APRIL 2013

| Pin No.                         | Symbol         | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14                              | OEDGE/TEN      | 50k GND            | Output Edge Select or Test Mode Enable input. If this input is high, the data outputs transition with the rising edge of the DRDY output. If this input is low, the data outputs transition with the falling edge of the DRDY output. Forcing a potential of $V_{\text{A}}/2$ at this input enables the Test Mode.                                                                                                        |

| 18                              | WENSYNC        | Vn                 | Synchronized WEN output. The WEN control input is synchronized on-chip with the internal sample clock and is provided at this output.                                                                                                                                                                                                                                                                                     |

| 31                              | DRDY           |                    | Data Ready output. This signal transitions with the transition of the digital data outputs and indicates that the output data is ready.                                                                                                                                                                                                                                                                                   |

| 26 thru 29<br>and<br>33 thru 36 | D0-D7          |                    | Digital data digital Outputs. D0 is the LSB, D7 is the MSB.                                                                                                                                                                                                                                                                                                                                                               |

| 16                              | FF             | GND                | Buffer Full Flag. This output is high when the capture buffer is full.                                                                                                                                                                                                                                                                                                                                                    |

| 15                              | EF             | GND                | Buffer Empty Flag. This output is high when the capture buffer is empty.                                                                                                                                                                                                                                                                                                                                                  |

| 25                              | ASW            | V <sub>D</sub>     | Auto-Stop Write input. This pin has a dual function. With the buffer enabled, this pin acts as the ASW input. When this input is high, writing to the buffer is halted when the capture buffer is full (FF high). When the buffer is disabled, this pin is ignored. When the device is in Test Mode, this pin acts as the Output Edge Select signal, functioning in accordance with the description of the OEDGE/TEN pin. |

| 23,24                           | BSIZE(1:0)     | ★ <b>山</b> 号       | Buffer Size input. These inputs determine the size of the buffer, as described in the Functional Description.                                                                                                                                                                                                                                                                                                             |

| 38, 39                          | MULT(1:0)      | GND                | Clock Multiply Factor input. These inputs determine the internal clock PLL's multiplication factor.                                                                                                                                                                                                                                                                                                                       |

| 1, 4, 12                        | V <sub>A</sub> |                    | Positive analog supply pin. Connect to a voltage source of +3.3V.                                                                                                                                                                                                                                                                                                                                                         |

| 43, 44, 48                      | V <sub>P</sub> |                    | PLL supply pin. Connect to a voltage source of +3.3V.                                                                                                                                                                                                                                                                                                                                                                     |

| 40                              | $V_D$          |                    | Digital core supply pin. Connect to a voltage source of +3.3V.                                                                                                                                                                                                                                                                                                                                                            |

| 32                              | $V_{DR}$       |                    | Power supply for the output drivers. Connect to a voltage source of 2.7V to $V_{\rm D}$ .                                                                                                                                                                                                                                                                                                                                 |

| 2, 5, 8, 11, 21,<br>42, 45, 47  | GND            |                    | The ground return for the chip core.                                                                                                                                                                                                                                                                                                                                                                                      |

| 7                               | SIG GND        |                    | Analog input signal ground.                                                                                                                                                                                                                                                                                                                                                                                               |

| 30                              | DR GND         |                    | The ground return for the output drivers.                                                                                                                                                                                                                                                                                                                                                                                 |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS (1)(2)(3)

| Supply Voltage (V <sub>A</sub> , V <sub>P</sub> , V <sub>D</sub> , V <sub>DR</sub> ) |                               | -0.3V to 3.8V           |

|--------------------------------------------------------------------------------------|-------------------------------|-------------------------|

| Driver Supply Voltage (V <sub>DR</sub> )                                             | -0.3V to V <sub>A</sub> +0.3V |                         |

| Voltage on Any Input or Output Pin                                                   |                               | -0.3V to V <sub>A</sub> |

| Reference Voltage (V <sub>RT</sub> , V <sub>RB</sub> )                               |                               | GND to V <sub>A</sub>   |

| Input Current, Data Outputs                                                          |                               | ±1 mA                   |

| Input Current all other pins (4)                                                     |                               | ±25 mA                  |

| Package Input Current (4)                                                            |                               | ±50 mA                  |

| Power Dissipation at T <sub>A</sub> = 25°C                                           |                               | See (5)                 |

| ESD Susceptibility (6)                                                               | Human Body Model              | 2500V                   |

|                                                                                      | Machine Model                 | 200V                    |

|                                                                                      | Charged Device Model          | 1000V                   |

| Soldering Temperature, Infrared, 10 second                                           | 235°C                         |                         |

| Storage Temperature                                                                  | −65°C to +150°C               |                         |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For specifications and test conditions, see the Electrical Characteristics. The specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.

- When the input voltage at any pin exceeds the power supplies (that is, less than GND or DR GND, or greater than V<sub>A</sub>, V<sub>P</sub>, V<sub>D</sub> or V<sub>DR</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two.

- The absolute maximum junction temperature (T<sub>J</sub>max) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>J</sub>max, the junction-to-ambient thermal resistance (θ<sub>JA</sub>), and the ambient temperature (T<sub>A</sub>), and can be calculated using the formula  $P_DMAX = (T_Jmax - T_A) / \theta_{JA}$ . Human body model is 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor. Machine model is 220 pF discharged through ZERO

## OPERATING RATINGS (1)(2)

| Operating Temperature Range                            | -40°C ≤ T <sub>A</sub> ≤ +105°C          |                                 |  |

|--------------------------------------------------------|------------------------------------------|---------------------------------|--|

| Supply Voltage (V <sub>A</sub> )                       | +3.0V to +3.6V                           |                                 |  |

| Driver Supply Voltage (V <sub>DR</sub> )               | Driver Supply Voltage (V <sub>DR</sub> ) |                                 |  |

| Maximum Supply Voltage V <sub>D</sub> , V <sub>P</sub> |                                          | V <sub>A</sub> + 0.3V           |  |

| CLK Frequency                                          | PLL Bypassed                             | 1 to 210 MHz                    |  |

|                                                        | PLL used                                 | 15 to 105 MHz                   |  |

| RCLK Frequency (3)                                     |                                          | 2 - 210 MHz                     |  |

| RCLK Duty Cycle                                        |                                          | 35% to 65%                      |  |

| Ground Difference  GND - DR GND                        |                                          | 0V to 300 mV                    |  |

| Upper Reference Voltage (V <sub>RT</sub> )             |                                          | 0.5V to (V <sub>A</sub> - 0.3V) |  |

| Lower Reference Voltage (V <sub>RB</sub> )             | 0V to (V <sub>RT</sub> - 0.5V)           |                                 |  |

| Reference Delta (V <sub>RT</sub> - V <sub>RB</sub> )   | 0.5V to 2.3V                             |                                 |  |

| V <sub>IN</sub> Voltage Range                          | $V_{RB}$ to $V_{RT}$                     |                                 |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For specifications and test conditions, see the Electrical Characteristics. The specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- All voltages are measured with respect to GND = DR GND = 0V, unless otherwise specified.

- RCLK should be stopped with the buffer is not being read.

Copyright © 2007-2013, Texas Instruments Incorporated

### **PACKAGE THERMAL RESISTANCE**

| Package      | $\theta_{ m JA}$ |

|--------------|------------------|

| 48-Lead TQFP | 76 °C/W          |

### **CONVERTER ELECTRICAL CHARACTERISTICS**

The following specifications apply for  $V_A = V_D = V_P = V_{DR} = +3.3 V_{DC}$ ,  $V_{RT} = +1.9 V$ ,  $V_{RB} = 0.3 V$ ,  $C_L = 10$  pF,  $f_{CLK} = 200$  MHz at 50% duty cycle, OEDGE/TEN = 1, Buffer and PLL bypassed. **Boldface limits apply for T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**: all other limits T<sub>J</sub> =  $25^{\circ}$ C  $^{(1)}$ (2)

|                   | Parameter                         | Test Conditions             |            | Typ <sup>(3)</sup> | Limits (3)            | Units<br>(Limits)    |

|-------------------|-----------------------------------|-----------------------------|------------|--------------------|-----------------------|----------------------|

| DC ACC            | CURACY                            |                             |            |                    |                       |                      |

| INL               | Integral Non-Linearity            |                             |            | ±0.55              | ±1.3                  | LSB (max)            |

| DNL               | Differential Non-Linearity        |                             |            | ±0.40              | ±0.9                  | LSB (max)            |

|                   | Missing Codes                     |                             |            |                    | 0                     | (max)                |

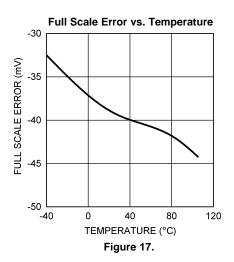

| FSE               | Full Scale Error                  |                             |            | -39                | -80<br>0              | mV (min)<br>mV (max) |

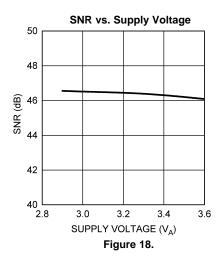

| V <sub>OFF</sub>  | Zero Scale Offset Error           |                             |            | 55                 | 70                    | mV (max)             |

| ANALO             | G INPUT AND REFERENCE CH          | ARACTERISTICS               |            | •                  | ·                     |                      |

|                   | lanut Valtana                     |                             |            | 4.0                | V <sub>RB</sub>       | V (min)              |

| $V_{IN}$          | Input Voltage                     |                             |            | 1.6                | V <sub>RT</sub>       | V (max)              |

| <u> </u>          | V Innut Conscitones               | \/ 0.75\/ +0.5\/rma         | (CLK LOW)  | 3                  |                       | pF                   |

| C <sub>IN</sub>   | V <sub>IN</sub> Input Capacitance | $V_{IN} = 0.75V + 0.5 Vrms$ | (CLK HIGH) | 4                  |                       | pF                   |

| R <sub>IN</sub>   | Analog Input Resistance           |                             | •          | >1                 |                       | ΜΩ                   |

| FPBW              | Full Power Bandwidth              |                             |            | 500                |                       | MHz                  |

| .,                | Ton Defended Malle an             |                             |            | 4.0                | V <sub>A</sub>        | V (max)              |

| $V_{RT}$          | Top Reference Voltage             |                             |            | 1.9                | 0.5                   | V (min)              |

|                   | Detters Deference Valters         |                             |            | 0.0                | V <sub>RT</sub> - 0.5 | V (max)              |

| $V_{RB}$          | Bottom Reference Voltage          |                             |            | 0.3                | 0                     | V (min)              |

| V <sub>RT</sub> - | Deference Voltage Delte           |                             |            | 1.6                | 0.5                   | V (min)              |

| $V_{RB}$          | Reference Voltage Delta           |                             |            | 1.0                | 2.3                   | V (max)              |

| D                 | Deference Lodder Decistores       | \/ to \/                    |            | 160                | 145                   | Ω (min)              |

| R <sub>REF</sub>  | Reference Ladder Resistance       | $V_{RT}$ to $V_{RB}$        |            | 160                | 200                   | Ω (max)              |

| DIGITA            | L INPUT CHARACTERISTICS           |                             |            | •                  |                       |                      |

| \/                | Lania High Janua Valtaga          |                             | OEDGE/TEN  | 2.2                | 2.7                   | V (min)              |

| $V_{IH}$          | Logic High Input Voltage          |                             | Others     | 1.6                | 2.1                   | V (min)              |

| 17                | Lania Laur Ianut Valtana          |                             | OEDGE/TEN  | 0.9                | 0.5                   | V (max)              |

| $V_{IL}$          | Logic Low Input Voltage           |                             | Others     | 1.3                | 0.7                   | V (max)              |

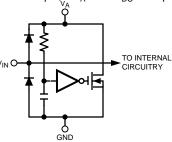

(1) The analog inputs are protected as shown below. Input voltage magnitudes up to V<sub>A</sub> + 300 mV or to 300 mV below GND will not damage this device. However, errors in the A/D conversion can occur if the input goes above V<sub>A</sub> or below GND by more than 100 mV. For example, if V<sub>A</sub> is 3.3V<sub>DC</sub> the input voltage must be ≤3.4V<sub>DC</sub> to ensure accurate conversions.

- (2) To ensure accuracy, it is required that V<sub>A</sub>, V<sub>D</sub>, V<sub>P</sub> and V<sub>DR</sub> be well bypassed. Each supply pin should be decoupled with separate bypass capacitors.

- (3) Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are specified to Texas Instrument's AOQL (Average Outgoing Quality Level).

## **CONVERTER ELECTRICAL CHARACTERISTICS (continued)**

The following specifications apply for  $V_A = V_D = V_P = V_{DR} = +3.3V_{DC}$ ,  $V_{RT} = +1.9V$ ,  $V_{RB} = 0.3V$ ,  $C_L = 10$  pF,  $f_{CLK} = 200$  MHz at 50% duty cycle, OEDGE/TEN = 1, Buffer and PLL bypassed. **Boldface limits apply for T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**: all other limits T<sub>J</sub> = 25°C (1)(2)

|                  | Parameter                    | Test Conditions                                           |                          |             | Typ <sup>(3)</sup> | Limits (3) | Units<br>(Limits) |

|------------------|------------------------------|-----------------------------------------------------------|--------------------------|-------------|--------------------|------------|-------------------|

|                  |                              |                                                           | OFFICE (TEN) Operational |             | 10                 |            |                   |

| I <sub>IH</sub>  | Logic High Input Current     | $V_{IH} = V_{DR} = V_A = 3.6V$                            | OEDGE/TEN                | Test Mode   | 70                 |            | μA<br>μA          |

|                  |                              |                                                           | Others                   | •           | 10                 |            | nA                |

|                  |                              |                                                           | OEDGE/TEN                | Operational | -10                |            | μA                |

| I <sub>IL</sub>  | Logic Low Input Current      | $V_{IL} = 0V, V_{DR} = V_A = 3.0V$                        | OLDGE/TEN                | Test Mode   | -600               |            | μA                |

|                  |                              |                                                           | Others                   |             | -50                |            | nA                |

| C <sub>IN</sub>  | Logic Input Capacitance      |                                                           |                          |             | 3                  |            | pF                |

| DIGITAL          | L OUTPUT CHARACTERISTICS     |                                                           |                          |             |                    |            |                   |

| V <sub>OH</sub>  | High Level Output Voltage    | $V_A = V_{DR} = 3.0V, I_{OH} = -5$                        | 3.0                      | 2.4         | V (min)            |            |                   |

| V <sub>OL</sub>  | Low Level Output Voltage     | $V_A = V_{DR} = 3.0V, I_{OL} = 5 \text{ m}$               | Α                        |             | 0.25               | 0.5        | V (max)           |

| C <sub>OUT</sub> | Digital Output Capacitance   |                                                           |                          |             | 2                  |            | pF                |

| DYNAM            | IC PERFORMANCE               |                                                           |                          |             |                    |            |                   |

|                  |                              | $f_{IN} = 10 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB                   |             | 7.4                |            | Bits              |

|                  |                              | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0$                |                          |             | 7.2                | 6.8        | Bits (min)        |

| ENOB             | Effective Number of Bits     | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB, PLL x8           |             | 7.2                |            | Bits              |

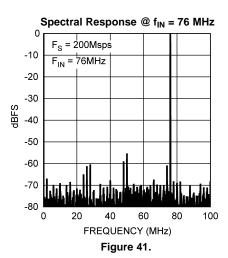

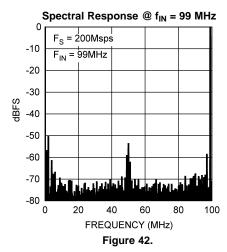

|                  |                              | $f_{IN} = 100 \text{ MHz}, V_{IN} = FS - 0.25 \text{ dB}$ |                          |             | 7.0                |            | Bits              |

|                  |                              | $f_{IN}$ = 100 MHz, $V_{IN}$ = FS - 0.25 dB, PLL x4       |                          |             |                    |            | Bits              |

|                  | Signal-to-Noise & Distortion | $f_{IN} = 10 \text{ MHz}, V_{IN} = FS - 0.25 \text{ dB}$  |                          |             | 46                 |            | dBc               |

|                  |                              | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0.25 \text{ dB}$  |                          |             | 45                 | 42.7       | dBc (min)         |

| SINAD            |                              | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0.$               | .25 dB, PLL x8           |             | 45                 |            | dBc               |

|                  |                              | $f_{IN} = 100 \text{ MHz}, V_{IN} = FS - 6$               | 0.25 dB                  |             | 44                 |            | dBc               |

|                  |                              | $f_{IN} = 100 \text{ MHz}, V_{IN} = FS - 6$               | 43.4                     |             | dBc                |            |                   |

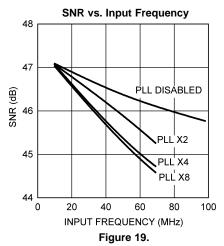

|                  |                              | $f_{IN} = 10 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB                   |             | 47                 |            | dBc               |

|                  |                              | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0.25 \text{ dB}$  |                          |             |                    | 43.7       | dBc (min)         |

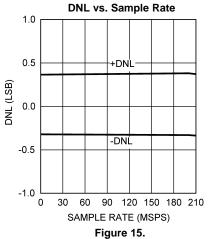

| SNR              | Signal-to-Noise Ratio        | $f_{IN}$ = 49 MHz, $V_{IN}$ = FS - 0.25 dB, PLL x8        |                          |             |                    |            | dBc               |

|                  |                              | $f_{IN}$ = 100 MHz, $V_{IN}$ = FS - 0.25 dB               |                          |             |                    |            | dBc               |

|                  |                              | $f_{IN} = 100 \text{ MHz}, V_{IN} = FS - 6$               | 0.25 dB, PLL x4          |             | 45.6               |            | \dBc              |

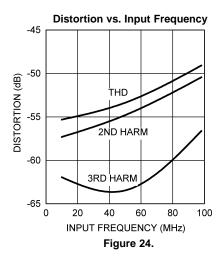

|                  |                              | $f_{IN} = 10 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB                   |             | 56                 |            | dBc               |

|                  |                              | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB                   |             | 56                 |            | dBc               |

| SFDR             | Spurious Free Dynamic Range  | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB, PLL x8           |             | 56                 |            | dBc               |

|                  |                              | $f_{IN} = 100 \text{ MHz}, V_{IN} = FS - 6$               | 0.25 dB                  |             | 50                 |            | dBc               |

|                  |                              | $f_{IN} = 100 \text{ MHz}, V_{IN} = FS - 6$               | 0.25 dB, PLL x4          |             | 49.7               |            | dBc               |

|                  |                              | $f_{IN} = 10 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB                   |             | -55                |            | dBc               |

|                  |                              | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB                   |             | -53                |            | dBc               |

| THD              | Total Harmonic Distortion    | $f_{IN} = 49 \text{ MHz}, V_{IN} = FS - 0$                | .25 dB, PLL x8           |             | -53                |            | dBc               |

|                  |                              | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FS - 0.25 dB |                          |             | -49                |            | dBc               |

|                  | _                            | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FS -         | 0.25 dB, PLL x4          |             | -47.5              |            | dBc               |

| -                |                              | f <sub>IN</sub> = 10 MHz, V <sub>IN</sub> = FS - 0        | .25 dB                   |             | -57                |            | dBc               |

|                  |                              | f <sub>IN</sub> = 49 MHz, V <sub>IN</sub> = FS - 0        | .25 dB                   |             | -55                |            | dBc               |

| HD2              | 2nd Harmonic Distortion      | f <sub>IN</sub> = 49 MHz, V <sub>IN</sub> = FS - 0        | .25 dB, PLL x8           |             | -55                |            | dBc               |

|                  |                              | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FS -         | 0.25 dB                  |             | -50                |            | dBc               |

|                  |                              | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FS -         | 0.25 dB, PLL x4          |             | -49.9              |            | dBc               |

Copyright © 2007–2013, Texas Instruments Incorporated

## **CONVERTER ELECTRICAL CHARACTERISTICS (continued)**

The following specifications apply for  $V_A = V_D = V_P = V_{DR} = +3.3V_{DC}$ ,  $V_{RT} = +1.9V$ ,  $V_{RB} = 0.3V$ ,  $C_L = 10$  pF,  $f_{CLK} = 200$  MHz at 50% duty cycle, OEDGE/TEN = 1, Buffer and PLL bypassed. **Boldface limits apply for T**<sub>J</sub> = **T**<sub>MIN</sub> **to T**<sub>MAX</sub>: all other limits T<sub>J</sub> =  $25^{\circ}$ C  $^{(1)(2)}$

|                                                       | Parameter                         | Test Conditions                                                                                                | Typ <sup>(3)</sup> | Limits (3) | Units<br>(Limits) |

|-------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------|------------|-------------------|

|                                                       |                                   | f <sub>IN</sub> = 10 MHz, V <sub>IN</sub> = FS - 0.25 dB                                                       | -62                |            | dBc               |

| HD3                                                   |                                   | f <sub>IN</sub> = 49 MHz, V <sub>IN</sub> = FS - 0.25 dB                                                       | -63                |            | dBc               |

|                                                       | 3rd Harmonic Distortion           | f <sub>IN</sub> = 49 MHz, V <sub>IN</sub> = FS - 0.25 dB, PLL x8                                               | -62                |            | dBc               |

|                                                       |                                   | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FS - 0.25 dB                                                      | -56                |            | dBc               |

|                                                       |                                   | f <sub>IN</sub> = 100 MHz, V <sub>IN</sub> = FS - 0.25 dB, PLL x4                                              | -54.6              |            | dBc               |

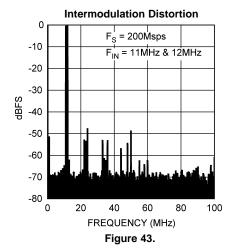

| IMD                                                   | Intermodulation Distortion        | $f_1 = 11 \text{ MHz}, V_{IN} = FS - 6.25 \text{ dB}$<br>$f_2 = 12 \text{ MHz}, V_{IN} = FS - 6.25 \text{ dB}$ | -50                |            | dBc               |

| POWER                                                 | SUPPLY CHARACTERISTICS            |                                                                                                                |                    |            |                   |

|                                                       |                                   | DC Input                                                                                                       | 72.5               |            | mA                |

| $I_A$                                                 | Analog Supply Current             | $f_{IN} = 50 \text{ MHz}$                                                                                      | 76.8               | 88.3       | mA (max)          |

|                                                       |                                   | PD High                                                                                                        | 0.3                |            | mA                |

|                                                       |                                   | DC Input, Buffer bypassed                                                                                      | 1.2                |            | mA                |

|                                                       |                                   | f <sub>IN</sub> = 50 MHz, Buffer bypassed                                                                      | 1.6                | 2.1        | mA (max)          |

| $I_D$                                                 | Digital Core Supply Current       | f <sub>IN</sub> = 50 MHz, 1k writing to Buffer <sup>(4)</sup>                                                  | 38                 | 42.4       | mA                |

|                                                       |                                   | PDADC High, reading Buffer (4)                                                                                 | 1.1                |            | mA                |

|                                                       |                                   | PD High                                                                                                        | 0.3                |            | mA                |

|                                                       |                                   | PLL x2                                                                                                         | 8.8                | 10.1       | mA (max)          |

| I <sub>P</sub>                                        | PLL Supply Current                | PLL disabled                                                                                                   | 3.6                | 4.3        | mA (max)          |

|                                                       |                                   | PD High                                                                                                        | 60                 |            | μA                |

|                                                       |                                   | DC Input                                                                                                       | 7                  |            | mA                |

| $I_{DR}$                                              | Output Driver Supply Current      | f <sub>IN</sub> = 50 MHz                                                                                       | 41                 | 57         | mA (max)          |

|                                                       |                                   | PD High                                                                                                        | 25                 |            | μA                |

|                                                       |                                   | DC Input, Buffer bypassed, PLL x2                                                                              | 97.5               |            | mA                |

| I <sub>A</sub> + I <sub>D</sub><br>+ I <sub>P</sub> + | Total Operating Current           | 50 MHz Input, writing to Buffer, PLL X2                                                                        | 164.6              | 198        | mA (max)          |

| I <sub>DR</sub>                                       |                                   | PDADC = Hi, reading Buffer,<br>RCLK = 200 MHz, D.C. input                                                      | 20                 |            | mA                |

|                                                       |                                   | PD High                                                                                                        | 0.65               |            | mA                |

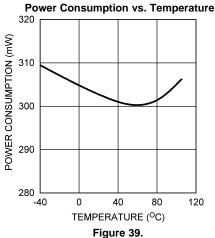

|                                                       |                                   | DC Input, Buffer & PLL bypassed                                                                                | 306                |            | mW                |

| PC                                                    | Power Consumption                 | 50 MHz Input, writing to Buffer, PLL X2                                                                        | 543                | 653        | mW (max)          |

|                                                       | ·                                 | PDADC High, reading Buffer, PLL disabled <sup>(5)</sup>                                                        | 66                 |            | mW                |

|                                                       |                                   | PD High                                                                                                        | 2.15               |            | mW                |

| PSRR <sub>1</sub>                                     | D.C. Power Supply Rejection Ratio | FSE change with 3.0V to 3.6V change in V <sub>A</sub> 48                                                       |                    | dB         |                   |

| PSRR <sub>2</sub>                                     | A.C. Power Supply Rejection Ratio | SNR reduction with 200 mV at 10MHz on supply                                                                   | TBD                |            | dB                |

This current or power is used only during the short time that the buffer is being written to or read from, depending upon the specification.

This current or power is used only during the short time that the buffer is being written to or read from, depending upon the specification.

#### CONVERTER TIMING CHARACTERISTICS

The following specifications apply for  $V_A = V_{DR} = +3.3 V_{DC}$ ,  $V_{RT} = +1.9 V$ ,  $V_{RB} = 0.3 V$ ,  $C_L = 50$  pF,  $f_{CLK} = 200$  MHz at 50% duty cycle, OEDGE/TEN = 1, Buffer and PLL bypassed. **Boldface limits apply for T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**: all other limits T<sub>J</sub> = 25°C  $^{(1)}(2)$

|                   | Parameter                                     | Test Conditions        | Typ <sup>(3)</sup> | Limits <sup>(3)</sup> | Units<br>(Limits)           |  |

|-------------------|-----------------------------------------------|------------------------|--------------------|-----------------------|-----------------------------|--|

| ,                 | Maria de la control de la Parte               | PLL Disabled           | 210                | 200                   | MHz (min)                   |  |

| f <sub>C1</sub>   | Maximum Input Clock Rate                      | Using PLL              | 15                 | 105                   | MHz (min)                   |  |

| f <sub>C2</sub>   | Mariana Innut Clark Data                      | PLL Disabled           | 1                  |                       | MHz                         |  |

|                   | Minimum Input Clock Rate                      | Using PLL              | 15                 |                       | MHz                         |  |

| t <sub>CL</sub>   | Minimum CLK Low Time                          | (4)                    |                    | 1.7                   | ns (min)                    |  |

| t <sub>CH</sub>   | Minimum CLK High Time                         | (4)                    |                    | 1.7                   | ns (min)                    |  |

| f <sub>RC1</sub>  | Maximum RCLK Rate                             | (5)                    | 210                | 200                   | MHz (min)                   |  |

| f <sub>RC2</sub>  | Minimum RCLK Rate                             | (5)                    | 2                  |                       | MHz                         |  |

| t <sub>RCL</sub>  | Minimum RCLK Low Time                         | (4)                    |                    | 2.0                   | ns (min)                    |  |

| t <sub>RCH</sub>  | Minimum RCLK High Time                        | (4)                    |                    | 2.0                   | ns (min)                    |  |

| ΔDC               | DRDY to RCLK Duty Cycle Delta                 |                        | 0.3                | ±3                    | %                           |  |

| t <sub>SU</sub>   | REN to RCLK Set-Up Time                       |                        | -0.4               | -0.8<br>4.0           | ns (min)<br>ns (max)        |  |

| t <sub>RR</sub>   | RCLK Rising Edge to DRDY Rising Edge          |                        | 3.8                | 2.4<br>5.9            | ns (min)<br>ns (max)        |  |

| t <sub>RF</sub>   | RCLK Falling Edge to DRDY Falling Edge        |                        | 3.5                |                       | ns                          |  |

| t <sub>SKDR</sub> | Skew of DRDY Rising Edge to DATA              |                        | 160                |                       | ps                          |  |

| t <sub>SKR</sub>  | RCLK Falling Edge to First DATA<br>Byte       |                        | 2.3                | 1.8<br>7.4            | ns (min)<br>ns (max)        |  |

| t <sub>SKEF</sub> | Skew of DRDY Rising Edge to EF<br>Rising Edge |                        | 36                 |                       | ps                          |  |

| t <sub>CFF</sub>  | CLK Rising Edge to FF Rising Edge             |                        | 4.2                |                       | ns                          |  |

| t <sub>FFW</sub>  | FF Rising Edge to WENSYNC Falling Edge        | ASW pin high           | 4.2                |                       | ns                          |  |

| t <sub>CW</sub>   | CLK Rising Edge to WENSYNC<br>Rising Edge     | PLL Disabled           | 3.5                | 2.4<br>5.5            | ns (min)<br>ns (max)        |  |

| t <sub>RST</sub>  | RESET Pulse Width                             | (4)                    |                    | 4                     | Write Clock<br>Cycles (min) |  |

|                   | Output Data Rise Time                         | C <sub>L</sub> = 10 pF | 0.9                |                       | ns                          |  |

| t <sub>r</sub>    | (0.4V to 2.5V)                                | C <sub>L</sub> = 20 pF | 2                  |                       | ns                          |  |

(1) The analog inputs are protected as shown below. Input voltage magnitudes up to V<sub>A</sub> + 300 mV or to 300 mV below GND will not damage this device. However, errors in the A/D conversion can occur if the input goes above V<sub>A</sub> or below GND by more than 100 mV. For example, if V<sub>A</sub> is 3.3V<sub>DC</sub> the input voltage must be ≤3.4V<sub>DC</sub> to ensure accurate conversions.

- (2) To ensure accuracy, it is required that V<sub>A</sub>, V<sub>D</sub>, V<sub>P</sub> and V<sub>DR</sub> be well bypassed. Each supply pin should be decoupled with separate bypass capacitors.

- (3) Typical figures are at T<sub>J</sub> = 25°C, and represent most likely parametric norms. Test limits are specified to Texas Instrument's AOQL (Average Outgoing Quality Level).

- 4) This parameter is specified by design and/or characterization and is not production tested.

- (5) RCLK should be stopped with the buffer is not being read.

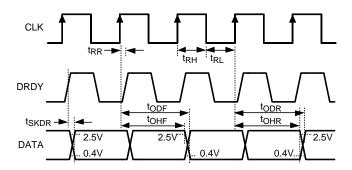

## **CONVERTER TIMING CHARACTERISTICS (continued)**

The following specifications apply for  $V_A = V_{DR} = +3.3V_{DC}$ ,  $V_{RT} = +1.9V$ ,  $V_{RB} = 0.3V$ ,  $C_L = 50$  pF,  $f_{CLK} = 200$  MHz at 50% duty cycle, OEDGE/TEN = 1, Buffer and PLL bypassed. **Boldface limits apply for T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**: all other limits T<sub>J</sub> = 25°C (1)(2)

|                    | Parameter                                       | Test Co                               | Test Conditions |     | Limits <sup>(3)</sup> | Units<br>(Limits)    |

|--------------------|-------------------------------------------------|---------------------------------------|-----------------|-----|-----------------------|----------------------|

|                    | Output Data Fall Time                           | C <sub>L</sub> = 10 pF                |                 | 1.4 |                       | ns                   |

| t <sub>f</sub>     | (2.4V to 0.4V)                                  | C <sub>L</sub> = 20 pF                |                 | 3.2 |                       | ns                   |

| t <sub>ODF</sub>   | RCLK Rising Edge to Data Output                 | Reading Buffer                        |                 | 7.0 | 4.0<br>11.7           | ns (min)<br>ns (max) |

| 02.                | Fall to 0.4V                                    | Buffer bypassed, PL                   | L disabled      | 5.5 |                       | ns                   |

| t <sub>ODR</sub>   | RCLK Rising Edge to Data Output                 | Reading Buffer                        |                 | 6.5 | 2.3<br>13.1           | ns (min)<br>ns (max) |

| ODIC               | Rise to 2.5V                                    | Buffer bypassed, PLL disabled         |                 | 5.5 |                       | ns                   |

| t <sub>OHF</sub>   | RCLK Rising Edge to Data Output Fall to 2.5V    | Reading Buffer                        |                 | 3.8 | 2.4<br>5.5            | ns (min)<br>ns (max) |

| t <sub>OHR</sub>   | RCLK Rising Edge to Data Output<br>Rise to 0.4V | Reading Buffer                        |                 | 4.5 | 2.6<br>6.9            | ns (min)<br>ns (max) |

|                    | Output Olava Pata                               | Output Falling (2.4V to 0.4V)         |                 | 1.5 |                       | V / ns               |

| t <sub>SLEW</sub>  | Output Slew Rate                                | Output Rising (0.4V to 2.5V)          |                 | 2.3 |                       | V / ns               |

|                    | BB 1                                            | PLL Enabled                           |                 | 20  |                       | μs                   |

| t <sub>DRDY1</sub> | PD Low to Device Active                         | PLL Bypassed                          |                 | 2   |                       | μs                   |

| t <sub>DRDY2</sub> | PDADC Low to Device Active                      |                                       |                 | 2   |                       | μs                   |

|                    | Pipeline Delay (Latency)                        |                                       |                 | 6   |                       | Clock Cycles         |

|                    | Compliant (Amentura) Dalari                     | CLK Rise to                           | PLL on          | 3.4 |                       | ns                   |

| t <sub>AD</sub>    | Sampling (Aperture) Delay                       | Acquisition of Data                   | PLL off         | 3.9 |                       | ns                   |

|                    | A                                               | PLL Bypassed                          |                 | 2   |                       | ps rms               |

| $t_{AJ}$           | Aperture Jitter                                 | PLL Enabled in x8 mode <sup>(6)</sup> |                 | 7   |                       | ps rms               |

<sup>(6)</sup> Jitter with the PLL enabled is measured with 32k samples and the PLL in the x8 multiplication mode.

### SPECIFICATION DEFINITIONS

- **APERTURE (SAMPLING) DELAY** is that time delay after the rise of the sample clock until the input signal is sampled within the ADC.

- **APERTURE JITTER** is the variation in aperture delay from sample to sample. Aperture jitter shows up as input noise.

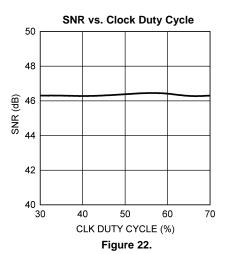

- **CLOCK DUTY CYCLE** is the ratio of the time that the clock waveform is at a logic high to the total time of one clock period.

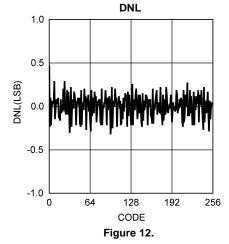

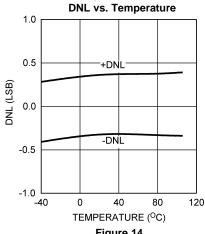

- **DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB. Measured at 200 MSPS with a ramp input.

- **EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion Ratio, or SINAD. ENOB is defined as (SINAD 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

- **FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

- **FULL-SCALE ERROR** is a measure of how far the last code transition is from the ideal  $1\frac{1}{2}$  LSB below  $V_{RT}$  and is defined as:

$$FSE = V_{max} + 1.5 LSB - V_{RT}$$

where

ullet  $V_{max}$  is the voltage at which the transition to the maximum (full scale) code occurs

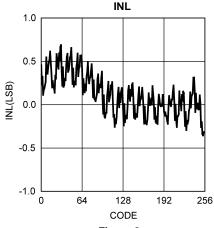

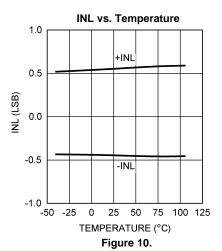

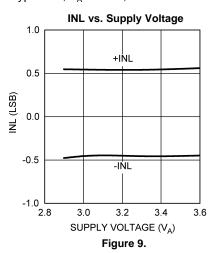

INTEGRAL NON-LINEARITY (INL) is a measure of the deviation of each individual code from a line drawn from

0 Submit Documentation Feedback

(1)

zero scale (½ LSB below the first code transition) through positive full scale (½ LSB above the last code transition). The deviation of any given code from this straight line is measured from the center of that code value. The end point test method is used. Measured at 200 MSPS with a ramp input.

- **INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time. it is defined as the ratio of the power in the second and third order intermodulation products to the power in one of the original frequencies. IMD is usually expressed in dBFS.

- **MISSING CODES** are those output codes that are skipped and will never appear at the ADC outputs. These codes cannot be reached with any input value.

- **OFFSET ERROR** is the error in the input voltage required to cause the first code transition. It is defined as the difference between the voltage required to cause the first code transition and the ideal voltage (1/2 LSB) to cause that transition.

$$V_{OFF} = V_{ZT} - 1/2 LSB = V_{ZT} - (V_{RT} - V_{RB}) / 512$$

where

V<sub>ZT</sub> is the first code transition input voltage

(2)

- **OUTPUT DELAY** is the time delay after the rising edge of the RCLK input before the data update is present at the output pins.

- **OUTPUT HOLD TIME** is the length of time that the output data is valid after the rise of CLK or RCLK output.

- **PIPELINE DELAY (LATENCY)** is the number of clock cycles between initiation of conversion and when that data is presented to the output driver stage. New data is available at every clock cycle, but the data lags the conversion by the Pipeline Delay plus the Output Delay.

- **POWER SUPPLY REJECTION RATIO (PSRR)** is a measure of how well the ADC rejects a change in the power supply voltage. For the ADC08B200, PSRR1 is the ratio of the change in Full-Scale Error that results from a change in the DC power supply voltage, expressed in dB. PSRR2 is a measure of how well an a.c. signal riding upon the power supply is rejected at the output.

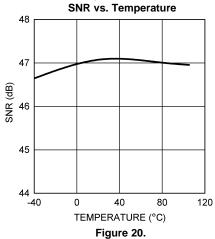

- **SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal at the output to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or d.c.

- **SIGNAL TO NOISE PLUS DISTORTION (S/(N+D) or SINAD)** is the ratio, expressed in dB, of the rms value of the input signal at the output to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

- **SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the rms values of the input signal at the output and the peak spurious signal, where a spurious signal is any signal present in the output spectrum that is not present at the input.

- **TOTAL HARMONIC DISTORTION (THD)** is the ratio expressed in dB, of the rms total of the first nine harmonic levels at the output to the level of the fundamental at the output. THD is calculated as

THD = 20 x log

$$\sqrt{\frac{A_{f2}^2 + ... + A_{f10}^2}{A_{f1}^2}}$$

where

- A<sub>f1</sub> is the RMS power of the fundamental (output) frequency

- A<sub>f2</sub> through A<sub>f10</sub> are the RMS power of the first 9 harmonic frequencies in the output spectrum

(3)

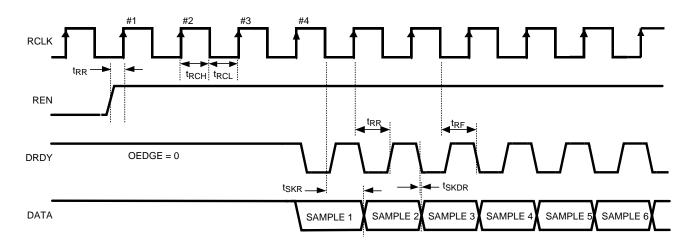

## **TIMING DIAGRAMS (PLL BYPASSED)**

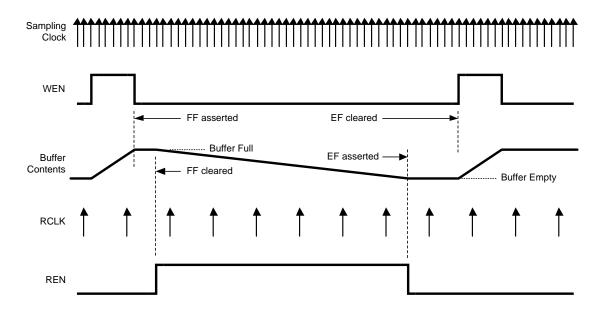

Figure 2. ADC08B200 Data Capture and Read Operation

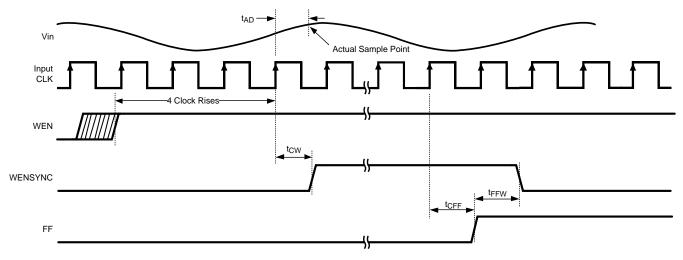

Figure 3. ADC08B200 Capture and Write Enable Timing

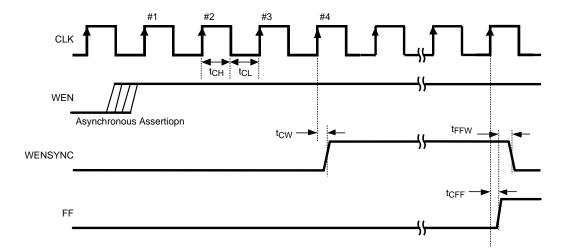

Figure 4. ADC08B200 Buffer Write Timing

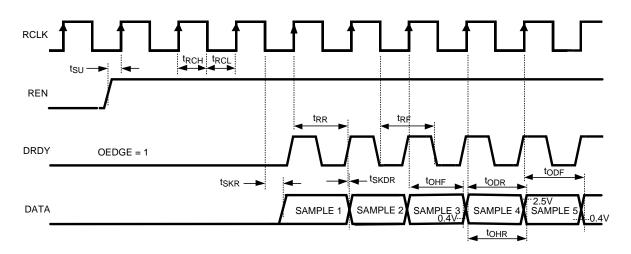

Figure 5. ADC08B200 Buffer Read Timing (OEDGE/TEN = 1)

Figure 6. ADC08B200 Buffer Read Timing (OEDGE/TEN = 0)

Figure 7. ADC08B200 Buffer Bypassed Timing

## TYPICAL PERFORMANCE CHARACTERISTICS

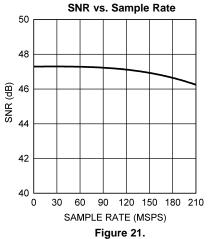

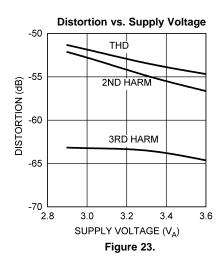

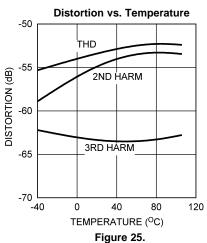

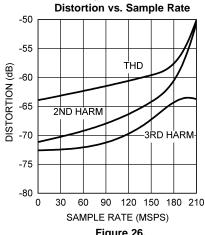

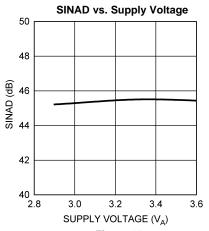

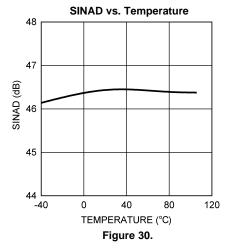

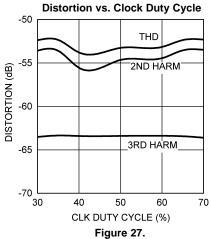

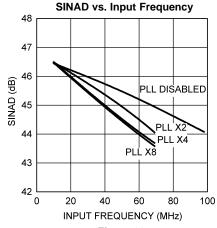

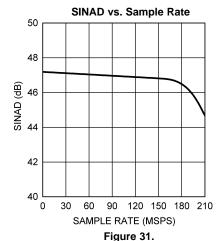

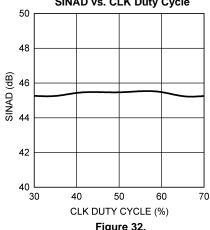

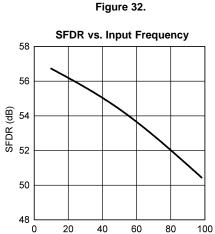

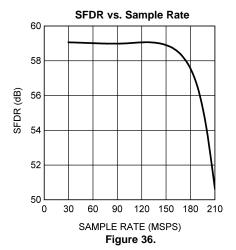

$V_A = V_D = V_P = V_{DR} = 3.3V$ ,  $f_{CLK} = 200$  MHz,  $f_{IN} = 50$  MHz, PLL & Buffer bypassed,  $T_A = 25$ °C, unless otherwise stated

1.0 +INL vs. Sample Rate

1.0 -0.5 -1.0 0 30 60 90 120 150 180 210 SAMPLE RATE (MSPS)

Figure 11.

$V_A = V_D = V_P = V_{DR} = 3.3V$ ,  $f_{CLK} = 200$  MHz,  $f_{IN} = 50$  MHz, PLL & Buffer bypassed,  $T_A = 25$ °C, unless otherwise stated

$V_A = V_D = V_P = V_{DR} = 3.3V$ ,  $f_{CLK} = 200$  MHz,  $f_{IN} = 50$  MHz, PLL & Buffer bypassed,  $T_A = 25$ °C, unless otherwise stated

$V_A = V_D = V_P = V_{DR} = 3.3V$ ,  $f_{CLK} = 200$  MHz,  $f_{IN} = 50$  MHz, PLL & Buffer bypassed,  $T_A = 25$ °C, unless otherwise stated

Figure 28.

Figure 29.

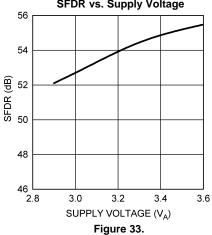

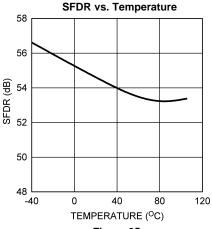

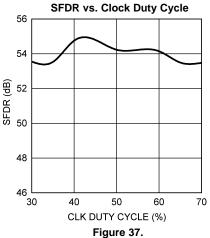

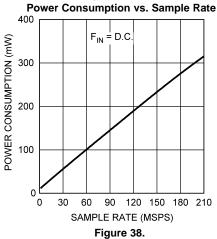

$V_{A} = V_{D} = V_{P} = V_{DR} = 3.3V, \ f_{CLK} = 200 \ \text{MHz}, \ f_{IN} = 50 \ \text{MHz}, \ \text{PLL \& Buffer bypassed}, \ T_{A} = 25^{\circ}\text{C}, \ \text{unless otherwise stated} \\ \textbf{SINAD vs. CLK Duty Cycle} \\ \textbf{SFDR vs. Supply Voltage}$

INPUT FREQUENCY (MHz) Figure 34.

80

20

Figure 35.

$V_{A} = V_{D} = V_{P} = V_{DR} = 3.3V, \ f_{CLK} = 200 \ MHz, \ f_{IN} = 50 \ MHz, \ PLL \ \& \ Buffer \ bypassed, \ T_{A} = 25^{\circ}C, \ unless \ otherwise \ stated$

#### FUNCTIONAL DESCRIPTION

The ADC08B200 integrates an 8-bit, high speed ADC and a configurable capture buffer of up to 1 kilobyte, allowing the sampling and processing tasks to be independent of each other. This functionality is intended for those applications that need to sample an input signal at a high rate and then read the collected samples at a slower rate. The Timing Diagrams illustrate the operation of the ADC08B200.

The analog input signal that is within the voltage range set by  $V_{RT}$  and  $V_{RB}$  is digitized to eight bits. Input voltages below  $V_{RB}$  will cause the output word to consist of all zeroes. Input voltages above  $V_{RT}$  will cause the output word to consist of all ones.

The ADC08B200 exhibits a power consumption that is proportional to frequency, limiting power consumption to what is needed at the clock rate that is used. This, its excellent performance over a wide range of clock frequencies and the incorporation of a capture buffer make ADC08B200 an ideal choice for many 8-bit ADC applications.

Data is acquired at the rising edge of the sample clock and, in the buffer bypass mode, the digital equivalent of that data is available at the digital outputs 6 clock cycles plus t<sub>OD</sub> later. When the Buffer is enabled, the converted data is written to the buffer with each internal conversion clock cycle and can be read out with the RCLK signal. The ADC08B200 will convert as long as a CLK signal is present, but when using the buffer no writing to the buffer will occur when that buffer is full. The output coding is straight binary.

The entire device is in the active state when the Power Down pin (PD) is low. When the PD pin is high, the entire device is in the power down mode, consuming very little power. Holding the clock input low after raising the Power Down pin will further reduce the power consumption in the power down mode.

When the PDADC pin is high, only the A/D converter itself is in the power down mode. The rest of the chip is left powered up so that the capture buffer may be read. If both the PD and PDADC pins are high, the PD pin dominates and the entire device is powered down.

The A/D converter sample clock can be either the clock signal at the CLK input pin or a multiplied version of that clock. The clock multiplier can be 2, 4 or 8. In any case, the sample clock is also used to write the converter data into the capture buffer when that buffer is used.

As long as the chip is not in a power down state and there is a clock signal present, the A/D converter is converting the input signal. However, the data is stored into the capture buffer, when the buffer is used, only while the Write Enable (WEN) input is high. The data is read from the capture buffer with the RCLK signal, which can be a free running clock, while the Read Enable (REN) signal is high.

Note that the capture buffer on this chip must be entirely filled to its configured size before reading its contents can begin. It is not possible to write to and read from the buffer at the same time and the WEN and REN inputs should not be high at the same time. If they are high at the same time, the REN input is ignored. This is true even if the REN input is high first and a read operation is progressing normally when the WEN input goes high. Asserting the WEN input while REN is high will cause the read operation to be aborted, an internal buffer reset to be issued (resetting the pointers) and a capture operation to begin. Although this device is intended for fast capture and slower read out applications, it is possible for the RCLK to operate at the same rate or faster than the sample clock.

Two status flags are provided to manage the capture buffer. As the name suggests, the Full Flag (FF) goes high when the buffer is full. The next sample clock rise after the assertion of FF will begin writing over the oldest data because the write pointer will "wrap around". This is called an "over run" condition. Similarly, the Empty Flag (EF) indicates that the last of the data has been read and the buffer is empty. When EF goes high, the DRDY and Data outputs stop switching and both DRDY and the Data lines remain low if OEDGE=1. Both remain high if OEDGE=0.

The user has the option to stop writing to the buffer automatically upon a buffer full condition with the use of the ASW (Auto Stop Write) input. If the ASW input is low, the buffer will be continually written to, resulting in the possibility of the write pointer "wrapping around" and the data continually being overwritten as long as there is a clock and the WEN input is high. If the ASW input is high, the write operation stops upon reaching the "full" condition.

FF goes low upon device reset and when the "full" condition is removed by starting a transfer operation with the assertion of REN. The EF output goes low when the "empty" condition is removed by starting a capture operation with the raising of WEN. The EF output goes high upon device reset because resetting empties the buffer.

Copyright © 2007–2013, Texas Instruments Incorporated

The RESET signal resets the read and write pointers and the EF and FF flags. The RESET signal also stops the read operation early (before the EF flag goes high). Consequently, only a partial read is performed if the RESET input goes high while a buffer read out is under way. This allows the buffer pointers to be reset so a new capture operation can begin. The RESET signal has no effect upon the A/D converter, which has its own internal Power-On Reset circuit.

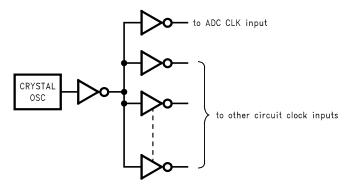

Note that the RCLK input does not need to be as noise (jitter) free as does the CLK signal. The reason for this is that RCLK is only used to read the Capture Buffer, while the CLK signal is either the ADC sample clock or is the reference for the internal PLL that generates the sample clock for the ADC. Consequently, CLK jitter directly affects the ADC's SNR performance. There is no requirement for the RCLK to have any fixed relationship with CLK in terms of phase or frequency.

## **Applications Information**

#### REFERENCE INPUTS

The reference inputs  $V_{RT}$  and  $V_{RB}$  are the top and bottom of the reference ladder, respectively. Input signals between these two voltages will be digitized to 8 bits. External voltages applied to the reference input pins should be within the range specified in OPERATING RATINGS and ELECTRICAL CHARACTERISTICS. Any device used to drive the reference pins should be able to source sufficient current into the  $V_{RT}$  pin and sink sufficient current from the  $V_{RB}$  pin to maintain the desired voltages.

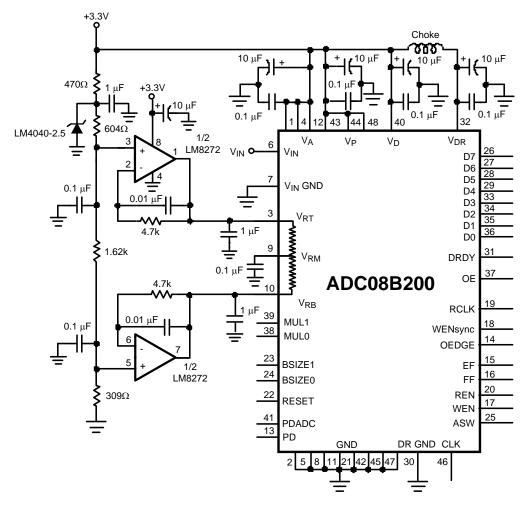

Because of the ladder and external resistor tolerances, the reference voltage of this circuit can vary too much for some applications.

Figure 44. Simple, Low Component Count Reference Biasing

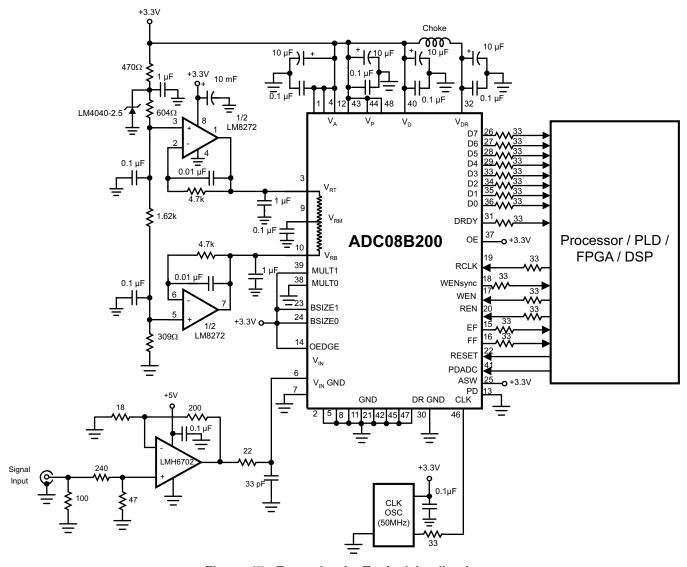

The reference bias circuit of Figure 44 is very simple and the performance is adequate for many applications. However, circuit tolerances will lead to a wide reference voltage range. Better reference tolerance can be achieved by driving the reference pins with low impedance sources.

The circuit of Figure 45 will allow a more accurate setting of the reference voltages, with upper and lower reference accuracies of about 16 mV, or about 2 1/2 LSB. The upper amplifier must be able to source the reference current as determined by the value of the reference resistor and the value of  $(V_{RT} - V_{RB})$ . The lower amplifier must be able to sink this reference current. Both amplifiers should be stable with a capacitive load.

The *LM8272* was chosen because of its rail-to-rail input and output capability, its high output current capability and its ability to drive large capacitive loads.

The divider resistors at the inputs to the amplifiers could be changed to suit the application reference voltage needs, or the divider can be replaced with potentiometers or DACs for precise settings. The bottom of the ladder (V<sub>RR</sub>) may be returned to ground if the minimum input signal excursion is 0V.

$V_{RT}$  should always be at least 0.5V more positive than  $V_{RB}$ . While  $V_{RT}$  may be as high as the  $V_A$  supply voltage and  $V_{RB}$  may be as low as ground, the difference between these two voltages ( $V_{RT}$  –  $V_{RB}$  should not exceed 2.3V to prevent a slight waveform distortion.

The  $V_{RM}$  pin is the center of the reference ladder and should be bypassed to a quiet point in the ground plane with a 0.1  $\mu$ F capacitor. DO NOT leave this pin open and DO NOT load this pin with more than 10 $\mu$ A.

Figure 45. Driving the Reference to Force Desired Values Requires Driving with a Low Impedance Source

### THE ANALOG INPUT

The analog input of the ADC08B200 is a switch followed by an integrator. The input capacitance changes with the clock level, appearing as 3 pF when the clock is low, and 4 pF when the clock is high. The sampling nature of the analog input causes current spikes at the input that result in voltage spikes there. These spikes are normal and need not be eliminated. However, any amplifier used to drive the analog input must be able to settle within the clock high time. Using a single pole RC filter between the amplifier and the ADC input will minimize the effects of these transients on the driving amplifier. The cutoff frequency of this filter should be approximately the same as the ADC sample rate for Nyquist applications. Choose a capacitor value of 33 pF to 51 pF and a resistor value according to the formula

Copyright © 2007–2013, Texas Instruments Incorporated

$$R = \frac{1}{2 \cdot \pi \cdot (C + 6 \text{ pF}) \cdot f_S}$$

where

f<sub>S</sub> is the converter sample rate

(4)

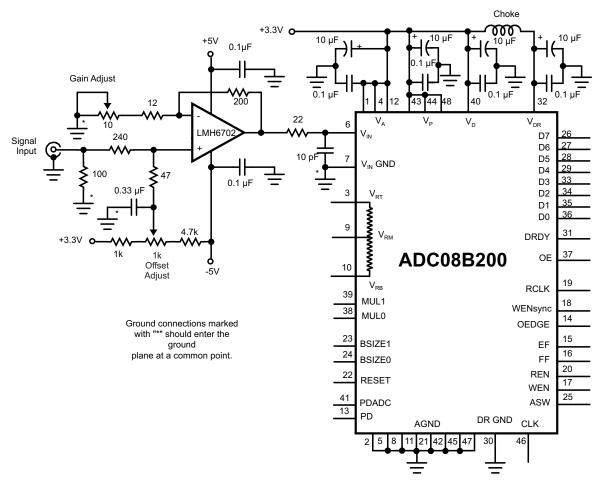

The added 6 pF in the formula above allows for the ADC input capacitance and a small board capacitance. For undersampling applications, eliminate the capacitor and chose a pole frequency of about 2 to 3 times the maximum input frequency, using the ADC input capacitance when the clock is high, plus trace capacitance, for the filter capacitor. The optimum time constant for this circuit depends not only upon the amplifier and ADC, but also upon the circuit layout and board material. The LMH6702 and the LMH6628 have been found to be good amplifiers to drive the ADC08B200.

Figure 46 shows an example of an input circuit using the LMH6702 at the ADC08B200 input. The input amplifier should incorporate some gain as most operational amplifiers exhibit better phase margin and transient response with gains above 2 or 3 than with unity gain. If an overall gain of less than 3 is required, attenuate the input and operate the amplifier at a higher gain, as indicated in Figure 46.

This will provide optimum SNR performance for Nyquist applications. Best THD performance is realized when the capacitor and resistor values are both zero, but this would compromise SNR and SINAD performance. Generally, the capacitor should not be added for undersampling applications.

The circuit of Figure 46 has both gain and offset adjustments. If you eliminate these adjustments normal circuit tolerances may result in signal clipping unless care is exercised in the worst case analysis of component tolerances and the input signal excursion is appropriately limited to account for the worst case conditions.

Full scale and offset adjustments may also be made by adjusting  $V_{RT}$  and  $V_{RB}$ , perhaps with the aid of a pair of a DACs or a dual DAC. Of course, this circuit may be implemented without provision for offset and gain adjustments, but component tolerances would require the planned use of less than the full dynamic range of the ADC.

One advantage of having access to the bottom of the reference ladder ( $V_{RB}$ ) is that the voltage at the analog input does not have to come to 0V to cause an output code of zero. If  $V_{RB}$  is set high enough, the negative supply on the amplifier driving the analog input may be at ground. How high  $V_{RB}$  needs to be set to allow this will depend upon the amplifier type and how close to its negative supply (or ground) the output can go while maintaining linearity. This might be 100mV to 150mV for a rail-to-rail output amplifier or 1 Volt for other amplifiers.

Figure 46. The Input Amplifier Should Incorporate Some Gain for Best Performance (see text)

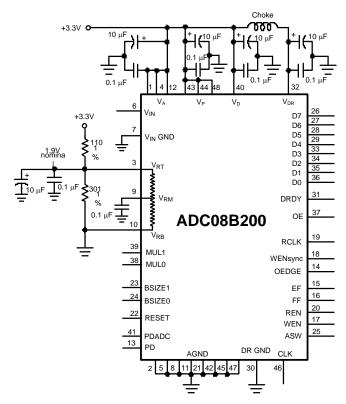

### POWER SUPPLY CONSIDERATIONS

A/D converters draw sufficient transient current to corrupt their own power supplies if not adequately bypassed. Generally, a 10  $\mu$ F tantalum or aluminum electrolytic capacitor should be provided for each of the four supplies and a 0.1  $\mu$ F ceramic chip capacitor placed within one centimeter of each converter power supply pin.

To further lower the inductance in series with the capacitors, mount the 0.1 µF capacitors on the same side of the board as the ADC and use 2 to 4 closely spaced through holes to connect the ground side of the capacitors to the ground plane. The through holes used to ground one side of these capacitors should not be used to connect anything else to ground. Leadless chip capacitors are preferred because they have low lead inductance.

While a single voltage source is recommended for the  $V_A$ ,  $V_D$  and  $V_P$  supplies of the ADC08B200, the  $V_A$  supply pins should be well isolated from the other supply pins to prevent any digital noise from being coupled into the analog portions of the ADC. A choke is recommended between the  $V_{DR}$  supply pin and the other supply pins with adequate bypass capacitors close to each supply pin, as shown in Figure 44, Figure 45 and Figure 46.