National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

### DS89C386 Twelve Channel CMOS Differential Line Receiver

#### **General Description**

The DS89C386 is a high speed twelve channel CMOS differential receiver that meets the requirements of TIA/EIA-422-B. The DS89C386 features low power dissipation of 240 mW typical.

Each TRI-STATE<sup>®</sup> enable, EN, allows the receiver output to be active or in a Hi-impedance off state. Each enable is common to only two receivers for flexibility and multiplexing of receiver outputs.

The receiver output (RO) is guaranteed to be High when the inputs are left open and unterminated. The receiver can detect signals as low and including  $\pm 200$  mV over the common mode range of  $\pm 7V$ . The receiver outputs (RO) are compatible with both TTL and CMOS levels.

#### **Features**

- Low power design—240 mW typical

- Meets TIA/EIA-422-B (RS-422)

- Receiver OPEN input failsafe feature

- Guaranteed AC parameters:

- Maximum receiver skew -4 ns

- Maximum transition time –9 ns

- High Output Drive Capability: ±6 mA

- Available in SSOP packaging:

- Requires 30% less PCB space than 3 DS34C86TMs

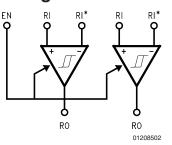

#### **Function Diagram**

1/6 of package

#### **Truth Table**

| Enable          | Inputs                    | Output |

|-----------------|---------------------------|--------|

| EN              | RI–RI*                    | RO     |

| L               | Х                         | Z      |

| Н               | ≥200 mV or OPEN†          | Н      |

| Н               | ≤ –200 mV                 | L      |

| Н               | +200  mV > and > -200  mV | Х      |

| +Not terminated | •                         |        |

Not terminated.

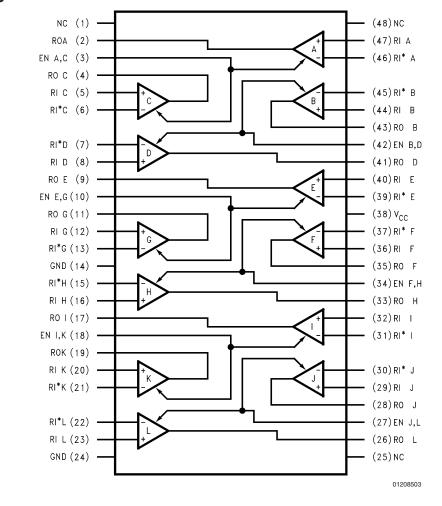

**Connection Diagram** 48L SSOP DS89C386 48 -NC NC • RO A -47 RI A EN A,C RI\* A 46 RO C• 45 - RI\* B RI C. RI B 44 RI\* C-43 -RO B RI\*D-42 EN B,D RID--RO D 41 RO E-40 -RIE - RI\*F EN E,G-10 39 RO G - 11 38 -v<sub>cc</sub> RIG-12 37 - RI\* F RI\*G - 13 36 GND - 14 35 - RO F RI\*H-15 34 -EN F,H 16 -RO H 33 RIH-RO I - 17 32 -RII EN I,K-18 31 - RI\* I RO K - 19 - RI\* .I 30 RI K — 20 29 -RIJ RI\*K -21 28 -RO J 22 -EN J.L RI\*L -27 RI L - 23 26 -ROL GND -24 25 NC 01208501 Order Number DS89C386TMEA See NS Package Number MS48A TRI-STATE® is a registered trademark of National Semiconductor Corporation. © 2004 National Semiconductor Corporation DS012085

#### Absolute Maximum Ratings (Notes 1,

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )               | –0.5 to 7V |

|-------------------------------------------------|------------|

| Input Common Mode Range (V <sub>CM</sub> )      | ±14V       |

| Differential Input Voltage (V <sub>DIFF</sub> ) | ±14V       |

| Enable Input Voltage (V <sub>IN)</sub>          | 7V         |

| Storage Temperature Range (T <sub>STG</sub> )   | −65°C to   |

|                                                 | +150°C     |

| Lead Temperature (Soldering 4 sec)              | 260°C      |

#### DC Electrical Characteristics (Note 3)

Maximum Power Dissipation at 25°C (Note 4)

| SSOP Package       | 1359 mW |

|--------------------|---------|

| Current Per Output | ±25 mA  |

This device does not meet 2000V ESD rating. (Note 5)

#### **Operating Conditions**

|                                               | Min  | Max  | Unit |

|-----------------------------------------------|------|------|------|

| Supply Voltage (V <sub>CC</sub> )             | 4.50 | 5.50 | V    |

| Operating Temperature Range (T <sub>A</sub> ) |      |      |      |

| DS89C386T                                     | -40  | +85  | °C   |

| Enable Input Rise or Fall Times               |      | 500  | ns   |

| Symbol            | Parameter                        | Conditions                               | Min  | Тур  | Max             | Units |

|-------------------|----------------------------------|------------------------------------------|------|------|-----------------|-------|

| V <sub>TH</sub>   | Differential Input Voltage       | $V_{OUT} = V_{OH} \text{ or } V_{OL}$    | -200 | ±35  | +200            | mV    |

|                   |                                  | $-7V < V_{CM} < +7V$                     |      |      |                 |       |

| V <sub>HYST</sub> | Input Hysteresis                 | $V_{CM} = 0V$                            |      | 70   |                 | mV    |

| R <sub>IN</sub>   | Input Resistance                 | $V_{IN} = -7V, +7V$                      | 5.0  | 6.8  | 10              | kΩ    |

|                   |                                  | (Other Input = GND)                      |      |      |                 |       |

| I <sub>IN</sub>   | Input Current                    | $V_{IN} = +10V$ , Other Input = GND      |      | +1.1 | +1.5            | mA    |

|                   | (Under Test)                     | $V_{IN} = -10V$ , Other Input = GND      |      | -2.0 | -2.5            | mA    |

| V <sub>OH</sub>   | High Level Output Voltage        | $V_{CC} = Min., V_{(DIFF)} = +1V$        | 3.8  | 4.2  |                 | V     |

|                   |                                  | $I_{OUT} = -6.0 \text{ mA}$              |      |      |                 |       |

| V <sub>OL</sub>   | Low Level Output Voltage         | $V_{CC} = Max., V_{(DIFF)} = -1V$        |      | 0.2  | 0.3             | V     |

|                   |                                  | I <sub>OUT</sub> = 6.0 mA                |      |      |                 |       |

| V <sub>IH</sub>   | Enable High Input Level Voltage  |                                          | 2.0  |      | V <sub>CC</sub> | V     |

| V <sub>IL</sub>   | Enable Low Input Level Voltage   |                                          | GND  |      | 0.8             | V     |

| I <sub>oz</sub>   | TRI-STATE Output Leakage Current | $V_{OUT} = V_{CC}$ or GND, EN = $V_{IL}$ |      | ±0.5 | ±5.0            | μA    |

| I <sub>I</sub>    | Enable Input Current             | $V_{IN} = V_{CC}$ or GND                 |      |      | ±1.0            | μA    |

| I <sub>cc</sub>   | Quiescent Power Supply Current   | $V_{CC} = Max., V_{(DIFF)} = +1V$        |      | 48   | 69              | mA    |

#### AC Electrical Characteristics (Note 3)

|--|

| Symbol              | Parameter         | Conditions             | Min | Тур | Max | Units |

|---------------------|-------------------|------------------------|-----|-----|-----|-------|

| t <sub>PLH</sub> ,  | Propagation Delay | C <sub>L</sub> = 50 pF |     |     |     |       |

| t <sub>PHL</sub>    | Input to Output   | $V_{DIFF} = 2.5V$      | 10  | 19  | 30  | ns    |

|                     |                   | $V_{CM} = 0V$          |     |     |     |       |

| t <sub>sk</sub>     | Skew              | C <sub>L</sub> = 50 pF |     |     |     |       |

|                     |                   | $V_{DIFF} = 2.5V$      | 0   | 2   | 4   | ns    |

|                     |                   | $V_{CM} = 0V$          |     |     |     |       |

| t <sub>RISE</sub> , | Output Rise and   | C <sub>L</sub> = 50 pF |     |     |     |       |

| t <sub>FALL</sub>   | Fall Times        | $V_{DIFF} = 2.5V$      |     | 4   | 9   | ns    |

|                     |                   | $V_{CM} = 0V$          |     |     |     |       |

| t <sub>PLZ</sub> ,  | Propagation Delay | C <sub>L</sub> = 50 pF |     |     |     |       |

| t <sub>PHZ</sub>    | ENABLE to Output  | $R_L = 1000\Omega$     |     | 13  | 18  | ns    |

|                     |                   | $V_{DIFF} = 2.5V$      |     |     |     |       |

| t <sub>PZL</sub> ,  | Propagation Delay | C <sub>L</sub> = 50 pF |     |     |     |       |

| t <sub>PZH</sub>    | ENABLE to Output  | $R_L = 1000\Omega$     |     | 13  | 21  | ns    |

|                     |                   | $V_{DIFF} = 2.5V$      |     |     |     |       |

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified, all voltages are referenced to ground.

Note 3: Unless otherwise specified, Min/Max limits apply across the operating temperature range. All typicals are given for V<sub>CC</sub> = 5V and T<sub>A</sub> = 25°C.

Note 4: Ratings apply to ambient temperature at 25°C. Above this temperature derate SSOP (MEA) Package 10.9 mW/°C.

Note 5: ESD Rating: HEM (1.5 kΩ, 100 pF)

Inputs  $\geq 2000V$

Outputs ≥ 1000V

EIAJ (0Ω, 200 pF)

All Pins ≥ 350V

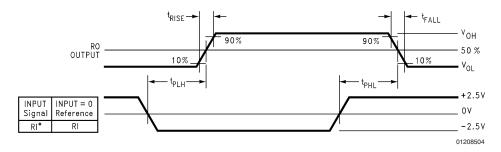

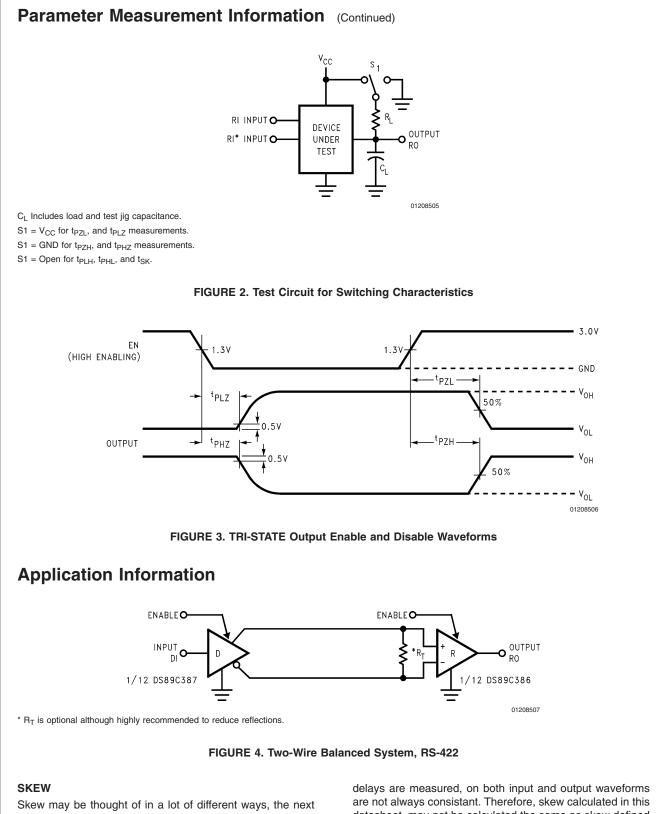

#### **Parameter Measurement Information**

FIGURE 1. Propagation Delays

Skew may be thought of in a lot of different ways, the next few paragraphs should clarify what is represented by  $t_{SK}$  in this datasheet and how it is determined. Skew, as used in this databook, is the absolute value of a mathematical difference between two propagation delays. This is commonly accepted throughout the semiconductor industry. However, there is no standardized method of measuring propagation delay, from which skew is calculated, of differential line receivers. Elucidating, the voltage level, at which propagation

delays are measured, on both input and output waveforms are not always consistant. Therefore, skew calculated in this datasheet, may not be calculated the same as skew defined in another. This is important to remember whenever making a skew comparison.

Skew may be calculated for the DS89C386, from many different propagation delay measurements. They may be classified into two categories, single-ended and differential. Single-ended skew is calculated from  $t_{\rm PHL}$  and  $t_{\rm PLH}$  propa-

DS89C386

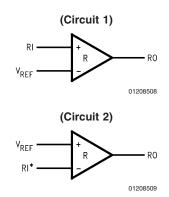

#### Application Information (Continued)

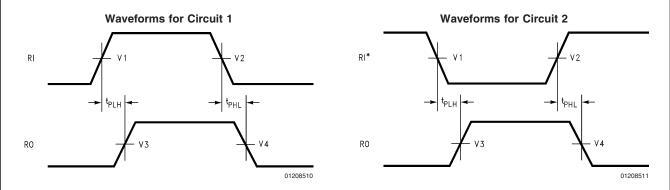

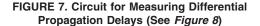

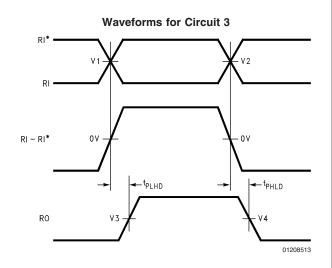

skew is calculated from  $t_{PHLD}$  and  $t_{PLHD}$  differential propagation delay measurements (see *Figures 7, 8*).

gation delay measurements (see Figures 5, 6). Differential

FIGURE 6. Propagation Delay Waveforms for Circuit 1 and Circuit 2 (See Figure 5)

In *Figure 6*, VX, where X is a number, is the waveform voltage level at which the propagation delay measurement either starts or stops. Furthermore, V1 and V2 are normally identical. The same is true for V3 and V4. However, as mentioned before, these levels are not standardized and may vary, even with similar devices from other companies. Also note,  $V_{\mathsf{REF}}$  in *Figure 1* should equal V1 and V2 in *Figure 6*.

The single-ended skew provides information about the pulse width distortion of the output waveform. The lower the skew, the less the output waveform will be distorted. For best case, skew would be zero, and the output duty cycle would be 50%, assuming the input has a 50% duty cycle.

#### FIGURE 8. Propagation Delay Waveforms for Circuit 3 (see Figure 7)

For differential propagation delays, V1 may not equal V2. Furthermore, the crossing point of RI and RI\* corresponds to zero volts on the differential waveform. (See middle waveform in *Figure 8*.) This is true whether V1 equals V2 or not. However, if V1 and V2 are specified voltages, then V1 and

#### Application Information (Continued)

V2 are less likely to be equal to the crossing point voltage. Thus, the differential propagation delays will not be measured from zero volts on the differential waveform.

The differential skew also provides information about the pulse width distortion of the output waveform relative to the differential input waveform. The higher the skew, the greater the distortion of the output waveform. Assuming the differential input has a 50% duty cycle, the output will have a 50% duty cycle if skew equals zero and less than a 50% duty cycle if skew is greater than zero.

Only  $t_{SK}$  is specified in this datasheet for the DS89C386.  $t_{SK}$  is measured single-endedly but corresponds to differential skew. Because, for single-ended skew, when  $V_{\mathsf{REF}}$  equals V1 and V2,  $t_{\mathsf{PHL}}$  equals  $t_{\mathsf{PHLD}}$  when  $t_{\mathsf{PHLD}}$  is measured from the crossing point.

More information can be calculated from the propagation delays. The channel to channel and device to device skew may be calculated in addition to the types of skew mentioned previously. These parameters provide timing performance information beneficial when designing. The channel to channel skew is calculated from the variation in propagation delay from receiver to receiver within one package. The device to device skew is calculated from the variation in propagation delay from one DS89C386 to another DS89C386.

For the DS89C386, the maximum channel to channel skew is 20 ns (t\_p max—t\_p min) where t\_p is the low to high or high

#### **Typical Performance Characteristics**

| TABLE | 1. | DS89C386 | Skew | Table |

|-------|----|----------|------|-------|

|-------|----|----------|------|-------|

| Parameter                 | Min | Тур | Max | Units |

|---------------------------|-----|-----|-----|-------|

| t <sub>SK</sub> (diff.)   | 0   | 2   | 4   | ns    |

| t <sub>sk</sub> (channel) | 0   |     | 20  | ns    |

| t <sub>SK</sub> (device)  | 0   |     | 20  | ns    |

Note  $t_{SK}$  (diff.) in *Table 1* is the same as  $t_{SK}$  in the datasheet. Also,  $t_{SK}$  (channel) and  $t_{SK}$  (device) are calculations, but are guaranteed by the propagation delay tests. Both  $t_{SK}$  (channel) and  $t_{SK}$  (device) would normally be tighter whenever specified from characterization data.

The information in this section of the datasheet is to help clarify how skew is defined in this datasheet. This should help when designing the DS89C386 into most applications.

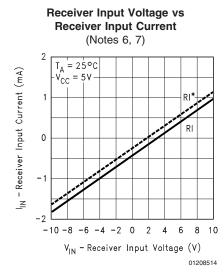

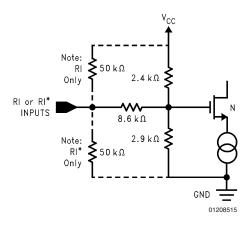

Note 6: The DS89C386 is V.11 compatible. I<sub>IN</sub> (RI input) is not  $\ge$  0 when V<sub>IN</sub>= 3V due to internal failsafe bias resistors (see *Figure 6*). See ITU V.11 for complete conditions.

Note 7: Failsafe (open inputs) is maintained over entire common mode range and operating range ±10V.

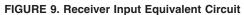

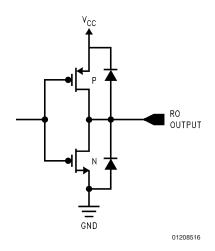

### DS89C386 Equivalent Input/Output Circuits

FIGURE 10. Receiver Output Equivalent Circuit

FIGURE 11. Receiver Enable Equivalent Circuit

| Pin Descriptions TABLE 2. Device Pin Names and Descriptions |                 |                                         |  |  |  |

|-------------------------------------------------------------|-----------------|-----------------------------------------|--|--|--|

|                                                             |                 |                                         |  |  |  |

| 2, 4, 9, 11, 17, 19, 26,                                    | RO              | TTL/CMOS Compatible Receiver Output Pin |  |  |  |

| 28, 33, 35, 41, 43                                          |                 |                                         |  |  |  |

| 5, 8, 12, 16, 20, 23, 29,                                   | RI              | Non-Inverting Signal Receiver Input Pin |  |  |  |

| 32, 36, 40, 44, 47                                          |                 |                                         |  |  |  |

| 6, 7, 13, 15, 21, 22, 30,                                   | RI*             | Inverting Signal Receiver Input Pin     |  |  |  |

| 31, 37, 39, 45, 46                                          |                 |                                         |  |  |  |

| 3, 10, 18, 27, 34, 42                                       | EN              | Active High Dual Receiver Enabling Pin  |  |  |  |

| 38                                                          | V <sub>cc</sub> | Positive Power Supply Pin +5 ±10%       |  |  |  |

| 14, 24                                                      | GND             | Device Ground Pin                       |  |  |  |

| 1, 25, 48                                                   | NC              | Unused Pin (NOT CONNECTED)              |  |  |  |