# 82750PB PIXEL PROCESSOR

- 25 MHz Clock with Single Cycle Execution

- Zero Branch Delay

- **Wide instruction Word Processor**

- 512 x 48-Bit instruction RAM

- 512 x 16-Bit Data RAM

- Two Internal 16-Bit Buses

- ALU with Dual-Add-With-Saturation Mode

- Variable Length Sequence Decoder

- Pixel Interpolator

- High Performance Memory Interface

- --- 32-Bit Memory Data Bus

- 50 MBytes per Second Maximum

- 25 MBytes per Second with Standard VRAMs or DRAMs

- **16 General-Purpose Registers**

- 4 Gbyte Linear Address Space

- 132-Pin PQFP

- Compatible with the 82750PA

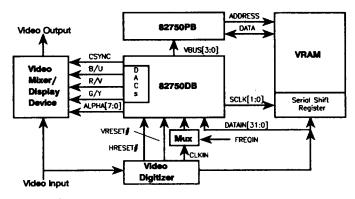

Intel's 82750PB is a 25 MHz wide instruction processor that generates and manipulates pixels. When paired with its companion chip, the 82750DB, and used to implement a DVI® Technology video subsystem, the 82750PB provides real time (30 images/sec) pixel processing, real time video compression, interactive motion video playback and real time video effects.

Real time pixel manipulations, including 30 images/sec video compression, are supported by the 25 MHz instruction rate. On-chip instruction RAM provides programmability for execution of a wide range of algorithms that support motion video decompression, text, and 2D and 3D graphics. Inner loops are optimized with the integration of sixteen 16-bit quad ported registers, on-chip DRAM, and two loop counters that provide zero delay two-way branching "free" in any instruction. Two, 16-bit internal buses enable two parallel register transfers on each 82750PB instruction, contributing to the real time performance of the video processing. Another feature that adds to the processing power of the 82750PB is the 16-bit ALU, which includes an 8-bit dual-add-with-saturate operation critical for pixel arithmetic. Other specialized features for pixel processing include a 2D pixel interpolator for image processing functions and a variable length sequence decoder for decoding compressed data.

The 82750PB is implemented using Intel's low-power CHMOS IV Technology and is packaged in a 132-lead space-saving, plastic quad flat pack (PQFP) package.

82750PB Subsystem Diagram

240854-1

October 1993 Order Number: 240854-005

1-1

# 82750PB Pixel Processor

| CONTENTS PAGE                   | CONTENTS PAGE                           |

|---------------------------------|-----------------------------------------|

| 1.0 82750PB PIN DESCRIPTION 1-5 | VRAM Pointers 1-30                      |

| Pinout                          | Shadow Copy 1-30                        |

| Quick Pin Reference             | Host Interface 1-3                      |

|                                 | Host Register Access 1-33               |

| <b>2.0 ARCHITECTURE</b>         | Host VRAM Access 1-33                   |

| Overview 1-12                   | Host External Access 1-33               |

| Registers1-12                   | Host Register Address Mapping 1-33      |

| ALU 1-13                        | Initializing the 82750PB 1-40           |

| Barrel Shifter 1-14             | Performance Monitoring 1-4              |

| Data RAM 1-14                   | Host/VRAM Timing Diagrams 1-4           |

| Loop Counters 1-14              |                                         |

| Microcode RAM 1-15              | 4.0 MICROCODE INSTRUCTION FORMAT1-40    |

| Horizontal Line Counter 1-16    | Overview 1-40                           |

| Field Counter 1-16              | Instruction Sequencing 1-4              |

| Input FIFOs 1-16                | Instruction Word Field Descriptions 1-4 |

| Output FIFOs 1-17               | NADDR—Next instruction Address          |

| Statistical Decoder 1-18        | Field 1-40                              |

| Pixel Interpolator 1-23         | CFSEL—Condition Flag Select             |

| Mode Select 1-24                | Field 1-40                              |

| Reset 1-24                      | ASRC—A Bus Source Select Field1-4       |

| Pairing 1-24                    | ADST—A Bus Destination Select           |

| Phase 1-24                      | Field                                   |

| Pipelining1-24                  | BSRC—B Bus Source Select                |

| Reserved 1-25                   | Field 1-4                               |

| Signature Register 1-25         | BDST—B Bus Destination Select           |

| Display Format Registers 1-25   | Field 1-4                               |

|                                 | CNT—Decrement Loop Counter Bit          |

| 3.0 HARDWARE INTERFACE 1-26     | LIT—Literal Select Bit1-4               |

| VRAM Interface1-26              | SHFT—Shift Control Field 1-4            |

| VRAM Accesses1-27               | ALUSS—ALU Source Select Bits 1-4        |

| Fast VRAM Cycles1-28            | ALUOP—ALU Operation Code                |

| VBUS Codes                      | Field1-4                                |

| Priority 1-29                   | LC—Loop Counter Select Bit 1-4          |

# 82750PB Pixel Processor

| CONTENTS                                        | PAGE  | CONTE                    | <b>NTS</b> PAG                                                          | ЗE            |

|-------------------------------------------------|-------|--------------------------|-------------------------------------------------------------------------|---------------|

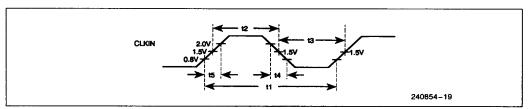

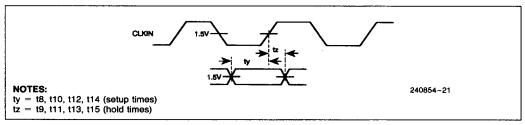

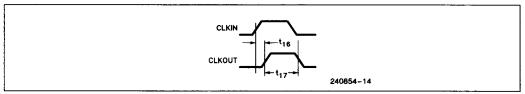

| 5.0 ELECTRICAL DATA                             | 1,53  | Figure 5-1.              | Clock Waveforms1-                                                       | -55           |

| DC Characteristics                              |       | Figure 5-2.              | Output Waveforms 1-                                                     | -55           |

| AC Characteristics                              |       | •                        | Input Waveforms 1-                                                      |               |

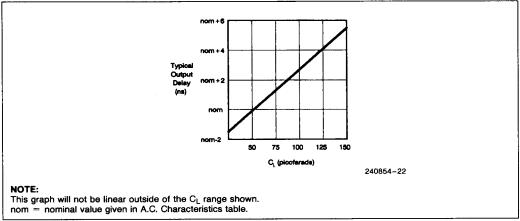

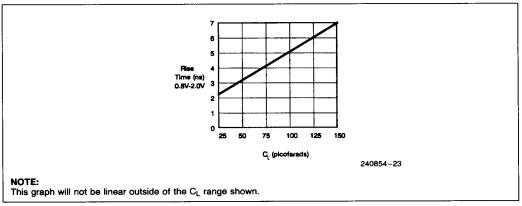

| Output Delay and Rise Time Versus               | 1 0-1 | Figure 5-4.              | CLKOUT Waveforms 1-                                                     | -55           |

| Load Capacitance                                | 1-56  | Figure 5-5.              | Typical Output Valid Delay                                              |               |

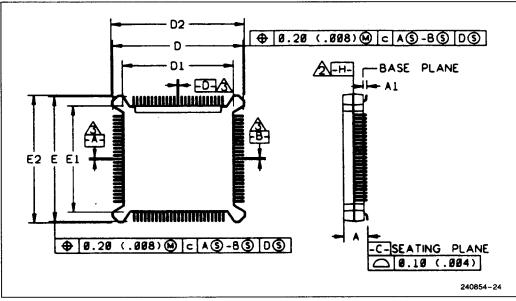

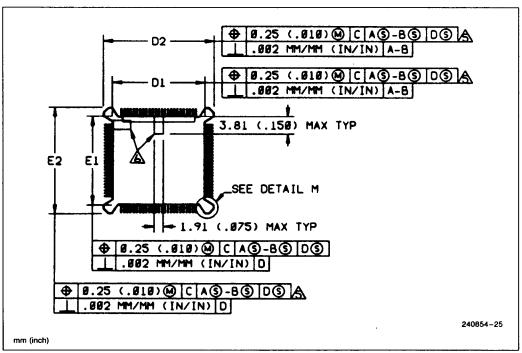

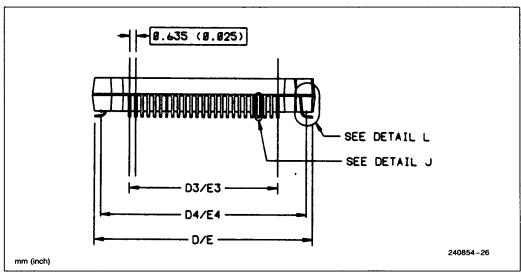

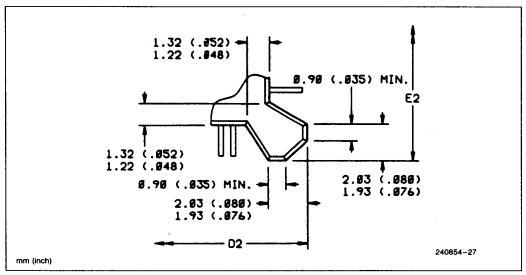

| 6.0 MECHANICAL DATA                             | 1-57  |                          | Versus Load Capacitance under Worst Case                                |               |

| Packaging Outlines and Dimensions               | 1-57  |                          | Conditions 1-                                                           | -56           |

| Package Thermal Specifications                  |       | Figure 5-6.              | Typical Output Rise Time<br>Versus Load Capacitance<br>under Worst Case |               |

| FIGURES                                         |       |                          | Conditions                                                              | -56           |

| Figure 1-1. 82750PB Pinout                      | 1-5   | Figure 6-1.              | Principal Dimensions of the                                             |               |

| Figure 1-2. 82750PB Functional Signal Groupings |       |                          | 82750PB in the 132-Lead PQFP Package                                    | -58           |

| Figure 2-1. 82750PB Block Diagram               |       | Figure 6-2.              | Detailed Dimensions of the 82750PB in the 132-Lead                      |               |

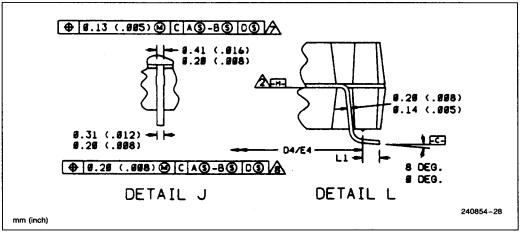

| Figure 2-2. Input FIFO Control Register         | 1-16  |                          | PQFP—Molding Details 1                                                  | -59           |

| Figure 2-3. Output FIFO Control Register        |       | Figure 6-3.              | Detailed Dimensions of the 82750PB in the 132-Lead                      |               |

| Figure 2-4. Statistical Decode CONTRO           |       |                          | PQFP—Terminal Details 1                                                 | -59           |

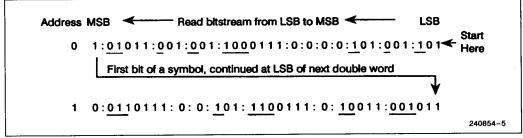

| Figure 2-5. VRAM Bitstream Decoding Addresses   |       | Figure 6-4.              | . 132-Lead PQFP Mechanical Package Detail—Protective Bumper             | -60           |

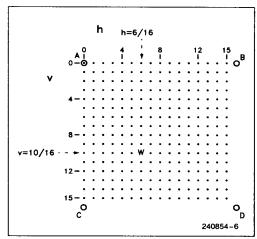

| Figure 2-6. Pixel Interpolation                 |       | Figure 6-5               | . 132-Lead PQFP Mechanical                                              | -             |

| Figure 2-7. Sequential-2D Pixel Interpolation   |       | , <b>,ga</b> , o o o.    | Package Detail—Typical<br>Lead1                                         | -60           |

| Figure 2-8. Pixel Interpolator Control          |       | TABLES                   |                                                                         |               |

| Register                                        |       | Table 1-1.               | Pin Cross Reference by Pin                                              |               |

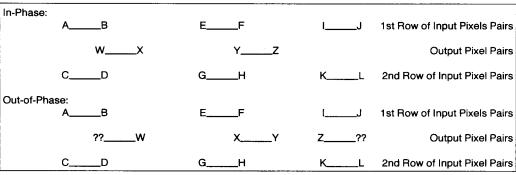

| Figure 2-9. Pixel Pair Phases                   |       |                          | Name                                                                    | 1-6           |

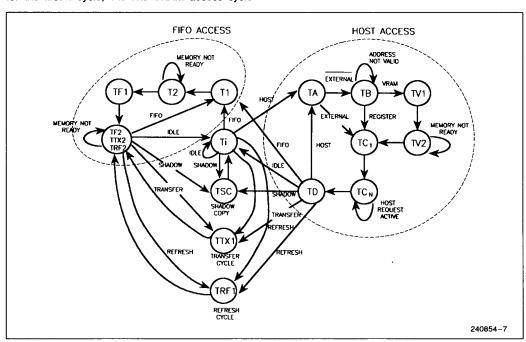

| Figure 3-1. Access State Diagram                |       | Table 1-2.               |                                                                         | . 7           |

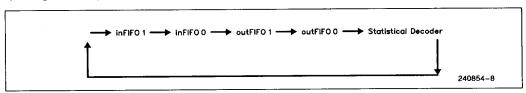

| Figure 3-2. Cyclic Ordering of FIFOs            |       | Table 1.0                | Location Pin Descriptions                                               |               |

| Figure 3-3. VRAM Addressing                     | 1-30  | Table 1-3.<br>Table 1-4. | ·                                                                       |               |

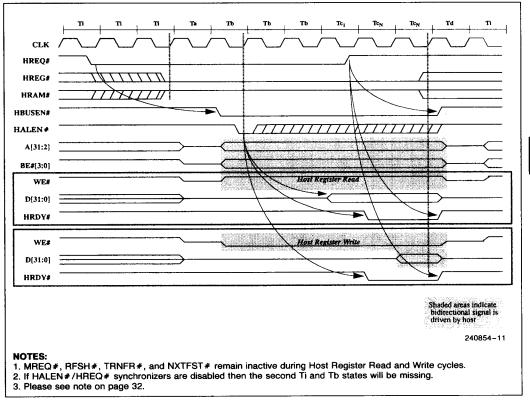

| Figure 3-4. VRAM Read and Write Cycles          | 1-42  | Table 1-4.               | ·                                                                       |               |

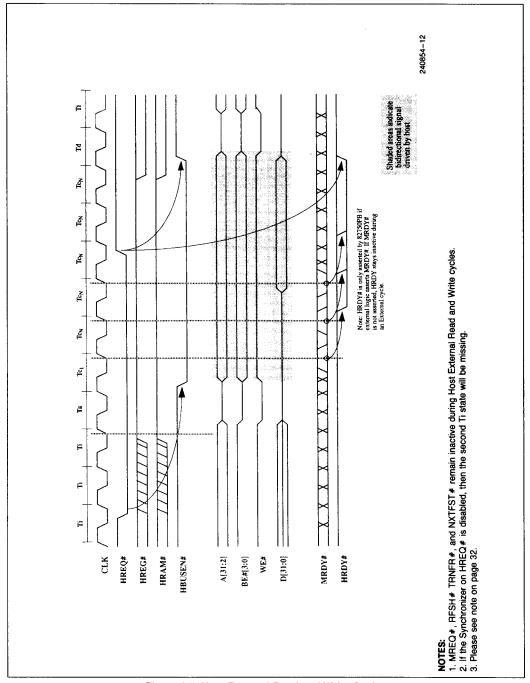

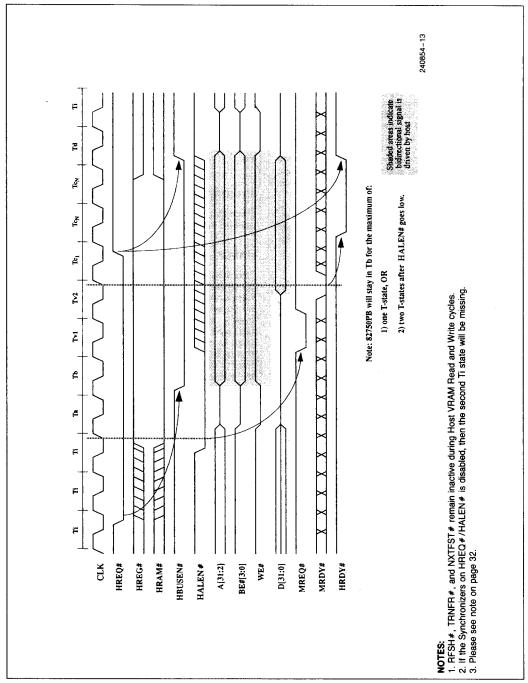

| Figure 3-5. VRAM Transfer and Refres            |       | Table 1-6.               | Input/Output Pins1                                                      |               |

| Cycles                                          |       | Table 2-1.               | •                                                                       | - , ,         |

| Figure 3-6. Host Register Read and Wr           | ite   | Tubio 2 1.               | Register1                                                               | -13           |

| Cycles Figure 3-7. Host VRAM Read and Write     |       | Table 2-2.               | ALU Opcodes 1                                                           | -13           |

| Cycles                                          | 1-44  | Table 2-3.               | •                                                                       | -17           |

| Figure 3-8. Host External Cycles                |       | Table 2-4.               | Sample Code Description Table                                           | 1.40          |

| Figure 4-1. Literal Field Mapping onto a        |       | Table 2-5.               |                                                                         |               |

| Bus                                             | 1-48  | Table 2-5.               |                                                                         | -15           |

| Figure 4-2. 82750PB Instruction Word Format     | 1-51  | 1 abie 2-0.              | Values1                                                                 | I- <b>1</b> 9 |

# 82750PB Pixel Processor

| CONTEN                   | NTS                                               | PAGE | CONTE       | NTS F                                               | PAGE   |

|--------------------------|---------------------------------------------------|------|-------------|-----------------------------------------------------|--------|

| Table 2-7.               | END Flag Decoded Values                           | 1-20 | Table 3-12. | Bit Assignments for                                 |        |

| Table 2-8.               | Packed 3-Bit Field Decoded Values                 | 1-20 |             | PROCESSOR STATUS Register                           | . 1-37 |

| Table 2-9.               | VRAM Bitstream Decoded Values                     | 1-22 | Table 3-13. | 82750PB A<br>Source/Destination Register<br>Mapping | . 1-38 |

| Table 2-10.              | Decoding Symbols                                  | 1-22 | Table 3-14. | 82750PB B                                           |        |

| Table 2-11.              | Mode Select Operating Modes                       | 1-24 |             | Source/Destination Register Mapping                 | . 1-39 |

| Table 2-12.              | Pipelining Delay for<br>Sequential-2D NON-PAIR    |      | Table 3-15. | VRAM Pointer RAM Mapping                            | . 1-40 |

| Table 2-13.              | Mode                                              |      | Table 4-1.  | Mirocode Next Instruction Selection                 | . 1-46 |

| Table 2-14.              | Display Registers                                 | 1-26 | Table 4-2.  | PC Load Example                                     | . 1-47 |

| Table 3-1.<br>Table 3-2. | VRAM Interface Signals 82750PB VRAM Access        | 1-26 | Table 4-3.  | Condition Flag Select Field Assignments             | . 1-47 |

|                          | States                                            |      | Table 4-4.  | SHIFT Control Field Coding                          | . 1-48 |

| Table 3-3.               | Priority of VRAM Operations                       |      | Table 4-5.  | 82750PB Source/Destination Coding                   |        |

| Table 3-5.               |                                                   | 1-31 | Table 5-1.  | Absolute Maximum Requirements                       | . 1-53 |

| Table 3-6.               | Host, VRAM and External Device Signals            | 1-31 | Table 5-2.  | DC Characteristics                                  | . 1-53 |

| Table 3-7.               | 82750PB Host Transaction States                   | 1-32 | Table 5-3.  | AC Characteristics at 25 MHz                        | . 1-54 |

| Table 3-8.               | Host Cycle Types                                  | 1-32 | Table 6-1.  | PQFP Symbol List                                    | . 1-57 |

| Table 3-9.               | Host Address Mapping                              | 1-34 | Table 6-2.  | Intel Case Outline Drawings for PQFP at 0.025-Inch  |        |

| Table 3-10.              | Bit Assignments for Microcode Processor           |      |             | Pitch                                               | . 1-58 |

| <b>T</b> 11 044          | CONTROL Register                                  | 1-35 | Table 6-3.  | Thermal Resistances (°C/W)                          | . 1-62 |

| 1 able 3-11.             | Bit Assignments for<br>INTERRUPT FLAG<br>Register | 1-36 | Table 6-4.  | Maximum T <sub>A</sub> at Various<br>Airflows       | . 1-62 |

# 1.0 82750PB PIN DESCRIPTION

#### **Pinout** 117 115 113 023 VCC 028 VCC 028 030 VSS VSS A31 A29 VCC A27 A25 A24 A26 VCC VSS D27 D29 D31 VCC CLKOUT A30 vss 0 O vss 0 vcc O vcc 2 97 A22 0 O 021 3 0 96 A21 O 020 ō 95 A20 Ö **VS**S O 018 A19 0 7 O D17 A1B 0 O 016 0 VCC O D15 90 A17 0 O vss 10 Ö VSS 11 ō A16 12 A15 0 13 O D12 0 A14 0 011 82750PB Pinout 14 0 15 O 810 TOP VIEW 0 A12 O 09 16 Ö A11 17 O vss VCC 0 18 Ō A10 19 0 20 0 21 O vss 0 22 77 0 23 O 04 VSS 0 76 24 O 03 0 75 25 0 26 0 27 0 01 72 A3 0 28 0 00 0 29 O vss 70 O HINT# 30 0 MERCYA TEST O HALTE 31 0 32 O vss VSS VBUS[3] VBUS[2:0] HALEN VSS VCC HREG! BE2! BEO! VSS VSS | BES# | BES# | VCC | CLKIN| WE# | VCC | 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66

Figure 1-1. 82750PB Pinout

240854-2

Table 1-1. Pin Cross Reference by Pin Name

| Pin<br>Name | Location |

|-------------|----------|

| A2          | 71       |

| A3          | 72       |

| A4          | 73       |

| A5          | 74       |

| A6          | 77       |

| A7          | 78       |

| A8          | 79       |

| A9          | 80       |

| A10         | 81       |

| A11         | 83       |

| A12         | 84       |

| A13         | 85       |

| A14         | 86       |

| A15         | 87       |

| A16         | 88       |

| A17         | 90       |

| A18         | 92       |

| A19         | 93       |

| A20         | 95       |

| A21         | 96       |

| A22         | 97       |

| A23         | 102      |

| A24         | 103      |

| A25         | 105      |

| A26         | 106      |

| A27         | 107      |

| A28         | 110      |

| A29         | 111      |

| A30         | 112      |

| A31         | 113      |

| BEO#        | 44       |

| BE1#        | 43       |

| BE2#        | 42       |

| Pin<br>Name | Location |

|-------------|----------|

| BE3#        | 41       |

| CLKIN       | 47       |

| CLKOUT      | 114      |

| D0          | 28       |

| D1          | 27       |

| D2          | 26       |

| D3          | 24       |

| D4          | 23       |

| D5          | 22       |

| D6          | 20       |

| D7          | 19       |

| D8          | 18       |

| D9          | 16       |

| D10         | 15       |

| D11         | 14       |

| D12         | 13       |

| D13         | 12       |

| D14         | 11       |

| D15         | 9        |

| D16         | 8        |

| D17         | 7        |

| D18         | 6 '      |

| D19         | 5        |

| D20         | 4        |

| D21         | 3        |

| D22         | 130      |

| D23         | 129      |

| D24         | 128      |

| D25         | 126      |

| `D26        | 125      |

| D27         | 122      |

| D28         | 121      |

| D29         | 120      |

| Location |

|----------|

| 119      |

| 118      |

| 55       |

| 31       |

| 36       |

| 30       |

| 58       |

| 38       |

| 40       |

| 56       |

| 60       |

| 59       |

| 61       |

| 70       |

| 63       |

| 62       |

| 69       |

| 37       |

| 54       |

| 53       |

| 52       |

| 50       |

| 2        |

| 33<br>35 |

| 35<br>45 |

| 45<br>51 |

| 51<br>65 |

| 67       |

| 75       |

| 82       |

| 91       |

| 98       |

|          |

| Pin<br>Name     | Location |

|-----------------|----------|

| V <sub>CC</sub> | 100      |

| Vcc             | 104      |

| Vcc             | 109      |

| Vcc             | 116      |

| Vcc             | 123      |

| Vcc             | 127      |

| Vcc             | 132      |

| Vss             | 1 1      |

| VSS             | 32       |

| VSS             | 34       |

| $V_{SS}$        | 39       |

| $V_{SS}$        | 48       |

| $V_{SS}$        | 57       |

| V <sub>SS</sub> | 66       |

| V <sub>SS</sub> | 68       |

| V <sub>SS</sub> | 76       |

| $V_{SS}$        | 89       |

| $V_{SS}$        | 94       |

| $V_{SS}$        | 99       |

| $V_{SS}$        | 101      |

| $V_{SS}$        | 108      |

| $V_{SS}$        | 115      |

| V <sub>SS</sub> | 117      |

| V <sub>SS</sub> | 124      |

| Vss             | 131      |

| V <sub>SS</sub> | 10       |

| VSS             | 17       |

| V <sub>SS</sub> | 21       |

| V <sub>SS</sub> | 25       |

| V <sub>SS</sub> | 29       |

| V <sub>SS</sub> | 46       |

| V <sub>SS</sub> | 64       |

| WE#             | 49       |

Table 1-2. Pin Cross Reference by Location

| Location | Pin<br>Name                        |  |

|----------|------------------------------------|--|

| 1        | V <sub>SS</sub>                    |  |

| 2        | Vcc                                |  |

| 3        | D21                                |  |

| 4        | D20                                |  |

| 5        | D19                                |  |

| 6        | D18                                |  |

| 7        | D17                                |  |

| 8        | D16                                |  |

| 9        | D15                                |  |

| 10       | Vss                                |  |

| 11       | D14                                |  |

| 12       | D13                                |  |

| 13       | D12                                |  |

| 14       | D11                                |  |

| 15       | D10                                |  |

| 16       | D9                                 |  |

| 17       | Vss                                |  |

| 18       | D8                                 |  |

| 19       | D7                                 |  |

| 20       | D6                                 |  |

| 21       | Vss                                |  |

| 22       | D5                                 |  |

| 23       | D4                                 |  |

| 24       | D3                                 |  |

| 25       | Vss                                |  |

| 26       | D2                                 |  |

| 27       | D1                                 |  |

| 28       | D0                                 |  |

| 29<br>20 | V <sub>SS</sub>                    |  |

| 30<br>31 | HALT#                              |  |

| 31<br>32 |                                    |  |

| 32       | V <sub>SS</sub><br>V <sub>CC</sub> |  |

|   | Table 1  | Z. 1 III 01000 I |

|---|----------|------------------|

|   | Location | Pin<br>Name      |

|   | 34       | V <sub>SS</sub>  |

| ĺ | 35       | V <sub>CC</sub>  |

|   | 36       | HBUSEN#          |

| ı | 37       | TRNFR#           |

|   | 38       | HRDY#            |

| - | 39       | V <sub>SS</sub>  |

|   | 40       | HREG#            |

| - | 41       | BE3#             |

|   | 42       | BE2#             |

| Į | 43       | BE1#             |

| 1 | 44       | BE0#             |

|   | 45       | Vcc              |

| 1 | 46       | V <sub>SS</sub>  |

|   | 47       | CLKIN            |

| Ì | 48       | V <sub>SS</sub>  |

|   | 49       | WE#              |

|   | 50       | VBUS[3]          |

|   | 51       | Vcc              |

| - | 52       | VBUS[2]          |

|   | 53       | VBUS[1]          |

|   | 54       | VBUS[0]          |

|   | 55       | HALEN#           |

|   | 56       | HREQ#            |

|   | 57       | V <sub>SS</sub>  |

|   | 58<br>59 | MREQ#            |

|   |          | MRDY#            |

|   | 60<br>61 | NXTFST#          |

|   | 62       | RFSH#            |

|   | 63       | RESET#           |

|   | 64       | V <sub>SS</sub>  |

|   | 65       | VSS              |

|   | 66       | VSS              |

| j |          |                  |

| Location | Pin<br>Name     |

|----------|-----------------|

| 67       | Vcc             |

| 68       | VSS             |

| 69       | TEST#           |

| 70       | PMFRZ#          |

| 71       | A2              |

| 72       | A3              |

| 73       | A4              |

| 74       | A5              |

| 75       | Vcc             |

| 76       | VSS             |

| 77       | A6              |

| 78       | A7              |

| 79       | A8              |

| 80       | A9              |

| 81       | A10             |

| 82       | Vcc             |

| 83       | A11             |

| 84       | A12             |

| 85       | A13             |

| 86       | A14             |

| 87       | A15             |

| 88       | A16             |

| 89       | V <sub>SS</sub> |

| 90       | A17             |

| 91       | Vcc             |

| 92       | A18             |

| 93       | A19             |

| 94       | V <sub>SS</sub> |

| 95       | A20             |

| 96       | A21             |

| 97       | A22             |

| 98       | V <sub>CC</sub> |

| 99       | Vss             |

| Location | Pin<br>Name     |

|----------|-----------------|

| 100      | V <sub>CC</sub> |

| 101      | Vss             |

| 102      | A23             |

| 103      | A24             |

| 104      | Vcc             |

| 105      | A25             |

| 106      | A26             |

| 107      | A27             |

| 108      | V <sub>SS</sub> |

| 109      | Vcc             |

| 110      | A28             |

| 111      | A29             |

| 112      | A30             |

| 113      | A31             |

| 114      | CLKOUT          |

| 115      | V <sub>SS</sub> |

| 116      | Vcc             |

| 117      | V <sub>SS</sub> |

| 118      | D31             |

| 119      | D30             |

| 120      | D29             |

| 121      | D28             |

| 122      | D27             |

| 123      | Vcc             |

| 124      | Vss             |

| 125      | D26             |

| 126      | D25             |

| 127      | V <sub>CC</sub> |

| 128      | D24             |

| 129      | D23             |

| 130      | D22             |

| 131      | Vss             |

| 132      | Vcc             |

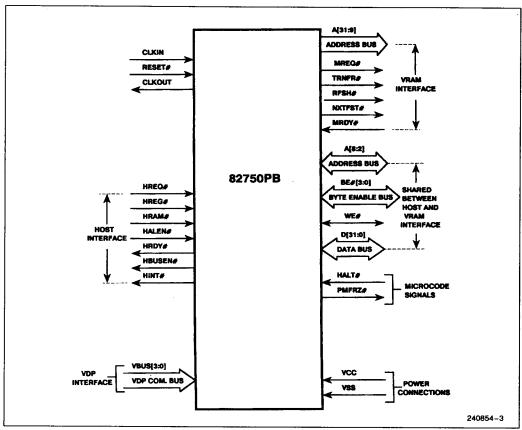

Figure 1-2. 82750PB Functional Signal Groupings

# **Quick Pin Reference**

Table 1-3 provides descriptions of 82750PB pins.

Table 1-3. Pin Descriptions

| Symbol            | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKIN             | ı     | CLKIN is a 1X CLOCK INPUT that provides the fundamental timing for the 82750PB. One cycle of CLKIN is denoted as one T-cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET#            | ı     | The 82750PB is reset and initialized by holding this signal active for at least ten T-cycles. Refer to Initializing the 82750PB Section in Chapter 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HREQ#             | _     | The <b>HOST REQUEST</b> signal is a request from the host CPU to perform a read or write access to either registers on the 82750PB, an external device, or to VRAM shared by the 82750PB and the host. The type of access that is requested is determined by the host access definition signals: HREG#, HRAM#, and WE#.                                                                                                                                                                                                                                                                                                                         |

| HREG,#<br>HRAM#   |       | The <b>HOST REGISTER</b> and <b>HOST RAM</b> signals, when validated by HREQ#, are used to define three host access cycles. HRAM# active indicates the host is requesting a VRAM read or write cycle. HREG# active indicates that the host is requesting a 82750PB register read or register write cycle. When both signals are inactive, a host external cycle is requested.                                                                                                                                                                                                                                                                   |

| HBUSEN#           | 0     | HOST BUS ENABLE is asserted by the 82750PB at the start of a host access to indicate that the 82750PB Address and Data buses (A[31:2], BE# [3:0], and D[31:0]) have been tri-stated. This allows the host to drive the same buses either for accessing shared VRAM or the 82750PB internal registers.                                                                                                                                                                                                                                                                                                                                           |

| HALEN#            | ı     | The <b>HOST ADDRESS LATCH ENABLE</b> signal is used to indicate to the 82750PB that the host has asserted a valid address (A[31:2], BE # [3:0]) and write enable (WE #).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HRDY#             | 0     | HOST READY is asserted by the 82750PB at the end of a host access to indicate that the access cycle is ready for data transfer. For a host write cycle, HRDY # indicates that the 82750PB is ready to accept data from the host. For a host VRAM write cycle, HRDY # indicates that the VRAM has latched the data from the host. For a host read cycle, HRDY # indicates that output data from the 82750PB or VRAM is ready to be latched by the host.                                                                                                                                                                                          |

| HINT#             | 0     | HOST INTERRUPT: This output is asserted when an interrupt condition is detected by the 82750PB, and the enable bit in the PROCESSOR CONTROL register corresponding to that interrupt condition is set to a ONE. HINT# stays active until the host CPU reads the INTERRUPT STATUS register. If an interrupt condition that is enabled occurs during the same cycle that the INTERRUPT STATUS register is being read, HINT# remains active.                                                                                                                                                                                                       |

| D[31:0]           | 1/0   | The <b>DATA BUS</b> is used to transfer data between:  1. The 82750PB and VRAM, and  2. The Host CPU and internal 82750PB registers. During host VRAM accesses, this bus is tri-stated to allow the host to share the same VRAM data bus. During host accesses to internal 82750PB registers all 32 bits are used for data transfer.                                                                                                                                                                                                                                                                                                            |

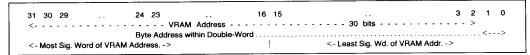

| A[31:9]<br>A[8:2] | 0 1/0 | The <b>ADDRESS BUS</b> is shared between the 82750PB and the host for addressing VRAM. This 30-pin bus addresses 32-bit double words in VRAM. Byte Enable signals are used to address individual bytes or words within a double word in VRAM. In addition, the address for host accesses to internal 82750PB registers are communicated to the 82750PB using the lower seven pins, A[8:2], and the BE# pins. During host access cycles to either VRAM or 82750PB internal registers, A[31:2] are tri-stated. For internal register accesses, as indicated by HREG# being low, the lower seven bits, A[8:2], are used as the host address input. |

| CLKOUT            | 0     | The CLOCK OUTPUT signal is one of the two internal clocks and is synchronized with CLKIN. It is always driven and will have a 50% duty cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  | Table 1-3. Pin Descriptions (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol           | Туре                                    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| BE#[3:0]         | 1/0                                     | The <b>BYTE ENABLE BUS</b> is shared by the 82750PB and the host for addressing VRAM down to the byte level. The correspondence between the four Byte Enable pins and the D[31:0] pins is: BE#[3] – D[31:24], BE#[2] – D[23:16], BE#[1] – D[15:8], and BE#[0] – D[7:0]. During VRAM read cycles, the 82750PB enables all four bytes. During write cycles the 82750PB only enables those bytes that are to be written. Bytes that are not enabled are not to be altered in VRAM. During host accesses to 82750PB on-chip registers, the BE#[0] pin is used as an input to select whether the even or odd word is being accessed; the double word address is provided by the host on the A[8:2] pins. BE#[0] = 0 indicates that data is transferred on D[31:16]. |  |  |  |

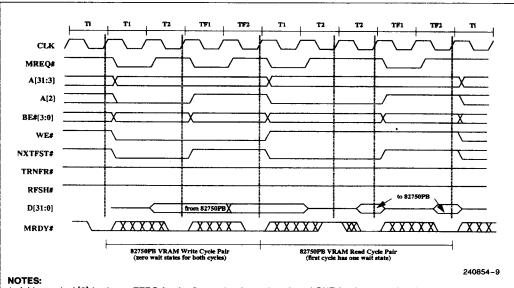

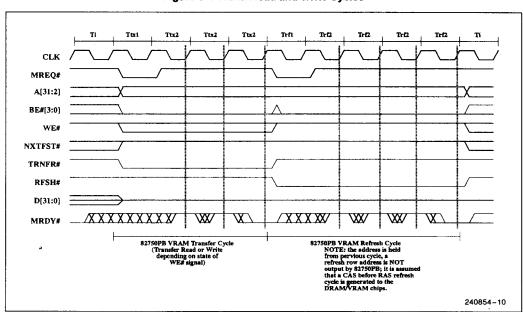

| MREQ#            | 0                                       | MEMORY REQUEST is asserted for the first cycle, T1, of each VRAM cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| TRNFR#,<br>RFSH# | 0                                       | The <b>MEMORY CYCLE DEFINITION SIGNALS:</b> Transfer, Refresh and Write Enable are asserted at the same time as MREQ#, but stay active for the entire VRAM cycle. TRNFR# active indicates a VRAM transfer cycle. RFSH# active indicates a VRAM refresh cycle. If neither TRNFR# nor RFSH# are active, a VRAM data read or write cycle is requested.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| WE#              | 1/0                                     | The WRITE ENABLE pin is used as an output during an 82750PB/VRA cycle to drive the WE # signal, which defines the access as a VRAM reacycle (when inactive) or write cycle (when active). During Host/VRAM and Host External cycles, the 82750PB tri-states this pin to allow the hot odrive the VRAM write enable signals directly. During Host/register cycles, this pin is used as an input for the Host Write Enable signal to determine whether the host is reading or writing the 82750PB register.                                                                                                                                                                                                                                                      |  |  |  |

| NXTFST#          | 0                                       | The NEXT FAST signal indicates that the following vram cycle can be performed with a page-mode or bank-interleaved access. This signal is asserted during the first of a pair of VRAM cycles that is guaranteed to be within the same VRAM page and in opposite banks—a pair of accesses to two sequential double words in VRAM at addresses Even Address and Even Address + 1. In other words, A[2] is a zero for the first cycle and a one for the second cycle.                                                                                                                                                                                                                                                                                             |  |  |  |

| MRDY#            |                                         | The <b>MEMORY READY</b> input indicates that the VRAM cycle has progressed to the point where it is ready to perform the data transfer. For a VRAM read cycle, the VRAM data can be latched by the transition of MRDY# to an active state. For a VRAM write cycle, MRDY# indicates that the data has been latched into the VRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VBUS[3:0]        | I                                       | The VDP COMMUNICATION BUS is used to communicate from the 82750DB to the 82750PB. Codes sent over this bus indicate interrupt requests, transfer requests, and status information. Since the 82750DB and 82750PB run asynchronously, the VBUS signals are sampled on the falling edge of CLKIN and compared with the previous sample. For a VBUS code to be detected by the 82750PB, it must be valid for two successive samples.                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HALT#            | 1                                       | The <b>HALT</b> signal causes the microcode processor on the 82750PB to halt prior to executing the next instruction. This signal does not halt the VRAM interface. The Halt signal will allow the design of a hardware emulator for the 82750PB based on an 82750PB chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TEST#            | ł                                       | The <b>TEST</b> signal is used for test purposes only and must remain high for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

Table 1-3. Pin Descriptions (Continued)

| Symbol Type PMFRZ# O |   | Name and Function                                                                                                                                                                          |  |  |

|----------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      |   | The <b>PERFORMANCE MONITORING AND FREEZE</b> signal is toggled by specific microcode instructions and can be used to determine the time required to execute certain sections of microcode. |  |  |

| V <sub>CC</sub>      | ı | <b>POWER</b> pins provide the +5V D.C. supply input.                                                                                                                                       |  |  |

| V <sub>SS</sub>      | 1 | GROUND pins provide the 0V connection to which all inputs and outputs are referenced.                                                                                                      |  |  |

**Table 1-4. Output Pins**

| Name               | Active<br>Level | When<br>Floated    |

|--------------------|-----------------|--------------------|

| CLKOUT             | High            | Always Driven      |

| A[31:9]            | High            | Reset*, Host Cycle |

| HBUSEN# Low Reset* |                 | Reset*             |

| HRDY#              | Low `           | Reset*             |

| HINT#              | Low             | Reset*             |

| MREQ#              | Low             | Reset*             |

| TRNFR#,<br>RFSH#   | Low             | Reset*             |

| NXTFST#            | Low             | Reset*             |

| PMFRZ#             | Low             | Reset*             |

Table 1-5. Input Pins

| Name      | Active<br>Level | Synchronous/<br>Asynchronous |

|-----------|-----------------|------------------------------|

| CLKIN     | High            | Synchronous                  |

| RESET#    | Low             | Asynchronous                 |

| HREQ#     | Low             | Asynchronous*                |

| HREG#     | Low             | Synchronous                  |

| HRAM#     | Low             | Synchronous                  |

| MRDY#     | Low             | Synchronous                  |

| VBUS[3:0] | High            | Asynchronous                 |

| HALT#     | Low             | Synchronous                  |

| HALEN#    | Low             | Asynchronous*                |

<sup>\*</sup>Can be programmed to accept synchronous inputs.

Table 1-6. Input/Output Pins

| Name     | Active Level | When Floated       | Synch/Async |

|----------|--------------|--------------------|-------------|

| D[31:0]  | High         | Reset*, Host Cycle | Synchronous |

| A[8:2]   | High         | Reset*, Host Cycle | Synchronous |

| BE#[3:0] | Low          | Reset*, Host Cycle | Synchronous |

| WE#      | Low          | Reset*, Host Cycle | Synchronous |

<sup>\*</sup>The reset state is caused by RESET# being active low.

All output pins are floated when RESET is active low.

## 2.0 ARCHITECTURE

### Overview

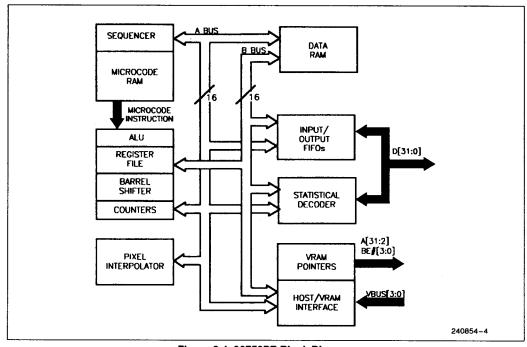

The 82750PB includes a wide instruction word processor that comprises a number of processing, storage, and input/output elements. The wide instruction word architecture allows a number of these elements to operate in parallel. The 82750PB executes one instruction every internal clock cycle or T-cycle. The various elements are connected via two 16-bit buses, the A bus and B bus, as shown in Figure 2-1. During each instruction execution cycle, data can be transferred from a bus source to a bus destination element on both buses.

# Registers

$\{rN; N = 0 - 15\}$

There are 16 general-purpose data registers, each 16 bits wide, that are connected to both the A bus and B bus as both sources and destinations. These registers are designated rO-r15. All the registers are

functionally identical except r0, which also includes logic for bit shifting and byte swapping. A register can source both the A bus and the B bus in the same cycle. A register cannot be the destination of both the A bus and the B bus in a single instruction. Because the registers are doubly latched, the same register may be both a source and destination in the same cycle. The result is that the data in the register prior to the current cycle will be driven on the source bus, and the data on the destination bus will be latched into the register at the end of the cycle.

Register nO has additional logic to allow bit shifting and byte swapping. The value in nO can be shifted left or right one bit position per instruction cycle. For a right shift, the new MSB is equal to the old MSB; in other words, the value is sign-extended. For left shifting, the new LSB is equal to zero. nO cannot be shifted and loaded in the same instruction. Byte swapping, on the other hand, only occurs when nO is being loaded with a value from the A bus or B bus. Byte swapping causes the most significant byte and the least significant byte of the 16-bit value being loaded into nO to be interchanged. Refer to Chapter 4 for a description of the SHFT microcode field that controls the shifting and swapping operations in nO.

Figure 2-1. 82750PB Block Diagram

# **ALU**

(alu, cc)

The ALU performs 16-bit arithmetic and logic operations, and can also be operated as two independent 8-bit ALUs for the Dual-Add-with-Saturate operation. There are two fields in the microcode instruction that affect the operation of the ALU: the ALUOP field specifies the operation to be performed, and the ALUSS field specifies the source of the two ALU inputs. Refer to Chapter 4 for further information on these fields.

The two ALU operands either come from values held in the ALU input latches or from "eavesdropping" on the A or B buses. The result of any ALU operation is latched in the ALU output register, *alu*. In a subsequent instruction this result can be transferred to any A or B destination.

The ALU has four condition flag outputs: CarryOut, Sign, Overflow, and Zero. CarryOut is the carry out of the most significant bit position. Sign is equal to the value of the most significant bit of the result. Overflow is the exclusive-OR of CarryOut and the CarryIn to the most significant bit position of the result. Zero is true (a value of 1) if all 16 bits of the ALU result are equal to zero. CarryOut and Overflow are defined as equal to zero for all logical operations. For most ALU operations, the state of these four condition flags are latched when the operation is complete. There are eight operations (nop, a\*, b\*, +1, -1, 0\*, prof and int) that are exceptions. These operations are performed without disturbing the condition state of the previous ALU operation.

Microcode routines can read and write the ALU condition flag register, *cc*. This can be used to save and restore the state of these flags. The bit ordering of the ALU condition flags within *cc* are given in Table 2-1. A complete list of ALU opcodes is given in Table 2-2.

Table 2-1. Bit Assignments for cc Register

| Bit      | Condition                                                                 |  |

|----------|---------------------------------------------------------------------------|--|

| Bit 0    | False (This bit of the cc is always read as a zero.)*                     |  |

| Bit 1    | ALU Carry Out                                                             |  |

| Bit 2    | ALU Overflow                                                              |  |

| Bit 3    | ALU Sign                                                                  |  |

| Bit 4    | ALU Zero                                                                  |  |

| Bit 5    | Loop Counter Zero*                                                        |  |

| Bit 6    | R0 LSB*                                                                   |  |

| Bit 7    | R0 MSB*                                                                   |  |

| Bit 15:8 | RESERVED. The state of these bits is undefined when read; write as zeros. |  |

<sup>\*</sup>These are read-only values and are not affected by writes to the co register.

Table 2-2. ALU Opcodes

| Operation                 | Mnemonic |

|---------------------------|----------|

| No Operation              | nop      |

| pass a                    | а        |

| pass b                    | b        |

| 1's Compliment of a       | ~a       |

| 1's Compliment of b       | ~ b      |

| a AND b                   | &.       |

| (NOT a) AND b             | ~&       |

| a AND (NOT b)             | &~       |

| a OR b                    |          |

| a XOR b                   | ٨        |

| a + b                     | +        |

| a + b + 1                 | ++       |

| a – b                     |          |

| -a + b                    | -+       |

| 2's Compliment of a       | -a       |

| 2's Compliment of b       | -b       |

| Increment a               | a++      |

| Increment b               | b++      |

| Decrement a               | a        |

| Decrement b               | b        |

| Dual Add with Sat.        | +]       |

| a + b + (Prev. Carry)     | + <      |

| a - b - (Prev. Borrow)    | -<       |

| -a + b - (Prev. Borrow)   | -+<      |

| Interrupt Host            | int      |

| Zero                      | 0*       |

| Pass a, Don't Latch Flags | a*       |

| Pass b, Don't Latch Flags | a*       |

| (NOT a) OR b              | ~        |

| a OR (NOT b)              | ~        |

| Dual Sub. with Sat.       | <u> </u> |

| Performance Monitor       | prof     |

The Dual-Add-with-Saturate operation performs independent 8-bit ADDs on the upper and lower bytes of the two ALU operands. The two bytes of the A operand are treated as unsigned binary numbers (00:FF<sub>16</sub> corresponds to 0:255<sub>10</sub>). The two bytes of the B operand are treated as offset binary numbers

with an offset of +128 (00:FF<sub>16</sub> corresponds to  $-128_{10}$ :127<sub>10</sub>). The upper and lower byte results are treated as 9-bit offset binary, including the carry output of each byte, with a +128 offset (000:1FF<sub>16</sub> corresponds to  $-128_{10}$ :383<sub>10</sub>) and are saturated to a range of  $0-255_{10}$ . A result that is less than zero is set equal to zero or  $00_{16}$  and a result that is greater than +255 is set equal to +255 or FF<sub>16</sub>.

In fact, this operation is symmetric. Either the A operand or the B operand can be defined as the unsigned binary value, and the other operand will be treated as the offset signed binary value.

Dual-subtract-with-saturate is similar to dual-add-with-saturate. It calculates A-B+128 on each 8-bit half of the two 16-bit inputs, and clamps the results to 0 and 255. This can be viewed as subtracting an offset-binary signed byte (-128 to 127) from an unsigned byte (0 to 255).

The ALU opcode INT generates the MCINT (microcode interrupt) condition. When this condition is detected by interrupt logic in the host CPU interface, and if the Enable MCINT bit in the PROCESSOR CONTROL register is set to a ONE, the host interrupt output, HINT\*, will be asserted. Refer to Chapter 3 for further information on host interface.

The 'prof' opcode activates the PMFRZ# pin, and is primarily used for performance monitoring and/or debugging.

# **Barrel Shifter**

(shift, shift-r, shift-rl, shift-l)

The barrel shifter performs a single cycle, n-bit left or right shift. The barrel shifter operates independent of the ALU. The three barrel shifter operations are: Shift-r for a right shift with sign extend; Shift-r for a right shift with sign extend; Shift-r for a left shift with zero fill. The shift operation is invoked by writing a 4-bit value (the shift amount) to one of three A bus registers, depending on which of the three operations is to be performed. The operand is taken from the B bus, and the result is stored in the barrel shifter output register, Shift. Like the ALU result register, the value in Shift can be read onto the A bus or B bus in the following instruction cycle.

A barrel shifter operation does not affect any of the condition flags.

# **Data RAM**

$\{dramN, *dramN, ++, --; N = 1-4\}$

The Data RAM holds 512, 16-bit words that are accessed using four pointers. To access a value in a particular location, the microcode routine must first load a pointer with the address to be accessed, and then perform a read or write using the same pointer. In parallel with the data RAM access, the pointer can optionally be post-incremented or post-decremented. The four pointers, referred to as dram1-dram4, can be written and read via the A bus. When a dram pointer, which is only 9 bits wide, is read onto the A bus, its upper seven bits are set to zeros.

### NOTE:

The width of the dram pointers may change in later versions of the 82750PB. Software should not rely on the width of a pointer to, for example, mask the upper seven bits of a value to zero.

All four pointers can be used to read or write the Data RAM from either the A or B bus. Only one Data RAM access can be performed in any cycle. A Data RAM access is referred to, using C language syntax, as \*dram1. The \* means "the value pointed to by". As another example, \*dram3++ means access the Data RAM using the pointer dram3 and increment dram3. The symbol — in place of the ++ would indicate autodecrement.

# **Loop Counters**

(cnt,cnt2)

Two 16-bit loop counters are available to microcode programs for automatically counting iterations of a microcode loop. In parallel with other operations performed in an instruction, either loop counter can be decremented, and a conditional branch can be made based on the loop counter value being equal or not equal to zero. Since the two loop counters can be written and read on the A bus, as *cnt* and *cnt2* respectively, they can also be used for variable storage when not being used as loop counters. The loop counters can be written to and decremented during the same instruction cycle. The value in the counter at the start of the next cycle will be the value written to the counter minus one.

The LC microcode bit determines the loop counter that is selected for decrementing and/or branching in an instruction. The LC microcode bit does not affect the loop counter that is written or read over the A bus, since each loop counter is separately addressable as an A bus source or destination. Refer

to Chapter 4 for a description of the CNT — microcode bit that causes the select loop counter to be decremented, and for a description of the CFSEL microcode field that is used to perform a conditional branch based on the selected loop counter's value.

### Microcode RAM

{mcode1-3, maddr, pc}

The 82750PB executes instructions stored in an onchip microcode RAM. This RAM holds 512 instructions and each instruction is 48 bits wide. Normally, to start the microcode processor, the host CPU will load a microcode program into the microcode RAM, point the program counter, pc, to the start of the program, and then release the HALT bit to start executing the microcode program. The microcode processor can also load its own microcode RAM to overlay new routines and therefore, does not require constant intervention by the host to perform multiple operations.

Writing an instruction into Microcode RAM is done by first loading the three registers *mcode3*, *mcode2*, and *mcode1* with the three 16-bit words of the instruction (the most significant word goes into *mcode1*), and then loading the address where the instruction should be written into *maddr*.

The host CPU can also read the Microcode RAM by first loading the *pc* with the address of the instruction to be read and then reading the three 16-bit words of the instruction from the *mcode1-mcode3* registers. Normally, this would be done by the Host CPU while the 82750PB is halted. Since *mcode1-mcode3* hold the instruction pointed to by the *pc* (i.e. the instruction that is about to be executed), normally reading these three registers from a microcode routine is not useful.

The read registers named mcode1-mcode3 and the write registers also named mcode1-mcode3 are in fact different registers. Writing values into mcode1-mcode3 and then reading the values of mcode1-mcode3 will not read back the same values just written. The read registers hold the instruction stored in the instruction latch (the instruction to be executed). The write registers hold an instruction that is about to be written into microcode RAM.

After writing to *maddr* to load an instruction into microcode RAM, a one cycle freeze occurs and during the freeze a write to the microcode RAM takes place. The instruction following the write to *maddr* can either jump to the address just loaded or start loading the *mcode1-mcode3* registers with the next instruction to be written.

Here are two examples that illustrate the fact that the 82750PB requires at least one instruction between the write to maddr and the execution of the instruction that is loaded by the write to maddr.

```

Example 1:

/* load instruction */

maddr = ADDR1

jmp addrl

/* jump to it, this is the extra inst. required between */

/* writing to maddr and executing the loaded inst. */

ADDR1:

??????????

/* here's where new instruction gets loaded */

Example 2:

maddr = INST

non

/* extra instruction */

INST:

??????????

/* instruction gets loaded here */

When a microcode routine writes to pc, one more instruction is executed before the jump to the new address takes

effect. For example:

pc = ADDR1

jmp ADDR2 /* this instruction gets executed but */

r0 = r1

/* its jump to ADDR2 is ignored. */

ADDR1:

r3 = r0

/* after this instruction executes r3 = r0 = rl */

```

When the host CPU writes to the pc, the instruction at the address that was written is loaded into the mcode1-mcode3 registers and, when the microcode processor is released from its Halt condition, this is the first instruction that will be executed.

When the host CPU reads the *pc*, the result returned is the address of the instruction that will be executed when Halt is released, that is, the address of the instruction held in the *mcode1-mcode3* registers.

# **Horizontal Line Counter**

(Icnt)

The 12-bit Horizontal Line Counter is updated by VBUS codes from the 82750DB to track the horizontal display line that is currently being scanned by the 82750DB. The counter is reset by a VODD code and incremented each time an HLINE code is received. A value can also be written into a Horizontal Line Counter but this is used primarily for testing the 82750PB. The upper four bits will always read zeros.

# **Field Counter**

(fcnt)

The 4-bit field counter is updated by VBUS codes from the display processor to keep track of the field count being displayed by 82750DB. The counter is incremented each time a V<sub>ODD</sub> code or V<sub>EVEN</sub> code is received. When reading the field counter, the upper 12 bits will read zeros. This counter will not be initialized upon reset.

# Input FIFOs

(inN-lo, inN-hi, inN-c, \*inN; N = 1, 2)

There are two input channels, referred to as input FIFOs, through which the processor can read pixels or data from VRAM. Each channel automatically fetches 64-bit quad words from VRAM and breaks them into 8-bit bytes or 16-bit words that are read by microcode. Each input FIFO operates independently and can be programmed to automatically increment or decrement through bytes or words in VRAM. The FIFOs are double buffered so that while values are being extracted from one quad word (64 bits), the next quad word is being prefetched from VRAM.

The mode control register for each input FIFO, designated *in1-c* or *in2-c*, contains four mode bits as seen in Figure 2-2. The WORD/BYTE bit (bit 0) determines whether the input FIFO is in word mode (WORD/BYTE = 0) or byte mode (WORD/BYTE = 1). In byte mode, the FIFO can start reading on any byte boundary and in word mode on any word boundary.

The INC/DEC bit (bit 1) determines the order that bytes or words are read from VRAM. In INCREMENT mode, with INC/DEC = 0, the FIFO reads from the least significant byte or word to the most significant byte or word double word and increments through double words in VRAM. In DECREMENT mode, with INC/DEC = 1, the FIFO reads from most significant byte or word to least significant byte or word within a double word and decrements through double words in VRAM.

The AHOLD bit (Bit 2) is used by the address hold mode. When asserted, (bit 2 = 1) the automatic address increment/decrement function will be disabled and input FIFOs will not double buffer VRAM data. In other words, at the end of a VRAM cycle, when the FIFO has been updated with 64 bits of VRAM data, the input FIFO will not issue another MREQ# until there is a write to the address-lo registers OR a roll-over/roll-under read access of the input FIFO. If a roll-over/roll-under occurs, then a memory request will be issued to fetch data from the same VRAM location. If there is a write to the address-lo register, the FIFO will then fetch data from the new location.

The PREFETCH OFF bit (bit 3) specifies whether the FIFO will automatically prefetch successive quad words from VRAM or will only fetch a new quad word when a value from that quad word is requested. In PREFETCH-ON mode, bit 3 = 0, the input FIFO prefetches successive quad words from VRAM as necessary to keep its buffer full (either from ascending or descending addresses, depending on the state of the INC/DEC bit). In PREFETCH-OFF mode, the FIFO will still prefetch the first two quad words to fill its buffer (when started at a new address location), but will only fetch a new quad word when a read request is made to the FIFO for a value in the next unfetched quad word.

The CB bit (bit 4) allows circular buffers of sizes 64 kBytes, 128 kBytes, or 256 kBytes to be created in VRAM memory. The choice of different sizes of buffers are determined by programming the least significant 3 bits of the circular buffer register (cir-

| bits:     | 15 4         | 5          | 4  | 3      | 2     | 1       | 0         |

|-----------|--------------|------------|----|--------|-------|---------|-----------|

| J. Citto. | Set to Zeros | BY-32 MODE | СВ | PF OFF | AHOLD | INC/DEC | WORD/BYTE |

Figure 2-2. Input FIFO Control Register

cbuf). To enable this feature, the CB bit has to be set to a 1, then depending on the buffer size selected, the appropriate address pin that goes off chip will be forced to a 0 (register pointers remain unchanged). Table 2-3 shows the programming combinations of the circular buffer register.

It is important to note that the internal address counters themselves are not affected by the circbuf function. Only the selected external address pin is forced to '0'.

Table 2-3. Circular Buffer Register (circbuf)

| Bits [2:0] | Buffer Size | Effect on PB Address Bus (if Function Enabled) |  |

|------------|-------------|------------------------------------------------|--|

| 000        | Disabled    | None                                           |  |

| 100        | 256 kBytes  | Address Pin 18 Forced to 0                     |  |

| 010        | 128 kBytes  | Address Pin 17 Forced to 0                     |  |

| 001        | 64 kBytes   | Address Pin 16 Forced to 0                     |  |

In "BY-32" MODE (bit 3), the pointer increments or decrements by 32 bits, independent of whether the FIFO is in 8-bit pixel mode or 16-bit pixel mode. This mode was added to facilitate microcode that operates on one component of a 32-bit per pixel image.

The standard sequence for initializing an input FIFO is to write to the control register (in-c), the high address (in-hi), and then the low address (in-lo) of the appropriate FIFO. Refer to the access state diagram in Chapter 3. The write to in-lo causes the FIFO to start reading from VRAM. A byte or word is then read from \*in. Successive reads from \*in will read sequential bytes or words from VRAM. Writing to the control register each time the FIFO is started at a new address is not necessary, except to change the FIFO's mode. Also, if the new address is within the same 64 kByte page of VRAM, only the lo-address needs to be written in order to start the FIFO reading from the new address.

If microcode attempts to read a value from an empty input FIFO, the processor is frozen prior to the execution of the instruction, until the FIFO's control logic has fetched another double word from VRAM and extracted the next value. At this point, the processor is released from the frozen state, and the instruction that reads the value is executed. When the processor is frozen waiting for a particular FIFO that isn't yet ready, that FIFO's VRAM access priority is raised above all other FIFOs.

# **Output FIFOs**

{outN-lo, outN-hi, outN-c, \*outN, outN++; N = 1, 2}

There are two output channels, referred to as output FIFOs, through which the graphics processor writes pixels or data to VRAM. Each channel automatically collects bytes or words into 64-bit quad words and writes the quad words to VRAM. Each output FIFO operates independently and can be programmed to write bytes or words into sequential addresses in VRAM (either incrementing or decrementing). The FIFOs are double buffered so that while one quad word is waiting to be written to VRAM, the next quad word can be assembled from individual bytes or words.

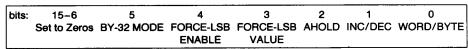

The mode control register for each output FIFO, designated *out1-c* or *out2-c*, contains six mode bits as shown in the Figure 2-3. The WORD/BYTE bit (bit 0) determines whether the output FIFO is in word mode (WORD/BYTE = 0) or byte mode (WORD/BYTE = 1). In byte mode the FIFO can start writing on any byte boundary in VRAM and in word mode on any word boundary.

The INC/DEC bit (bit 1) determines the order that bytes or words are written to VRAM. In INCREMENT mode, with INC/DEC = 0, the FIFO writes from the least significant byte or word to the most significant byte or word in a double word and increments through double words in VRAM. In DECREMENT mode, with INC/DEC = 1, the FIFO writes from most significant byte or word to least significant byte or word within a double word and decrements through double words in VRAM.

When the AHOLD bit (bit 2) is set, the output FIFO quad word address is not incremented or decremented. In this mode, the FIFO continues to output to a single quad word in VRAM.

The FORCE-LSB bits (bits 3 and 4) are used to force the least significant bit of each byte written to VRAM to either a zero or a one. This can be used, for example, to force the LSB to the correct polarity when writing to the U bitmap during motion video decompression. In certain display modes for the 82750DB, the LSB of the 8-bit samples in the U or Y bitmap are used to select VIDEO or GRAPHICS display mode for the n x n group of display pixels corresponding to the particular U or Y sample. A one in the FORCE-

Figure 2-3, Output FIFO Control Register

LSB ENABLE bit (bit 4) enables the forcing; a zero results in normal operation. The FORCE-LSB VAL-UE bit (bit 3) is used as the value to which the LSB is forced. Whether in byte mode or word mode, the LSB of *each byte* is forced to the FORCE-LSB value.

In "BY-32" MODE (bit 5), the pointer increments or decrements by 32 bits, independent of whether the FIFO is in 8-bit pixel mode or 16-bit pixel mode. This mode is used to facilitate microcode that operates one component of a 32-bit per pixel image. The bytes or words that are skipped over will be unchanged in VRAM.

The standard sequence for initializing an output FIFO is to write to the control register (out-c), the low address (out-lo), and then the high address (out-hi) of the appropriate FIFO. A series of bytes or words is then written to \*out. Refer to the access state diagram in Chapter 3 (Figure 3-1).

In order to flush any remaining data in an output FIFO before changing its VRAM pointer, it is necessary to write to the control register. When pointing to a new location in VRAM, if the new address is within the same 64 kByte page of VRAM, only the lo-address needs to be written.

There must be one instruction between the write to the output FIFOs low address and the first write to \*outN. Therefore, it is recommended that outN-lo be written before outN-hi. The write to outN-hi insures that this requirement is met. If only the outN-lo value is being changed, it is still necessary to have one additional instruction before the first write to \*outN.

When writing bytes or words to VRAM through an output FIFO, a byte or word can be skipped over by writing to *outIV++* instead of \*outIV. When the values are written to VRAM, any byte or word that was skipped will retain its original value in VRAM, and its value is not altered by the VRAM write. This can be used when writing a series of pixels, some of which are "transparent", allowing whatever was behind them to show through.

If the microcode routine attempts to write a value to a full output FIFO, the processor is frozen prior to the execution of the instruction. The processor remains frozen until the FIFO has a chance to write one of the buffered quad words to VRAM. At that point, the processor is released from the frozen state, and the instruction that writes the value is executed. When the processor is frozen, waiting for a particular FIFO that isn't yet ready, that FIFO's VRAM access priority is raised above all other FIFOs.

# Statistical Decoder

{ stat-lo, stat-hi, stat-c, stat-ram, \*stat, \*stat # }

The Statistical Decoder (also referred to as the Huffman Decoder) is a specialized input channel that can read a variable-length bit sequence from VRAM and convert it into a fixed-length bit sequence that is read by the microcode processor. In image compression, as well as in other applications such as text compression, certain values occur more frequently than others. A means of compressing this data is to use fewer bits to encode more frequently occurring values and more bits to encode less frequently occurring values. This type of encoding results in a variable-length sequence in which the length of a symbol (the group of bits used to encode a single value) can range for example, from one bit to sixteen bits.

The statistical code that the statistical decoder can decode is of either of the two forms:

| 0x               |    | 1x             |

|------------------|----|----------------|

| 10x              |    | 01x            |

| 110xxx           |    | 001xxx         |

| 1110xxxxx        |    | 0001xxxxx      |

|                  | or |                |

| 111111110xxxxx   |    | 00000001xxxxxx |

| 1111111110xxxxxx |    | 00000001xxxxx  |

|                  |    |                |

Each symbol of a given length (one per line as shown here) consists of a run-in sequence followed by some number of x-bits. The run-in sequence is defined as a series of zero or more ONEs followed by a ZERO or, as in the code on the right above, zero or more ZEROs followed by a ONE. The remainder of this description will use examples of the code on the left. A bit in the decoder's control register determines the polarity of the run-in sequence bits.

In the example on the left, there would be two symbols of length two: 00 and 01. Each x-bit can take on a ZERO or ONE value. The number of x-bits following a run-in sequence can range from zero to six. Since the goal, in general, is to have a few short codes and a larger number of long codes, typically, codes with fewer run-in bits will have fewer x's following. However, this is not a hardware constraint. A code of this form is completely described by a code description table indicating: for each length of run-in sequence, R = the number of ONEs in the run-in, and how many x-bits follow the ZERO. The value of R is used as an index into the code description table. Due to the hardware implementation, the number actually stored in the table is 2x, where x is the number of x-bits.

For the example above, the corresponding code description values are given in Table 2-4.

Table 2-4. Sample Code Description Table

| R | x | 2×(dec.) | 2×(bin.) |

|---|---|----------|----------|

| 0 | 1 | 2        | 000 0010 |

| 1 | 1 | 2        | 000 0010 |

| 2 | 3 | 8        | 000 1000 |

| 3 | 5 | 32       | 010 0000 |

| 7 | 6 | 64       | 100 0000 |

Note that the table only goes up to symbols with seven ONEs in the run-in. For symbols with more than seven ONEs, the value of X and 2<sup>x</sup> for seven ONEs is used for all symbols having seven or more ONEs in the run-in sequence. For example, in the code above a symbol with eight or more ONEs in the run-in sequence has six x-bits following the ZERO, which is the same as symbols having seven ONEs.

For each different symbol, including all symbols of the same run-in length with different x-bit values, the decoder generates a unique fixed-length, 16-bit value. Some of the decoded values for the sample code given above are provided in Table 2-5.

Table 2-5. Decoded Values

| Symbol*           | Decoded Value |

|-------------------|---------------|

| 00                | 0             |

| 01                | 1             |

| 100               | 2             |

| 101               | 3             |

| 110000            | 4             |