### DS1743/DS1743P Y2K-Compliant, Nonvolatile Timekeeping RAMs

#### www.maxim-ic.com

#### **FEATURES**

- Integrated NV SRAM, Real-Time Clock, Crystal, Power-Fail Control Circuit, and Lithium Energy Source

- Clock Registers are Accessed Identically to the Static RAM. These Registers Reside in the Eight Top RAM Locations.

- Century Byte Register

- Totally Nonvolatile with Over 10 Years of Operation in the Absence of Power

- BCD-Coded Century, Year, Month, Date, Day, Hours, Minutes, and Seconds with Automatic Leap Year Compensation Valid through 2099

- Low-Battery-Voltage Level Indicator Flag

- Power-Fail Write Protection Allows for ±10%

V<sub>CC</sub> Power-Supply Tolerance

- Lithium Energy Source is Electrically Disconnected to Retain Freshness Until Power is Applied for the First Time

- DIP Module Only Standard JEDEC Bytewide 8k x 8 Static RAM Pinout

- PowerCap Module Board Only Surface-Mountable Package for Direct Connection to PowerCap Containing Battery and Crystal Replaceable Battery (PowerCap) Power-On Reset Output Pin-for-Pin Compatible with Other Densities of DS174XP Timekeeping RAM

- Underwriters Laboratory (UL) Recognized to Prevent Charging of the Internal Lithium Battery

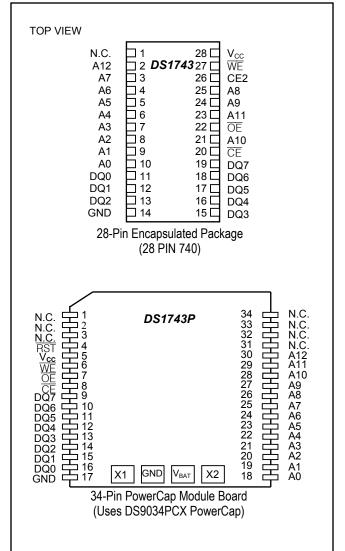

### **PIN CONFIGURATIONS**

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <u>www.maxim-ic.com/errata</u>.

| PIN  |                   | NAME | FUNCTION              |

|------|-------------------|------|-----------------------|

| PDIP | PowerCap          | NAME | FUNCTION              |

| 1    | 1, 2, 3,<br>31–34 | N.C. | No Connection         |

| 2    | 30                | A12  |                       |

| 3    | 25                | A7   |                       |

| 4    | 24                | A6   |                       |

| 5    | 23                | A5   |                       |

| 6    | 22                | A4   | Address Input         |

| 7    | 21                | A3   |                       |

| 8    | 20                | A2   |                       |

| 9    | 19                | A1   |                       |

| 10   | 18                | A0   |                       |

| 11   | 16                | DQ0  | Data Immet/           |

| 12   | 15                | DQ1  | Data Input/<br>Output |

| 13   | 14                | DQ2  | Output                |

| 14   | 17                | GND  | Ground                |

| 15   | 13                | DQ3  |                       |

| 16   | 12                | DQ4  | Data Immet/           |

| 17   | 11                | DQ5  | Data Input/<br>Output |

| 18   | 10                | DQ6  | Output                |

| 19   | 9                 | DQ7  |                       |

# **PIN DESCRIPTION**

| P    | PIN      | NAME            | FUNCTION                                |

|------|----------|-----------------|-----------------------------------------|

| PDIP | PowerCap |                 |                                         |

| 20   | 8        | TE              | Chip Enable,<br>Active Low              |

| 21   | 28       | A10             | Address Input                           |

| 22   | 7        | ŌĒ              | Output Enable,<br>Active Low            |

| 23   | 29       | A11             | Address Input                           |

| 24   | 27       | A9              |                                         |

| 25   | 26       | A8              |                                         |

| 26   |          | CE2             | Chip Enable 2                           |

| 27   | 6        | WE              | Write Enable,<br>Active Low             |

| 28   | 5        | V <sub>CC</sub> | Power-Supply<br>Input                   |

|      | 4        | RST             | Power-On Reset<br>Output, Active<br>Low |

|      |          | X1, X2          | Crystal<br>Connection                   |

|      |          | $V_{BAT}$       | Battery<br>Connection                   |

| PART              | TEMP RANGE                       | PIN-PACKAGE    | VOLTAGE<br>(V) | TOP MARK**       |

|-------------------|----------------------------------|----------------|----------------|------------------|

| <b>DS1743-</b> 70 | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 5              | DS1743-70        |

| DS1743-85         | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 5              | DS1743-85        |

| DS1743-100        | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 5              | DS1743-100       |

| DS1743-100 IND    | -40°C to +85°C                   | 28 EDIP Module | 5              | DS1743-100-IND   |

| DS1743P-70        | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 5              | DS1743P-70       |

| DS1743P-85        | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 5              | DS1743P-85       |

| DS1743P-100       | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 5              | DS1743P-100      |

| DS1743P-100IND    | -40°C to +85°C                   | 34 PowerCap*   | 5              | DS1743P-100 IND  |

| DS1743W-120       | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 3.3            | DS1743W-120      |

| DS1743W-120 IND   | -40°C to +85°C                   | 28 EDIP Module | 3.3            | DS1743W-120 IND  |

| DS1743W-150       | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 3.3            | DS1743W-150      |

| DS1743W-150 IND   | -40°C to +85°C                   | 28 EDIP Module | 3.3            | DS1743W-150 IND  |

| DS1743WP-120      | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 3.3            | DS1743WP-120     |

| DS1743WP-120 IND  | -40°C to +85°C                   | 34 PowerCap*   | 3.3            | DS1743WP-120 IND |

| DS1743-70+        | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 5              | DS1743-70        |

| DS1743-85+        | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 5              | DS1743-85        |

| DS1743-100+       | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 5              | DS1743-100       |

| DS1743-100 IND+   | -40°C to +85°C                   | 28 EDIP Module | 5              | DS1743-100-IND   |

| DS1743P-70+       | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 5              | DS1743P-70       |

| DS1743P-85+       | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 5              | DS1743P-85       |

| DS1743P-100+      | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 5              | DS1743P-100      |

| DS1743P-100IND+   | -40°C to +85°C                   | 34 PowerCap*   | 5              | DS1743P-100 IND  |

| DS1743W-120+      | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 3.3            | DS1743W-120      |

| DS1743W-120 IND+  | -40°C to +85°C                   | 28 EDIP Module | 3.3            | DS1743W-120 IND  |

| DS1743W-150+      | $0^{\circ}$ C to $+70^{\circ}$ C | 28 EDIP Module | 3.3            | DS1743W-150      |

| DS1743W-150 IND+  | -40°C to +85°C                   | 28 EDIP Module | 3.3            | DS1743W-150 IND  |

| DS1743WP-120+     | $0^{\circ}$ C to $+70^{\circ}$ C | 34 PowerCap*   | 3.3            | DS1743WP-120     |

| DS1743WP-120 IND+ | -40°C to +85°C                   | 34 PowerCap*   | 3.3            | DS1743WP-120 IND |

| DS9034PCX         | $0^{\circ}$ C to $+70^{\circ}$ C | PowerCap       |                | DS9034PC         |

| DS90340I-PCX      | -40°C to +85°C                   | PowerCap IND   |                | DS9034PCI        |

| DS9034PCX+        | $0^{\circ}$ C to $+70^{\circ}$ C | PowerCap       |                | DS9034PC         |

| DS90340I-PCX+     | -40°C to +85°C                   | PowerCap IND   |                | DS9034PCI        |

### **ORDERING INFORMATION**

\*DS9034PCX required (must be ordered separately).

\*\*A '+' indicates lead-free. The top mark will include a '+' symbol on lead-free devices.

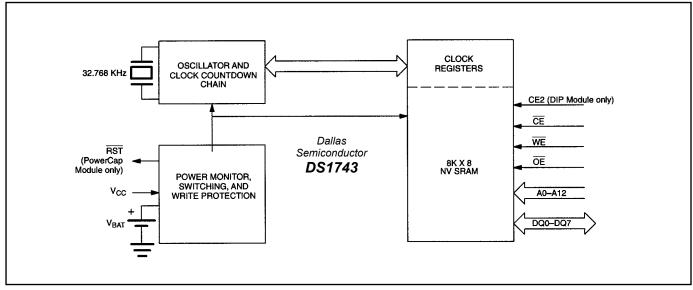

## DESCRIPTION

The DS1743 is a full-function, year-2000-compliant (Y2KC), real-time clock/calendar (RTC) and 8k x 8 nonvolatile static RAM. User access to all registers within the DS1743 is accomplished with a bytewide interface as shown in Figure 1. The RTC information and control bits reside in the eight uppermost RAM locations. The RTC registers contain century, year, month, date, day, hours, minutes, and seconds data in 24-hour binary-coded decimal (BCD) format. Corrections for the day of the month and leap year are made automatically. The RTC clock registers are double buffered to avoid access of incorrect data that can occur during clock update cycles. The double-buffered system also prevents time loss as the timekeeping countdown continues unabated by access to time register data. The DS1743 also contains its own powerfail circuitry, which deselects the device when the  $V_{CC}$  supply is in an out-of-tolerance condition. When  $V_{CC}$  is above  $V_{PF}$ , the device is fully accessible. When  $V_{CC}$  is below  $V_{PF}$ , the internal  $\overline{CE}$  signal is forced

high, preventing any access. When  $V_{CC}$  rises above  $V_{PF}$ , access remains inhibited for  $T_{REC}$ , allowing time for the system to stabilize. These features prevent loss of data from unpredictable system operation brought on by low  $V_{CC}$  as errant access and update cycles are avoided.

## PACKAGES

The DS1743 is available in two packages: the 28-pin DIP and the 34-pin PowerCap module. The 28-pin DIP-style module integrates the crystal, lithium energy source, and silicon all in one package. The 34-pin PowerCap Module Board is designed with contacts for connection to a separate PowerCap (DS9034PCX) that contains the crystal and battery. This design allows the PowerCap to be mounted on top of the DS1743P after the completion of the surface-mount process. Mounting the PowerCap after the surface-mount process prevents damage to the crystal and battery due to the high temperatures required for solder reflow. The PowerCap is keyed to prevent reverse insertion. The PowerCap Module Board and PowerCap are ordered separately and shipped in separate containers. The part number for the PowerCap is DS9034PCX.

## TIME AND DATE OPERATION

The time and date information is obtained by reading the appropriate register bytes. Table 2 shows the RTC registers. The time and date are set or initialized by writing the appropriate register bytes. The contents of the time and date registers are in the BCD format. The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined, but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday and so on). Illogical time and date entries result in undefined operation.

# **CLOCK OPERATIONS-READING THE CLOCK**

While the double-buffered register structure reduces the chance of reading incorrect data, internal updates to the DS1743 clock registers should be halted before clock data is read to prevent reading of data in transition. However, halting the internal clock register updating process does not affect clock accuracy. Updating is halted when a 1 is written into the read bit, bit 6 of the century register (see Table 2). As long as a 1 remains in that position, updating is halted. After a halt is issued, the registers reflect the count that is day, date, and time that was current at the moment the halt command was issued. However, the internal clock registers of the double-buffered system continue to update so that the clock accuracy is not affected by the access of data. All the DS1743 registers are updated simultaneously after the internal clock register updating process has been re-enabled. Updating is within a second after the read bit is written to 0.

The READ bit must be a zero for a minimum of 500µs to ensure the external registers are updated.

#### Figure 1. Block Diagram

#### Table 1. Truth Table

| V <sub>CC</sub>            | <b>CE</b> | CE2             | ŌĒ              | WE              | MODE     | DQ       | POWER                  |

|----------------------------|-----------|-----------------|-----------------|-----------------|----------|----------|------------------------|

|                            | $V_{IH}$  | Х               | Х               | Х               | Deselect | High-Z   | Standby                |

|                            | Х         | V <sub>IL</sub> | Х               | Χ               | Deselect | High-Z   | Standby                |

| $V_{CC} > V_{PF}$          | $V_{IL}$  | V <sub>IH</sub> | Х               | V <sub>IL</sub> | Write    | Data In  | Active                 |

|                            | $V_{IL}$  | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Read     | Data Out | Active                 |

|                            | $V_{IL}$  | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Read     | High-Z   | Active                 |

| $V_{SO} < V_{CC} < V_{PF}$ | Х         | Х               | Х               | Х               | Deselect | High-Z   | CMOS Standby           |

| $V_{CC} < V_{SO} < V_{PF}$ | Х         | Х               | Х               | Х               | Deselect | High-Z   | Data-Retention<br>Mode |

### SETTING THE CLOCK

As shown in Table 2, bit 7 of the century register is the write bit. Setting the write bit to a 1, like the read bit, halts updates to the DS1743 registers. The user can then load them with the correct day, date and time data in 24-hour BCD format. Resetting the write bit to a 0 then transfers those values to the actual clock counters and allows normal operation to resume.

### STOPPING AND STARTING THE CLOCK OSCILLATOR

The clock oscillator may be stopped at any time. To increase the shelf life, the oscillator can be turned off to minimize current drain from the battery. The  $\overrightarrow{OSC}$  bit is the MSB (bit 7) of the seconds registers, see Table 2. Setting it to a 1 stops the oscillator.

#### FREQUENCY TEST BIT

As shown in Table 2, bit 6 of the day byte is the frequency test bit. When the frequency test bit is set to logic 1 and the oscillator is running, the LSB of the seconds register will toggle at 512Hz. When the seconds register is being read, the DQ0 line will toggle at the 512Hz frequency as long as conditions for access remain valid (i.e.,  $\overline{CE}$  low,  $\overline{OE}$  low,  $\overline{WE}$  high, and address for seconds register remain valid and stable).

# CLOCK ACCURACY (DIP MODULE)

The DS1743 is guaranteed to keep time accuracy to within  $\pm 1$  minute per month at  $\pm 25^{\circ}$ C. The RTC is calibrated at the factory by Dallas Semiconductor using nonvolatile tuning elements, and does not require additional calibration. For this reason, methods of field clock calibration are not available and not necessary. The electrical environment also affects clock accuracy, so caution should be taken to place the RTC in the lowest-level EMI section of the PC board layout. For additional information, please refer to *Application Note 58: Crystal Considerations with Dallas Real-Time Clocks*.

# CLOCK ACCURACY (PowerCap MODULE)

The DS1743 and DS9034PCX are each individually tested for accuracy. Once mounted together, the module will typically keep time accuracy to within  $\pm 1.53$  minutes per month (35ppm) at  $\pm 25^{\circ}$ C. The electrical environment also affects clock accuracy, so caution should be taken to place the RTC in the lowest-level EMI section of the PC board layout. For additional information, please refer to *Application Note 58: Crystal Considerations with Dallas Real-Time Clocks*.

| ADDRESS | DATA                  |                |                       |                       |                       |                                                        |          |          | FUNCTION | RANGE |  |

|---------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|--------------------------------------------------------|----------|----------|----------|-------|--|

| ADDRESS | <b>B</b> <sub>7</sub> | B <sub>6</sub> | <b>B</b> <sub>5</sub> | <b>B</b> <sub>4</sub> | <b>B</b> <sub>3</sub> | $\mathbf{B}_2 \qquad \mathbf{B}_1 \qquad \mathbf{B}_0$ |          | FUNCTION | KANGE    |       |  |

| 1FFF    |                       | 10             | Year                  |                       |                       | Yea                                                    | r        |          | Year     | 00–99 |  |

| 1FFE    | Х                     | Х              | Х                     | 10<br>Month           |                       | Mont                                                   | h        |          | Month    | 01–12 |  |

| 1FFD    | Х                     | Х              | 10 1                  | Date                  |                       | Date                                                   | <b>)</b> |          | Date     | 01–31 |  |

| 1FFC    | BF                    | FT             | Х                     | Х                     | Х                     |                                                        | Day      |          | Day      | 01–07 |  |

| 1FFB    | Х                     | Х              | 10 I                  | Hour                  |                       | Hou                                                    | r        |          | Hour     | 00–23 |  |

| 1FFA    | Х                     | 1              | 10 Minute             | es                    |                       | Minutes                                                |          |          | Minutes  | 00–59 |  |

| 1FF9    | ŌSC                   | 1              | 0 Second              | ls                    | Seconds               |                                                        |          |          | Seconds  | 00–59 |  |

| 1FF8    | W                     | R              | 10 Ce                 | entury                | Century               |                                                        |          |          | Control  | 00–39 |  |

#### Table 2. Register Map

OSC = STOP BITR = READ BITFT = FREQUENCY TESTW = WRITE BITX = SEE NOTE BELOWBF = BATTERY FLAG

**Note:** All indicated "X" bits must be set to "0" when written to ensure proper clock operation.

## **RETRIEVING DATA FROM RAM OR CLOCK**

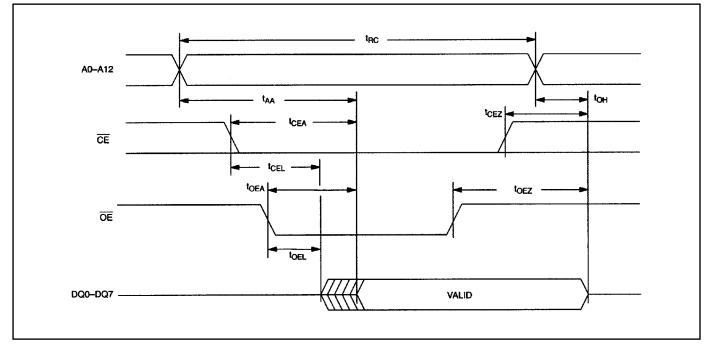

The DS1743 is in the read mode whenever  $\overline{OE}$  (output enable) is low,  $\overline{WE}$  (write enable) is high, and  $\overline{CE}$  (chip enable) is low. The device architecture allows ripple-through access to any of the address locations in the NV SRAM. Valid data will be available at the DQ pins within  $t_{AA}$  after the last address input is stable, providing that the,  $\overline{CE}$  and  $\overline{OE}$  access times and states are satisfied. If  $\overline{CE}$ , or  $\overline{OE}$  access times and states are not met, valid data will be available at the latter of chip enable access ( $t_{CEA}$ ) or at output enable access time ( $t_{CEA}$ ). The state of the data input/output pins (DQ) is controlled by  $\overline{CE}$  and  $\overline{OE}$ . If the outputs are activated before  $t_{AA}$ , the data lines are driven to an intermediate state until  $t_{AA}$ . If the address inputs are changed while  $\overline{CE}$  and  $\overline{OE}$  remain valid, output data will remain valid for output data hold time ( $t_{OH}$ ) but will then go indeterminate until the next address access.

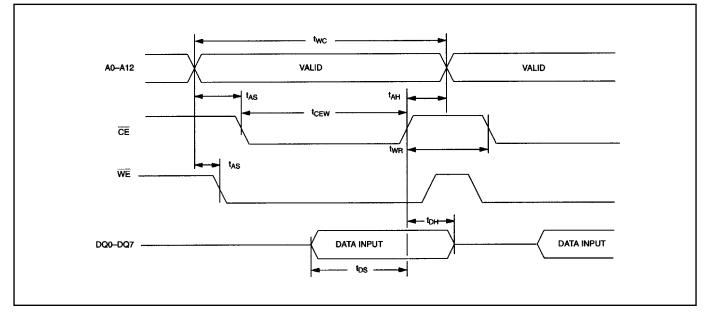

## WRITING DATA TO RAM OR CLOCK

The DS1743 is in the write mode whenever  $\overline{WE}$ , and  $\overline{CE}$  are in their active state. The start of a write is referenced to the latter occurring transition of  $\overline{WE}$ , on  $\overline{CE}$ . The addresses must be held valid throughout the cycle.  $\overline{CE}$  or  $\overline{WE}$  must return inactive for a minimum of  $t_{WR}$  prior to the initiation of another read or write cycle. Data in must be valid  $t_{DS}$  prior to the end of write and remain valid for  $t_{DH}$  afterward. In a typical application, the  $\overline{OE}$  signal will be high during a write cycle. However,  $\overline{OE}$  can be active provided that care is taken with the data bus to avoid bus contention. If  $\overline{OE}$  is low prior to  $\overline{WE}$  transitioning low the data bus can become active with read data defined by the address inputs. A low transition on  $\overline{WE}$  will then disable the outputs  $t_{WEZ}$  after  $\overline{WE}$  goes active.

## DATA-RETENTION MODE

The 5V device is fully accessible and data can be written or read only when  $V_{CC}$  is greater than  $V_{PF}$ . However, when  $V_{CC}$  is below the power-fail point,  $V_{PF}$ , (point at which write protection occurs) the internal clock registers and SRAM are blocked from any access. At this time (PowerCap only) the powerfail reset-output signal ( $\overline{RST}$ ) is driven active and remains active until  $V_{CC}$  returns to nominal levels. When  $V_{CC}$  falls below the battery switch point  $V_{SO}$  (battery supply level), device power is switched from the  $V_{CC}$ in to the backup battery. RTC operation and SRAM data are maintained from the battery until  $V_{CC}$  is returned to nominal levels.

The 3.3V device is fully accessible and data can be written or read only when  $V_{CC}$  is greater than  $V_{PF}$ . When  $V_{CC}$  falls below the power-fail point,  $V_{PF}$ , access to the device is inhibited. At this time the power-fail reset-output signal ( $\overline{RST}$ ) is driven active and remains active until  $V_{CC}$  returns to nominal levels. If  $V_{PF}$  is less than  $V_{SO}$ , the device power is switched from  $V_{CC}$  to the backup supply ( $V_{BAT}$ ) when  $V_{CC}$  drops below  $V_{PF}$ . If  $V_{PF}$  is greater than  $V_{SO}$ , the device power is switched from  $V_{CC}$  to the backup supply ( $V_{BAT}$ ) when  $V_{CC}$  drops below  $V_{SO}$ . RTC operation and SRAM data are maintained from the battery until  $V_{CC}$  is returned to nominal levels. The  $\overline{RST}$  (PowerCap only) signal is an open-drain output and requires a pullup resistor. Except for  $\overline{RST}$ , all control, data, and address signals must be powered down when  $V_{CC}$  is powered down.

# BATTERY LONGEVITY

The DS1743 has a lithium power source that is designed to provide energy for clock activity and clock and RAM data retention when the  $V_{CC}$  supply is not present. The capability of this internal power supply is sufficient to power the DS1743 continuously for the life of the equipment in which it is installed. For specification purposes, the life expectancy is 10 years at +25°C with the internal clock oscillator running in the absence of  $V_{CC}$  power. Each DS1743 is shipped from Dallas Semiconductor with its lithium energy source disconnected, guaranteeing full energy capacity. When  $V_{CC}$  is first applied at a level greater than  $V_{PF}$ , the lithium energy source is enabled for battery backup operation. Actual life expectancy of the DS1743 will be longer than 10 years since no lithium battery energy is consumed when  $V_{CC}$  is present.

## **BATTERY MONITOR**

The DS1743 constantly monitors the battery voltage of the internal battery. The battery flag bit (bit 7) of the day register is used to indicate the voltage level range of the battery. This bit is not writeable and should always be a 1 when read. If a 0 is ever present, an exhausted lithium energy source is indicated and both the contents of the RTC and RAM are questionable.

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground      | -0.3V to +6.0V                           |

|--------------------------------------------------|------------------------------------------|

| Operating Temperature Range                      |                                          |

| Storage Temperature Range                        |                                          |

| Soldering Temperature (EDIP) (leads, 10 seconds) |                                          |

| Soldering Temperature                            | See J-STD-020 Specification (See Note 8) |

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

#### **OPERATING RANGE**

| RANGE      | TEMP RANGE                     | V <sub>CC</sub>      |

|------------|--------------------------------|----------------------|

| Commercial | $0^{\circ}C$ to $+70^{\circ}C$ | 3.3V ±10% or 5V ±10% |

| Industrial | -40°C to +85°C                 | 3.3V ±10% or 5V ±10% |

## **RECOMMENDED DC OPERATING CONDITIONS**

$(T_A = Over the Operating Range.)$

| PARAMETER                  | SYMBOL          | CONDITIONS              | MIN  | ТҮР | MAX                      | UNITS | NOTES |

|----------------------------|-----------------|-------------------------|------|-----|--------------------------|-------|-------|

| Logic 1 Voltage All Inputs | V               | $V_{CC} = 5V \pm 10\%$  | 2.2  |     | V <sub>CC</sub><br>+0.3V | V     | 1     |

|                            | $V_{IH}$        | $V_{CC} = 3.3V$<br>±10% | 2.0  |     | V <sub>CC</sub><br>+0.3V | V     | 1     |

| Logic 0 Voltage All Inputs |                 | $V_{CC} = 5V \pm 10\%$  | -0.3 |     | +0.8                     | V     | 1     |

|                            | V <sub>IL</sub> | $V_{CC} = 3.3V$<br>±10% | -0.3 |     | +0.6                     | V     | 1     |

## DC ELECTRICAL CHARACTERISTICS (5V)

| ( | $(V_{CC} = 5.0V \pm 10\%)$ | $T_A$ = Over the Operating Range.) |  |

|---|----------------------------|------------------------------------|--|

|   |                            |                                    |  |

| PARAMETER                                                                                                             | SYMBOL           | MIN  | TYP       | MAX  | UNITS | NOTES |

|-----------------------------------------------------------------------------------------------------------------------|------------------|------|-----------|------|-------|-------|

| Active Supply Current                                                                                                 | I <sub>CC</sub>  |      | 15        | 50   | mA    | 2, 3  |

| $\frac{\text{TTL Standby Current}}{(\overline{\text{CE}} = \text{V}_{\text{IH}}, \text{CE2} = \text{V}_{\text{IL}})}$ | I <sub>CC1</sub> |      | 1         | 3    | mA    | 2, 3  |

| CMOS Standby Current<br>( $\overline{CE} \ge V_{CC} - 0.2V$ ; CE2 = GND + 0.2V)                                       | I <sub>CC2</sub> |      | 1         | 3    | mA    | 2, 3  |

| Input Leakage Current (Any Input)                                                                                     | $I_{IL}$         | -1   |           | +1   | μΑ    |       |

| Output Leakage Current (Any Output)                                                                                   | I <sub>OL</sub>  | -1   |           | +1   | μΑ    |       |

| Output Logic 1 Voltage<br>(I <sub>OUT</sub> = -1.0mA)                                                                 | V <sub>OH</sub>  | 2.4  |           |      |       | 1     |

| Output Logic 0 Voltage<br>$(I_{OUT} = 2.1 \text{mA})$                                                                 | V <sub>OL1</sub> |      |           | 0.4  |       | 1     |

| Write-Protection Voltage                                                                                              | $V_{ m PF}$      | 4.20 |           | 4.50 | V     | 1     |

| Battery Switchover Voltage                                                                                            | V <sub>SO</sub>  |      | $V_{BAT}$ |      |       | 1, 4  |

# DC ELECTRICAL CHARACTERISTICS (3.3V)

$(V_{cc} = 3.3V \pm 10\%, T_A = Over the Operating Range.)$

| PARAMETER                                                                                                              | SYMBOL           | MIN  | ТҮР                                       | MAX  | UNITS | NOTES |

|------------------------------------------------------------------------------------------------------------------------|------------------|------|-------------------------------------------|------|-------|-------|

| Active Supply Current                                                                                                  | I <sub>CC</sub>  |      | 10                                        | 30   | mA    | 2, 3  |

| TTL Standby Current ( $\overline{CE} = V_{IH}$ )                                                                       | I <sub>CC1</sub> |      | 0.7                                       | 2    | mA    | 2, 3  |

| $\begin{array}{l} CMOS \mbox{ Standby Current} \\ (\overline{CE} \geq V_{CC} - 0.2V; \\ CE2 = GND + 0.2V) \end{array}$ | I <sub>CC2</sub> |      | 0.7                                       | 2    | mA    | 2, 3  |

| Input Leakage Current<br>(Any Input)                                                                                   | I <sub>IL</sub>  | -1   |                                           | +1   | μΑ    |       |

| Output Leakage Current<br>(Any Output)                                                                                 | I <sub>OL</sub>  | -1   |                                           | +1   | μΑ    |       |

| Output Logic 1 Voltage<br>(I <sub>OUT</sub> = -1.0mA)                                                                  | V <sub>OH</sub>  | 2.4  |                                           |      |       | 1     |

| Output Logic 0 Voltage<br>(I <sub>OUT</sub> =2.1mA)                                                                    | V <sub>OL1</sub> |      |                                           | 0.4  |       | 1     |

| Write-Protection Voltage                                                                                               | $V_{PF}$         | 2.75 |                                           | 2.97 | V     | 1     |

| Battery Switchover Voltage                                                                                             | V <sub>SO</sub>  |      | V <sub>BAT</sub><br>or<br>V <sub>PF</sub> |      | V     | 1,4   |

## AC CHARACTERISTICS—READ CYCLE (5V)

(V<sub>CC</sub> = 5.0V  $\pm$ 10%, T<sub>A</sub> = Over the Operating Range.)

| PARAMETER                                 | SYMBOL            | 70ns |     | 85ns |     | 100ns |     | UNITS | NOTES |

|-------------------------------------------|-------------------|------|-----|------|-----|-------|-----|-------|-------|

|                                           |                   | MIN  | MAX | MIN  | MAX | MIN   | MAX |       |       |

| Read Cycle Time                           | t <sub>RC</sub>   | 70   |     | 85   |     | 100   |     | ns    |       |

| Address Access Time                       | t <sub>AA</sub>   |      | 70  |      | 85  |       | 100 | ns    |       |

| $\overline{\text{CE}}$ to CE2 to DQ Low-Z | t <sub>CEL</sub>  | 5    |     | 5    |     | 5     |     | ns    | 5     |

| <b>CE</b> Access Time                     | t <sub>CEA</sub>  |      | 70  |      | 85  |       | 100 | ns    | 5     |

| CE2 Access Time                           | t <sub>CE2A</sub> |      | 80  |      | 95  |       | 105 | ns    | 5     |

| CE and CE2 Data-Off<br>Time               | t <sub>CEZ</sub>  |      | 25  |      | 30  |       | 35  | ns    |       |

| $\overline{OE}$ to DQ Low-Z               | t <sub>OEL</sub>  | 5    |     | 5    |     | 5     |     | ns    |       |

| OE Access Time                            | t <sub>OEA</sub>  |      | 35  |      | 45  |       | 55  | ns    |       |

| OE Data-Off Time                          | t <sub>OEZ</sub>  |      | 25  |      | 30  |       | 35  | ns    |       |

| Output Hold from<br>Address               | t <sub>OH</sub>   | 5    |     | 5    |     | 5     |     | ns    |       |

# AC CHARACTERISTICS—READ CYCLE (3.3V)

(V<sub>cc</sub> = 3.3V ±10%, T<sub>A</sub> = Over the Operating Range.)

|                                                |                  |       | ACC |       |     |       |       |

|------------------------------------------------|------------------|-------|-----|-------|-----|-------|-------|

| PARAMETER                                      | SYMBOL           | 120ns |     | 150ns |     | UNITS | NOTES |

|                                                |                  | MIN   | MAX | MIN   | MAX |       |       |

| Read Cycle Time                                | t <sub>RC</sub>  | 120   |     | 150   |     | ns    |       |

| Address Access Time                            | t <sub>AA</sub>  |       | 120 |       | 150 | ns    |       |

| $\overline{\text{CE}}$ and CE2 Low to DQ Low-Z | $t_{\rm CEL}$    | 5     |     | 5     |     | ns    | 5     |

| $\overline{\text{CE}}$ and CE2 Access Time     | t <sub>CEA</sub> |       | 120 |       | 150 | ns    | 5     |

| $\overline{\text{CE}}$ and CE2 Data-Off time   | $t_{CEZ}$        |       | 40  |       | 50  | ns    | 5     |

| $\overline{OE}$ Low to DQ Low-Z                | t <sub>OEL</sub> | 5     |     | 5     |     | ns    |       |

| OE Access Time                                 | t <sub>OEA</sub> |       | 100 |       | 130 | ns    |       |

| OE Data-Off Time                               | t <sub>OEZ</sub> |       | 35  |       | 35  | ns    |       |

| Output Hold from Address                       | t <sub>OH</sub>  | 5     |     | 5     |     | ns    |       |

## **READ CYCLE TIMING DIAGRAM**

# AC CHARACTERISTICS—WRITE CYCLE (5V)

(V<sub>CC</sub> = 5.0V  $\pm$ 10%, T<sub>A</sub> = Over the Operating Range.)

|                                    |                   | ACCESS |     |      |     |       |     |       |       |

|------------------------------------|-------------------|--------|-----|------|-----|-------|-----|-------|-------|

| PARAMETER                          | SYMBOL            | 70ns   |     | 85ns |     | 100ns |     | UNITS | NOTES |

|                                    |                   | MIN    | MAX | MIN  | MAX | MIN   | MAX |       |       |

| Write Cycle Time                   | t <sub>WC</sub>   | 70     |     | 85   |     | 100   |     | ns    |       |

| Address Setup Time                 | t <sub>AS</sub>   | 0      |     | 0    |     | 0     |     | ns    | 5     |

| WE Pulse Width                     | t <sub>WEW</sub>  | 50     |     | 65   |     | 70    |     | ns    |       |

| $\overline{\text{CE}}$ Pulse Width | t <sub>CEW</sub>  | 60     |     | 70   |     | 75    |     | ns    | 5     |

| CE2 Pulse Width                    | t <sub>CE2W</sub> | 65     |     | 75   |     | 85    |     | ns    | 5     |

| Data Setup Time                    | t <sub>DS</sub>   | 30     |     | 35   |     | 40    |     | ns    | 5     |

| Data Hold Time $\overline{CE}$     | t <sub>DH</sub>   | 0      |     | 0    |     | 0     |     | ns    | 5     |

| Data Hold Time CE2                 | t <sub>DH</sub>   | 8      |     | 8    |     | 8     |     | ns    | 5     |

| Address Hold Time                  | t <sub>AH</sub>   | 5      |     | 5    |     | 5     |     | ns    | 5     |

| WE Data-Off Time                   | t <sub>WEZ</sub>  |        | 25  |      | 30  |       | 35  | ns    |       |

| Write Recovery Time                | t <sub>WR</sub>   | 10     |     | 10   |     | 10    |     | ns    |       |

# AC CHARACTERISTICS—WRITE CYCLE (3.3V)

( $V_{cc}$  = 3.3V ±10%, T<sub>A</sub> = Over the Operating Range.)

|                                            |                  |       | ACC | UNITS | NOTES |       |   |

|--------------------------------------------|------------------|-------|-----|-------|-------|-------|---|

| PARAMETER                                  | SYMBOL           | 120ns |     |       |       | 150ns |   |

|                                            |                  | MIN   | MAX | MIN   | MAX   |       |   |

| Write Cycle Time                           | t <sub>WC</sub>  | 120   |     | 150   |       | ns    |   |

| Address Setup Time                         | t <sub>AS</sub>  | 0     |     | 0     |       | ns    | 5 |

| WE Pulse Width                             | $t_{\rm WEW}$    | 100   |     | 130   |       | ns    |   |

| $\overline{\text{CE}}$ and CE2 Pulse Width | t <sub>CEW</sub> | 110   |     | 140   |       | ns    | 5 |

| Data Setup Time                            | t <sub>DS</sub>  | 80    |     | 90    |       | ns    | 5 |

| Data Hold Time $\overline{CE}$             | t <sub>DH</sub>  | 0     |     | 0     |       | ns    | 5 |

| Data Hold Time CE2                         | t <sub>DH</sub>  | 10    |     | 10    |       | ns    | 5 |

| Address Hold Time                          | t <sub>AH</sub>  | 0     |     | 0     |       | ns    | 5 |

| WE Data-Off Time                           | t <sub>WEZ</sub> |       | 40  |       | 50    | ns    |   |

| Write Recovery Time                        | t <sub>WR</sub>  | 10    |     | 10    |       | ns    |   |

# WRITE CYCLE TIMING—WRITE-ENABLE CONTROLLED (See Note 5)

# WRITE CYCLE TIMING— CE /CE2-CONTROLLED (See Note 5)

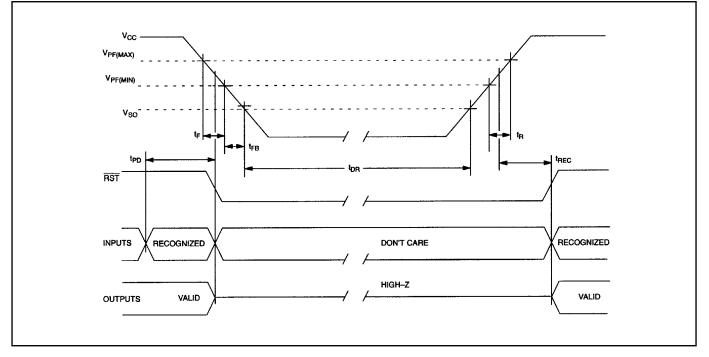

## POWER-UP/DOWN CHARACTERISTICS—5V

$(V_{CC} = 5.0V \pm 10\%, T_A = Over the Operating Range.)$

| PARAMETER                                                                                                           | SYMBOL           | MIN | ТҮР | MAX | UNITS | NOTES |

|---------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-------|-------|

| $\overline{\text{CE}}$ or $\overline{\text{WE}}$ at V <sub>IH</sub> , CE2 at V <sub>IL</sub> , Before<br>Power-Down | t <sub>PD</sub>  | 0   |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{PF(MAX)}$ to $V_{PF(MIN)}$                                                                  | t <sub>F</sub>   | 300 |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{\text{PF}(\text{MIN})}$ to $V_{SO}$                                                         | $t_{\rm FB}$     | 10  |     |     | μs    |       |

| V <sub>CC</sub> Rise Time: V <sub>PF(MIN)</sub> to V <sub>PF(MAX)</sub>                                             | t <sub>R</sub>   | 0   |     |     | μs    |       |

| Power-Up Recover Time                                                                                               | t <sub>REC</sub> |     |     | 35  | ms    |       |

| Expected Data-Retention Time<br>(Oscillator On)                                                                     | t <sub>DR</sub>  | 10  |     |     | years | 6, 7  |

# POWER-UP/DOWN TIMING (5V DEVICE)

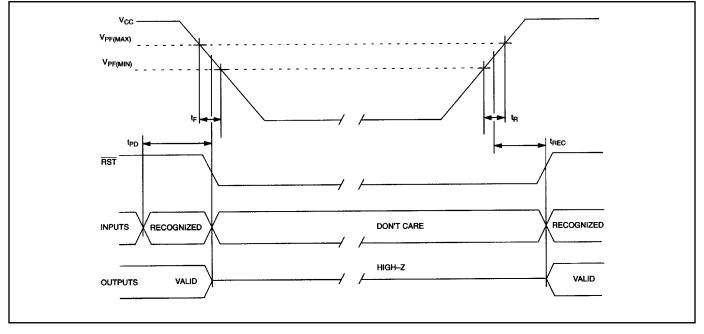

## POWER-UP/DOWN CHARACTERISTICS—3.3V

(V<sub>cc</sub> = 3.3V ±10%, T<sub>A</sub> = Over the Operating Range.)

|                                                                              | <u> </u>         | - / |     |     |       |       |

|------------------------------------------------------------------------------|------------------|-----|-----|-----|-------|-------|

| PARAMETER                                                                    | SYMBOL           | MIN | ТҮР | MAX | UNITS | NOTES |

| $\overline{CE}$ or $\overline{WE}$ at V <sub>IH</sub> , Before<br>Power-Down | t <sub>PD</sub>  | 0   |     |     | μs    |       |

| $V_{CC}$ Fall Time: $V_{PF(MAX)}$ to $V_{PF(MIN)}$                           | t <sub>F</sub>   | 300 |     |     | μs    |       |

| $V_{CC}$ Rise Time: $V_{PF(MIN)}$ to $V_{PF(MAX)}$                           | t <sub>R</sub>   | 0   |     |     | μs    |       |

| $V_{PF}$ to $\overline{RST}$ High                                            | t <sub>REC</sub> |     |     | 35  | ms    |       |

| Expected Data-Retention Time<br>(Oscillator On)                              | t <sub>DR</sub>  | 10  |     |     | years | 6, 7  |

### **POWER-UP/DOWN WAVEFORM TIMING (3.3V DEVICE)**

## CAPACITANCE

$(T_A = +25^{\circ}C)$

| PARAMETER                      | SYMBOL          | MIN | ТҮР | MAX | UNITS | NOTES |

|--------------------------------|-----------------|-----|-----|-----|-------|-------|

| Capacitance on All Input Pins  | C <sub>IN</sub> |     |     | 7   | pF    |       |

| Capacitance on All Output Pins | Co              |     |     | 10  | pF    |       |

## AC TEST CONDITIONS

Output Load: 50 pF + 1TTL Gate Input Pulse Levels: 0 to 3.0V Timing Measurement Reference Levels: Input: 1.5V Output: 1.5V Input Pulse Rise and Fall Times: 5ns

# NOTES:

- 1) Voltages are referenced to ground.

- 2) Typical values are at +25°C and nominal supplies.

- 3) Outputs are open.

- 4) Battery switchover occurs at the lower of either the battery terminal voltage or  $V_{PF}$ .

- 5) The CE2 control signal functions the same as the  $\overline{CE}$  signal except that the logic levels for active and inactive levels are opposite. If CE2 is used to terminate a write, the CE2 data hold time (t<sub>DH</sub>) applies.

- 6) Data-retention time is at  $+25^{\circ}$ C.

- 7) Each DS1743 has a built-in switch that disconnects the lithium source until  $V_{CC}$  is first applied by the user. The expected  $t_{DR}$  is defined for DIP modules as a cumulative time in the absence of  $V_{CC}$  starting from the time power is first applied by the user.

- 8) RTC Encapsulated DIP Modules (EDIP) can be successfully processed through conventional wavesoldering techniques as long as temperatures as long as temperature exposure to the lithium energy source contained within does not exceed +85°C. Post-solder cleaning with water-washing techniques is acceptable, provided that ultrasonic vibration is not used. See the PowerCap package drawing for details regarding the PowerCap package.

#### PACKAGE INFORMATION

For the latest package outline information, go to www.maxim-ic.com/DallasPackInfo.

28-pin 740 EDIP Module Document number: 56-G0002-001

32-pin PowerCap Module Document number: <u>56-G0003-001</u>

16 of 16

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 © 2006 Maxim Integrated Products

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor.

## **DS1743**

#### **Part Number Table**

| Part Number   |        | Buy<br>Direct | Package: TYPE PINS SIZE<br>DRAWING CODE/VAR *                                 | Temp           | RoHS/Lead-Free?<br>Materials Analysis     |

|---------------|--------|---------------|-------------------------------------------------------------------------------|----------------|-------------------------------------------|

| DS1743-85+    | Sample | Buy           | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)<br>Use pkgcode/variation: MDF28+2* | 0°C to +70°C   | RoHS/Lead-Free: Yes<br>Materials Analysis |

|               |        |               | Use procode/variation. MDF28+2*                                               |                | Materials Analysis                        |

| DS1743-85IND+ |        | Buy           | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)                                    | -40°C to +85°C | RoHS/Lead-Free: Yes                       |

|               |        |               | Use pkgcode/variation: MDF28+2*                                               |                | Materials Analysis                        |

| DS1743-100    | [      | Buy           | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)<br>Use pkgcode/variation: MDF28-2* | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743-100+   | Sample | Buy           | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)                                    | 0°C to +70°C   | RoHS/Lead-Free: Yes                       |

|               |        |               | Use pkgcode/variation: MDF28+2*                                               |                | Materials Analysis                        |

| DS1743W-120   |        | Buy           | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)<br>Use pkgcode/variation: MDF28-2* | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743W-150   | [      | Buy           | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)                                    | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

|                  |            | Use pkgcode/variation: MDF28-2*                                                |                |                                           |

|------------------|------------|--------------------------------------------------------------------------------|----------------|-------------------------------------------|

| DS1743W-120+     | Sample Buy | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)<br>Use pkgcode/variation: MDF28+2*  | 0°C to +70°C   | RoHS/Lead-Free: Yes<br>Materials Analysis |

|                  |            |                                                                                |                | · · · · · · · · · · · · · · · · · · ·     |

| DS1743W-150+     | Sample Buy | MOD;28 pin;600<br>Dwa: 56-G0002-001A (PDF)                                     | 0°C to +70°C   | RoHS/Lead-Free: Yes                       |

|                  |            | Use pkgcode/variation: MDF28+2*                                                |                | Materials Analysis                        |

| DS1743W-120IND+  | Buy        | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)                                     | 0°C to +70°C   | RoHS/Lead-Free: Yes                       |

|                  |            | Use pkgcode/variation: MDF28+2*                                                |                | Materials Analysis                        |

| DS1743W-120 IND  | Buy        | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)<br>Use pkgcode/variation: MDF28-2*  | -40°C to +85°C | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743-100 IND   | Buy        | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)<br>Use pkgcode/variation: MDF28-2*  | -40°C to +85°C | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743-100IND+   | Buy        | MOD;28 pin;600<br>Dwg: 56-G0002-001A (PDF)                                     | -40°C to +85°C | RoHS/Lead-Free: Yes                       |

|                  |            | Use pkgcode/variation: MDF28+2*                                                |                | Materials Analysis                        |

| DS1743WP-120IND+ | Buy        | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)                                  | -40°C to +85°C | RoHS/Lead-Free: Yes                       |

|                  |            | Use pkgcode/variation: PC1+2*                                                  |                | Materials Analysis                        |

| DS1743WP-120+    | Sample Buy | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)                                  | 0°C to +70°C   | RoHS/Lead-Free: Yes                       |

|                  |            | Use pkgcode/variation: PC1+2*                                                  |                | Materials Analysis                        |

| DS1743WP-150     | Buy        | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1-2* | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743WP-120     | Buy        | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1-2* | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743WP-150+    | Sample Buy | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)                                  | 0°C to +70°C   | RoHS/Lead-Free: Yes                       |

|                  |            | Use pkgcode/variation: PC1+2*                                                  |                | Materials Analysis                        |

| DS1743WP-120IND  | Buy        | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1-2* | -40°C to +85°C | RoHS/Lead-Free: No<br>Materials Analysis  |

Didn't Find What You Need?

Copyright © 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy

### DS1743P

#### **Part Number Table**

| Part Number     |        | Buy<br>Direct | Package: TYPE PINS SIZE<br>DRAWING CODE/VAR *                                  | Temp           | RoHS/Lead-Free?<br>Materials Analysis     |

|-----------------|--------|---------------|--------------------------------------------------------------------------------|----------------|-------------------------------------------|

| DS1743P-C01+    | [      | Buy           | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1+2* | 0°C to +70°C   | RoHS/Lead-Free: Yes<br>Materials Analysis |

| DS1743P-85+     | Sample | Buy           | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1+2* | 0°C to +70°C   | RoHS/Lead-Free: Yes<br>Materials Analysis |

| DS1743P-85IND+  | [      | Buy           | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1+2* | -40°C to +85°C | RoHS/Lead-Free: Yes<br>Materials Analysis |

| DS1743P-100     | [      | Buy           | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1-2* | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743P-100IND  | [      | Buy           | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)<br>Use pkgcode/variation: PC1-2* | 0°C to +70°C   | RoHS/Lead-Free: No<br>Materials Analysis  |

| DS1743P-100IND+ | [      | Buy           | PWRCP;34 pin;960<br>Dwg: 56-G0003-001A1 (PDF)                                  | 0°C to +70°C   | RoHS/Lead-Free: Yes                       |

|                     |                    | Use pkgcode/va                  | riation: PC1+2* |              | Materials Analysis  |  |  |

|---------------------|--------------------|---------------------------------|-----------------|--------------|---------------------|--|--|

| DS1743P-100+        | Sample Buy         | PWRCP;34 pin;9<br>Dwg: 56-G0003 |                 | 0°C to +70°C | RoHS/Lead-Free: Yes |  |  |

|                     |                    | Use pkgcode/va                  | riation: PC1+2* |              | Materials Analysis  |  |  |

| Didn't Find What Yo | u Need?            |                                 |                 |              |                     |  |  |

| 4.                  | CONTACT US: FEEDBA | CK, QUESTIONS                   | MATE THIS PAGE  |              | IIS PAGE            |  |  |

Copyright © 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy