#### **General Description**

The MAX9723 stereo DirectDrive<sup>™</sup> headphone amplifier with BassMax and volume control is ideal for portable audio applications where space is at a premium and performance is essential. The MAX9723 operates from a single 1.8V to 3.6V power supply and includes features that reduce external component count, system cost, board space, and improves audio reproduction.

The headphone amplifier uses Maxim's patented DirectDrive architecture that produces a ground-referenced output from a single supply, eliminating the need for large DC-blocking capacitors. The headphone amplifiers deliver 62mW into a 16 $\Omega$  load, feature low 0.006% THD+N, and high 90dB PSRR. The MAX9723 features Maxim's industry-leading click-and-pop suppression.

The BassMax feature boosts the bass response of the amplifier, improving audio reproduction when using inexpensive headphones. The integrated volume control features 32 discrete volume levels, eliminating the need for an external potentiometer. BassMax and the volume control are enabled through the I<sup>2</sup>C\*/SMBus<sup>™</sup>-compatible interface. Shutdown is controlled through either the hardware or software interfaces.

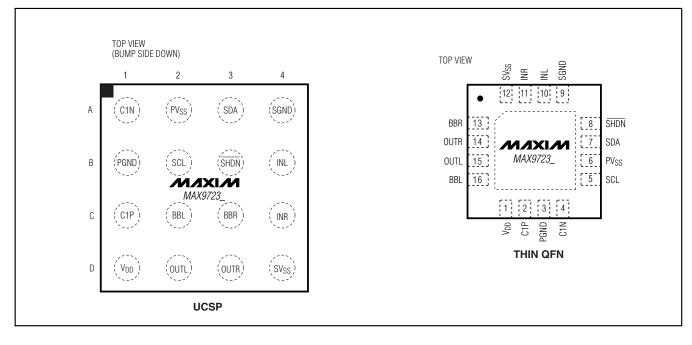

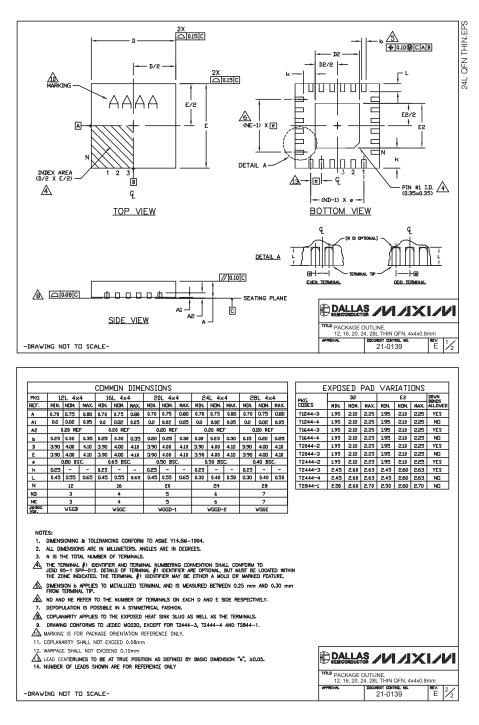

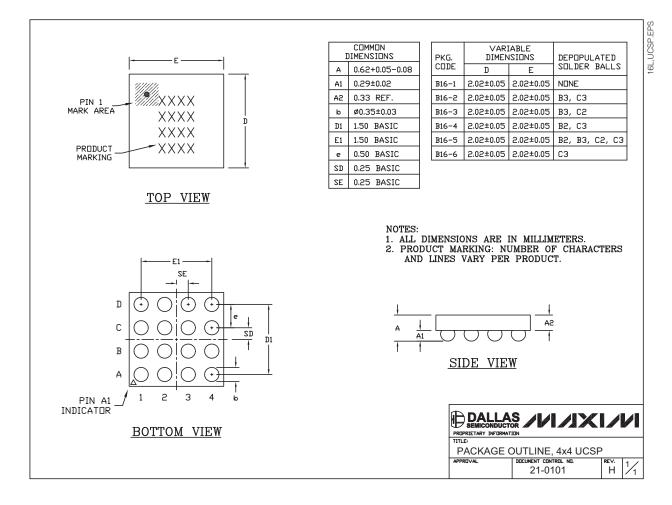

The MAX9723 consumes only 3.7mA of supply current at 1.8V, provides short-circuit and thermal-overload protection, and is fully specified over the extended -40°C to +85°C temperature range. The MAX9723 is available in a tiny (2mm x 2mm x 0.62mm) 16-bump chip-scale package (UCSP<sup>TM</sup>) or 16-pin thin QFN (4mm x 4mm x 0.8mm) package.

#### **Applications**

PDA Audio Portable CD Players Mini Disc Players Automotive Multimedia MP3-Enabled Cellular Phones MP3 Players

#### **Selector Guide**

| PART     | SLAVE ADDRESS | MAXIMUM GAIN (dB) |

|----------|---------------|-------------------|

| MAX9723A | 1001100       | 0                 |

| MAX9723B | 1001101       | 0                 |

| MAX9723C | 1001100       | +6                |

| MAX9723D | 1001101       | +6                |

\*Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc. or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

SMBus is a trademark of Intel Corp.

UCSP is a trademark of Maxim Integrated Products, Inc.

####

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### \_ Features

62mW, DirectDrive Headphone Amplifier Eliminates Bulky DC-Blocking Capacitors

ΜΛΧΙΜ

- ♦ 1.8V to 3.6V Single-Supply Operation

- Integrated 32-Level Volume Control

- High 90dB PSRR at 1kHz

- Low 0.006% THD+N

- Industry-Leading Click-and-Pop Suppression

- ♦ ±8kV HBM ESD-Protected Headphone Outputs

- Short-Circuit and Thermal-Overload Protection

- Low-Power Shutdown Mode (5µA)

- Software-Enabled Bass Boost (BassMax)

- ♦ I<sup>2</sup>C/SMBus-Compatible Interface

- Available in Space-Saving, Thermally Efficient Packages:

16-Bump UCSP (2mm x 2mm x 0.62mm) 16-Pin Thin QFN (4mm x 4mm x 0.8mm)

#### **Ordering Information**

| TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE                                                            |

|----------------|-----------------|------------------------------------------------------------------------|

| -40°C to +85°C | 16 UCSP-16      | B16-1                                                                  |

| -40°C to +85°C | 16 TQFN         | T1644-4                                                                |

|                | -40°C to +85°C  | TEMP RANGE         PACKAGE           -40°C to +85°C         16 UCSP-16 |

\*\*Replace the '\_' with the one-letter code that denotes the slave address and maximum programmable gain. See the Selector Guide.

+Denotes lead-free package.

\*Future product—contact factory for availability.

Pin Configurations appear at end of data sheet.

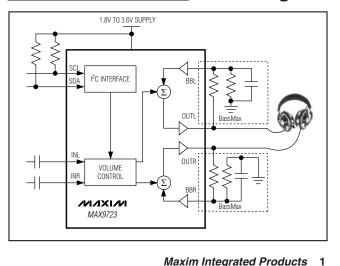

#### **Block Diagram**

#### **ABSOLUTE MAXIMUM RATINGS**

| SGND to PGND                     | -0.3V to +0.3V                          |

|----------------------------------|-----------------------------------------|

| V <sub>DD</sub> to PGND          | -0.3V to +4V                            |

| PVss to SVss                     | 0.3V to +0.3V                           |

| C1P to PGND                      | 0.3V to (V <sub>DD</sub> + 0.3V)        |

| C1N to PGND                      | (PV <sub>SS</sub> - 0.3V) to +0.3V      |

| PVss, SVss to PGND               | +0.3V to -4V                            |

| IN_ to SGND                      | $(SV_{SS} - 0.3V)$ to $(V_{DD} + 0.3V)$ |

| SDA, SCL to PGND                 | -0.3V to +4V                            |

| SHDN to PGND                     | 0.3V to (V <sub>DD</sub> + 0.3V)        |

| OUT_ to SGND                     | 3V to +3V                               |

| BB_ to SGND                      | 2V to +2V                               |

| Duration of OUT Short Circuit to | _GNDContinuous                          |

| Continuous Current Into/Out of:                                                      |

|--------------------------------------------------------------------------------------|

| V <sub>DD</sub> , C1P, PGND, C1N, PV <sub>SS</sub> , SV <sub>SS</sub> , or OUT±0.85A |

| Any Other Pin±20mA                                                                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                |

| 4 x 4 UCSP (derate 8.2mW/°C above +70°C)659.2mW                                      |

| 16-Pin Thin QFN (derate 16.9mW/°C above +70°C)1349mW                                 |

| Operating Temperature Range40°C to +85°C                                             |

| Junction Temperature+150°C                                                           |

| Storage Temperature Range65°C to +150°C                                              |

| Bump Temperature (soldering)                                                         |

| Reflow+230°C                                                                         |

| Lead Temperature (soldering, 10s)+300°C                                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = \overline{SHDN} = 3V, PGND = SGND = 0V, C1 = C2 = 1\mu F, BB_ = 0V. gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT_ and SGND where specified. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)$

| PARAMETER                    | SYMBOL             |                               | CON   | IDITIONS                                                          | MIN | ТҮР  | МАХ  | UNITS |

|------------------------------|--------------------|-------------------------------|-------|-------------------------------------------------------------------|-----|------|------|-------|

| GENERAL                      |                    |                               |       |                                                                   |     |      |      |       |

| Supply Voltage Range         | V <sub>DD</sub>    |                               |       |                                                                   | 1.8 |      | 3.6  | V     |

| Quiescent Supply Current     | IDD                | No load                       |       |                                                                   |     | 4    | 6.5  | mA    |

| Shutdown Supply Current      | IDD_SHDN           | $V_{\overline{SHDN}} = 0^{V}$ | V     |                                                                   |     | 5    | 8.5  | μΑ    |

| Turn-On Time                 | ton                |                               |       |                                                                   |     | 200  |      | μs    |

| Turn-Off Time                | tOFF               |                               |       |                                                                   |     | 35   |      | μs    |

| Thermal Shutdown Threshold   | T <sub>THRES</sub> |                               |       |                                                                   |     | +143 |      | °C    |

| Thermal Shutdown Hysteresis  | T <sub>HYST</sub>  |                               |       |                                                                   |     | 12   |      | °C    |

| HEADPHONE AMPLIFIER          |                    |                               |       |                                                                   |     |      |      |       |

| Output Offset Voltage        | Vos                | Measured between              |       | Gain = 0dB,<br>MAX9723A/<br>MAX9723B                              |     | ±0.7 | ±4.5 | mV    |

| Output Onset Voltage         | VUS                | OUT_ and S<br>(Note 2)        |       | Gain = +6dB,<br>MAX9723C/<br>MAX9723D                             |     | ±0.8 | ±5   | IIIV  |

| Input Resistance             | RIN                | All volume I                  | evels |                                                                   | 10  | 17   | 27   | kΩ    |

| BBR, BBL Input Bias Current  | IBIAS_BB           |                               |       |                                                                   |     | ±10  | ±100 | nA    |

|                              |                    |                               | DC, V | / <sub>DD</sub> = 1.8V to 3.6V                                    | 73  | 90   |      |       |

| Power-Supply Rejection Ratio |                    |                               |       | f = 217Hz, 100mV <sub>P-P</sub> ripple,<br>V <sub>DD</sub> = 3.0V |     | 87   |      |       |

|                              | PSRR               | (Note 2)                      |       | Hz, 100mV <sub>P-P</sub> ripple,<br>= 3.0V                        |     | 86   |      | dB    |

|                              |                    |                               |       | kHz, 100mVp₋p ripple,<br>= 3.0V                                   |     | 61   |      |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = \overline{SHDN} = 3V, PGND = SGND = 0V, C1 = C2 = 1\mu F, BB_ = 0V. gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT_ and SGND where specified. TA = T_{MIN} to T_{MAX}, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)$

| PARAMETER                          | SYMBOL          |                                                                                                                               | CONE                                                   | DITIONS                   |                    | MIN                      | ТҮР   | МАХ                      | UNITS |

|------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------|--------------------|--------------------------|-------|--------------------------|-------|

|                                    | D               | THD+N = 1%,                                                                                                                   |                                                        | $R_L = 32\Omega$          | 2                  |                          | 59    |                          |       |

| Output Power                       | Pout            | f <sub>IN</sub> = 1kHz                                                                                                        |                                                        | $R_L = 16\Omega$ (Note 5) |                    | 38                       | 60    |                          | mW    |

| Total Harmonic Distortion Plus     |                 | $R_L = 16\Omega, P_{OU}$                                                                                                      | IT = 35                                                | imW, f <sub>IN</sub> =    | = 1kHz             |                          | 0.006 |                          | 0/    |

| Noise                              | THD+N           | $R_L = 32\Omega$ , $P_{OU}$                                                                                                   | $R_L = 32\Omega$ , $P_{OUT} = 45$ mW, $f_{IN} = 1$ kHz |                           |                    | 0.004                    |       | %                        |       |

|                                    |                 | MAX9723A/                                                                                                                     |                                                        | Gain rang                 | ge bit 5 = 1       |                          | 0     |                          | dD    |

| Maximum Gain                       | <b>A.</b>       | MAX9723B                                                                                                                      |                                                        | Gain rang                 | ge bit 5 = 0       |                          | -5    |                          | dB    |

| Maximum Gain                       | Amax            | MAX9723C/                                                                                                                     |                                                        | Gain rang                 | ge bit 5 = 1       |                          | +6    |                          | dB    |

|                                    |                 | MAX9723D                                                                                                                      |                                                        | Gain rang                 | ge bit 5 = 0       |                          | +1    |                          | uв    |

| Signal-to-Noise Ratio              | SNR             | $R_L = 32\Omega$ ,                                                                                                            | <u> </u> _                                             | BW = 22                   | Hz to 22kHz        |                          | 99    |                          | dB    |

|                                    | ONIT            | $V_{OUT} = 1V_{RMS}$                                                                                                          |                                                        | A-weight                  | ed                 |                          | 100   |                          | GD    |

| Slew Rate                          | SR              |                                                                                                                               |                                                        |                           |                    |                          | 0.35  |                          | V/µs  |

| Capacitive Drive                   |                 | No sustained c                                                                                                                | scillat                                                | ions                      |                    |                          | 300   |                          | pF    |

| Output Resistance in Shutdown      | ROUT_SHDN       | V <del>SHDN</del> = 0V, m<br>SGND                                                                                             | neasur                                                 | ed from C                 | OUT_ to            |                          | 20    |                          | kΩ    |

| Output Capacitance in Shutdown     | COUT_SHDN       | V <u>SHDN</u> = 0V, measured from OUT_ to<br>SGND                                                                             |                                                        |                           |                    | 60                       |       | pF                       |       |

|                                    | Кср             | R <sub>L</sub> = 32Ω,<br>peak voltage,<br>A-weighted,<br>32 samples<br>per second                                             | MAX9723A/                                              |                           | Into<br>shutdown   |                          | -69   |                          |       |

|                                    |                 |                                                                                                                               | MAXS                                                   | 9723B                     | Out of<br>shutdown | -71                      |       |                          |       |

| Click/Pop Level                    |                 |                                                                                                                               | MAX9723                                                | 9723C/                    | Into<br>shutdown   |                          | -70   |                          | dB    |

|                                    |                 | (Notes 2, 4)                                                                                                                  | MAX                                                    | MAX9723D                  | Out of<br>shutdown |                          | -69   |                          | 1     |

| Charge-Pump Switching<br>Frequency | fCP             |                                                                                                                               | 1                                                      |                           |                    | 505                      | 600   | 700                      | kHz   |

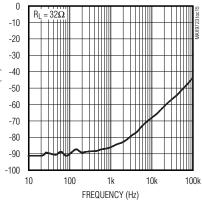

| Crosstalk                          | XTALK           | L to R or R to L, f = 10kHz,<br>V <sub>OUT</sub> = 1V <sub>P-P</sub> , R <sub>L</sub> = 32 $\Omega$ , both channels<br>loaded |                                                        |                           |                    | 80                       |       | dB                       |       |

| DIGITAL INPUTS (SHDN, SDA, S       | CL)             |                                                                                                                               |                                                        |                           |                    |                          |       |                          |       |

| Input High Voltage                 | VIH             |                                                                                                                               |                                                        |                           |                    | 0.7 x<br>V <sub>DD</sub> |       |                          | V     |

| Input Low Voltage                  | V <sub>IL</sub> |                                                                                                                               |                                                        |                           |                    |                          |       | 0.3 x<br>V <sub>DD</sub> | V     |

| Input Leakage Current              |                 |                                                                                                                               |                                                        |                           |                    |                          |       | ±1                       | μA    |

| DIGITAL OUTPUTS (SDA)              |                 | •                                                                                                                             |                                                        |                           |                    |                          |       |                          |       |

| Output Low Voltage                 | Vol             | $I_{OL} = 3mA$                                                                                                                |                                                        |                           |                    |                          |       | 0.4                      | V     |

| Output High Current                | ЮН              | V <sub>SDA</sub> = V <sub>DD</sub>                                                                                            |                                                        |                           |                    |                          |       | 1                        | μA    |

#### TIMING CHARACTERISTICS

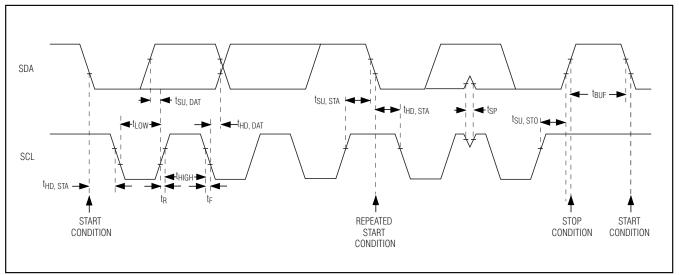

$(V_{DD} = \overline{SHDN} = 3V, PGND = SGND = 0V, C1 = C2 = 1\mu F, BB_ = 0V, gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT_ and SGND where specified. TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at TA = +25°C, see Timing Diagram.) (Notes 1, 3)$

| PARAMETER                                          | SYMBOL              | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|----------------------------------------------------|---------------------|------------|-----|-----|-----|-------|

| Serial Clock Frequency                             | fSCL                |            | 0   |     | 400 | kHz   |

| Bus Free Time Between a STOP and a START Condition | tBUF                |            | 1.3 |     |     | μs    |

| START Condition Hold Time                          | <sup>t</sup> HD:STA |            | 0.6 |     |     | μs    |

| Low Period of the SCL Clock                        | tLOW                |            | 1.3 |     |     | μs    |

| High Period of the SCL Clock                       | thigh               |            | 0.6 |     |     | μs    |

| Setup Time for a Repeated START Condition          | <sup>t</sup> SU:STA |            | 0.6 |     |     | μs    |

| Data Hold Time                                     | thd:dat             |            | 0   |     | 0.9 | μs    |

| Data Setup Time                                    | tsu:dat             |            | 100 |     |     | ns    |

| Maximum Rise Time of SDA and SCL Signals           | tr                  |            |     | 300 |     | ns    |

| Maximum Fall Time of SDA and SCL Signals           | tf                  |            |     | 300 |     | ns    |

| Setup Time for STOP Condition                      | tsu:sto             |            | 0.6 |     |     | μs    |

| Pulse Width of Suppressed Spike                    | tsp                 |            |     | 100 |     | ns    |

| Maximum Capacitive Load for<br>Each Bus Line       | CL_BUS              |            |     | 400 |     | pF    |

**Note 1:** All specifications are 100% tested at  $T_A = +25^{\circ}C$ . Temperature limits are guaranteed by design.

**Note 2:** Inputs AC-coupled to SGND.

Note 3: Guaranteed by design.

Note 4: Headphone mode testing performed with a 32Ω resistive load connected to GND. Mode transitions are controlled by <u>SHDN</u>. The K<sub>CP</sub> level is calculated as: 20 x log [(level peak voltage during mode transition, no input signal)/(peak voltage under normal operation at rated power)]. Units are expressed in dB.

**Note 5:** Output power MIN is specified at  $T_A = +25^{\circ}C$ .

OUTPUT POWER (mW)

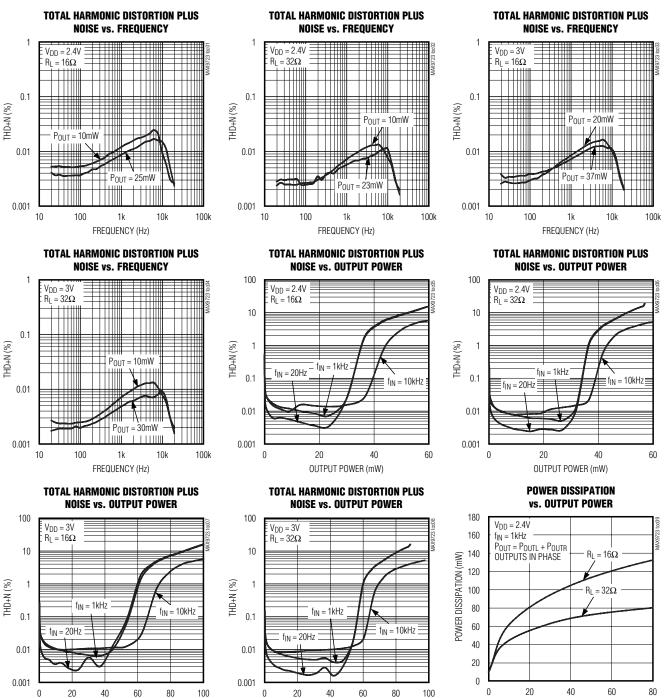

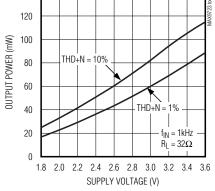

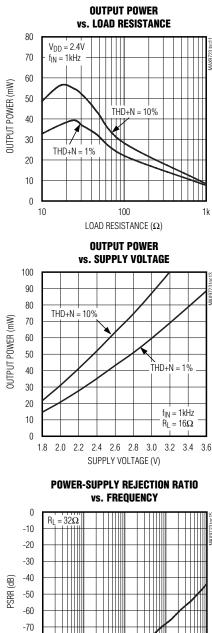

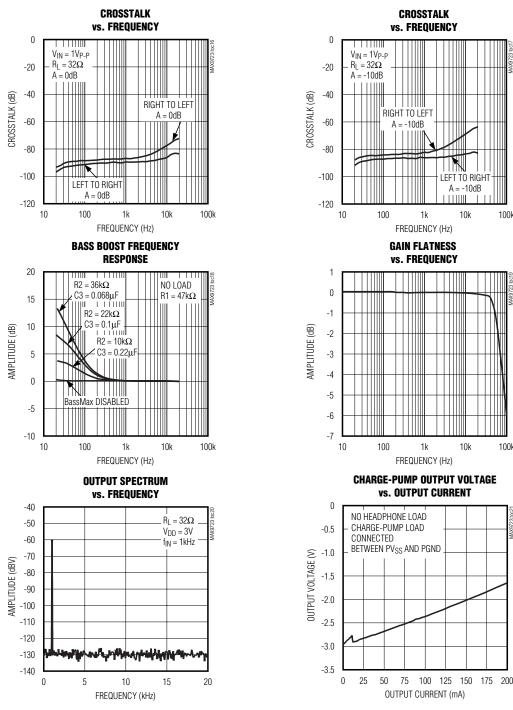

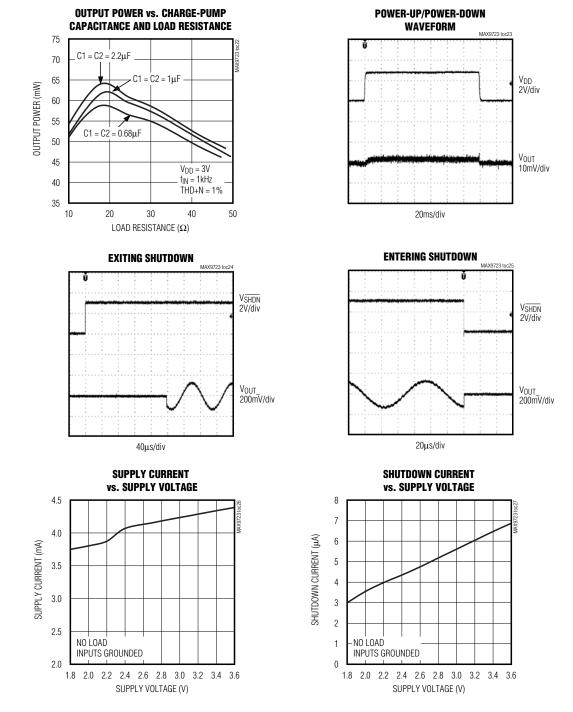

**Typical Operating Characteristics**

$(V_{DD} = \overline{SHDN} = 3V, PGND = SGND = 0V, C1 = C2 = 1\mu F, BB_ = 0V, gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT_ and SGND where specified. Outputs in phase, both channels loaded. T<sub>A</sub> = +25°C, unless otherwise noted.) (See$ *Functional Diagram/Typical Operating Circuit*)

OUTPUT POWER (mW)

OUTPUT POWER (mW)

**MAX9723**

#### (V<sub>DD</sub> = SHDN = 3V, PGND = SGND = 0V, C1 = C2 = 1µF, BB\_ = 0V, gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT\_ and SGND where specified. Outputs in phase, both channels loaded. TA = +25°C, unless otherwise noted.) (See Functional Diagram/Typical Operating Circuit)

140

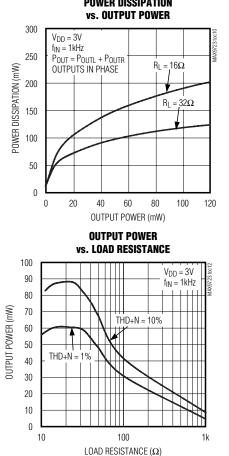

### Typical Operating Characteristics (continued)

**POWER DISSIPATION**

#### Typical Operating Characteristics (continued)

(VDD = SHDN = 3V, PGND = SGND = 0V, C1 = C2 = 1µF, BB\_ = 0V, gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT\_ and SGND where specified. Outputs in phase, both channels loaded. TA = +25°C, unless otherwise noted.) (See Functional Diagram/Typical Operating Circuit)

100k

100k

## \_\_\_\_\_Typical Operating Characteristics (continued)

$(V_{DD} = \overline{SHDN} = 3V, PGND = SGND = 0V, C1 = C2 = 1\mu F, BB_ = 0V, gain = 0dB, maximum volume, BassMax disabled. Load connected between OUT_ and SGND where specified. Outputs in phase, both channels loaded. T<sub>A</sub> = +25°C, unless otherwise noted.) (See$ *Functional Diagram/Typical Operating Circuit*)

**Pin Description**

| PIN      | BUMP |                 |                                                                                                                                                                                                                         |

|----------|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THIN QFN | UCSP | NAME            | FUNCTION                                                                                                                                                                                                                |

| 1        | D1   | V <sub>DD</sub> | Power-Supply Input. Bypass V <sub>DD</sub> to PGND with a 1µF capacitor.                                                                                                                                                |

| 2        | C1   | C1P             | Charge-Pump Flying Capacitor Positive Terminal                                                                                                                                                                          |

| 3        | B1   | PGND            | Power Ground. Connect to SGND.                                                                                                                                                                                          |

| 4        | A1   | C1N             | Charge-Pump Flying Capacitor Negative Terminal                                                                                                                                                                          |

| 5        | B2   | SCL             | Serial Clock Input. Connect a 10k $\Omega$ pullup resistor from SCL to V_DD.                                                                                                                                            |

| 6        | A2   | PVSS            | Charge-Pump Output. Connect to $\text{SV}_{\text{SS}}.$ Bypass $\text{PV}_{\text{SS}}$ with a 1µF capacitor to PGND.                                                                                                    |

| 7        | A3   | SDA             | Serial-Data Input. Connect a $10k\Omega$ pullup resistor from SDA to V <sub>DD</sub> .                                                                                                                                  |

| 8        | B3   | SHDN            | Shutdown. Drive SHDN low to disable the MAX9723. Connect SHDN to $V_{DD}$ while bit 7 is high for normal operation (see the <i>Command Register</i> section).                                                           |

| 9        | A4   | SGND            | Signal Ground. Connect to PGND.                                                                                                                                                                                         |

| 10       | B4   | INL             | Left-Channel Input                                                                                                                                                                                                      |

| 11       | C4   | INR             | Right-Channel Input                                                                                                                                                                                                     |

| 12       | D4   | SVSS            | Headphone Amplifier Negative Power-Supply Input. Connect to PVSS.                                                                                                                                                       |

| 13       | C3   | BBR             | Right BassMax Input. Connect an external lowpass filter between OUTR and BBR to apply bass boost to the right-channel output. Connect BBR to SGND if BassMax is not used (see the <i>BassMax (Bass Boost)</i> section). |

| 14       | D3   | OUTR            | Right Headphone Output                                                                                                                                                                                                  |

| 15       | D2   | OUTL            | Left Headphone Output                                                                                                                                                                                                   |

| 16       | C2   | BBL             | Left BassMax Input. Connect an external lowpass filter between OUTL and BBL to apply bass boost to the right-channel output. Connect BBL to SGND if BassMax is not used (see the <i>BassMax (Bass Boost)</i> section).  |

| EP       |      | EP              | Exposed Paddle. Connect EP to SV <sub>SS</sub> or leave unconnected.                                                                                                                                                    |

#### **Detailed Description**

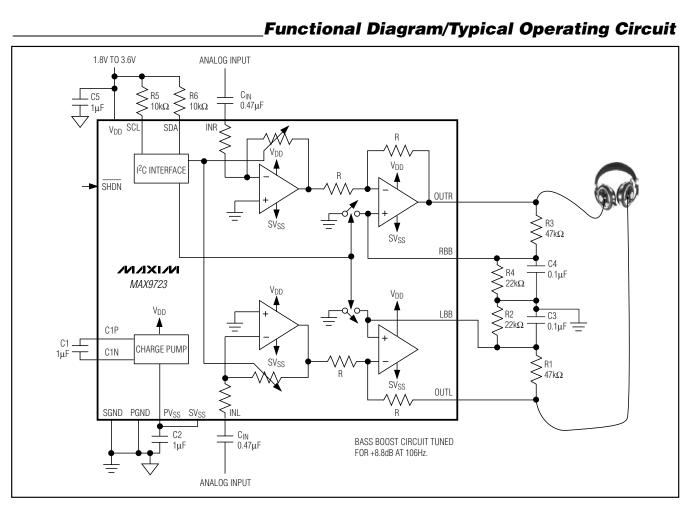

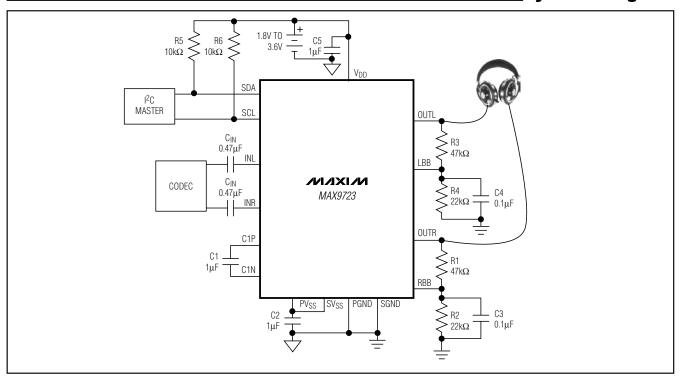

The MAX9723 stereo headphone amplifier features Maxim's patented DirectDrive architecture, eliminating the large output-coupling capacitors required by conventional single-supply headphone amplifiers. The MAX9723 consists of two 62mW Class AB headphone amplifiers, hardware/software shutdown control, inverting charge pump, integrated 32-level volume control, BassMax circuitry, comprehensive click-and-pop suppression circuitry, and an I<sup>2</sup>C-compatible interface (see the Functional Diagram/Typical Operating Circuit). A negative power supply (PVss) is created internally by inverting the positive supply (VDD). Powering the amplifiers from VDD and PVSS increases the dynamic range of the amplifiers to almost twice that of other single-supply amplifiers, increasing the total available output power.

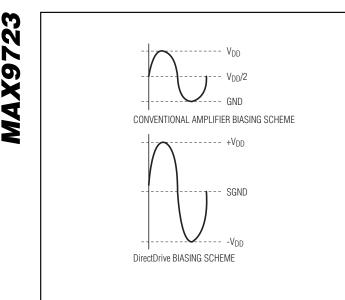

The MAX9723 DirectDrive outputs are biased at SGND (see Figure 1). The benefit of this OV bias is that the amplifier outputs do not have a DC component, eliminating the need for large DC-blocking capacitors. Eliminating the DC-blocking capacitors on the output saves board space, system cost, and improves low-frequency response.

An I<sup>2</sup>C-compatible interface allows serial communication between the MAX9723 and a microcontroller. The MAX9723 is available with two different I<sup>2</sup>C addresses allowing two MAX9723 ICs to share the same bus (see Table 1). The internal command register controls the shutdown status of the MAX9723, enables the BassMax circuitry, sets the maximum gain of the amplifier, and sets the volume level (see Table 2). The MAX9723's BassMax circuitry improves audio reproduction by boosting the bass response of the amplifier, compensating for any low-frequency attenuation introduced by **MAX9723**

Figure 1. Traditional Amplifier Output vs. MAX9723 DirectDrive Output

the headphone. The MAX9723A and MAX9723B have a maximum amplifier gain of 0dB while the MAX9723C and MAX9723D have a maximum gain of +6dB. Amplifier volume is digitally programmable to any one of 32 levels.

**DirectDrive** Traditional single-supply headphone amplifiers have their outputs biased at a nominal DC voltage, typically half the supply, for maximum dynamic range. Large coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone amplifier.

Maxim's patented DirectDrive architecture uses a charge pump to create an internal negative supply voltage. This allows the MAX9723 headphone amplifier outputs to be biased at 0V, almost doubling the dynamic range while operating from a single supply. With no DC component, there is no need for the large DC-blocking capacitors. Instead of two large (typically 220µF) tantalum capacitors, the MAX9723 charge pump requires only two small 1µF ceramic capacitors, thereby conserving board space, reducing cost, and improving the low-frequency response of the headphone amplifier. See the Output Power vs. Charge-Pump Capacitance and Load Resistance graph in the *Typical Operating Characteristics* for details of the possible capacitor sizes. In addition to the cost and size disadvantages, the DCblocking capacitors required by conventional headphone amplifiers limit low-frequency response and can distort the audio signal.

Previous attempts at eliminating the output-coupling capacitors involved biasing the headphone return (sleeve) to the DC bias voltage of the headphone amplifiers. This method raises some issues:

- The sleeve is typically grounded to the chassis. Using the midrail biasing approach, the sleeve must be isolated from system ground, complicating product design. The DirectDrive output biasing scheme allows the sleeve to be grounded.

- During an ESD strike, the amplifier's ESD structure is the only path to system ground. The amplifier must be able to withstand the full ESD strike. The MAX9723 headphone outputs can withstand an ±8kV ESD strike (HBM).

- 3) When using the headphone jack as a line out to other equipment, the bias voltage on the sleeve may conflict with the ground potential from other equipment, resulting in possible damage to the amplifiers. The DirectDrive outputs of the MAX9723 can be directly coupled to other ground-biased equipment.

#### **Charge Pump**

The MAX9723 features a low-noise charge pump. The 600kHz switching frequency is well beyond the audio range, and does not interfere with the audio signals. This enables the MAX9723 to achieve a 99dB SNR. The switch drivers feature a controlled switching speed that minimizes noise generated by turn-on and turn-off transients. Limiting the switching speed of the charge pump minimizes di/dt noise caused by the parasitic bond wire and trace inductance. Although not typically required, additional high-frequency noise attenuation can be achieved by increasing the size of C2 (see the *Functional Diagram/Typical Operating Circuit*).

#### Shutdown

The MAX9723 features a 5µA, low-power shutdown mode that reduces quiescent current consumption and extends battery life. Shutdown is controlled by a hardware or software interface. Driving SHDN low disables the drive amplifiers, bias circuitry, charge pump, and sets the headphone amplifier output impedance to  $20k\Omega$ . Similarly, the MAX9723 enters shutdown when bit seven (B7) in the control register is reset. SHDN and B7 must be high to enable the MAX9723. The I<sup>2</sup>C interface is active and the contents of the command register are not affected when in shutdown. This allows the master to write to the MAX9723 while in shutdown.

#### Click-and-Pop Suppression

The output-coupling capacitor is a major contributor of audible clicks and pops in conventional single-supply headphone amplifiers. The amplifier charges the coupling capacitor to its output bias voltage at startup. During shutdown the capacitor is discharged. This charging and discharging results in a DC shift across the capacitor, which appears as an audible transient at the speaker. Since the MAX9723 headphone amplifier does not require output-coupling capacitors, no audible transients occur.

Additionally, the MAX9723 features extensive click-andpop suppression that eliminates any audible transient sources internal to the device. The Power-Up/Power-Down Waveform in the *Typical Operating Characteristics* shows that there are minimal transients at the output upon startup or shutdown.

In most applications, the preamplifier driving the MAX9723 has a DC bias of typically half the supply. The input-coupling capacitor is charged to the preamplifier's bias voltage through the MAX9723's input impedance (R<sub>IN</sub>) during startup. The resulting voltage shift across the capacitor creates an audible click/pop. To avoid clicks/pops caused by the input filter, delay the rise of SHDN by at least 4 time constants,  $4 \times R_{IN} \times C_{IN}$ , relative to the start of the preamplifier.

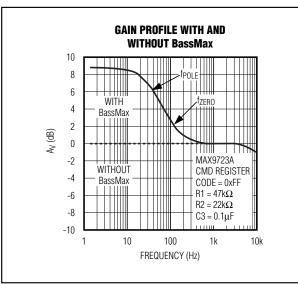

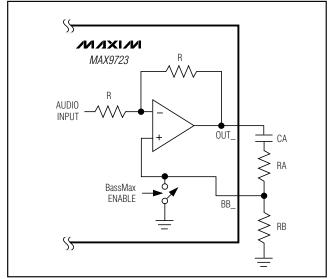

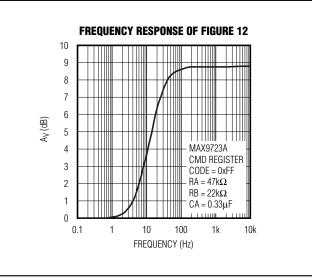

#### BassMax (Bass Boost)

Typical headphones do not have a flat-frequency response. The small physical size of the diaphragm does not allow the headphone speaker to efficiently reproduce low frequencies. This physical limitation results in attenuated bass response. The MAX9723 includes a bass boost feature that compensates for the headphone's poor bass response by increasing the amplifier gain at low frequencies.

The DirectDrive output of the MAX9723 has more headroom than typical single-supply headphone amplifiers. This additional headroom allows boosting the bass frequencies without the output-signal clipping.

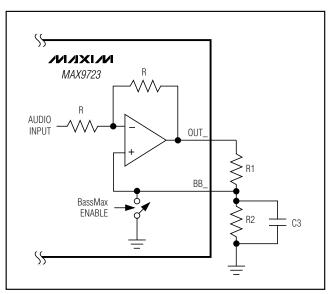

Program the BassMax gain and cutoff frequency with external components connected between OUT\_ and BB\_ (see the *Functional Diagram/Typical Operating Circuit*). Use the I<sup>2</sup>C-compatible interface to program the command register to enable/disable the BassMax circuit.

BB\_ is connected to the noninverting input of the output amplifier when BassMax is enabled. BB\_ is pulled to SGND when BassMax is disabled. The typical application of the BassMax circuit involves feeding a lowpass version of the output signal back to the amplifier. This is realized

Figure 2. BassMax External Connections

using positive feedback from OUT\_ to BB\_. Figure 2 shows the connections needed to implement BassMax.

#### **Maximum Gain Control**

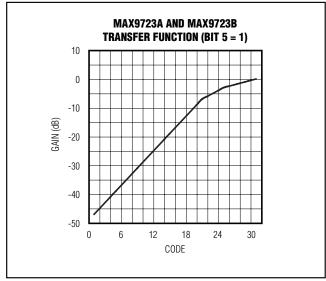

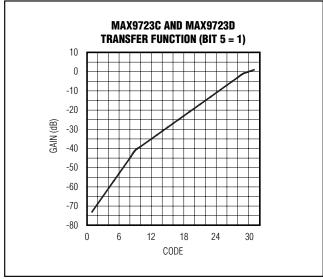

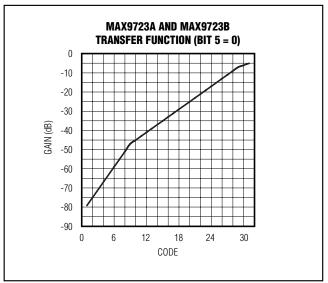

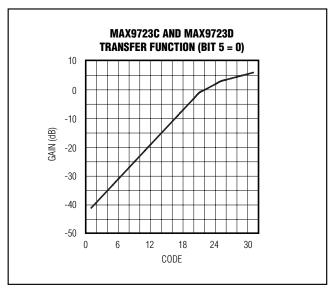

The MAX9723A and MAX9723B have selectable maximum gains of -5dB or 0dB (see Table 5) while the MAX9723C and MAX9723D have selectable maximum gains of +1dB or +6dB (see Table 6). Bit 5 in the command register selects between the two maximum gain settings.

#### Volume Control

The MAX9723 includes a 32-level volume control that adjusts the gain of the output amplifiers according to the code contained in the command register. Volume is programmed through the command register bits [4:0]. Tables 7–10 show all of the available gain settings for the MAX9723A–MAX9723D. The mute attenuation is typically better than 100dB when driving a  $32\Omega$  load.

#### **Serial Interface**

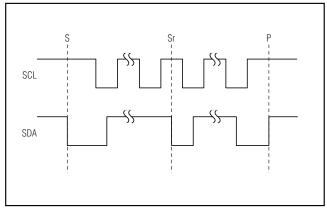

The MAX9723 features an I<sup>2</sup>C/SMBus-compatible, 2-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate communication between the MAX9723 and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The MAX9723 is a receive-only slave device relying on the master to generate the SCL signal. The MAX9723 cannot write to the SDA bus except to acknowledge the receipt of data

Figure 3. 2-Wire Serial-Interface Timing Diagram

from the master. The master, typically a microcontroller, generates SCL and initiates data transfer on the bus.

A master device communicates to the MAX9723 by transmitting the proper address followed by the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

The MAX9723 SDA line operates as both an input and an open-drain output. A pullup resistor, greater than 500 $\Omega$ , is required on the SDA bus. The MAX9723 SCL line operates as an input only. A pullup resistor, greater than 500 $\Omega$ , is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX9723 from highvoltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions section*). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

#### Start and Stop Conditions

SDA and SCL idle high when the bus is not in use. A master device initiates communication by issuing a

START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 4). A START condition from the master signals the beginning of transmission to the MAX9723. The master terminates transmission and frees the bus by issuing a STOP condition. The bus remains active if a REPEATED START condition is generated instead of a STOP condition.

#### Early STOP Conditions

The MAX9723 recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition.

#### Slave Address

The MAX9723 is available with one of two preset slave addresses (see Table 1). The address is defined as the seven most significant bits (MSBs) followed by the Read/Write (R/W) bit. The address is the first byte of information sent to the MAX9723 after the START condition. The MAX9723 is a slave device only capable of being written to. The sent R/W bit must always be a zero when configuring the MAX9723.

The MAX9723 acknowledges the receipt of its address even if  $R/\overline{W}$  is set to 1. However, the MAX9723 will not drive SDA. Addressing the MAX9723 with  $R/\overline{W}$  set to 1 causes the master to receive all 1's regardless of the contents of the command register.

#### Acknowledge

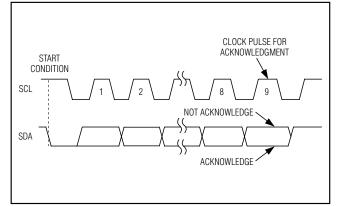

The acknowledge bit (ACK) is a clocked 9th bit that the MAX9723 uses to handshake receipt of each byte of

Figure 4. START, STOP, and REPEATED START Conditions

#### Table 1. MAX9723 Address Map

| PART     |    | MAX9723 SLAVE ADDRESS |            |    |    |    |    |     |  |

|----------|----|-----------------------|------------|----|----|----|----|-----|--|

| FANI     | A6 | A5                    | <b>A</b> 4 | A3 | A2 | A1 | A0 | R/W |  |

| MAX9723A | 1  | 0                     | 0          | 1  | 1  | 0  | 0  | 0   |  |

| MAX9723B | 1  | 0                     | 0          | 1  | 1  | 0  | 1  | 0   |  |

| MAX9723C | 1  | 0                     | 0          | 1  | 1  | 0  | 0  | 0   |  |

| MAX9723D | 1  | 0                     | 0          | 1  | 1  | 0  | 1  | 0   |  |

#### Table 2. MAX9723 Command Register

| B7       | B6                | B5              | <b>B</b> 4 | <b>B</b> 3 | B2   | B1 | B0 |

|----------|-------------------|-----------------|------------|------------|------|----|----|

| SHUTDOWN | BassMax<br>ENABLE | MAXIMUM<br>GAIN |            | V          | OLUN | ΛE |    |

data (see Figure 5). The MAX9723 pulls down SDA during the master-generated 9th clock pulse. The SDA line must remain stable and low during the high period of the acknowledge clock pulse. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master may reattempt communication.

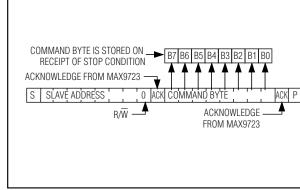

#### Write Data Format

A write to the MAX9723 includes transmission of a START condition, the slave address with the R/W bit reset to 0 (see Table 1), one byte of data to configure the command register, and a STOP condition. Figure 6 illustrates the proper format for one frame.

The MAX9723 only accepts write data, but it acknowledges the receipt of its address byte with the R/W bit set high. The MAX9723 does not write to the SDA bus in the event that the R/W bit is set high. Subsequently,

Figure 5. Acknowledge

#### Table 3. Shutdown Control, SHDN = 1

| MODE             | B7 |

|------------------|----|

| MAX9723 Disabled | 0  |

| MAX9723 Enabled  | 1  |

#### Table 4. BassMax Control

| MODE             | B6 |

|------------------|----|

| BassMax Disabled | 0  |

| BassMax Enabled  | 1  |

the master reads all 1's from the MAX9723. Always reset the R/W bit to 0 to avoid this situation.

#### **Command Register**

The MAX9723 has one command register that is used to enable/disable shutdown, enable/disable BassMax, and set the maximum gain and volume. Table 2 describes the function of the bits contained in the command register.

Reset B7 to 0 to shut down the MAX9723. The MAX9723 wakes up from shutdown when B7 is set to 1 provided SHDN is high. SHDN must be high and B7 must be set to 1 for the MAX9723 to operate normally (see Table 3).

Set B6 to 1 to enable BassMax (see Table 4). The output signal's low-frequency response will be boosted according to the external components connected between OUT\_ and BB\_. See the *BassMax Gain-Setting Components* section in the *Applications Information* section for details on choosing the external components.

Figure 6. Write Data Format Example

The MAX9723A and MAX9723B have a maximum gain setting of -5dB or 0dB, while the MAX9723C and MAX9723D have a maximum gain setting of +1dB or +6dB. B5 in the command register programs the maximum gain (see Tables 5 and 6).

Adjust the MAX9723's amplifier gain with the volume control bits [4:0]. The gain is adjustable to one of 32 steps ranging from full mute to the maximum gain programmed by B5. Tables 7–10 list all the possible gain settings for the MAX9723. Figures 7–10 show the volume control transfer functions for the MAX9723.

#### Power-On Reset

The contents of the MAX9723's command register at power-on are shown in Table 11.

#### \_Applications Information

#### **Power Dissipation and Heat Sinking**

Linear power amplifiers can dissipate a significant amount of power under normal operating conditions. The maximum power dissipation for each package is given in the *Absolute Maximum Ratings* section under Continuous Power Dissipation or can be calculated by the following equation:

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_{A}}{\theta_{JA}}$$

where T<sub>J(MAX)</sub> is +150°C, T<sub>A</sub> is the ambient temperature, and  $\theta_{JA}$  is the reciprocal of the derating factor in °C/W as specified in the *Absolute Maximum Ratings* section. For example,  $\theta_{JA}$  for the thin QFN package is +59°C/W.

The MAX9723 has two power dissipation sources, the charge pump and the two output amplifiers. If the power dissipation exceeds the rated package dissipa-

# Table 5. MAX9723A and MAX9723BMaximum Gain Control

| MAXIMUM GAIN (dB) | B5 |

|-------------------|----|

| -5                | 0  |

| 0                 | 1  |

# Table 6. MAX9723C and MAX9723DMaximum Range Control

| MAXIMUM GAIN (dB) | B5 |

|-------------------|----|

| +1                | 0  |

| +6                | 1  |

tion, reduce V<sub>DD</sub>, increase load impedance, decrease the ambient temperature, or add heatsinking. Large output, supply, and ground traces decrease  $\theta_{JA}$ , allowing more heat to be transferred from the package to surrounding air.

#### **Output Dynamic Range**

Dynamic range is the difference between the noise floor of the system and the output level at 1% THD+N. It is essential that a system's dynamic range be known before setting the maximum output gain. Output clipping will occur if the output signal is greater than the dynamic range of the system. The DirectDrive architecture of the MAX9723 has increased dynamic range compared to other single-supply amplifiers.

Use the THD+N vs. Output Power in the *Typical Operating Characteristics* to identify the system's dynamic range. Find the output power that causes 1% THD+N for a given load. This point will indicate what output power causes the output to begin to clip. Use the following equation to determine the peak output voltage that causes 1% THD+N for a given load.

$$V_{OUT_(P-P)} = 2\sqrt{2(P_{OUT_{1\%}} \times R_L)}$$

where  $P_{OUT_1\%}$  is the output power that causes 1% THD+N, R<sub>L</sub> is the load resistance, and  $V_{OUT_(P-P)}$  is the peak output voltage. After  $V_{OUT_(P-P)}$  is identified, determine the peak input voltage that can be amplified without clipping:

$$V_{\text{IN}(\text{P}-\text{P})} = \frac{V_{\text{OUT}(\text{P}-\text{P})}}{10^{\left(\frac{A_{\text{V}}}{20}\right)}}$$

where  $V_{IN\_(P-P)}$  is the largest peak voltage that can be amplified without clipping, and  $A_V$  is the voltage gain of

# Table 7. MAX9723A and MAX9723B GainSettings (Bit 5 = 1, Max Gain = 0dB)

| В4 | В3 | B2 | B1 | B0<br>(LSB) | GAIN<br>(dB) |

|----|----|----|----|-------------|--------------|

| 1  | 1  | 1  | 1  | 1           | 0            |

| 1  | 1  | 1  | 1  | 0           | -0.5         |

| 1  | 1  | 1  | 0  | 1           | -1           |

| 1  | 1  | 1  | 0  | 0           | -1.5         |

| 1  | 1  | 0  | 1  | 1           | -2           |

| 1  | 1  | 0  | 1  | 0           | -2.5         |

| 1  | 1  | 0  | 0  | 1           | -3           |

| 1  | 1  | 0  | 0  | 0           | -4           |

| 1  | 0  | 1  | 1  | 1           | -5           |

| 1  | 0  | 1  | 1  | 0           | -6           |

| 1  | 0  | 1  | 0  | 1           | -7           |

| 1  | 0  | 1  | 0  | 0           | -9           |

| 1  | 0  | 0  | 1  | 1           | -11          |

| 1  | 0  | 0  | 1  | 0           | -13          |

| 1  | 0  | 0  | 0  | 1           | -15          |

| 1  | 0  | 0  | 0  | 0           | -17          |

| 0  | 1  | 1  | 1  | 1           | -19          |

| 0  | 1  | 1  | 1  | 0           | -21          |

| 0  | 1  | 1  | 0  | 1           | -23          |

| 0  | 1  | 1  | 0  | 0           | -25          |

| 0  | 1  | 0  | 1  | 1           | -27          |

| 0  | 1  | 0  | 1  | 0           | -29          |

| 0  | 1  | 0  | 0  | 1           | -31          |

| 0  | 1  | 0  | 0  | 0           | -33          |

| 0  | 0  | 1  | 1  | 1           | -35          |

| 0  | 0  | 1  | 1  | 0           | -37          |

| 0  | 0  | 1  | 0  | 1           | -39          |

| 0  | 0  | 1  | 0  | 0           | -41          |

| 0  | 0  | 0  | 1  | 1           | -43          |

| 0  | 0  | 0  | 1  | 0           | -45          |

| 0  | 0  | 0  | 0  | 1           | -47          |

| 0  | 0  | 0  | 0  | 0           | MUTE         |

the amplifier in dB determined by the maximum gain setting (Bit 5) or the combination of the maximum gain setting plus bass boost (see the *BassMax Gain-Setting Components* section).

# Table 8. MAX9723A and MAX9723B GainSettings (B5 = 0, Max Gain = -5dB)

| B4 | В3 | B2 | B1 | B0<br>(LSB) | GAIN<br>(dB) |  |  |  |

|----|----|----|----|-------------|--------------|--|--|--|

| 1  | 1  | 1  | 1  | 1           | -5           |  |  |  |

| 1  | 1  | 1  | 1  | 0           | -6           |  |  |  |

| 1  | 1  | 1  | 0  | 1           | -7           |  |  |  |

| 1  | 1  | 1  | 0  | 0           | -9           |  |  |  |

| 1  | 1  | 0  | 1  | 1           | -11          |  |  |  |

| 1  | 1  | 0  | 1  | 0           | -13          |  |  |  |

| 1  | 1  | 0  | 0  | 1           | -15          |  |  |  |

| 1  | 1  | 0  | 0  | 0           | -17          |  |  |  |

| 1  | 0  | 1  | 1  | 1           | -19          |  |  |  |

| 1  | 0  | 1  | 1  | 0           | -21          |  |  |  |

| 1  | 0  | 1  | 0  | 1           | -23          |  |  |  |

| 1  | 0  | 1  | 0  | 0           | -25          |  |  |  |

| 1  | 0  | 0  | 1  | 1           | -27          |  |  |  |

| 1  | 0  | 0  | 1  | 0           | -29          |  |  |  |

| 1  | 0  | 0  | 0  | 1           | -31          |  |  |  |

| 1  | 0  | 0  | 0  | 0           | -33          |  |  |  |

| 0  | 1  | 1  | 1  | 1           | -35          |  |  |  |

| 0  | 1  | 1  | 1  | 0           | -37          |  |  |  |

| 0  | 1  | 1  | 0  | 1           | -39          |  |  |  |

| 0  | 1  | 1  | 0  | 0           | -41          |  |  |  |

| 0  | 1  | 0  | 1  | 1           | -43          |  |  |  |

| 0  | 1  | 0  | 1  | 0           | -45          |  |  |  |

| 0  | 1  | 0  | 0  | 1           | -47          |  |  |  |

| 0  | 1  | 0  | 0  | 0           | -51          |  |  |  |

| 0  | 0  | 1  | 1  | 1           | -55          |  |  |  |

| 0  | 0  | 1  | 1  | 0           | -59          |  |  |  |

| 0  | 0  | 1  | 0  | 1           | -63          |  |  |  |

| 0  | 0  | 1  | 0  | 0           | -67          |  |  |  |

| 0  | 0  | 0  | 1  | 1           | -71          |  |  |  |

| 0  | 0  | 0  | 1  | 0           | -75          |  |  |  |

| 0  | 0  | 0  | 0  | 1           | -79          |  |  |  |

| 0  | 0  | 0  | 0  | 0           | MUTE         |  |  |  |

| 0  | 0  | 5  | 5  | 5           |              |  |  |  |

#### **Component Selection**

#### Input-Coupling Capacitor

The AC-coupling capacitor (C<sub>IN</sub>) and internal gain-setting resistor form a highpass filter that removes any DC bias from an input signal (see the *Functional Diagram/ Typical Operating Circuit*). C<sub>IN</sub> allows the MAX9723 to bias the signal to an optimum DC level. The -3dB point

| Settings (B5 = 1, Max Gain = +6dB) |    |    |    |             |              |  |  |

|------------------------------------|----|----|----|-------------|--------------|--|--|

| B4                                 | В3 | B2 | B1 | B0<br>(LSB) | GAIN<br>(dB) |  |  |

| 1                                  | 1  | 1  | 1  | 1           | 6            |  |  |

| 1                                  | 1  | 1  | 1  | 0           | 5.5          |  |  |

| 1                                  | 1  | 1  | 0  | 1           | 5            |  |  |

| 1                                  | 1  | 1  | 0  | 0           | 4.5          |  |  |

| 1                                  | 1  | 0  | 1  | 1           | 4            |  |  |

| 1                                  | 1  | 0  | 1  | 0           | 3.5          |  |  |

| 1                                  | 1  | 0  | 0  | 1           | 3            |  |  |

| 1                                  | 1  | 0  | 0  | 0           | 2            |  |  |

| 1                                  | 0  | 1  | 1  | 1           | 1            |  |  |

| 1                                  | 0  | 1  | 1  | 0           | 0            |  |  |

| 1                                  | 0  | 1  | 0  | 1           | -1           |  |  |

| 1                                  | 0  | 1  | 0  | 0           | -3           |  |  |

| 1                                  | 0  | 0  | 1  | 1           | -5           |  |  |

| 1                                  | 0  | 0  | 1  | 0           | -7           |  |  |

| 1                                  | 0  | 0  | 0  | 1           | -9           |  |  |

| 1                                  | 0  | 0  | 0  | 0           | -11          |  |  |

| 0                                  | 1  | 1  | 1  | 1           | -13          |  |  |

| 0                                  | 1  | 1  | 1  | 0           | -15          |  |  |

| 0                                  | 1  | 1  | 0  | 1           | -17          |  |  |

| 0                                  | 1  | 1  | 0  | 0           | -19          |  |  |

| 0                                  | 1  | 0  | 1  | 1           | -21          |  |  |

| 0                                  | 1  | 0  | 1  | 0           | -23          |  |  |

| 0                                  | 1  | 0  | 0  | 1           | -25          |  |  |

| 0                                  | 1  | 0  | 0  | 0           | -27          |  |  |

| 0                                  | 0  | 1  | 1  | 1           | -29          |  |  |

| 0                                  | 0  | 1  | 1  | 0           | -31          |  |  |

| 0                                  | 0  | 1  | 0  | 1           | -33          |  |  |

| 0                                  | 0  | 1  | 0  | 0           | -35          |  |  |

| 0                                  | 0  | 0  | 1  | 1           | -37          |  |  |

| 0                                  | 0  | 0  | 1  | 0           | -39          |  |  |

| 0                                  | 0  | 0  | 0  | 1           | -41          |  |  |

| 0                                  | 0  | 0  | 0  | 0           | MUTE         |  |  |

Table 9. MAX9723C and MAX9723D Gain

of the highpass filter, assuming zero-source impedance, is given by:

$$f_{-3dB} = \frac{1}{2\pi \times R_{IN} \times C_{IN}}$$

| Table 10. MAX9723C and MAX9723D Gain |

|--------------------------------------|

| Settings (B5 = 0, Max Gain = +1dB)   |

| B4B3B2B1B0<br>(LSB)GAIN<br>(dB)11111111110011101-111100-311011-511011-511019-711001-911011-1310111-1310111-1710110110111-1710110110110-1510110-1510110-1710110-1710110-1510110-2310110-2310011-2910011-3310011-3310110-3411011-3701011-410101                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |    | - / |    |   |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|-----|----|---|------|

| 11110011101-111100-311011-511010-711001-911000-1110111-3310111-1310111-1710110-1510101-171010-191010-191010-231001-211001-251000-270111-290111-29011330110-350101-370101-490011-490011-490011-650010-6100101-6500010-6900101-73 <th>B4</th> <th>B3</th> <th>B2</th> <th>B1</th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                   | B4 | B3 | B2  | B1 |   |      |

| 11101-111100-311011-511010-711001-911000-1110111-3310111-1310110-1510110-1710101-1710101-1710101-1710101-1710101-1710101-2110101-211001-231001-25100001111-2901111-3301110-3301101-3701011-3701011-4900110-5300101-5700101-5700<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1  | 1  | 1   | 1  | 1 | 1    |

| 11100 $-3$ 11011 $-5$ 11010 $-7$ 11001 $-9$ 11001 $-9$ 11000 $-11$ 10111 $-13$ 10110 $-15$ 10101 $-17$ 10100 $-19$ 10100 $-19$ 10011 $-21$ 10011 $-21$ 10011 $-21$ 10011 $-21$ 1001 $-21$ 1001 $-25$ 1000 $-27$ 0111 $-29$ 0111 $-29$ 0111 $-33$ 0110 $-31$ 0101 $-37$ 0101 $-37$ 0101 $-41$ 0101 $-57$ 001010010 $-61$ 0010 $-61$ 0010 $-65$ <t< td=""><td>1</td><td>1</td><td></td><td>1</td><td>0</td><td>0</td></t<>                                                                                                                                                                                                                                                                                              | 1  | 1  |     | 1  | 0 | 0    |

| 11011 $-5$ 11010 $-7$ 11001 $-9$ 11000 $-11$ 10111 $-13$ 10110 $-15$ 10101 $-17$ 10101 $-17$ 10101 $-17$ 10101 $-17$ 10011 $-21$ 10011 $-21$ 10011 $-21$ 10011 $-21$ 1001 $-23$ 1001 $-25$ 1000 $-27$ 0111 $-29$ 0111 $-29$ 0111 $-33$ 0111 $-33$ 0101 $-33$ 0101 $-33$ 0101 $-33$ 0101 $-41$ 0101 $-57$ 0011 $-57$ 001010010 $-61$ 0010 $-69$ 0                                                                                                                                                                                                                                                                                                                                                                      | 1  | 1  | 1   | 0  | 1 | -1   |

| 11010-711001-911000-1110111-1310110-1510101-1710101-1710101-1710101-1710101-1710101-1710101-1710101-1710101-1710101-1710101-1710101-1710101-2110011-2110000-2310000-2701111-2901111-3301110-3101101-3301011-3701011-410110-5300110-53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 1  | 1   | 0  | 0 | -3   |

| 11001 $-9$ 11000 $-11$ 10111 $-13$ 10110 $-15$ 10101 $-17$ 10101 $-17$ 10101 $-17$ 10011 $-21$ 10011 $-21$ 10011 $-21$ 10011 $-25$ 10001 $-25$ 10000 $-27$ 01111 $-29$ 01111 $-29$ 0111 $-33$ 0110 $-31$ 0110 $-35$ 0101 $-33$ 0101 $-33$ 0100 $-45$ 0011 $-41$ 0100 $-45$ 0011 $-57$ 0010 $-61$ 0010 $-65$ 0001 $-73$                                                                                                                                                                                                                                                                                                                                                                                                | 1  | 1  | 0   | 1  | 1 | -5   |

| 11000-1110111-1310110-1510101-1710101-1710101-1710101-1710101-1710011-1710011-1710011-2110011-2110011-2310001-2510000-2701111-2901111-2901111-3301103-3501101-3301011-3701011-4900111-4900110-5300101-5700101-6500010-6900010-690001-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 1  | 0   | 1  | 0 | -7   |

| 10111 $-13$ 10110 $-15$ 10101 $-17$ 10101 $-17$ 10100 $-19$ 10011 $-21$ 100102310001 $-25$ 10000 $-27$ 01111 $-29$ 01111 $-29$ 01110 $-31$ 01110 $-31$ 01101 $-33$ 01101 $-33$ 01011 $-37$ 01011 $-37$ 01011 $-41$ 01011 $-41$ 01011 $-53$ 00110 $-53$ 00101 $-65$ 00101 $-65$ 00010 $-69$ 00010 $-69$ 0001 $-73$                                                                                                                                                                                                                                                                                                                                                                                                     | 1  | 1  | 0   | 0  | 1 | -9   |

| 10110 $-15$ 10101 $-17$ 10100 $-19$ 10011 $-21$ 10010 $-23$ 10001 $-25$ 10001 $-25$ 10000 $-27$ 01111 $-29$ 01111 $-29$ 01110 $-31$ 01110 $-31$ 01101 $-33$ 01011 $-33$ 0101 $-37$ 0101 $-37$ 0101 $-41$ 0100 $-45$ 0011 $-49$ 0011 $-57$ 0010 $-53$ 0010 $-61$ 00010 $-69$ 0001 $-65$ 0001 $-73$                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  | 1  | 0   | 0  | 0 | -11  |

| 10101 $-17$ 10100 $-19$ 10011 $-21$ 10010 $-23$ 10001 $-25$ 10000 $-27$ 01111 $-29$ 01110 $-31$ 01110 $-31$ 01101 $-33$ 01101 $-33$ 010130101 $-37$ 0101 $-37$ 0101 $-41$ 0100 $-45$ 0011 $-49$ 0011 $-57$ 0010 $-53$ 0010 $-61$ 0001 $-65$ 0001 $-69$ 0001 $-73$                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  | 0  | 1   | 1  | 1 | -13  |

| 10100 $-19$ 10011 $-21$ 10010 $-23$ 10001 $-25$ 10000 $-27$ 01111 $-29$ 01111 $-29$ 01110 $-31$ 011031001100 $-35$ 01011 $-37$ 01011 $-37$ 01011 $-37$ 01011 $-37$ 01011 $-37$ 01011 $-37$ 01011 $-49$ 00111 $-49$ 00110 $-53$ 00101 $-57$ 00101 $-65$ 00010 $-69$ 0001 $-73$                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  | 0  | 1   | 1  | 0 | -15  |

| 10011 $-21$ 10010 $-23$ 10001 $-25$ 10000 $-27$ 01111 $-29$ 01110 $-31$ 011013301101 $-33$ 01101 $-33$ 0101330101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-37$ 0101 $-41$ 010010011 $-57$ 001010010 $-61$ 000110001 $-65$ 0001 $-73$                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 0  | 1   | 0  | 1 | -17  |

| 10010 $-23$ 10001 $-25$ 10000 $-27$ 01111 $-29$ 01110 $-31$ 011013301101 $-33$ 010137010110101-370101-370101-390101-4101001-410100110011-530010-530010-61000110010-69000173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1  | 0  | 1   | 0  | 0 | -19  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 0  | 0   | 1  | 1 | -21  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 0  | 0   | 1  | 0 | -23  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 0  | 0   | 0  | 1 | -25  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  | 0  | 0   | 0  | 0 | -27  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0  | 1  | 1   | 1  | 1 | -29  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0  | 1  | 1   | 1  | 0 | -31  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0  | 1  | 1   | 0  | 1 | -33  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0  | 1  | 1   | 0  | 0 | -35  |

| 0         1         0         0         1         -41           0         1         0         0         0         -45           0         1         0         0         0         -45           0         0         1         1         1         -49           0         0         1         1         1         -49           0         0         1         1         0         -53           0         0         1         0         1         -57           0         0         1         0         0         -61           0         0         0         1         1         -65           0         0         0         1         0         -69           0         0         0         0         1         -73 | 0  | 1  | 0   | 1  | 1 | -37  |

| 0         1         0         0         0         -45           0         0         1         1         1         -49           0         0         1         1         0         -53           0         0         1         0         1         -57           0         0         1         0         0         -61           0         0         0         1         1         -65           0         0         0         1         0         -69           0         0         0         0         1         -73                                                                                                                                                                                                 | 0  | 1  | 0   | 1  | 0 | -39  |

| 0         0         1         1         1         -49           0         0         1         1         0         -53           0         0         1         0         1         -57           0         0         1         0         0         -61           0         0         0         1         1         -65           0         0         0         1         0         -69           0         0         0         0         1         -73                                                                                                                                                                                                                                                                 | 0  | 1  | 0   | 0  | 1 | -41  |

| 0         0         1         1         0         -53           0         0         1         0         1         -57           0         0         1         0         1         -57           0         0         1         0         0         -61           0         0         0         1         1         -65           0         0         0         1         0         -69           0         0         0         0         1         -73                                                                                                                                                                                                                                                                 | 0  | 1  | 0   | 0  | 0 | -45  |