# **GAL16V8QS-10L, -15L** 20-Pin 0.8μ EECMOS PLDs

### **General Description**

The EECMOS GAL16V8QS devices are fabricated using National's CS80BEV 0.8 µ Electrically Erasable CMOS pro-This advanced process makes GAL16V8QS extremely fast, allowing controlled output edge rates which dramatically reduce noise. Low noise is actually specified and guaranteed with National's GAL16V8QS Quiet Series™ devices.

National's fast programming algorithm allows the GAL16V8QS to be programmed significantly faster than similar devices using industry standard programmers. Fast programming reduces the cost of programming by greatly increasing programming throughput. National guarantees a minimum of 100 erase/write cycles.

Unique test circuitry and reprogrammable cells allow complete AC, DC, cell, and functionality testing during manufacture. Therefore, National guarantees 100% field programmability and functionality of GAL® devices. In addition, a security circuit is built-in, providing proprietary designs with copy protection.

#### **Features**

- High performance 0.8 µ EECMOS technology

- 10 ns maximum propagation delay

- 5 ns setup time delay

- 7.5 ns clock to registered output delay

- $f_{MAX} = 80 MHz$

- Reduced ground bounce

- 2000V ESD protection

- Reduced power

- $I_{CC} max = 90 mA @ 25 MHz$

- Electrically erasable cell technology

- 100% tested at manufacture

- Fast programming algorithm

- Reduces programming cost, increases throughput

- Emulates popular PAL® devices

- Fully supported by National's OPALTM and OPAL ir software as well as 3rd-party PLD development software

- Commercial and industrial grades

### Ordering Information

#### - GENERIC ARRAY LOGIC FAMILY NUMBER OF ARRAY INPUTS QUITPUT TYPE V = VARIABLE NUMBER OF OUTPUTS OS = QUIET SERIES SPEED 10: t<sub>PD</sub> = 10 ns 15: t<sub>PD</sub> = 15 ns 25: $t_{PD} = 25 \text{ ns}$ L = LOW POWER PACKAGE TYPE N = 20-PIN PLASTIC DIP V = 20-PIN PLCC M = 20-PIN SOIC TEMPERATURE RANGE C = COMMERCIAL (0°C TO +75°C) | = INDUSTRIAL (-40°C TO +85°C) 16 V 8 QS -10

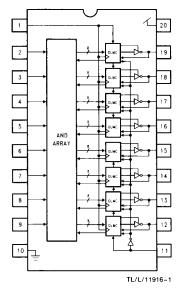

## **Block Diagram**

TL/L/11916-23

TRI-STATE® is a registered trademark of National Semiconductor Corporation. OPAL™ and Quiet Series™ are trademarks of National Semiconductor Corporation. GAL® is a registered trademark of Lattice Semiconductor

PAL® is a registered trademark of and used under license from Advanced Micro Devices, Inc.

GAL

L

#### **COMMERCIAL**

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) (Note 2)

$-\,0.5V$  to  $\,+\,7.0V$

Input Voltage (Note 2)

-2.5V to  $V_{CC} + 1.0$ V

Off-State Output Voltage (Note 2)

-2.5V to  $V_{CC} + 1.0$ V

Output Current Storage Temperature ± 100 mA

Latchup Current

$-65^{\circ}\text{C}$  to  $\,+\,150^{\circ}\text{C}$

200 mA

Ambient Temperature

with Power applied

-65°C to +125°

Junction Temperature

-65°C to +150°C

Lead Temperature

(Soldering, 10 seconds)

300°C 2000V

ESD Tolerance

$C_{ZAP} = 100 pF$

$R_{ZAP} = 1500\Omega$

Test Method: Human Body Model

Test Specification: NSC SOP-5-028

## **Recommended Operating Conditions**

| Symbol            | Parameter                      |      | Units |      |       |

|-------------------|--------------------------------|------|-------|------|-------|

| Oymbol .          | rainetei                       | Min  | Тур   | Max  | Onits |

| $V_{CC}$          | Supply Voltage                 | 4.75 | 5     | 5.25 | ٧     |

| TA                | Operating Free-Air Temperature | 0    | 25    | 75   | °C    |

| t <sub>r</sub>    | Clock Rise Time                |      | 3     | 250  | ns    |

| t <sub>f</sub>    | Clock Fall Time                |      | 3     | 250  | ns    |

| t <sub>rVCC</sub> | V <sub>CC</sub> Rise Time      |      |       | 250  | ms    |

#### **Electrical Characteristics**

| Symbol           | Parameter                    | Conditions                                                                       | Conditions |      |                       | Units |

|------------------|------------------------------|----------------------------------------------------------------------------------|------------|------|-----------------------|-------|

| - Cyllibol       | , arameter                   | Conditions                                                                       |            | Min  | Max                   |       |

| V <sub>IH</sub>  | High Level Input Voltage     |                                                                                  |            | 2.0  | V <sub>CC</sub> + 1.0 | ٧     |

| V <sub>IL</sub>  | Low Level Input Voltage      |                                                                                  |            | -0.5 | 0.8                   | V     |

| V <sub>OH</sub>  | High Level Output Voltage    | $V_{CC} = Min, I_{OH} = -3.2 m$                                                  | A          | 2.4  |                       | ٧     |

| V <sub>OL</sub>  | Low Level Output Voltage     | V <sub>CC</sub> = Min, I <sub>OL</sub> = 24 mA                                   |            |      | 0.5                   | ٧     |

| l <sub>IH</sub>  | High Level Input Current     | V <sub>CC</sub> = Max, V <sub>1</sub> = V <sub>CC</sub> (max                     |            | 10   | μА                    |       |

| 1 <sub>IL</sub>  | Low Level Input Current      | V <sub>CC</sub> = Max, V <sub>I</sub> = GND                                      |            | -10  | μА                    |       |

| los              | Output Short Circuit Current | $V_{CC} = 5.0V, V_O = 0.5V$ $T_A = 25^{\circ}C$ (One Output, Duration <1 second) |            | -30  | - 135                 | mA    |

| lcc              | Supply Current (Note 3)      | f = 25 MHz,                                                                      | -10L       |      | 115                   |       |

|                  |                              | V <sub>CC</sub> = Max,<br>No Load                                                | - 1        |      | 90                    | mA    |

| C <sub>I</sub>   | Input Capacitance            | V <sub>CC</sub> = 5.0V, T <sub>A</sub> = 25°C,<br>f = 25 MHz                     |            |      | 5                     | pF    |

| C <sub>I/O</sub> | I/O Capacitance              | $V_{CC} = 5.0V, T_A = 25^{\circ}C,$<br>f = 25  MHz                               |            |      | 6                     | рF    |

Note 1: Absolute Maximum Ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside the specified Recommended Operating Conditions.

Note 2: Some device pins may be raised above these limits during programming and preload operations according to the applicable specification.

Note 3: I<sub>CC</sub> parameters not directly 100% tested.

## **COMMERCIAL**

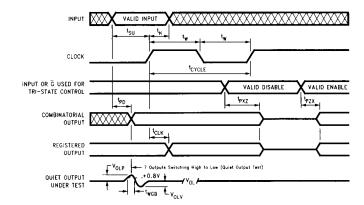

# **AC Specifications**

|                    |                                      |                                                         |      |      | Units |      |     |

|--------------------|--------------------------------------|---------------------------------------------------------|------|------|-------|------|-----|

| Symbol             | Parameter                            | Conditions (Note 4)                                     | -10L |      |       | -15L |     |

|                    |                                      |                                                         | Min  | Max  | Min   | Max  |     |

| t <sub>PD</sub>    | Input or F/B to Combinatorial Output |                                                         |      | 10   |       | 15   | ns  |

| t <sub>SU</sub>    | Input or F/B Setup Time before Clock |                                                         | 5    |      | 7     |      | ns  |

| t <sub>H</sub>     | Hold Time (Input after Clock)        |                                                         | 0    |      | 0     |      | ns  |

| tolk               | Clock to Registered Output or F/B    |                                                         |      | 7.5  |       | 9    | ns  |

| f <sub>MAX</sub>   | Clock Frequency (Note 5)             | With Feedback                                           |      | 80   |       | 62.5 | MHz |

|                    |                                      | Without Feedback                                        |      | 83.3 |       | 62.5 |     |

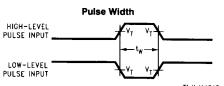

| t <sub>W</sub>     | Clock Pulse Width (High/Low)         | Referenced at 1.5V                                      | 6    |      | 8     |      | ns  |

| t <sub>CYCLE</sub> | Clock Period (with F/B)              | t <sub>CYCLE</sub> = t <sub>SU</sub> + t <sub>CLK</sub> | 12.5 |      | 16    |      | ns  |

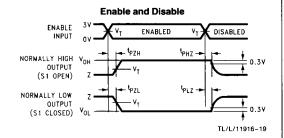

| t <sub>PZxi</sub>  | Input to Output Enable               |                                                         |      | 10   |       | 15   | ns  |

| t <sub>PxZI</sub>  | Input to Output Disable (Note 6)     |                                                         |      | 12   |       | 15   | ns  |

| t <sub>PZxG</sub>  | G to Output Enable                   |                                                         |      | 10   |       | 15   | ns  |

| t <sub>PxZG</sub>  | G to Output Disable (Note 6)         |                                                         |      | 12   |       | 15   | ns  |

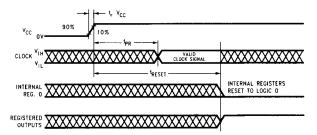

| †RESET             | Power-Up to Registered Output High   |                                                         |      | 45   |       | 45   | μs  |

| fi                 | Input Frequency (Note 7)             |                                                         |      | 100  |       | 66.6 | MHz |

| t <sub>PR</sub>    | Clock Valid after Power-Up           |                                                         |      | 100  |       | 100  | ns  |

Note 4: See AC test load on page 7.  $I_{CC}$  is measured with the GAL16V8QS configured as two 4-bit Gray code counters.

Note 5: f<sub>MAX</sub> parameters not directly 100% tested.

Note 6: Values are tested with  $C_L = 50 pF$

Note 7:  $f_1 = (t_{PD}) - 1$

### **INDUSTRIAL**

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) (Note 2)

-0.5V to +7.0V

Input Voltage (Note 2)

Off-State Output Voltage (Note 2) **Output Current**

-2.5V to  $V_{CC} + 1.0$ V

Storage Temperature

Latchup Current

-2.5V to  $V_{CC} + 1.0V$

$\pm 100 \text{ mA}$

-65°C to +150°C 200 mA Ambient Temperature

with Power Applied

Junction Temperature

-65°C to +125°C -65°C to +150°C

Lead Temperature

(Soldering, 10 seconds)

300°C 2000V

**ESD Tolerance**  $C_{ZAP} = 100 pF$

$R_{ZAP} = 1500\Omega$

Test Method: Human Body Model Test Specification: NSC SOP-5-028

## **Recommended Operating Conditions**

| Symbol          | Parameter                      |      | Units |      |       |

|-----------------|--------------------------------|------|-------|------|-------|

|                 | , arameter                     | Min  | Тур   | Max  | Oints |

| V <sub>CC</sub> | Supply Voltage                 | 4.50 | 5     | 5.50 | ٧     |

| TA              | Operating Free-Air Temperature | -40  | 25    | 85   | °C    |

| t <sub>r</sub>  | Clock Rise Time                |      | 3     | 250  | ns    |

| t <sub>f</sub>  | Clock Fall Time                |      | 3     | 250  | ns    |

| trvcc           | V <sub>CC</sub> Rise Time      |      |       | 250  | ms    |

#### **Electrical Characteristics**

| Symbol           | Parameter                    | Conditions                                                                                |      | Industrial |                       | Units |  |

|------------------|------------------------------|-------------------------------------------------------------------------------------------|------|------------|-----------------------|-------|--|

|                  |                              | - Containono                                                                              |      | Min        | Min Max               |       |  |

| V <sub>IH</sub>  | High Level Input Voltage     |                                                                                           |      | 2.0        | V <sub>CC</sub> + 1.0 | V     |  |

| V <sub>IL</sub>  | Low Level Input Voltage      |                                                                                           |      | -0.5       | 0.8                   | V     |  |

| V <sub>OH</sub>  | High Level Output Voltage    | $V_{CC} = Min, I_{OH} = -3.2 \text{ mA}$                                                  |      | 2.4        |                       | ٧     |  |

| V <sub>OL</sub>  | Low Level Output Voltage     | V <sub>CC</sub> = Min, I <sub>OL</sub> = 24 mA                                            |      |            | 0.5                   | V     |  |

| l <sub>iH</sub>  | High Level Input Current     | $V_{CC} = Max, V_I = V_{CC} (Max)$                                                        |      |            | 10                    | μΑ    |  |

| I <sub>IL</sub>  | Low Level Input Current      | V <sub>CC</sub> = Max, V <sub>I</sub> = GND                                               |      |            | -10                   | μΑ    |  |

| los              | Output Short Circuit Current | $V_{CC} = 5.0V$ , $V_O = 0.5V$<br>$T_A = 25^{\circ}C$ (One Output,<br>Duration <1 second) |      | -30        | <b>- 135</b>          | mA    |  |

| lcc              | Supply Current (Note 3)      | f = 25 MHz,                                                                               | -10L |            | 130                   |       |  |

|                  |                              | V <sub>CC</sub> = Max,<br>No Load                                                         | -15L |            | 130                   | mA    |  |

| C <sub>I</sub>   | Input Capacitance            | $V_{CC} = 5.0V, T_A = 25^{\circ}C,$<br>f = 25 MHz                                         | •    |            | 5                     | pF    |  |

| C <sub>I/O</sub> | I/O Capacitance              | $V_{CC} = 5.0V, T_A = 25^{\circ}C,$<br>f = 25 MHz                                         |      |            | 6                     | pF    |  |

Note 1: Absolute Maximum Ratings are those values beyond which the device may be permanently damaged. Proper operation is not guaranteed outside the specified Recommended Operating Conditions.

Note 2: Some device pins may be raised above these limits during programming and preload operations according to the applicable specification.

Note 3: ICC parameters not directly 100% tested.

## **INDUSTRIAL**

# **AC Specifications**

|                   | Parameter                            |                                                         |      |      | Units |      |     |

|-------------------|--------------------------------------|---------------------------------------------------------|------|------|-------|------|-----|

| Symbol            |                                      | Conditions (Note 4)                                     | -10L |      |       | -15L |     |

|                   |                                      |                                                         | Min  | Max  | Min   | Max  |     |

| t <sub>PD</sub>   | Input or F/B to Combinatorial Output |                                                         |      | 10   |       | 15   | ns  |

| t <sub>SU</sub>   | Input or F/B Setup Time before Clock |                                                         | 5    |      | 7     |      | ns  |

| t <sub>H</sub>    | Hold Time (Input after Clock)        |                                                         | 0    |      | 0     |      | ns  |

| t <sub>CLK</sub>  | Clock to Registered Output or F/B    |                                                         |      | 7.5  |       | 9    | ns  |

| fMAX              | Clock Frequency (Note 5)             | With Feedback                                           |      | 80   |       | 62.5 | MHz |

|                   |                                      | Without Feedback                                        |      | 83.3 |       | 62.5 |     |

| tw                | Clock Pulse Width (High/Low)         | Referenced at 1.5V                                      | 6    |      | 8     |      | ns  |

| tCYCLE            | Clock Period (with F/B)              | t <sub>CYCLE</sub> = t <sub>SU</sub> + t <sub>CLK</sub> | 12.5 |      | 16    |      | ns  |

| t <sub>PZXI</sub> | Input to Output Enable               |                                                         |      | 10   |       | 15   | ns  |

| t <sub>PXZI</sub> | Input to Output Disable (Note 6)     |                                                         |      | 12   |       | 15   | ns  |

| tpzxg             | G to Output Enable                   |                                                         |      | 10   |       | 15   | ns  |

| tpxzg             | G to Output Disable (Note 6)         |                                                         |      | 12   |       | 15   | ns  |

| tRESET            | Power-Up to Registered Output High   |                                                         |      | 45   |       | 45   | μs  |

| f <sub>l</sub>    | Input Frequency (Note 7)             |                                                         |      | 100  |       | 66.6 | MHz |

| t <sub>PR</sub>   | Clock Valid after Power-Up           |                                                         |      | 100  |       | 100  | ns  |

Note 4: See AC test load on page 7. I<sub>CC</sub> is measured with the GAL16V8QS configured as two 4-bit Gray code counters.

Note 5: f<sub>MAX</sub> parameters not directly 100% tested.

Note 6: Values are tested with  $C_L = 50 \text{ pF}$

Note 7:  $f_1 = (t_{PD})$

## **GAL16V8QS Quiet Electrical Characteristics**

| Symbol           | Parameter                                        | Conditions (Note 1)                               | Comn | Units |        |

|------------------|--------------------------------------------------|---------------------------------------------------|------|-------|--------|

|                  |                                                  | Conditions (Note 1)                               | Тур  | Max   | Ollits |

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic VOL                 | $V_{CC} = 5.0V, T = 25^{\circ}C$                  | 1.2  | 1.5   | V      |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic V <sub>OL</sub>     | V <sub>CC</sub> = 5.0V, T = 25°C                  | -0.3 | -1.2  | V      |

| V <sub>IHD</sub> | Maximum High Level Dynamic<br>Input Voltage      | $V_{CC} = 5.0V$ , $T = 25^{\circ}C$ , $f = 1$ MHz | 1.9  | 2.2   | ٧      |

| V <sub>ILD</sub> | Maximum Low Level Dynamic<br>Input Voltage       | V <sub>CC</sub> = 5.0V, T = 25°C, f = 1 MHz       | 1.2  | 0.8   | V      |

| twgB             | Width of Ground Bounce Peak<br>Measured at +0.8V | V <sub>CC</sub> = 5.0V, T = 25°C                  |      | 3.0   | ns     |

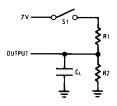

Note 1: AC test load is used with  $R_1 = R_2 = 500\Omega$ , S1 open. Quiet Electrical Characteristics are measured with seven outputs switching from HIGH to LOW, with the remaining output LOW.  $V_{OLP}$  and  $V_{OLV}$  are measured at the non-switching output. Input-under-test switching is 3V to threshold for  $V_{ILD}$  and 0V to threshold for  $V_{IHD}$ . Quiet Electrical Parameters are not directly 100% tested, but are characterized and guaranteed by design.

### **AC Test Load**

$R1 = R2 = 500\Omega$   $C_L = 50 \text{ pF}$ For:

t<sub>PD</sub>: S1 open t<sub>PZH/HZ</sub>: S1 open t<sub>PZL/LZ</sub>: S1 closed

Active to TRI-STATE measurement level = active output level ± 0.3V.

TL/L/11916-2

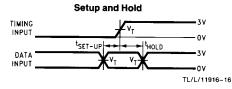

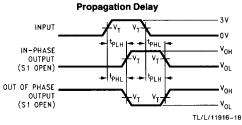

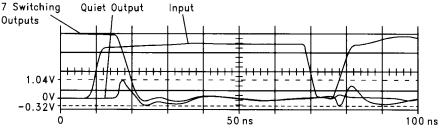

#### **Test Waveforms**

#

TL/L/11916-15

Note A. V<sub>OHV</sub> and V<sub>OLP</sub> are measured with respect to ground reference.

Note B. Input pulses have the following characteristics: f = 1 MHz,  $t_r = 3$  ns, skew < 150 ps.

**Note C.** Test load for Quiet output:  $C_L = 50 \text{ pF}$ ,  $R_L = 500 \Omega$ .

### Test Waveforms (Continued)

#### Notes:

C<sub>L</sub> includes probe and jig capacitance.

$V_T = 1.5V$ .

Test Inputs have rise and fall times of 3 ns between 0.3V and 2.7V.

In the examples above, the phase relationship between inputs and outputs have been chosen arbitrarily.

## **Switching Waveforms**

TL/L/11916-3

## **Power-Up Reset Waveforms**

### **Functional Description**

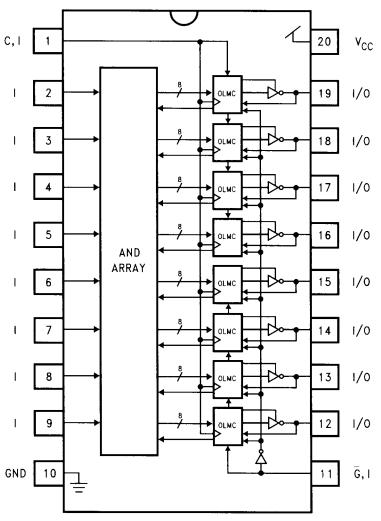

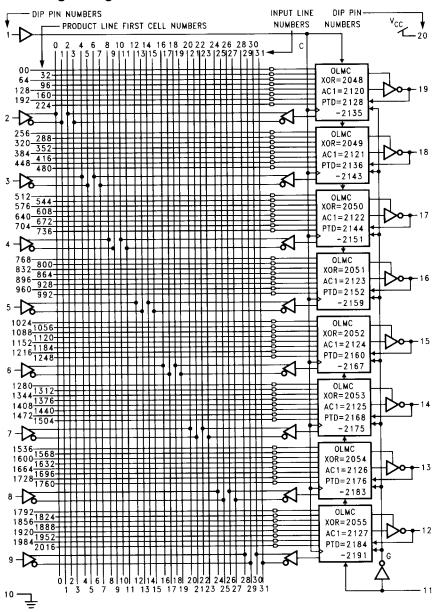

The GAL logic array consists of a programmable AND array with fixed OR-gate connections, similar to the bipolar PAL architecture. The logic array is organized as 16 complementary input lines crossing 64 "product term" lines with a programmable EEPROM cell at each intersection (2048 cells). Each programmable cell may establish a connection between an input line (true or complement phase of an array input signal) and a product term. A product term is satisfied (logically true) while all of the input lines "connected" to it are in the high logic state.

The 64 product terms are organized into eight output groups with eight terms each. Seven or eight of the product terms in each output group feed into an OR-gate to produce each output logic function; one of the product terms may instead be used to control the associated TRI-STATE device output.

The fundamental transfer function of each GAL output is the familiar Boolean sum-of-products. Design development software is available which accepts Boolean equations and converts them automatically into GAL programming patterns.

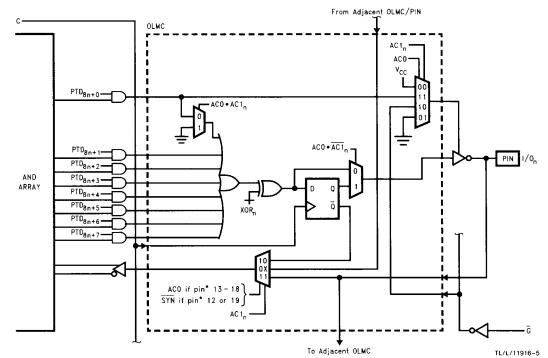

As shown in the GAL16V8QS Block Diagram (Figure 2), a total of eight output logic functions are available. Each of the AND/OR logic functions feeds into an "output logic macrocell" (OLMC). The eight OLMCs control the flow of input and output signals between the logic array and the device's I/O pins.

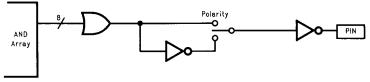

Under control of an OLMC, each output may be designated either registered or combinatorial (non-registered). In the registered output configuration, the logic function output passes through a D-type flip-flop triggered by the rising edge of the clock input. Additionally, the logic function's output polarity may be designated active-low or active-high (adjusted before the register, if present). OLMC options such as these are selected using a set of programmable architecture control cells. These architecture cells are normally configured automatically by the development software or programming hardware.

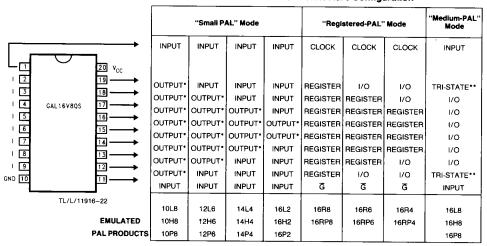

All of the possible I/O configurations of the GAL16V8QS are classified into three basic modes: "Small-PAL" mode, "Registered-PAL" mode and "Medium-PAL" mode. These modes correspond to the architectures of the PAL families which the GAL16V8QS can emulate. The modes determine the mixture of OLMC configurations which can be selected for the device. The OLMC Selection table (Table I) lists which functions can be selected on the device pin\* 1 and pins\* 11 through 19 for each of the three modes. The logic diagram in Figure 3 illustrates these OLMC functions. "OUT-PUT" represents the always-active combinatorial output configuration available in the "Small-PAL" mode. "REGIS-TER" is the registered output with register feedback available in the "Registered-PAL" mode. "1/O" is the combinatorial bidirectional I/O available in "Registered-PAL" and "Medium-PAL" modes. "TRI-STATE" is the TRI-STATE combinatorial output function appearing on pins\* 12 and 19 in the "Medium-PAL" mode. "INPUT" in Table I denotes an OLMC used as a dedicated input only.

In the "Small-PAL" and "Medium-PAL" modes (Table I), pins\* 1 and 11 are always dedicated inputs. In the "Registered-PAL" mode, however, pin\* 1 becomes the clock input controlling all OLMC registers, and pin\* 11 becomes the output enable (G) input controlling the TRI-STATE outputs of all registered OLMCs. Within the "Small-PAL" and "Registered OLMCs. Within the "Small-PAL" and "Registered

istered-PAL" modes in Table I, the functions of pins\* 12 through 19 can be selected individually from either of the two functions listed. For example, in "Registered-PAL" mode, pins\* 12 through 19 can each be designated as either a registered output or a combinatorial I/O. The "Medium-PAL" mode represents a single fixed configuration used to emulate combinatorial medium PAL devices (16L8, 16H8, 16P8).

Table II lists the bipolar PAL products which the GAL16V8QS can emulate, and the specific input/output configurations used. This is just a subset, however, of all the configurations provided in Table I.

All registers in a GAL device are reset to the low state upon power-up. The active-low outputs, in turn, assume high logic levels (if enabled) regardless of the selected output polarity. This may simplify sequential circuit design and test. To ensure successful power-up reset,  $V_{\rm CC}$  must rise monotonically until the specified operating voltage is attained. During power-up, the clock input should assume a valid, stable logic state as early as possible (within the specified time,  $t_{\rm PR}$ ) to avoid interfering with the reset operation. The clock input should also remain stable until after the power-up reset operation is completed to allow the registers to capture the proper next state on the first high-going clock transition.

It should be noted that the switching of any input not logically connected to a product term or logic function has no effect on the associated output logic state. To minimize power consumption, however, unused inputs should be connected to a stable logic level such as ground or  $V_{CC}$  (CMOS GAL inputs may be tied directly to the supply voltage without causing excessive loading conditions).

\*Applies to 20-pin DIP, 20-pin SOIC and 20-lead PLCC packages for GAL16V8QS.

#### **Quiet Series**

As system frequencies increase, so do concerns over both device generated and system generated noise. Proper printed circuit board layout and construction techniques should be followed by the designer to minimize system generated noise, additionally however, IC manufacturers should bear the responsibility to minimize device generated noise. One of the biggest sources of device generated noise is ground bounce. Ground bounce not only manifests itself on the ground pin, but more importantly on quiet outputs, input thresholds, and other internal circuitry. Noise on quiet outputs can cause the false triggering of external devices, while a shift in the device's internal ground can cause false triggering and even instability in the device itself. Often these problems are attributed to a damaged or faulty PLD when, in fact, the PLD has marginally lower noise immunity than other seemingly identical devices.

The magnitude of ground bounce has a direct correlation with output edge rates. Therefore National's Quiet Series devices have slower more "gentle" edges. National uses an advanced  $0.8\mu$  back-biased EECMOS process to decrease propagation times in order to accomodate the slower edge rates. The result is a very robust, high speed PLD. Since National offers Quiet Series devices at comparable pricing to non-Quiet Series devices, Quiet Series devices are recommended for new designs.

# GAL16V8QS Block Diagram/DIP and SOIC Connections

FIGURE 1

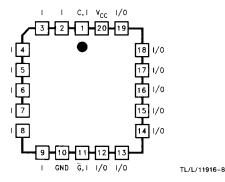

#### **GAL16V8QS PLCC Connections**

FIGURE 2

## **Quiet Series Testing**

Quiet Series testing is performed with seven outputs switching. The remaining output, referred to as the "quiet output", maintains a low logic level.  $V_{\rm OLP}$  and  $V_{\rm OLV}$  measure the peak and valley, respectively, of the "bounce" on this quiet output (referenced to ground) as the seven outputs swing from high to low. Notice  $V_{\rm OLP}$  and  $V_{\rm OLV}$  do not directly measure the ground itself (which is stabilized through the use of proper PCB design techniques), but more importantly quantify how ground bounce affects a non-switching output. Noise on the quiet output will be propagated to the inputs of subsequent devices and can falsely trigger these devices. False triggering occurs when the magnitude of a signal exceeds the input thresholds of these devices for a sufficient duration. Therefore, the width of the bounce,  $t_{\rm WGB}$ , is also

measured. Based on extensive empirical analysis, the values for V<sub>OLP</sub> and t<sub>WGB</sub> have been found to be below the triggering requirements of common types of logic devices.

Just as ground bounce affects external circuitry, it also affects the internal silicon circuitry of the PLD. Usually the effect of ground bounce on device input thresholds is most significant.  $V_{\rm IHD}$  and  $V_{\rm ILD}$  measure the effect of a change in the ground potential on the input thresholds of the PLD.  $V_{\rm IHD}$  and  $V_{\rm ILD}$  are measured with seven outputs switching at 1 MHz while the input voltage at one input is gradually changed until the device shows signs of triggering. Note that the outputs may only exhibit small differences that show they are being affected by the input under test. The test is repeated on all inputs.

TL/L/11916-4

Typical Quiet Electrical Measurements Seven Outputs Switching into AC Test Load  $V_{CC}=5.0V, T=25^{\circ}C$

# **OLMC Configuration**

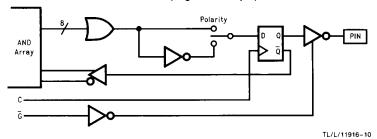

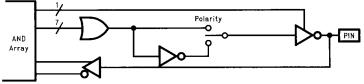

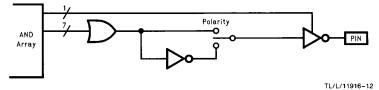

#### **OUTPUT (Active Combinatorial Output)**

TL/L/11916-9

#### **REGISTER (Registered Output)**

#### I/O (Combinatorial Input/Output)

TL/L/11916-11

#### TRI-STATE (TRI-STATE Combinatorial Output)

FIGURE 3

## Clock/Input Frequency Specifications

The clock frequency (f<sub>CLK</sub>) parameter listed in the Recommended Operating Conditions table specifies the maximum speed at which the GAL registers are guaranteed to operate. Clock frequency is defined differently for the two cases in which register feedback is used versus when it is not. In a data-path type application, when the logic functions fed into the registers are not dependent on register feedback from the previous cycle (i.e. based only on external inputs), the minimum required cycle period (f<sub>CLK</sub>-1 without feedback) is defined as the greater of the minimum clock period (tw high + tw low) and the minimum "data window" period (tsu + t<sub>H</sub>). This assumes optimal alignment between data inputs and the clock input. In sequential logic applications such as state machines, the minimum required cycle period (t<sub>CYCLE</sub> = f<sub>CLK</sub>-1 with feedback) is defined as t<sub>CLK</sub> + t<sub>SU</sub>. This provides sufficient time for outputs from the registers to feed back through the logic array and set up on the inputs to the registers before the end of each cycle.

The input frequency ( $f_1$ ) parameter specifies the maximum rate at which each GAL input can be toggled and still produce valid logic transitions on each combinatorial output. The  $f_1$  specification is derived as the inverse of the combinatorial propagation delay ( $t_{PD}$ ).

## **Security Cell**

A security cell is provided on all GAL16V8QS devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, the circuitry enabling array access is disabled, preventing further programming or verification of the array. The security cell can be erased only in conjunction with the array during a bulk erase cycle, so the original configuration can never be examined once this cell is programmed.

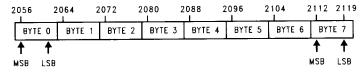

## **Electronic Signature**

Each GAL16V8QS device contains a User Electronic Signature (UES) word consisting of 64 bits of reprogrammable memory. The electronic signature word can be programmed to contain any identification information desired by the user. Some uses include pattern identification labels, revision numbers, dates, inventory control information, etc. The data stored in the electronic signature word has no effect on the functionality of the device. The information is read out of the device using the normal program verification procedure provided by the programming equipment. The information may be accessed at any time independent of the state of the security cell. National's OPAL and OPAL jr development softwares allow electronic signature data to be entered by the user and downloaded to the programming equipment.

#### **Bulk Erase**

The programming equipment automatically performs a bulk erase operation prior to each programming operation. No special erase operation need be performed by the user. Bulk erase clears the logic array, architecture cells, security cell, and electronic signature information. The GAL device is thereby reverted back to its virgin state.

### Manufacturer Testing

Because of EECMOS technology, GAL devices can be reprogrammed in milliseconds. This allows each device to be completely tested by the manufacturer using numerous logic array and architecture patterns prior to shipping. Every programmable cell and every logic path through every device is fully tested for programmability, functionality and performance to all AC and DC parameters. The customer can therefore expect 100% programming and functional yield and 100% compliance of all GAL products to datasheet specifications.

### **Development Support**

National's GAL16V8QS family is supported by popular industry-standard PLD development software and device programmers. In addition, GAL16V8QS devices are supported by National's OPAL and OPAL jr PLD development software packages. OPAL and OPAL jr also contain a PAL to GAL conversion utility for converting designs from PAL devices to GAL devices. OPAL jr is distributed free of charge and can be obtained through your local National Semiconductor sales representative or by downloading it from National's PLD Applications and Support Bulletin Board at (408) 721-7418, (8-n-1), 2400-19200 bps.

National strongly recommends using only approved programming hardware and software for developing GAL designs. Programming using unapproved equipment generally voids all guarantees. Approved programmers incorporate specialized programming algorithms that program the array and automatically configure the architecture cells.

## **OLMC Configuration Details**

Understanding the information in this section is not essential when using approved programming equipment and software for developing GAL designs. This is a more thorough disclosure of the GAL architecture provided for direct JEDEC cell-map editing and diagnostic purposes. This section alone, however, does not contain sufficient information to implement the GAL programming algorithm. If detailed specifications of the GAL programming algorithm are needed, please contact the National Semiconductor Programmable Products Applications and Support Department.

### **OLMC Configuration Details (Continued)**

As mentioned in the Functional Description, the OLMC is responsible for selecting input and/or output paths, registered vs. combinatorial outputs, active-high or low polarity, and common vs. locally-controlled TRI-STATE control. Additionally, the OLMCs select between alternate logic array input paths to maintain JEDEC cell-map compatibility with either "small-PAL" or "medium-PAL" logic arrays.

The various configurations of the OLMCs are controlled by a set of programmable "architecture" cells, separate from the logic-defining array cells. Each GAL device contains two "global" architecture cells, "SYN" and "ACO", which affect all OLMCs. Each of the device's eight OLMCs also contains two "local" cells, "AC1" and "XOR". The OLMC Logic Diagram in Figure 4 shows how the architecture cells select the different paths through the OLMC.

The SYN bit controls whether a device will have any registered outputs (SYN = 0) or will be purely combinatorial (SYN=1). The SYN bit determines whether device pins\* 1 and 11 are used as the clock and global TRI-STATE control

inputs (SYN=0) or whether they are ordinary inputs (SYN=1). The AC0 bit selects between the "Small-PAL" mode and the "Medium/Registered-PAL" modes. The function of the AC1 bits depend on the state of the AC0 bit. In "Small-PAL" mode (AC0=0), the AC1 bit in each OLMC determines whether the associated device pin is an output (AC1=0) or an input (AC1=1). In "Registered-PAL" mode (AC0=1), the AC1 bit determines whether each OLMC is registered (AC1=0) or combinatorial (AC1=1). In "Medium-PAL" mode (AC0=1), the AC1 bits in all OLMCs must be set to 1 (combinatorial). All of the valid architecture bit configurations are shown in the OLMC Architecture table (Table I).

Independent of SYN, AC0 and the AC1 bits, the XOR bit in each OLMC selects between active-low (XOR = 0) or active-high (XOR = 1) output polarity.

\*Applies to both 20-pin DIP and 20-lead PLCC packages for GAL16V8QS.

### **OLMC Logic Diagram**

\*Applies to 20-pin DIP, 20-pin SOIC and 20-lead PLCC packages for GAL16V8QS.

FIGURE 4

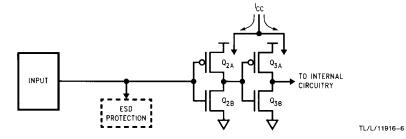

## **Input Schematic**

**TABLE I. OLMC Architecture Configuration**

| Pin Number            | "Small P                                        | AL" Mode             | "Registered                       | I PAL"Mode           | "Medium PAL" Mode              |  |

|-----------------------|-------------------------------------------------|----------------------|-----------------------------------|----------------------|--------------------------------|--|

| Pili Number           | Fund                                            | ction                | Fund                              | etion                | Function                       |  |

| 1                     | INPUT                                           | INPUT                | CLOCK                             | CLOCK                | INPUT                          |  |

| 19***                 | 1/0                                             | INPUT                | REGISTER                          | 1/0                  | TRI-STATE**                    |  |

| 18***                 | 1/0                                             | INPUT                | REGISTER                          | 1/0                  | 1/0                            |  |

| 17***                 | 1/0                                             | INPUT                | REGISTER                          | 1/0                  | 1/0                            |  |

| 16***                 | OUTPUT*                                         | NC NC                | REGISTER                          | 1/0                  | 1/0                            |  |

| 15***                 | OUTPUT*                                         | NC                   | REGISTER                          | 1/0                  | 1/0                            |  |

| 14***                 | 1/0                                             | INPUT                | REGISTER                          | 1/0                  | 1/0                            |  |

| 13***                 | I/O                                             | INPUT                | REGISTER                          | 1/0                  | 1/0                            |  |

| 12***                 | 1/0                                             | INPUT                | REGISTER                          | 1/0                  | TRI-STATE**                    |  |

| 11                    | INPUT                                           | INPUT                | G                                 | G                    | INPUT                          |  |

| Architecture          | AC1 <sub>n</sub> = 0                            | AC1 <sub>n</sub> = 1 | AC1 <sub>n</sub> = 0              | AC1 <sub>n</sub> = 1 | AC1 <sub>n</sub> = 1           |  |

| Bits<br>Configuration | SYN = 1                                         | , AC0 = 0            | SYN = 0,                          | AC0 = 0              | SYN = 1, AC0 = 0               |  |

|                       | All outputs are combinatorial and always active |                      | At least one output is registered |                      | All I/O pins are combinatorial |  |

Note: Pin numbers above apply to 20-pin DIP, 20-pin SOIC and 20-lead PLCC packages for GAL16V8.

- Active combinatorial output

TRI-STATE combinatorial output

- \*\*\* AC1<sub>n</sub> applies to these I/O pins only

## **PAL Replacement Configurations**

**TABLE II. OLMC Architecture Configuration**

<sup>\*</sup>Active combinatorial output.

<sup>\*\*</sup>TRI-STATE combinatorial output.

## **GAL16V8QS Logic Diagram**

USER ELECTRONIC SIGNATURE WORD:

SYN=2192 AC0=2193

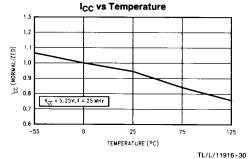

5.50

TL/L/11916-29

T = 25°C, F = 25 MHz

I<sup>CC</sup> (NORMALIZED) 0.96.0 0.96.0 0.94 1.00

0.98 0.96

0.92

4.50

4.75

$v_{cc}(v)$

## Ordering Information†

#### **Commercial Devices**

| t <sub>PD</sub> (ns) | t <sub>SU</sub> (ns) | t <sub>CLK</sub> (ns) | I <sub>CC</sub> (mA) | QS | Part Number     | Package |

|----------------------|----------------------|-----------------------|----------------------|----|-----------------|---------|

| 10                   | 5                    | 7.5                   | 115                  | Y  | GAL16V8QS-10LNC | PDIP    |

| 10                   | 5                    | 7.5                   | 115                  | Y  | GAL16V8QS-10LVC | PLCC    |

| 10                   | 5                    | 7.5                   | 115                  | Y  | GAL16V8QS-10LMC | SOIC    |

| 15                   | 7                    | 9                     | 90                   | Υ  | GAL16V8QS-15LNC | PDIP    |

| 15                   | 7                    | 9                     | 90                   | Y  | GAL16V8QS-15LVC | PLCC    |

| 15                   | 7                    | 9                     | 90                   | Y  | GAL16V8QS-15LMC | SOIC    |

#### **Industrial Devices**

| t <sub>PD</sub> (ns) | t <sub>SU</sub> (ns) | t <sub>CLK</sub> (ns) | I <sub>CC</sub> (mA) | QS | Part Number     | Package |

|----------------------|----------------------|-----------------------|----------------------|----|-----------------|---------|

| 10                   | 5                    | 7.5                   | 130                  | Y  | GAL16V8QS-10LNI | PDIP    |

| 10                   | 5                    | 7.5                   | 130                  | Y  | GAL16V8QS-10LVI | PLCC    |

| 10                   | 5                    | 7.5                   | 130                  | Y  | GAL16V8QS-10LMI | SOIC    |

| 15                   | 7                    | 9                     | 130                  | Y  | GAL16V8QS-15LNI | PDIP    |

| 15                   | 7                    | 9                     | 130                  | Y  | GAL16V8QS-15LVI | PLCC    |

| 15                   | 7                    | 9                     | 130                  | Y  | GAL16V8QS-15LMI | SOIC    |

## **Military Devices**

Contact your local National Semiconductor sales representative for availability of military grade GAL16V8QS devices.

†Quiet Series devices (GAL16V8QS) recommended for new designs. Refer to 1993 Programmable Logic Devices Databook and Design Guide (Lit # 400081) for quarter power GAL16V8A specifications.

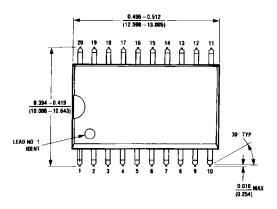

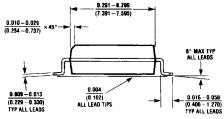

## Physical Dimensions inches (millimeters)

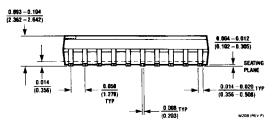

20-Lead (0.300" Wide) Molded Small Outline Package, JEDEC NS Package Number M20B

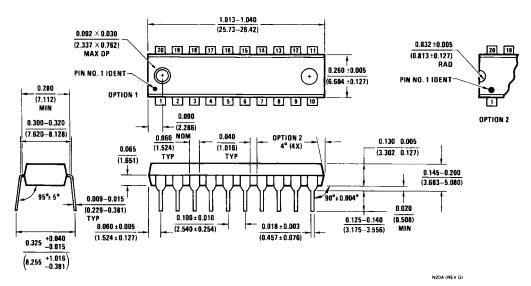

20-Lead (0.300" Wide) Molded Dual-In-Line Package NS Package Number N20A

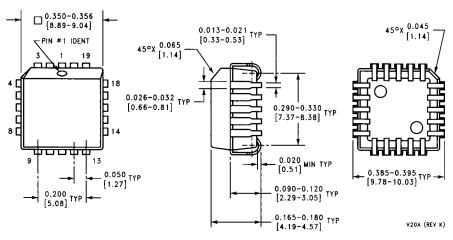

20-Lead Molded Plastic Leaded Chip Carrier

NS Package Number V20A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240 National Semiconductor GmbH Industriestrasse 10 D-8080 Fürstenfeldbruck Germany Tel: (0-81-41) 103-0 Telex: 527649 Fax: (0-81-41) 10-35-06

National Semiconduct Japan Ltd. Sanseido Bldg. 5F 4-15-3 Nishi Shinjuku Shinjuku-Ku, Tokyo 160, Japan Tel: 3-3299-7001 FAX: 3-3299-7000 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block Ocean Centre, 5 Canton Rd. Tsimshatsur, Kowloon Hong Kong Tel: (852) 737-1600 Telex: 51292 NSHKL Fax: (852) 736-9960 National Semiconductores Do Brazil Ltda. Av. Brig. Fana Lima, 1409 6 Andar Cep-01451, Paulistano, Sao Paulo, SP. Brazil Tele: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. 16 Business Park Dr. Notting Hill, VIC 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998