# 4.0 ELECTRICAL SPECIFICATIONS

# 4.1 Absolute Maximum Ratings

| Parameter                                 | Maximum Rating                  |

|-------------------------------------------|---------------------------------|

| Storage Temperature                       | -65 °C to +150 °C               |

| Case Temperature Under Bias(2)            | -40 °C to +125 °C               |

| Supply Voltage wrt. V <sub>SS</sub>       | -0.5V to +6.5V                  |

| Voltage on Other pins wrt V <sub>SS</sub> | -0.5V to V <sub>CC</sub> + 0.5V |

NOTICE: This data sheet contains information on products in the sampling and initial production phases of development. It is valid for the devices indicated in the revision history. The specifications are subject to change without notice.

# 4.2. Operating Conditions

## Operating Conditions (80960CF-33, -25, -16)

| Symbol             | Parameter                                           |                                        | Min                  | Max                  | Units             | Notes |

|--------------------|-----------------------------------------------------|----------------------------------------|----------------------|----------------------|-------------------|-------|

| V <sub>CC</sub>    | Supply Voltage                                      | 80960CF-30<br>80960CF-25<br>80960CF-16 | 4.75<br>4.50<br>4.50 | 5.25<br>5.50<br>5.50 | ٧                 |       |

| f <sub>CLK2x</sub> | Input Clock Frequency (2-x Mode)                    | 80960CF-30<br>80960CF-25<br>80960CF-16 | 0<br>0<br>0          | 60.6<br>50<br>32     | MHz<br>MHz<br>MHz |       |

| fCLK1x             | Input Clock Frequency (1-x Mode)                    | 80960CF-30<br>80960CF-25<br>80960CF-16 | 8<br>8<br>8          | 30.3<br>25<br>16     | MHz<br>MHz<br>MHz | (1)   |

| T <sub>C</sub>     | Case Temperature Under Bias<br>80960CF-30, -25, -16 | PGA Package                            | -40                  | +110                 | °C                |       |

#### NOTES:

#### 4.3 Recommended Connections

Power and ground connections must be made to multiple  $V_{CC}$  and  $V_{SS}$  (GND) pins. Every 80960CF-based circuit board should include power ( $V_{CC}$ ) and ground ( $V_{SS}$ ) planes for power distribution. Every  $V_{CC}$  pin must be connected to the power plane, and every  $V_{SS}$  pin must be connected to the ground plane. Pins identified as "N.C." **must not** be connected in the system.

Liberal decoupling capacitance should be placed near the 80960CF. The processor can cause transient power surges when its numerous output buffers transition, particularly when connected to large capacitive loads. Low inductance capacitors and interconnects are recommended for best high frequency electrical performance. Inductance can be reduced by shortening board traces between the processor and decoupling capacitors as much as possible. Capacitors specifically designed for PGA packages will offer the lowest possible inductance.

For reliable operation, always connect unused inputs to an appropriate signal level. In particular, any unused interrupt ( $\overline{X}|\overline{NT}, \overline{NM}|$ ) or DMA ( $\overline{D}\overline{REQ}$ ) input should be connected to  $V_{CC}$  through a pull-up resistor, as should  $\overline{B}\overline{T}\overline{E}\overline{RM}$  if not used. Pull-up resistors should be in the range of 20 K $\Omega$  for each pin tied high. If  $\overline{R}\overline{E}\overline{A}\overline{D}\overline{Y}$  or HOLD are not used, the unused input should be connected to ground. N.C. pins must always remain unconnected. Refer to the *i960 CA Microprocessor Reference Manual* for more information.

<sup>\*</sup>WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

<sup>(1)</sup> When in the 1-x input clock mode, CLKIN is an input to an internal phase-locked loop and must maintain a minimum frequency of 8 MHz for proper processor operation. However, in the 1-x Mode, CLKIN may still be stopped when the processor either is in a reset condition or is reset. If CLKIN is stopped, the specified RESET low time must be provided once CLKIN restarts and has stabilized.

<sup>(2)</sup> Case temperatures are "Instant On".

# 4.4. DC Specifications

#### **DC Characteristics**

(80960CF-30, -25, -16 under the conditions described in Section 4.2, Operating Conditions.)

| Symbol           | Parameter                                                                                                                         | Min                          | Max                   | Units | Notes                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-------|-----------------------------------------|

| VIL              | Input Low Voltage for all pins except RESET                                                                                       | -0.3                         | 0.8                   | >     |                                         |

| V <sub>IH</sub>  | Input High Voltage for all pins except RESET                                                                                      | 2.0                          | V <sub>CC</sub> + 0.3 | ٧     |                                         |

| VOL              | Output Low Voltage                                                                                                                |                              | 0.45                  | ٧     | I <sub>OL</sub> = 5 mA                  |

| VoH              | Output High Voltage $I_{OH} = -1 \text{mA}$<br>$I_{OH} = -200 \mu \text{A}$                                                       | 2.4<br>V <sub>CC</sub> - 0.5 |                       | > >   |                                         |

| V <sub>ILR</sub> | Input Low Voltage for RESET                                                                                                       | - 0.3                        | 1.5                   | ٧     |                                         |

| VIHR             | Input High Voltage for RESET                                                                                                      | 3.5                          | $V_{CC} + 0.3$        | ٧     |                                         |

| t <sub>L11</sub> | Input Leakage Current for each pin except:  BTERM, ONCE, DREQ3:0, STEST,  EOP3:0/TC3:0, NMI, XINT7:0,  READY, HOLD, BOFF, CLKMODE |                              | ± 15                  | μΑ    | 0V≤V <sub>IN</sub> ≤V <sub>CC</sub> (1) |

| l <sub>Ll2</sub> | Input Leakage Current for:<br>BTERM, ONCE, DREQ3:0, STEST,<br>EOP3:0/TC3:0, NMI, XINT7:0, BOFF                                    | 0                            | -325                  | μΑ    | V <sub>IN</sub> = 0.45V (2)             |

| ILI3             | Input Leakage Current for:<br>READY, HOLD, CLKMODE                                                                                | 0                            | 500                   | μΑ    | V <sub>IN</sub> = 2.4V (3)              |

| ILO              | Output Leakage Current                                                                                                            |                              | ±15                   | μΑ    | 0.45V≤V <sub>OUT</sub> ≤V <sub>CC</sub> |

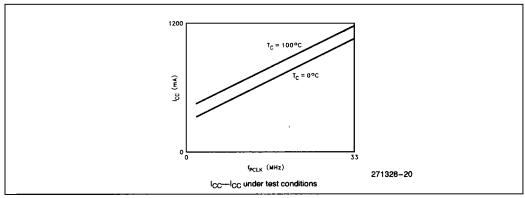

| lcc              | Supply Current (80960CF-30) ICC Max ICC Typ                                                                                       |                              | 1150<br>960           | mA    | (4)<br>(5)                              |

| lcc              | Supply Current (80960CF-25) ICC Max ICC Typ                                                                                       |                              | 950<br>775            | mA    | (4)<br>(5)                              |

| lcc              | Supply Current (80960CF-16)  ICC Max ICC Typ                                                                                      |                              | 750<br>575            | mA    | (4)<br>(5)                              |

| IONCE            | ONCE-mode Supply Current                                                                                                          |                              | 150                   | mA    |                                         |

| C <sub>IN</sub>  | Input Capacitance for:<br>CLKIN, RESET, ONCE,<br>READY, HOLD, DREQ3:0, BOFF<br>XINT7:0, NMI, BTERM, CLKMODE                       | 0                            | 12                    | pF    | F <sub>C</sub> = 1 MHz                  |

| Cout             | Output Capacitance of each output pin                                                                                             |                              | 12                    | ρF    | F <sub>C</sub> = 1 MHz, (6)             |

| CI/O             | I/O Pin Capacitance                                                                                                               |                              | 12                    | pF    | F <sub>C</sub> = 1 MHz                  |

### NOTES:

- (1) No Pull-up or pull-down.

- (2) These pins have internal pullup resistors.

- (3) These pins have internal pulldown resistors.

- (4) Measured at worst case frequency, V<sub>CC</sub> and temperature, with device operating and outputs loaded to the test conditions described in **Section 4.5.1, AC Test Conditions**.

- (5) I<sub>CC</sub> Typical is not tested.

- (6) Output Capacitance is the capacitive load of a floating output.

- (7) CLKMODE pin has a pulldown resistor only when ONCE pin is deasserted.

# 4.5 AC Specifications

# AC Characteristics — 80960CF-30

(80960CF-30 only, under the conditions described in Section 4.2, Operating Conditions and Section 4.5.1, AC Test Conditions.) See notes which follow this table.

| Symbol          | Parame                                | ter                               | Min                                              | Max                                           | Units    | Notes      |

|-----------------|---------------------------------------|-----------------------------------|--------------------------------------------------|-----------------------------------------------|----------|------------|

| INPUT CL        | OCK(10)                               |                                   | -                                                |                                               |          |            |

| Τ <sub>F</sub>  | CLKIN Frequency                       |                                   | 0                                                | 60.6                                          | MHz      | (1)        |

| T <sub>C</sub>  | CLKIN Period                          | In 1-x Mode (f <sub>CLK1x</sub> ) | 33                                               | 125                                           | ns       | (1,12)     |

|                 |                                       | In 2-x Mode (f <sub>CLK2x</sub> ) | 16.5                                             | 8                                             | ns       | (1)        |

| Tcs             | CLKIN Period Stability                | In 1-x Mode (f <sub>CLK1x</sub> ) |                                                  | ±0.1%                                         | Δ        | (1,13)     |

| T <sub>CH</sub> | CLKIN High Time                       | In 1-x Mode (f <sub>CLK1x</sub> ) | 6                                                | 62.5                                          | ns       | (1,12)     |

|                 |                                       | In 2-x Mode (f <sub>CLK2x</sub> ) | 6                                                | ∞                                             | ns       | (1)        |

| $T_{CL}$        | CLKIN Low Time                        | In 1-x Mode (f <sub>CLK1x</sub> ) | 6                                                | 62.5                                          | ns       | (1,12)     |

|                 | 01.491.51                             | In 2-x Mode (f <sub>CLK2x</sub> ) | 6                                                | - 0                                           | ns       | (1)        |

| T <sub>CR</sub> | CLKIN Rise Time                       |                                   | 0                                                | 6                                             | ns       | (1)        |

| T <sub>CF</sub> | CLKIN Fall Time                       |                                   | 0                                                | 6                                             | ns       | (1)        |

| OUTPUT          | CLOCKS(9)                             |                                   |                                                  |                                               |          |            |

| T <sub>CP</sub> | CLKIN to PCLK2:1 Delay                | In 1-x Mode (f <sub>CLK1x</sub> ) | -2                                               | 2                                             | ns       | (1,3,13,14 |

|                 | <del></del>                           | In 2-x Mode (f <sub>CLK2x</sub> ) | 2                                                | 25                                            | ns       | (1,3)      |

| T               | PCLK2:1 Period                        | In 1-x Mode (f <sub>CLK1x</sub> ) |                                                  | Ċ.                                            | ns       | (1,13)     |

|                 | DCL KOA Likeb Time                    | In 2-x Mode (f <sub>CLK2x</sub> ) | <del>                                     </del> | T <sub>C</sub>                                | ns       | (1,3)      |

| T <sub>PH</sub> | PCLK2:1 High Time                     |                                   | (T/2) - 2                                        | T/2                                           | ns       | (1,13)     |

| TPL             | PCLK2:1 Low Time                      |                                   | (T/2) - 2                                        | T/2                                           | ns       | (1,13)     |

| T <sub>PR</sub> | PCLK2:1 Rise Time                     | <del></del>                       | 1                                                | 4                                             | ns       | (1,3)      |

| TPF             | PCLK2:1 Fall Time                     |                                   | 1                                                | 4                                             | ns       | (1,3)      |

| SYNCHR          | ONOUS OUTPUTS(10)                     |                                   |                                                  |                                               |          | 1          |

| TOV             | Output Valid Delay, Outpu             |                                   | _                                                |                                               |          | (6, 11)    |

| TOH             | T <sub>OV1</sub> , T <sub>OH1</sub>   | A31:2                             | 3                                                | 14                                            | ns       |            |

|                 | Tova, Toha                            | BE3:0<br>ADS                      | 3<br>6                                           | 16<br>18                                      | ns<br>ns |            |

|                 | Тоv3, Тон3<br>Тоv4, Тон4              | W/R                               | 3                                                | 18                                            | ns       |            |

|                 | TOV5, TOH5                            | D/C, SUP, DMA                     | 4                                                | 16                                            | ns       | 1          |

|                 | Tove, Tohe                            | BLAST, WAIT                       | 5                                                | 16                                            | ns       | ļ          |

|                 | T <sub>OV7</sub> , T <sub>OH7</sub>   | DEN                               | 3                                                | 16                                            | ns       |            |

|                 | Tova, Toha                            | HOLDA, BREQ                       | 4                                                | 16                                            | ns       |            |

|                 | TOV9, TOH9                            | LOCK                              | 4                                                | 16                                            | ns       |            |

|                 | TOV10, TOH10                          | DACK3:0                           | 4                                                | 18                                            | ns       |            |

|                 | TOV11, TOH11                          | D31:0                             | 3                                                | 16                                            | ns       |            |

|                 | TOV12, TOH12                          | DT/R                              | T/2 + 3                                          | T/2 + 14                                      | ns       | ١          |

|                 | TOV13, TOH13                          | FAIL                              | 2                                                | 14                                            | ns       | (6, 11)    |

|                 | T <sub>OV14</sub> , T <sub>OH14</sub> | EOP/TC3:0                         | 3                                                | 18                                            | ns       |            |

| TOF             | Output Float for all output           | s                                 | 3                                                | 22                                            | ns       | (6)        |

| SYNCHR          | ONOUS INPUTS(10)                      |                                   |                                                  |                                               |          |            |

| T <sub>IS</sub> | Input Setup                           |                                   |                                                  |                                               |          |            |

|                 | T <sub>IS1</sub>                      | D31:0                             | 3                                                | 1                                             | ns       | (1,11)     |

|                 | T <sub>IS2</sub>                      | BOFF                              | 17                                               |                                               | ns       | (1,11)     |

|                 | T <sub>IS3</sub>                      | BTERM/READY                       | 7                                                |                                               | ns       | (1,11)     |

|                 | T <sub>IS4</sub>                      | HOLD                              | 7                                                | ļ                                             | ns       | (1,11)     |

| $T_IH$          | Input Hold                            | <b>A</b>                          | _                                                |                                               |          |            |

|                 | TIH1                                  | D31:0                             | 5                                                |                                               | ns       | (1,11)     |

|                 | T <sub>IH2</sub>                      | BOFF                              | 5                                                |                                               | ns       | (1,11)     |

|                 | TIH3                                  | BTERM/READY                       | 2                                                |                                               | ns       | (1,11)     |

|                 | T <sub>1H4</sub>                      | HOLD                              | 3                                                | <u>L.                                    </u> | ns       | (1,11)     |

#### AC Characteristics - 80960CF-30

(80960CF-30 only, under the conditions described in **Section 4.2, Operating Conditions** and **Section 4.5.1, AC Test Conditions**.) See notes which follow this table. (Continued)

| Symbol             | Parameter                                                   | Min             | Max             | Units       | Notes        |

|--------------------|-------------------------------------------------------------|-----------------|-----------------|-------------|--------------|

| RELATIVI           | E OUTPUT TIMINGS(9,7)                                       |                 |                 | <del></del> | <del>'</del> |

| T <sub>AVSH1</sub> | A31:2 Valid to ADS Rising                                   | T - 4           | T + 4           | ns          |              |

| T <sub>AVSH2</sub> | BE3:0, W/R, SUP, D/C, DMA, DACK3:0 Valid to ADS Rising      | T 6             | T + 6           | ns          |              |

| TAVEL1             | A31:2 Valid to DEN Falling                                  | T - 4           | T + 4           | ns          |              |

| TAVEL2             | BE3:0, W/R, SUP, INST,<br>DMA, DACK3:0 Valid to DEN Falling | T - 6           | T + 6           | ns          |              |

| TNLQV              | WAIT Falling to Output Data Valid                           | ±               | 6               | ns          |              |

| T <sub>DVNH</sub>  | Output Data Valid to WAIT Rising                            | N*T - 6         | N*T + 6         | ns          | (4)          |

| TNLNH              | WAIT Falling to WAIT Rising                                 | N*T             | ± 4             | ns          | (4)          |

| TNHQX              | Output Data Hold after WAIT Rising                          | (N + 1) * T - 6 | (N + 1) * T + 6 | ns          | (5)          |

| TEHTV              | DT/R Hold after DEN High                                    | T/2 - 6         | 00              | ns          | (6)          |

| T <sub>TVEL</sub>  | DT/R Valid to DEN Falling                                   | T/2 - 4         | T/2 + 4         | ns          | (7)          |

| RELATIV            | E INPUT TIMINGS(7)                                          |                 |                 |             | -            |

| T <sub>IS5</sub>   | RESET Input Setup (2x Clock Mode)                           | 6               | -               | ns          | (14)         |

| T <sub>IH5</sub>   | RESET Input Hold (2x Clock Mode)                            | 5               |                 | ns          | (14)         |

| T <sub>IS6</sub>   | DREQ3:0 Input Setup                                         | 12              |                 | ns          | (8)          |

| T <sub>tH6</sub>   | DREQ3:0 Input Hold                                          | 7               |                 | ns          | (8)          |

| T <sub>IS7</sub>   | XINT7:0, NMI Input Setup                                    | 7               |                 | ns          | (8)          |

| T <sub>IH7</sub>   | XINT7:0, NMI Input Hold                                     | 3               |                 | ns          | (8)          |

| TISB               | RESET Input Setup (1x Clock Mode)                           | 3               |                 | ns          | (15)         |

| T <sub>IH8</sub>   | RESET Input Hold (1x Clock Mode)                            | T/4 + 1         |                 | ns          | (15)         |

#### NOTES:

- 1. See Section 4.5.2, AC Timing Waveforms for waveforms and definitions.

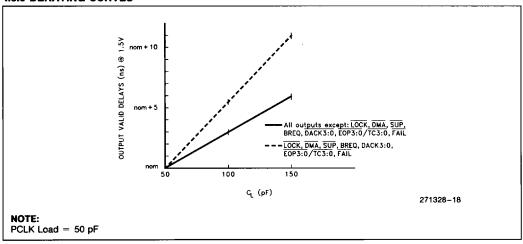

- 2. See Figure 22 for capacitive derating information for output delays and hold times.

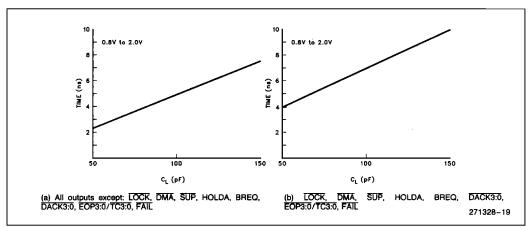

- 3. See Figure 23 for capacitive derating information for rise and fall times.

- Where N is the number of N<sub>RAD</sub>, N<sub>RDD</sub>, N<sub>WAD</sub>, or N<sub>WDD</sub> wait states that are programmed in the Bus Controller Region Table. When there are no wait states in an access, WAIT never goes active.

- N = Number of wait states inserted with READY.

- 6. Output Data and/or DT/R may be driven indefinitely following a cycle if there is no subsequent bus activity.

- 7. See Notes 1, 2 and 3.

- 8. Since asynchronous inputs are synchronized internally by the 80960CF they have no required setup or hold times in order to be recognized and for proper operation. However, to guarantee recognition of the input at a particular edge of PCLK2:1 the setup times shown must be met. Asynchronous inputs must be active for at least two consecutive PCLK2:1 rising edges to be seen by the processor.

- 9. These specifications are guaranteed by the processor.

- 10. These specifications must be met by the system for proper operation of the processor.

- This timing is dependent upon the loading of PCLK2:1. Use the derating curves of Section 4.5.3 to adjust the timing for PCLK2:1 loading.

- 12. In the 1-x input clock mode, the maximum input clock period is limited to 125 ns while the processor is operating. When the processor is in reset, the input clock may stop even in 1-x mode.

- 13. When in the 1-x input clock mode, these specifications assume a stable input clock with a period variation of less than ±0.1% between adjacent cycles.

- 14. In 2x clock mode, RESET is an asynchronous input which has no required setup and hold time for proper operation. However, to guarantee the device exits reset synchronized to a particular clock edge, the RESET pin must meet setup and hold times to the falling edge of the CLKIN. (See Figure 28a.)

- 15. In 1x clock mode, RESET is an asynchronous input which has no required setup and hold time for proper operation. However, to guarantee the device exits reset synchronized to a particular clock edge, the RESET pin must be deasserted while CLKIN is high and meet setup and hold times to the rising edge of the CLKIN. (See Figure 28b.)

# **SPECIAL ENVIRONMENT 80960CF-30, -25, -16**

AC Characteristics — 80960CF-25 (80960CF-25 only, under the conditions described in Section 4.2, Operating Conditions and Section 4.5.1, AC Test Conditions.)

| Symbol                             | Parame                                | eter                                                                   | Min       | Max                 | Units    | Notes                |

|------------------------------------|---------------------------------------|------------------------------------------------------------------------|-----------|---------------------|----------|----------------------|

|                                    |                                       | INPUT CLOCK                                                            | (10)      |                     | -        |                      |

| T <sub>F</sub>                     | CLKIN Frequency                       |                                                                        | 0         | 50                  | MHz      | (1)                  |

| T <sub>C</sub>                     | CLKIN Period                          | In 1-x Mode (f <sub>CLK1x</sub> )                                      | 40        | 125                 | ns       | (1,12)               |

|                                    | 0.100.5                               | In 2-x Mode (f <sub>CLK2x</sub> )                                      | · 20      |                     | ns       | (1)                  |

| T <sub>CS</sub>                    | CLKIN Period Stability                | In 1-x Mode (f <sub>CLK1x</sub> )                                      |           | ±0.1%               | Δ        | (1,13)               |

| T <sub>CH</sub>                    | CLKIN High Time                       | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | 8<br>8    | 62.5<br>∞           | ns<br>ns | (1,12)<br>(1)        |

| T <sub>CL</sub>                    | CLKIN Low Time                        | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | 8         | 62.5<br>∞           | ns<br>ns | (1,12)<br>(1)        |

| T <sub>CR</sub>                    | CLKIN Rise Time                       | · · · · · · · · · · · · · · · · · · ·                                  | 0         | 6                   | ns       | (1)                  |

| T <sub>CF</sub>                    | CLKIN Fall Time                       |                                                                        | 0         | 6                   | ns       | (1)                  |

| <u> </u>                           |                                       | OUTPUT CLOC                                                            | KS(9)     | _                   |          |                      |

| T <sub>CP</sub>                    | CLKIN to PCLK2:1 Delay                | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | -2<br>2   | 2<br>25             | ns<br>ns | (1,3,13,14)<br>(1,3) |

| Т                                  | PCLK2:1 Period                        | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | Т         | c<br>r <sub>c</sub> | ns<br>ns | (1,13)<br>(1,3)      |

| T <sub>PH</sub>                    | PCLK2:1 High Time                     |                                                                        | (T/2) - 3 | T/2                 | ns       | (1,13)               |

| T <sub>PL</sub>                    | PCLK2:1 Low Time                      |                                                                        | (T/2) - 3 | T/2                 | ns       | (1,13)               |

| TPR                                | PCLK2:1 Rise Time                     |                                                                        | 1         | 4                   | ns       | (1,3)                |

| TPF                                | PCLK2:1 Fall Time                     |                                                                        | 1         | 4                   | ns       | (1,3)                |

| ·rr                                |                                       | SYNCHRONOUS OU                                                         | TPUTS(10) |                     |          | (-1-7                |

| Tau                                | Output Valid Delay, Outpu             |                                                                        | T         |                     |          | (6, 11)              |

| T <sub>OV</sub><br>T <sub>OH</sub> | Tov1, ToH1                            | A31:2                                                                  | 3         | 16                  | ns       | (0, 11)              |

| · OH                               | Tov2, ToH2                            | BE3:0                                                                  | 3         | 18                  | ns       |                      |

|                                    | T <sub>OV3</sub> , T <sub>OH3</sub>   | ADS                                                                    | 6         | 20                  | ns       |                      |

|                                    | Tova, ToH4                            | W/Ā                                                                    | 3         | 20                  | ns       |                      |

|                                    | T <sub>OV5</sub> , T <sub>OH5</sub>   | D/C,SUP,DMA                                                            | 4         | 18                  | ns       |                      |

|                                    | Tove, Tohe                            | BLAST, WAIT                                                            | 5         | 18                  | ns       |                      |

|                                    | T <sub>OV7</sub> , T <sub>OH7</sub>   | DEN                                                                    | ] 3       | 18                  | ns       |                      |

|                                    | Tour Tour                             | HOLDA, BREQ                                                            | 4         | 18                  | ns       |                      |

|                                    | Tove, Tohe                            | · —                                                                    | 4         | 1                   |          |                      |

|                                    | T <sub>OV9</sub> , T <sub>OH9</sub>   | LOCK                                                                   | 1         | 18                  | ns       |                      |

|                                    | Tov10, ToH10                          | DACK3:0                                                                | 4         | 20                  | ns       |                      |

|                                    | Tov11, ToH11                          | D31:0                                                                  | 3         | 18                  | ns       |                      |

|                                    | T <sub>OV12</sub> , T <sub>OH12</sub> | D <u>T/R</u>                                                           | T/2 + 3   | T/2 + 16            | ns       |                      |

|                                    | T <sub>OV13</sub> , T <sub>OH13</sub> | FAIL                                                                   | 2         | 16                  | ns       |                      |

|                                    | T <sub>OV14</sub> , T <sub>OH14</sub> | EOP3:0/TC3:0                                                           | 3         | 20                  | ns       | (6, 11)              |

| TOF                                | Output Float for all outputs          | 3                                                                      | 3         | 22                  | ns       | (6)                  |

|                                    |                                       | SYNCHRONOUS IN                                                         | IPUTS(10) |                     |          | _                    |

| TIS                                | Input Setup                           |                                                                        |           |                     |          |                      |

|                                    | T <sub>IS1</sub>                      | D31:0                                                                  | 5         |                     | ns       | (1,11)               |

|                                    | T <sub>IS2</sub>                      | BOFF                                                                   | 19        |                     | ns       | (1,11)               |

|                                    | T <sub>IS3</sub>                      | BTERM/READY                                                            | 9         |                     | ns       | (1,11)               |

|                                    | T <sub>IS4</sub>                      | HOLD                                                                   | 9         |                     | ns       | (1,11)               |

| T <sub>IH</sub>                    | Input Hold                            | •                                                                      |           |                     |          |                      |

| . 111                              | T <sub>IH1</sub>                      | D31:0                                                                  | 5         | J                   | ns       | (1,11)               |

|                                    | T <sub>IH2</sub>                      | BOFF                                                                   | 7         | Į.                  | ns       | (1,11)               |

|                                    |                                       | BTERM/READY                                                            | 2         | 1                   | ns       | (1,11)               |

|                                    | T <sub>IH3</sub>                      | HOLD                                                                   | 5         |                     | ns       | (1,11)               |

|                                    | T <sub>IH4</sub>                      | HOLD                                                                   | J         | <u> </u>            | 113      | (1,1,1)              |

#### AC Characteristics --- 80960CF-25

(80960CF-25 only, under the conditions described in **Section 4.2, Operating Conditions** and **Section 4.5.1, AC Test Conditions**.) (Continued)

| Symbol             | Parameter                                                   | Min                | Max             | Units | Notes |

|--------------------|-------------------------------------------------------------|--------------------|-----------------|-------|-------|

|                    | RELATIVE                                                    | OUTPUT TIMINGS(9,  | 7)              |       |       |

| T <sub>AVSH1</sub> | A31:2 Valid to ADS Rising                                   | T 4                | T + 4           | ns    |       |

| T <sub>AVSH2</sub> | BE3:0, W/R, SUP, D/C,<br>DMA, DACK3:0 Valid to ADS Rising   | T 6                | T + 6           | ns    |       |

| T <sub>AVEL1</sub> | A31:2 Valid to DEN Falling                                  | T - 4              | T + 4           | ns    |       |

| T <sub>AVEL2</sub> | BE3:0, W/R, SUP, INST,<br>DMA, DACK3:0 Valid to DEN Falling | T - 6              | T + 6           | ns    |       |

| T <sub>NLQV</sub>  | WAIT Falling to Output Data Valid                           | ±                  | : 6             | ns    |       |

| TDVNH              | Output Data Valid to WAIT Rising                            | N*T - 6            | N*T + 6         | ns    | (4)   |

| T <sub>NLNH</sub>  | WAIT Falling to WAIT Rising                                 | N*T                | ± 4             | ns    | (4)   |

| T <sub>NHQX</sub>  | Output Data Hold after WAIT Rising                          | (N + 1) * T - 6    | (N + 1) * T + 6 | ns    | (5)   |

| TEHTV              | DT/R Hold after DEN High                                    | T/2 - 6            | ∞               | ns    | (6)   |

| T <sub>TVEL</sub>  | DT/R Valid to DEN Falling                                   | T/2 - 4            | T/2 + 4         | ns    | (7)   |

|                    | RELATIVE                                                    | E INPUT TIMINGS(7) |                 |       |       |

| T <sub>IS5</sub>   | RESET Input Setup (2x Clock Mode                            | 8                  |                 | ns    | (14)  |

| T <sub>IH5</sub>   | RESET Input Hold (2x Clock Mode)                            | 7                  |                 | ns    | (14)  |

| T <sub>IS6</sub>   | DREQ3:0 Input Setup                                         | 14                 |                 | ns    | (8)   |

| T <sub>IH6</sub>   | DREQ3:0 Input Hold                                          | 9                  |                 | ns    | (8)   |

| T <sub>IS7</sub>   | XINT7:0, NMI Input Setup                                    | 9                  |                 | ns    | (8)   |

| T <sub>IH7</sub>   | XINT7:0, NMI Input Hold                                     | 5                  |                 | ns    | (8)   |

| T <sub>IS8</sub>   | RESET Input Setup (1x Clock Mode)                           | 3                  |                 | ns    | (15)  |

| T <sub>IH8</sub>   | RESET Input Hold (1x Clock Mode)                            | T/4 + 1            |                 | ns    | (15)  |

#### NOTES

- (1) See Section 4.5.2, AC Timing Waveforms for waveforms and definitions.

- (2) See Figure 22 for capacitive derating information for output delays and hold times.

- (3) See Figure 23 for capacitive derating information for rise and fall times.

- (4) Where N is the number of N<sub>RAD</sub>, N<sub>RDD</sub>, N<sub>WAD</sub>, or N<sub>WDD</sub> wait states that are programmed in the Bus Controller Region Table. When there are no wait states in an access, WAIT never goes active.

- (5) N = Number of wait states inserted with READY.

- (6) Output Data and/or DT/R may be driven indefinitely following a cycle if there is no subsequent bus activity.

- (7) See Notes 1, 2 and 3.

- (8) Since asynchronous inputs are synchronized internally by the 80960CF they have no required setup or hold times in order to be recognized and for proper operation. However, to guarantee recognition of the input at a particular edge of PCLK2:1 the setup times shown must be met. Asynchronous inputs must be active for at least two consecutive PCLK2:1 rising edges to be seen by the processor.

- (9) These specifications are guaranteed by the processor.

- (10) These specifications must be met by the system for proper operation of the processor.

- (11) This timing is dependent upon the loading of PCLK2:1. Use the derating curves of **Section 4.5.3** to adjust the timing for PCLK2:1 loading.

- (12) In the 1-x input clock mode, the maximum input clock period is limited to 125 ns while the processor is operating. When the processor is in reset, the input clock may stop even in 1-x mode.

- (13) When in the 1-x input clock mode, these specifications assume a stable input clock with a period variation of less than  $\pm 0.1\%$  between adjacent cycles.

- (14) In 2x clock mode, RESET is an asynchronous input which has no required setup and hold time for proper operation. However, to guarantee the device exits reset synchronized to a particular clock edge, the RESET pin must meet setup and hold times to the falling edge of the CLKIN. (See Figure 28a.)

- (15) In 1x clock mode, RESET is an asynchronous input which has no required setup and hold time for proper operation. However, to guarantee the device exits reset synchronized to a particular clock edge, the RESET pin must be deasserted while CLKIN is high and meet setup and hold times to the rising edge of the CLKIN. (See Figure 28b.)

AC Characteristics — 80960CF-16 (80960CF-16 only, under the conditions described in Section 4.2, Operating Conditions and Section 4.5.1, AC Test Conditions.) (Continued)

| Symbol                             | Parame                                                                     | ter                                                                    | Min           | Max       | Units    | Notes               |

|------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|---------------|-----------|----------|---------------------|

|                                    |                                                                            | INPUT CLOCK                                                            | (10)          |           |          |                     |

| T <sub>F</sub>                     | CLKIN Frequency                                                            |                                                                        | 0             | 32        | MHz      | (1)                 |

| T <sub>C</sub>                     | CLKIN Period                                                               | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | 62.5<br>31.25 | 125<br>∞  | ns<br>ns | (1,12)<br>(1)       |

| T <sub>CS</sub>                    | CLKIN Period Stability                                                     | In 1-x Mode (f <sub>CLK1x</sub> )                                      | 020           | ±0.1%     | Δ        | (1,13)              |

| Тсн                                | CLKIN High Time                                                            | In 1-x Mode (f <sub>CLK1x</sub> )                                      | 10            | 62.5      | ns       | (1,12)              |

| . ОП                               |                                                                            | In 2-x Mode (f <sub>CLK2x</sub> )                                      | 10            | 90        | ns       | (1)                 |

| T <sub>CL</sub>                    | CLKIN Low Time                                                             | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | 10<br>10      | 62.5<br>∞ | ns<br>ns | (1,12)<br>(1)       |

| TCR                                | CLKIN Rise Time                                                            |                                                                        | 0             | 6         | ns       | (1)                 |

| T <sub>CF</sub>                    | CLKIN Fall Time                                                            |                                                                        | 0             | 6         | ns       | (1)                 |

|                                    | <u> </u>                                                                   | OUTPUT CLOC                                                            | KS(9)         |           |          |                     |

| T <sub>CP</sub>                    | CLKIN to PCLK2:1 Delay                                                     | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | -2<br>2       | 2<br>25   | ns<br>ns | (1,3,13,14<br>(1,3) |

| Т                                  | PCLK2:1 Period                                                             | In 1-x Mode (f <sub>CLK1x</sub> )<br>In 2-x Mode (f <sub>CLK2x</sub> ) | T<br>21       |           | ns<br>ns | (1,13)<br>(1,3)     |

| T <sub>PH</sub>                    | PCLK2:1 High Time                                                          |                                                                        | (T/2) - 4     | T/2       | ns       | (1,13)              |

| TPL                                | PCLK2:1 Low Time                                                           |                                                                        | (T/2) - 4     | T/2       | ns       | (1,13)              |

| T <sub>PR</sub>                    | PCLK2:1 Rise Time                                                          |                                                                        | 1             | 4         | ns       | (1,3)               |

| TpF                                | PCLK2:1 Fall Time                                                          |                                                                        | 1             | 4         | ns       | (1,3)               |

|                                    |                                                                            | SYNCHRONOUS OU                                                         | TPUTS(10)     |           |          |                     |

| T <sub>OV</sub><br>T <sub>OH</sub> | Output Valid Delay, Outpu                                                  | it Hold A31:2                                                          | 3             | 18        | ns       | (6, 11)             |

| ·OH                                | Tova Toha                                                                  | BE3:0                                                                  | 3             | 20        | ns       |                     |

|                                    | Тоиз, Тонз                                                                 | ADS                                                                    | 6             | 22        | ns       |                     |

|                                    | T <sub>OV4</sub> , T <sub>OH4</sub><br>T <sub>OV5</sub> , T <sub>OH5</sub> | W/R<br>D/C, SUP, DMA                                                   | 3 4           | 22<br>20  | ns<br>ns |                     |

|                                    | Tov6, ToH6                                                                 | BLAST, WAIT                                                            | 5             | 20        | ns       |                     |

|                                    | T <sub>OV7</sub> , T <sub>OH7</sub>                                        | DEN                                                                    | 3             | 20        | ns       |                     |

|                                    | Tova, Toha                                                                 | HOLDA, BREQ                                                            | 4             | 20        | ns       | Į.                  |

|                                    | Tove, Tohe                                                                 | LOCK                                                                   | 4             | 20        | ns       |                     |

|                                    | TOV10, TOH10                                                               | DACK3:0                                                                | 4             | 22        | ns       |                     |

|                                    | Tov11, ToH11                                                               | D31:0                                                                  | 3             | 20        | ns       |                     |

|                                    | TOV12, TOH12                                                               | DT/R                                                                   | T/2 + 3       | T/2 + 18  | ns       | l                   |

|                                    | TOV13, TOH13                                                               | FAIL                                                                   | 2             | 18        | ns       |                     |

|                                    | T <sub>OV14</sub> , T <sub>OH14</sub>                                      | EOP3:0/TC3:0                                                           | 3             | 22        | ns       | (6, 11)             |

| TOF                                | Output Float for all output                                                | s                                                                      | 3             |           | ns       | (6)                 |

|                                    |                                                                            | SYNCHRONOUS I                                                          | NPUTS(10)     |           |          |                     |

| T <sub>IS</sub>                    | Input Setup                                                                |                                                                        |               |           |          |                     |

|                                    | T <sub>IS1</sub>                                                           | D31:0                                                                  | 5             | 1         | ns       | (1,11)              |

|                                    | T <sub>IS2</sub>                                                           | BOFF                                                                   | 21            | 1         | ns       | (1,11)              |

|                                    | T <sub>IS3</sub>                                                           | BTERM/READY                                                            | 9             | 1         | ns       | (1,11)              |

|                                    | T <sub>IS4</sub>                                                           | HOLD                                                                   | 9             |           | ns       | (1,11)              |

| $T_{IH}$                           | Input Hold                                                                 | D04-0                                                                  | _             |           |          | (4.44)              |

|                                    | T <sub>IH1</sub>                                                           | D31:0                                                                  | 5             | 1         | ns       | (1,11)              |

|                                    | T <sub>IH2</sub>                                                           | BOFF                                                                   | 7             |           | ns       | (1,11)              |

|                                    | Тінз                                                                       | BTERM/READY                                                            | 2             |           | ns       | (1,11)              |

|                                    | T <sub>IH4</sub>                                                           | HOLD                                                                   | 5             |           | ns       | (1,11)              |

#### AC Characteristics - 80960CF-16

(80960CF-16 only, under the conditions described in **Section 4.2, Operating Conditions** and **Section 4.5.1, AC Test Conditions.**) (Continued)

| Symbol             | Parameter                                                   | Min              | Max            | Units | Notes |

|--------------------|-------------------------------------------------------------|------------------|----------------|-------|-------|

|                    | RELATIVE O                                                  | UTPUT TIMINGS(9, | 7)             |       |       |

| T <sub>AVSH1</sub> | A31:2 Valid to ADS Rising                                   | T – 4            | T + 4          | ns    |       |

| T <sub>AVSH2</sub> | BE3:0, W/R, SUP, D/C, DMA, DACK3:0 Valid to ADS Rising      | T - 6            | T + 6          | ns    |       |

| T <sub>AVEL1</sub> | A31:2 Valid to DEN Falling                                  | T - 6            | T + 6          | ns    |       |

| T <sub>AVEL2</sub> | BE3:0, W/R, SUP, INST,<br>DMA, DACK3:0 Valid to DEN Falling | T - 6            | T + 6          | ns    |       |

| TNLQV              | WAIT Falling to Output Data Valid                           | ±                | : 6            | ns    |       |

| T <sub>DVNH</sub>  | Output Data Valid to WAIT Rising                            | N*T - 6          | N*T + 6        | ns    | (4)   |

| TNLNH              | WAIT Falling to WAIT Rising                                 | N*T              | ± 4            | ns    | (4)   |

| T <sub>NHQX</sub>  | Output Data Hold after WAIT Rising                          | (N + 1) *T - 6   | (N + 1) *T + 6 | ns    | (5)   |

| T <sub>EHTV</sub>  | DT/R Hold after DEN High                                    | T/2 - 6          | ∞              | ns    | (6)   |

| T <sub>TVEL</sub>  | DT/R Valid to DEN Falling                                   | T/2 - 4          | T/2 + 4        | ns    | (7)   |

|                    | RELATIVE                                                    | INPUT TIMINGS(7) |                |       |       |

| T <sub>IS5</sub>   | RESET Input Setup (2x Clock Mode)                           | 10               |                | ns    | (14)  |

| T <sub>IH5</sub>   | RESET Input Hold (2x Clock Mode)                            | 9                |                | ns    | (14)  |

| T <sub>IS6</sub>   | DREQ3:0 Input Setup                                         | 16               |                | ns    | (8)   |

| T <sub>IH6</sub>   | DREQ3:0 Input Hold                                          | 11               |                | ns    | (8)   |

| T <sub>IS7</sub>   | XINT7:0, NMI Input Setup                                    | 9                |                | ns    | (8)   |

| T <sub>IH7</sub>   | XINT7:0, NMI Input Hold                                     | 5                |                | ns    | (8)   |

| T <sub>IS8</sub>   | RESET Input Setup (1x Clock Mode)                           | 3                |                | ns    | (15)  |

| TiH8               | RESET Input Hold (1x Clock Mode)                            | T/4 + 1          |                | ns    | (15)  |

#### NOTES

- (1) See Section 4.5.2, AC Timing Waveforms for waveforms and definitions.

- (2) See Figure 22 for capacitive derating information for output delays and hold times.

- (3) See Figure 23 for capacitive derating information for rise and fall times.

- (4) Where N is the number of N<sub>RAD</sub>, N<sub>RDD</sub>, N<sub>WAD</sub>, or N<sub>WDD</sub> wait states that are programmed in the Bus Controller Region Table. When there are no wait states in an access, WAIT never goes active.

- (5) N = Number of wait state inserted with READY.

- (6) Output Data and/or DT/R may be driven indefinitely following a cycle if there is no subsequent bus activity.

- (7) See Notes 1, 2 and 3.

- (8) Since asynchronous inputs are synchronized internally by the 80960CF they have no required setup or hold times in order to be recognized and for proper operation. However, to guarantee recognition of the input at a particular edge of PCLK2:1 the setup times shown must be met. Asynchronous inputs must be active for at least two consecutive PCLK2:1 rising edges to be seen by the processor.

- (9) These specifications are guaranteed by the processor.

- (10) These specifications must be met by the system for proper operation of the processor.

- (11) This timing is dependent upon the loading of PCLK2:1. Use the derating curves of Figure 22 to adjust the timing for PCLK2:1 loading.

- (12) In the 1-x input clock mode, the maximum input clock period is limited to 125 ns while the processor is operating. When the processor is in reset, the input clock may stop even in 1-x mode.

- (13) When in the 1-x input clock mode, these specifications assume a stable input clock with a period variation of less than ±0.1% between adjacent cycles.

- (14) In 2x clock mode, RESET is an asynchronous input which has no required setup and hold time for proper operation. However, to guarantee the device exits reset synchronized to a particular clock edge, the RESET pin must meet setup and hold times to the falling edge of the CLKIN. (See Figure 28a.)

- (15) In 1x clock mode, RESET is an asynchronous input which has no required setup and hold time for proper operation. However, to guarantee the device exits reset synchronized to a particular clock edge, the RESET pin must be deasserted while CLKIN is high and meet setup and hold times to the rising edge of the CLKIN. (See Figure 28b.)

### 4.5.1. AC TEST CONDITIONS

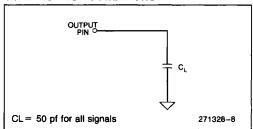

Figure 9. AC Test Load

The AC Specifications in Section 4.5 are tested with the 50 pf load shown in Figure 9. See Figure 16 to see how timings vary with load capacitance.

Specifications are measured at the 1.5V crossing point, unless otherwise indicated. Input waveforms are assumed to have a rise-and-fall time of  $\leq$  2 ns from 0.8V to 2.0V. See **Section 4.5.2, AC Timing Waveforms** for AC spec definitions, test points and illustrations.

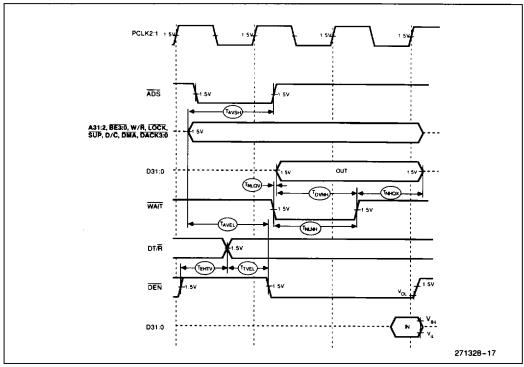

## 4.5.2. AC TIMING WAVEFORMS

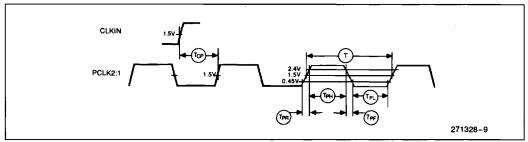

Figure 10a. Input and Output Clocks Waveform

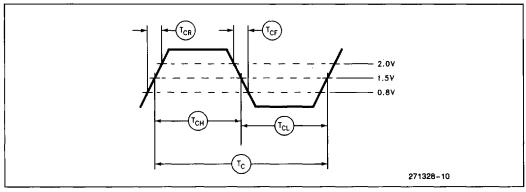

Figure 10b. CLKIN Waveform

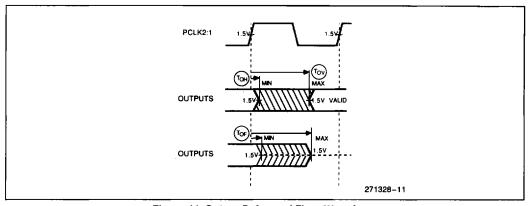

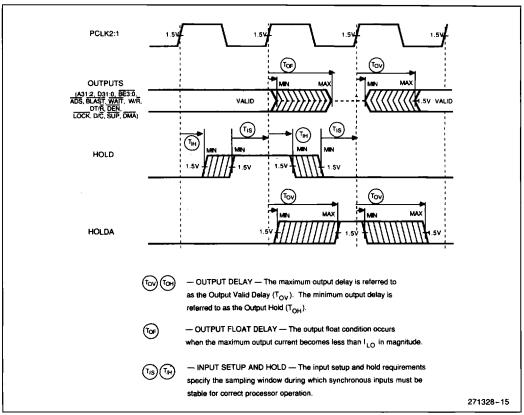

Figure 11. Output Delay and Float Waveform

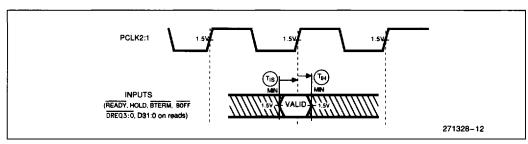

Figure 12a. Input Setup and Hold Waveform

- (To) (To) OUTPUT DELAY The maximum output delay is referred to as the Output Valid Delay (T<sub>OV</sub>). The minimum output delay is referred to as the Output Hold (T<sub>OH</sub>).

- Toe OUTPUT FLOAT DELAY The output float condition occurs when the maximum output current becomes less than I<sub>LO</sub> in magnitude.

- INPUT SETUP AND HOLD The input setup and hold requirements specify the sampling window during which synchronous inputs must be stable for correct processor operation.

271328-13

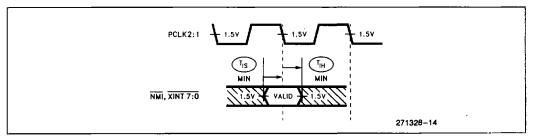

Figure 12b. NMI, XINT7:0 Input Setup and Hold Waveform

Figure 13. Hold Acknowledge Timings

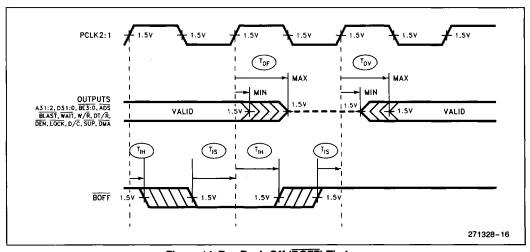

Figure 14. Bus Back-Off (BOFF) Timings

Figure 15. Relative Timings Waveforms

# **4.5.3 DERATING CURVES**

Figure 16. Output Delay or Hold vs Load Capacitance

Figure 17. Rise and Fall Time Derating at Highest Operating Temperature and Minimum  $V_{CC}$

Figure 18. I<sub>CC</sub> vs Frequency and Temperature