# Dual Bootstrapped MOSFET Driver

### **ADP3416**

### **FEATURES**

All-In-One Synchronous Buck Driver Bootstrapped High Side Drive One PWM Signal Generates Both Drives Anticross-Conduction Protection Circuitry Pulse-by-Pulse Disable Control

#### **APPLICATIONS**

Mobile Computing CPU Core Power Converters Multiphase Desktop CPU Supplies Single-Supply Synchronous Buck Converters Standard-to-Synchronous Converter Adaptations

### **GENERAL DESCRIPTION**

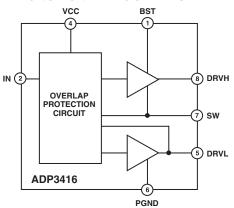

The ADP3416 is a dual MOSFET driver optimized for driving two N-channel MOSFETs which are the two switches in a nonisolated synchronous buck power converter. One of the drivers can be bootstrapped and is designed to handle the

### FUNCTIONAL BLOCK DIAGRAM

high voltage slew rate associated with "floating" high side gate drivers. The ADP3416 includes overlapping drive protection (ODP) to prevent shoot-through current in the external MOSFETs.

The ADP3416 is specified over the commercial temperature range of 0°C to 70°C and is available in an 8-lead SOIC package.

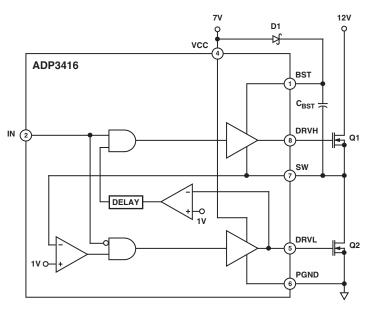

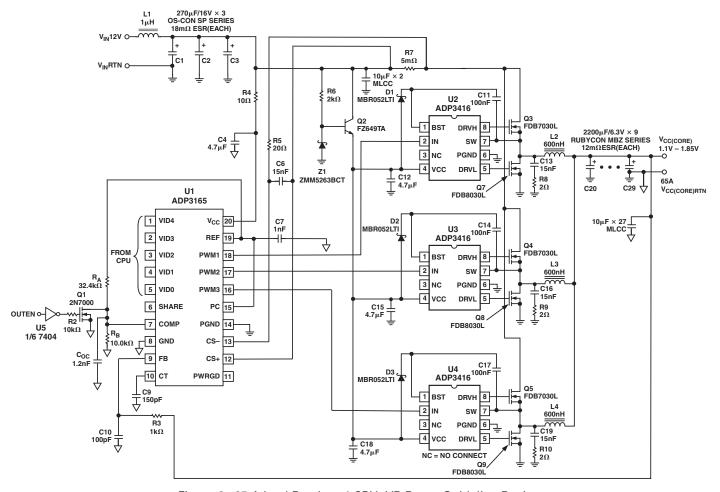

Figure 1. General Application Circuit

### REV. A

## $\textbf{ADP3416-SPECIFICATIONS}^{1}(T_A = 0^{\circ}\text{C to } 70^{\circ}\text{C}, \, \text{VCC} = 7 \, \text{V, BST} = 4 \, \text{V to } 26 \, \text{V, unless otherwise noted.})$

| Parameter                                                                                      | Symbol                                                                              | Conditions                                                                                                                                                                                     | Min  | Тур                      | Max                      | Unit                                |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|--------------------------|-------------------------------------|

| SUPPLY Supply Voltage Range Quiescent Current                                                  | VCC<br>ICC <sub>Q</sub>                                                             |                                                                                                                                                                                                | 4.15 | 2                        | 7.5<br>5                 | V<br>mA                             |

| PWM INPUT Input Voltage High <sup>2</sup> Input Voltage Low <sup>2</sup>                       |                                                                                     |                                                                                                                                                                                                | 2.3  |                          | 0.8                      | V<br>V                              |

| HIGH SIDE DRIVER Output Resistance, Sourcing Current Output Resistance, Sinking Current        |                                                                                     | $V_{BST} - V_{SW} = 5 V$ $V_{BST} - V_{SW} = 7 V$ $V_{BST} - V_{SW} = 5 V$ $V_{BST} - V_{SW} = 7 V$                                                                                            |      | 3.0<br>2.0<br>2.0<br>1.0 | 5.0<br>4.0<br>4.0<br>2.5 | $\Omega$ $\Omega$ $\Omega$ $\Omega$ |

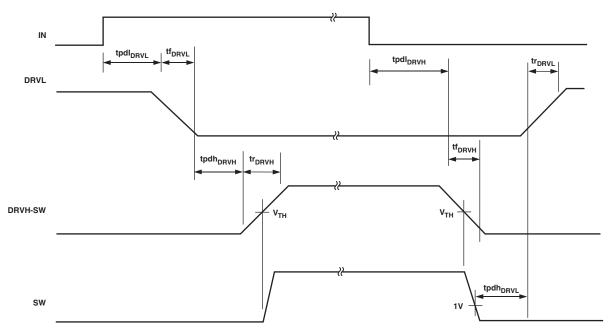

| Transition Times <sup>3</sup> (See Figure 2)  Propagation Delay <sup>3, 4</sup> (See Figure 2) | ${ m tr}_{ m DRVH} \ { m tf}_{ m DRVH} \ { m tpdh}_{ m DRVH} \ { m tpdl}_{ m DRVH}$ | $V_{BST} - V_{SW} = 7 \text{ V}, C_{LOAD} = 3 \text{ nF}$<br>$V_{BST} - V_{SW} = 7 \text{ V}, C_{LOAD} = 3 \text{ nF}$<br>$V_{BST} - V_{SW} = 7 \text{ V}$<br>$V_{BST} - V_{SW} = 7 \text{ V}$ |      | 25<br>20<br>65<br>25     | 40<br>30<br>90<br>35     | ns<br>ns<br>ns<br>ns                |

| LOW SIDE DRIVER Output Resistance, Sourcing Current Output Resistance, Sinking Current         |                                                                                     | VCC = 5 V<br>VCC = 7 V<br>VCC = 5 V<br>VCC = 7 V                                                                                                                                               |      | 3.0<br>2.0<br>2.0<br>1.0 | 5.0<br>4.0<br>4.0<br>2.5 | $\Omega$ $\Omega$ $\Omega$          |

| Transition Times <sup>3</sup> (See Figure 2)  Propagation Delay <sup>3, 4</sup> (See Figure 2) | ${ m tr_{DRVL}} \ { m tf_{DRVL}} \ { m tpdh_{DRVL}} \ { m tpdl_{DRVL}}$             | $VCC = 7 \text{ V}, C_{LOAD} = 3 \text{ nF}$ $VCC = 7 \text{ V}, C_{LOAD} = 3 \text{ nF}$ $VCC = 7 \text{ V}$ $VCC = 7 \text{ V}$                                                              |      | 25<br>20<br>30<br>15     | 40<br>30<br>40<br>25     | ns<br>ns<br>ns                      |

#### NOTES

Specifications subject to change without notice.

-2- REV. A

<sup>&</sup>lt;sup>1</sup>All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

$<sup>^2</sup> Logic$  inputs meet typical CMOS I/O conditions for source/sink current (~1  $\mu A).$

<sup>&</sup>lt;sup>3</sup>AC specifications are guaranteed by characterization but not production tested.

<sup>&</sup>lt;sup>4</sup>For propagation delays, "tpdh" refers to the specified signal going high; "tpdl" refers to it going low.

### **ABSOLUTE MAXIMUM RATINGS\***

| VCC0.3 V to +8 V                                  |

|---------------------------------------------------|

| BST0.3 V to +30 V                                 |

| BST to SW0.3 V to +8 V                            |

| SW5.0 V to +25 V                                  |

| IN0.3 V to VCC + 0.3 V                            |

| Operating Ambient Temperature Range 0°C to 70°C   |

| Operating Junction Temperature Range 0°C to 125°C |

| $\theta_{JA}$                                     |

| $\theta_{\rm JC}$                                 |

| Storage Temperature Range65°C to +150°C           |

| Lead Temperature (Soldering, 10 sec) 300°C        |

<sup>\*</sup>This is a stress rating only; operation beyond these limits can cause the device to be permanently damaged. Unless otherwise specified, all voltages are referenced to PGND.

### **ORDERING GUIDE**

| Model     | Temperature | Package                                 | Package |

|-----------|-------------|-----------------------------------------|---------|

|           | Range       | Description                             | Option  |

| ADP3416JR | 0°C to 70°C | 8-Lead Standard<br>Small Outline (SOIC) | SOIC-8  |

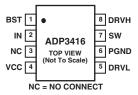

### **PIN CONFIGURATION**

### PIN FUNCTION DESCRIPTIONS

| Pin | Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BST      | Floating Bootstrap Supply for the Upper MOSFET. A capacitor connected between BST and SW Pins holds this bootstrapped voltage for the high side MOSFET as it is switched. The capacitor should be chosen between $100 \text{ nF}$ and $1 \mu\text{F}$ .                                                                                                                      |

| 2   | IN       | TTL-level input signal that has primary control of the drive outputs.                                                                                                                                                                                                                                                                                                        |

| 3   | NC       | No Connection.                                                                                                                                                                                                                                                                                                                                                               |

| 4   | VCC      | Input Supply. This pin should be bypassed to PGND with ~1 μF ceramic capacitor.                                                                                                                                                                                                                                                                                              |

| 5   | DRVL     | Synchronous Rectifier Drive. Output drive for the lower (synchronous rectifier) MOSFET.                                                                                                                                                                                                                                                                                      |

| 6   | PGND     | Power Ground. Should be closely connected to the source of the lower MOSFET.                                                                                                                                                                                                                                                                                                 |

| 7   | SW       | This pin is connected to the buck-switching node, close to the upper MOSFET's source. It is the floating return for the upper MOSFET drive signal. It is also used to monitor the switched voltage to prevent turn-on of the lower MOSFET until the voltage is below ~1 V. Thus, according to operating conditions, the high low transition delay is determined at this pin. |

| 8   | DRVH     | Buck Drive. Output drive for the upper (buck) MOSFET.                                                                                                                                                                                                                                                                                                                        |

### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADP3416 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. A -3-

### **ADP3416**

Figure 2. Nonoverlap Timing Diagram (Timing Is Referenced to the 90% and 10% Points Unless Otherwise Noted)

-4- REV. A

### **Typical Performance Characteristics—ADP3416**

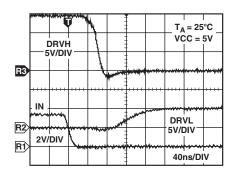

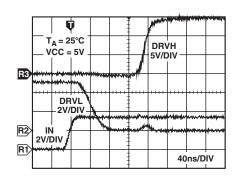

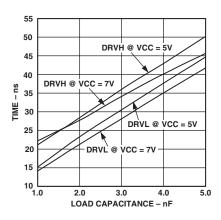

TPC 1. DRVH Fall and DRVL Rise Times

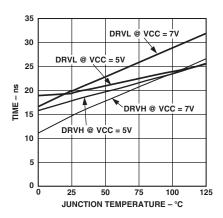

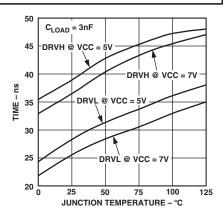

TPC 4. DRVH and DRVL Fall Times vs. Temperature

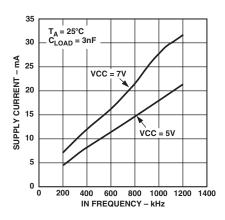

TPC 7. Supply Current vs. Frequency

TPC 2. DRVL Fall and DRVH Rise Times

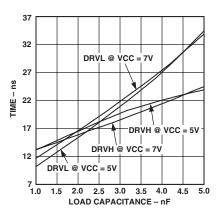

TPC 5. DRVH and DRVL Rise Times vs. Load Capacitance

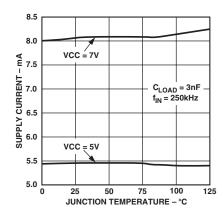

TPC 8. Supply Current vs. Temperature

TPC 3. DRVH and DRVL Rise Times vs. Temperature

TPC 6. DRVH and DRVL Fall Times vs. Load Capacitance

REV. A -5-

### **ADP3416**

#### THEORY OF OPERATION

The ADP3416 is a dual MOSFET driver optimized for driving two N-channel MOSFETs in a synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high side and the low side FETs. Each driver is capable of driving a 3 nF load.

A more detailed description of the ADP3416 and its features follows. Refer to the Functional Block Diagram.

### Low Side Driver

The low side driver is designed to drive low  $R_{DS(ON)}$  N-channel MOSFETs. The maximum output resistance for the driver is 4  $\Omega$  for sourcing and 2.5  $\Omega$  for sinking gate current. The low output resistance allows the driver to have 40 ns rise and 30 ns fall times into a 3 nF load. The bias to the low side driver is internally connected to the VCC supply and PGND.

When the driver is enabled, the driver's output is 180 degrees out of phase with the PWM input. When the ADP3416 is disabled, the low side gate is held low.

#### **High Side Driver**

The high side driver is designed to drive a floating low  $R_{DS(ON)}$  N-channel MOSFET. The maximum output resistance for the driver is 4  $\Omega$  for sourcing and 2.5  $\Omega$  for sinking gate current. The low output resistance allows the driver to have 40 ns rise and 30 ns fall times into a 3 nF load. The bias voltage for the high side driver is developed by an external bootstrap supply circuit, which is connected between the BST and SW Pins.

The bootstrap circuit comprises a diode, D1, and bootstrap capacitor,  $C_{BST}$ . When the ADP3416 is starting up, the SW Pin is at ground, so the bootstrap capacitor will charge up to VCC through D1. When the PWM input goes high, the high side driver will begin to turn the high side MOSFET, Q1, ON by pulling charge out of  $C_{BST}$ . As Q1 turns ON, the SW Pin will rise up to  $V_{IN}$ , forcing the BST Pin to  $V_{IN} + V_{C(BST)}$ , which is enough gate to source voltage to hold Q1 ON. To complete the cycle, Q1 is switched OFF by pulling the gate down to the voltage at the SW Pin. When the low side MOSFET, Q2, turns ON, the SW Pin is pulled to ground. This allows the bootstrap capacitor to charge up to VCC again.

The high side driver's output is in phase with the PWM input. When the driver is disabled, the high side gate is held low.

### **Overlap Protection Circuit**

The overlap protection circuit (OPC) prevents both of the main power switches, Q1 and Q2, from being ON at the same time. This is done to prevent shoot-through currents from flowing through both power switches and the associated losses that can occur during their ON-OFF transitions. The overlap protection circuit accomplishes this by adaptively controlling the delay from Q1's turn OFF to Q2's turn ON, and by internally setting the delay from Q2's turn OFF to Q1's turn ON.

To prevent the overlap of the gate drives during Q1's turn OFF and Q2's turn ON, the overlap circuit monitors the voltage at the SW Pin. When the PWM input signal goes low, Q1 will begin to turn OFF (after a propagation delay), but before Q2 can turn ON, the overlap protection circuit waits for the voltage at the SW Pin to fall from  $V_{\rm IN}$  to 1 V. Once the voltage on the SW Pin has fallen to 1 V, Q2 will begin turn ON. By waiting for the voltage on the

SW Pin to reach 1 V, the overlap protection circuit ensures that Q1 is OFF before Q2 turns on, regardless of variations in temperature, supply voltage, gate charge, and drive current.

To prevent the overlap of the gate drives during Q2's turn OFF and Q1's turn ON, the overlap circuit provides a internal delay that is set to 50 ns. When the PWM input signal goes high, Q2 will begin to turn OFF (after a propagation delay), but before Q1 can turn ON, the overlap protection circuit waits for the voltage at DRVL to drop to around 10% of VCC. Once the voltage at DRVL has reached the 10% point, the overlap protection circuit will wait for a 20 ns typical propagation delay. Once the delay period has expired, Q1 will begin turn ON.

### APPLICATION INFORMATION

### **Supply Capacitor Selection**

For the supply input (VCC) of the ADP3416, a local bypass capacitor is recommended to reduce the noise and to supply some of the peak currents drawn. Use a 1  $\mu F$ , low ESR capacitor. Multilayer ceramic chip (MLCC) capacitors provide the best combination of low ESR and small size and can be obtained from the following vendors:

Murata GRM235Y5V106Z16 www.murata.com

Taivo-

Yuden EMK325F106ZF www.t-yuden.com

Tokin C23Y5V1C106ZP www.tokin.com

Keep the ceramic capacitor as close as possible to the ADP3416.

### **Bootstrap Circuit**

The bootstrap circuit uses a charge storage capacitor ( $C_{BST}$ ) and a Schottky diode, as shown in Figure 1. Selection of these components can be done after the high side MOSFET has been chosen.

The bootstrap capacitor must have a voltage rating that is able to handle the maximum battery voltage plus 5 volts. A minimum 50 V rating is recommended. The capacitance is determined using the following equation:

$$C_{BST} = \frac{Q_{GATE}}{\Delta V_{RST}}$$

where,  $Q_{GATE}$  is the total gate charge of the high side MOSFET, and  $\Delta V_{BST}$  is the voltage droop allowed on the high side MOSFET drive. For example, the IRF7811 has a total gate charge of about 20 nC. For an allowed droop of 200 mV, the required bootstrap capacitance is 100 nF. A good quality ceramic capacitor should be used.

A Schottky diode is recommended for the bootstrap diode due to its low forward drop, which maximizes the drive available for the high side MOSFET. The bootstrap diode must have a minimum 40 V rating to withstand the maximum battery voltage plus 5 V. The average forward current can be estimated by:

$$I_{F(AVG)} \approx Q_{GATE} \times f_{MAX}$$

where  $f_{MAX}$  is the maximum switching frequency of the controller. The peak surge current rating should be checked in-circuit, since this is dependent on the source impedance of the 5 V supply, and the ESR of  $C_{\rm BST}$ .

-6- REV. A

**ADP3416**

### **Printed Circuit Board Layout Considerations**

Use the following general guidelines when designing printed circuit boards:

- 1. Trace out the high current paths and use short, wide traces to make these connections.

- 2. Connect the PGND Pin of the ADP3416 as close as possible to the source of the lower MOSFET.

- 3. The VCC bypass capacitor should be located as close as possible to VCC and PGND Pins.

### **Typical Application Circuits**

The circuit in Figure 3 shows how two drivers can be combined with the ADP3165 to form a total power conversion solution for  $V_{\text{CC(CORE)}}$  generation in a high current Intel CPU computer.

Figure 3. 65 A Intel Pentium 4 CPU, VR Down Guideline Design

REV. A -7-

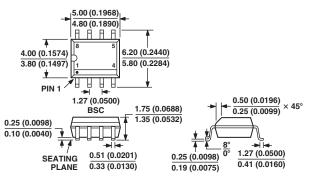

### **OUTLINE DIMENSIONS**

### 8-Lead Standard Small Outline Package [SOIC] Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

COMPLIANT TO JEDEC STANDARDS MS-012AA

### **Revision History**

| Location                                        | Page |

|-------------------------------------------------|------|

| 08/02—Data Sheet changed from REV. 0 to REV. A. |      |

| Undated OUTLINE DIMENSIONS                      | 8    |