# MTTL Complex Functions MOTOROLA

## **COMPLEX FUNCTIONS**

# MC4300/MC4000 Series

The MTTL complex functions are designed for digital applications in the medium to high-speed range.

These MTTL devices provide significant reduction in package count and increased logic per function over devices in the basic MTTL and MDTL families.

## FUNCTIONS AND CHARACTERISTICS (V<sub>CC</sub> = 5.0 V, $T_A$ = 25°C)

All devices shown can be used with all MTTL and MDTL devices; however, the loading factors shown reflect use with other devices in the same MC-number series unless otherwise noted.

|                                                 | Operating Temp         | perature Range       | Output<br>Loading       | Propagation<br>Delay                  | Power<br>Dissipation |

|-------------------------------------------------|------------------------|----------------------|-------------------------|---------------------------------------|----------------------|

| Function                                        | Type 1<br>55 to +125°C | Type 1<br>0 to +75°C | Factor<br>Each Output   | tpd<br>ns typ                         | PD<br>mW typ/pkg     |

| Dual 4-Channel Data Selector                    | MC4300F,L              | MC4000F,L,P          | 10                      | Control Line = 18<br>Data Line = 11   | 150                  |

| BCD-to-Binary/Binary-to-BCD<br>Number Converter |                        | MC4001F,L,P          | Open Collector          | Address Time<br><45 ns                | 300                  |

| Dual Data Distributor                           | MC4302F,L              | MC4002F,L,P          | 10                      | 10.5                                  | 175                  |

| 16 Bit Scratch Pad Memory Cell                  | MC4304F,L              | MC4004F,L,P          | 1 <sub>OL</sub> = 40 mA | Write mode 25<br>Sense mode 15        | 250                  |

| 16 Bit scratch Pad Memory Cell                  | MC4305F'L              | MC4005F,L,P          | Open Collector          | Write mode 25<br>Sense mode 15        | 250                  |

| Binary to One-of-Eight Line Decoder             | MC4306F,L              | MC4006F,L,P          | 10                      | 14                                    | 100                  |

| Dual Binary to One-of-Four Line Decoder         | MC4307F,L              | MC4007F,L,P          | 10                      | 14                                    | 125                  |

| 8-Bit Parity Tree                               | MC4308F,L              | MC4008F,L,P          | 10                      | 15 to 30                              | 150                  |

| Dual 4 Bit Parity Tree                          | MC4310F,L              | MC4010F,L,P          | 10                      | 9.5 to 22                             | 125                  |

| 4-Bit Shift Register                            | MC4312F,L              | MC4012F,L,P          | 10                      | 22/bit                                | 180                  |

| Quad Type D Flip Flop                           | MC4315F,L              | MC4015F,L,P          | 10                      | 16                                    | 190                  |

| Programmable Module-N<br>Decade Counter         | MC4316F,L              | MC4016F,L,P          | 8                       | Clock to Q3 = 50<br>Clock to Bus = 35 | 250                  |

| Programmable Modulo 2, Modulo 5 Counters        | MC4317F,L              | MC4017F,L,P          | 8                       | Clock to Q3 = 50<br>Clock to Bus = 35 | 250                  |

| Programmable Module-N<br>Hexadecimal Counter    | MC4318F,L              | MC4018F,L,P          | 8                       | Clock to Q3 = 50<br>Clock to Bus = 35 | 250                  |

| Dual Programmable Modulo 4 Counters             | MC4319F,L              | MC4019F,L,P          | 8                       | Clock to Q3 = 50<br>Clock to Bus = 35 | 250                  |

## MC4300/4000 Series continued

|                                                        |               |             | Output<br>Loading                                                | Propagation<br>Delay         | Power<br>Dissipation |

|--------------------------------------------------------|---------------|-------------|------------------------------------------------------------------|------------------------------|----------------------|

| Function                                               | -55 to +125°C | 0 to +75°C  | Factor<br>Each Output                                            | <sup>t</sup> pd<br>ns typ    | PD<br>mW typ/pkg     |

| Dual 4-Bit Comparator (Open Collector)                 | MC4321F,L     | MC4021F,L,P | 10                                                               | 20                           | 250                  |

| Dual 4-Bit Comparator                                  | MC4322F,L     | MC4022F,L,P | 10                                                               | 20                           | 250                  |

| 4-Bit Universal Counter                                | MC4323F,L     | MC4023F,L,P | 10                                                               | 16/bit                       | 200                  |

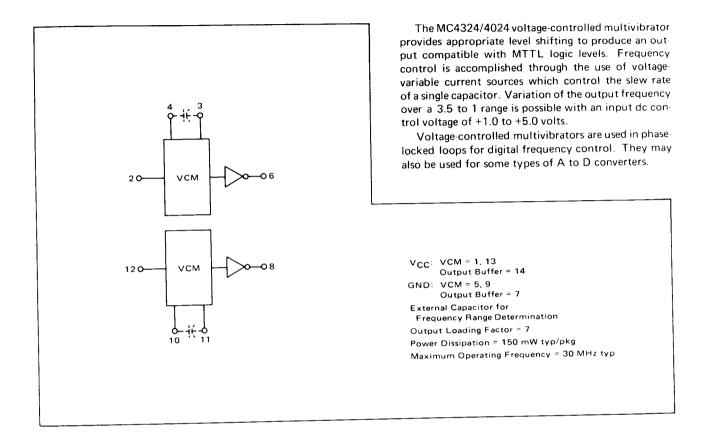

| Dual Voltage Controlled Multivibrator                  | MC4324F,L     | MC4024F,L,P | 7                                                                | f <sub>max</sub> = 30 MHz    | 150                  |

| Full Adder                                             | MC4326F,L     | MC4026F,L,P | 15/12**                                                          | 25/13#                       | 90                   |

| Full Adder                                             | MC4327F,L     | MC4027F,L,P | 7/6**                                                            | 25/13#                       | 90                   |

| Adder (Dependent Carry)                                | MC4328F,L     | MC4028F,L,P | 15/12**                                                          | 25/13#                       | 125                  |

| Adder (Dependent Carry)                                | MC4329F,L     | MC4029F,L,P | 7/6**                                                            | 25/13#                       | 125                  |

| Adder (Independent Carry)                              | MC4330F,L     | MC4030F,L,P | 15/12**                                                          | 25/13#                       | 125                  |

| Adder (Independent Carry)                              | MC4331F,L     | MC4031F,L,P | 7/6**                                                            | 25/13#                       | 125                  |

| Carry Decoder                                          | MC4332F,L     | MC4032F,L,P |                                                                  | △t <sub>pd</sub> = 4 decoder | 20                   |

| Quad Latch (Open Collector)                            | MC4335F,L     | MC4035F,L,P | 7                                                                | 25                           | 140                  |

| Quad Latch                                             | MC4337F,L     | MC4037F,L,P | 10                                                               | 25                           | 150                  |

| Inverting/Non-Inverting One-of-Eight Decoder           | _             | MC4038F,L,P |                                                                  | 1                            | 240                  |

| Seven Segment Character Generator                      | _             | MC4039F,L,P | Open Collector                                                   | Address                      | 240                  |

| Binary to Two-of-Eight Decoder                         |               | MC4040F,L,P | <br>  I <sub>OL</sub> = 20 mA                                    | Time                         | 200                  |

| Single-Error Hamming Code Detector and Generator       | _             | MC4041F,L,P | )                                                                | <45 ns                       | 240                  |

| Quad Predriver                                         | MC4342F,L     | MC4042F,L,P | I <sub>OL</sub> = 50 mA<br>Open Collector                        | 15                           | 120                  |

| Dual Line Selector                                     | MC4343F,L     | MC4043F,L,P | I <sub>OL</sub> = 400 mA<br>Pulsed                               | 20                           | 70                   |

| Phase-Frequency Detector                               | MC4344F,L     | MC4044F,L,P | 10                                                               | 9.0                          | 85                   |

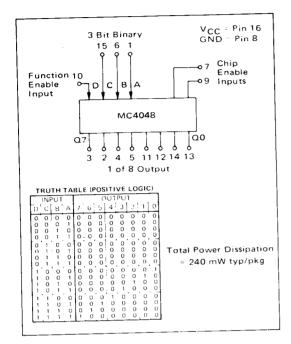

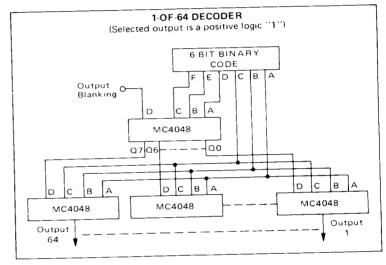

| Non-Inverting One-of-Eight Decoder                     | -             | MC4048F,L,P | Open Collector<br>IOL = 16 mA                                    | Address Time<br><50 ns)      | 240                  |

| Counter-Latch-Decoder                                  | MC4350F,L     | MC4050F.L.P | Open Collector<br>IOL = 40 mA                                    | f <sub>Tog</sub> = 35 MHz    | 450                  |

| Counter-Latch-Decoder                                  | MC4351F,L     | MC4051F,L,P | Open Emitter<br>40 mA Sourcing<br>Capability @<br>10% Duty Cycle | f <sub>Tog</sub> = 35 MHz    | 450                  |

| Dual Decade Counter                                    | MC4352F,L     | MC4052F,L,P | 10                                                               | f <sub>Tog</sub> = 40 MHz    | 350                  |

| Dual Hexadecimal Counter                               | MC4353F,L     | MC4053F,L,P | 10                                                               | f <sub>Tog</sub> = 40 MHz    | 350                  |

| Dual Decade Up/Down Counter                            | MC4354F,L     | MC4054F,L,P | 10                                                               | f <sub>Tog</sub> = 12 MHz    | 600                  |

| Dual Binary Up/Down Counter                            | MC4355F,L     | MC4055F,L,P | 10                                                               | f <sub>Tog</sub> = 12 MHz    | 600                  |

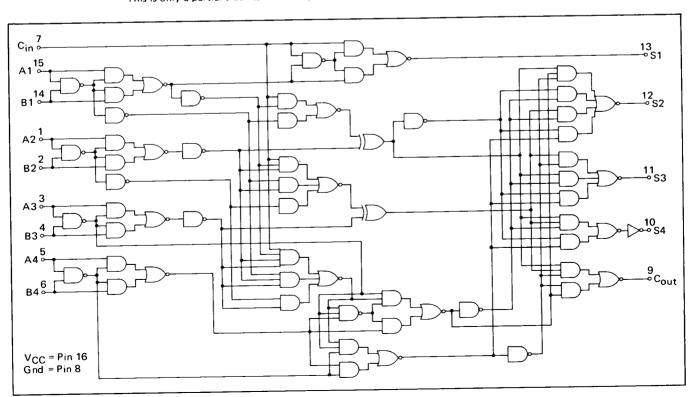

| NBCD Adder                                             | MC4356F,L     | MC4056F,L,P | 10                                                               | 30                           | 300                  |

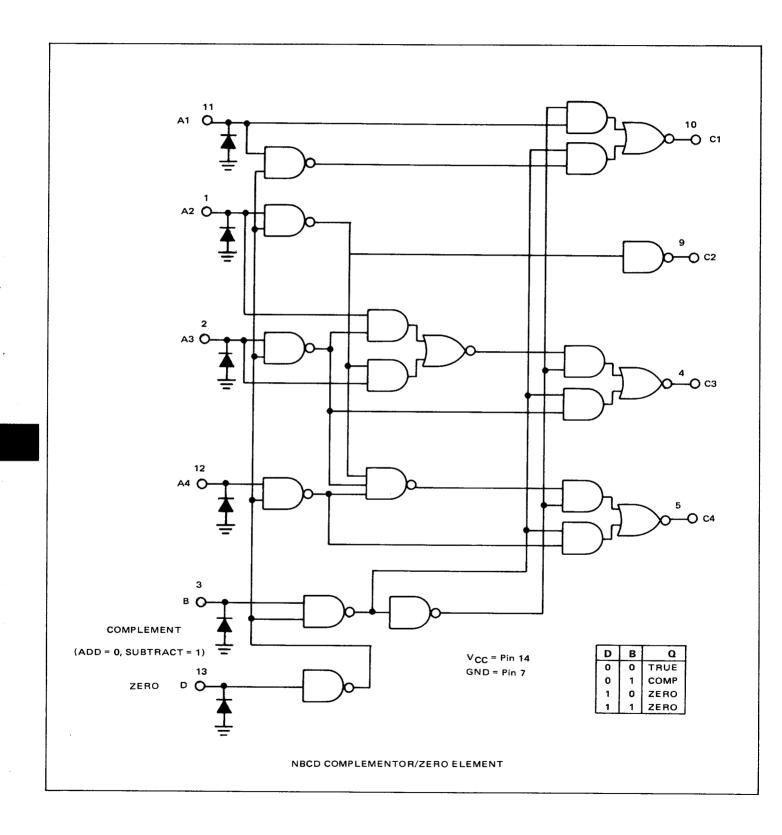

| Nines Complement/Zero Element                          | MC4358F,L     | MC4058F,L,P | 10                                                               | 30                           | 200                  |

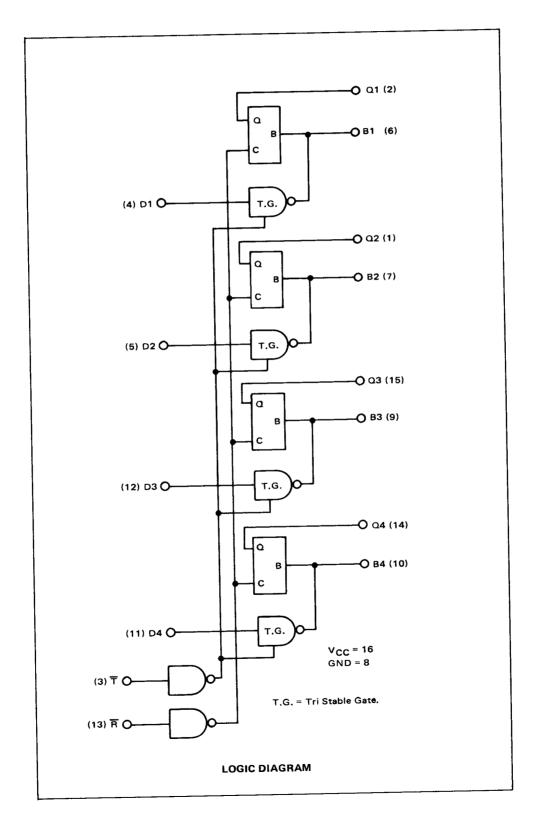

| Bus Transfer Switch                                    | MC4360F,L     | MC4060F,L,P | 10                                                               | 25                           | 350                  |

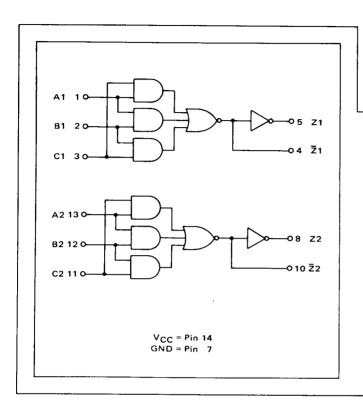

| Dual Majority Logic Gate                               | MC4362F,L     | MC4062F,L,P | 10                                                               | Z = 20<br>Z = 11             | 75                   |

| 64-Bit Random Access Memory                            | -             | MC4064F,L,P | Open Collector                                                   | Access Time<br><60 ns        | 384                  |

| Dual MOS-to-TTL Level Translator with Tri-state Output | MC4368F,L     | MC4068F,L,P | 10                                                               | 20                           | 150                  |

<sup>\*\*</sup>MC4300/MC400 Series loading specified for use with MTTLI Devices #Add delay, Carry delay

## MC4300 MC4000

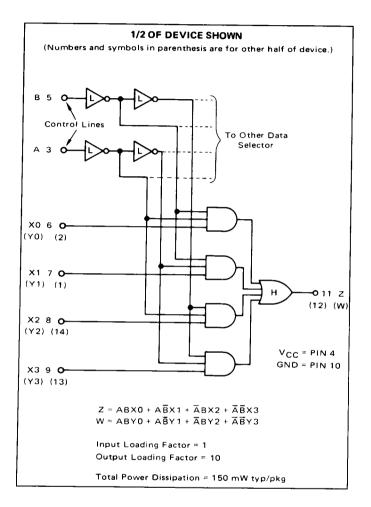

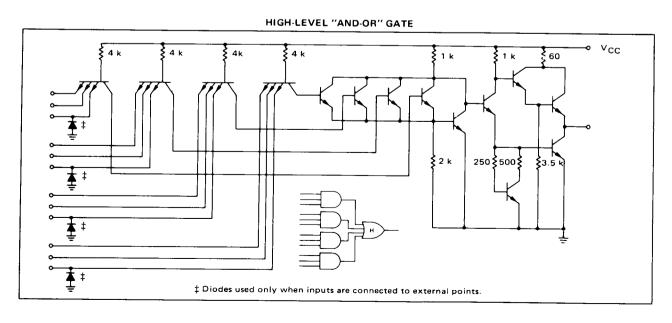

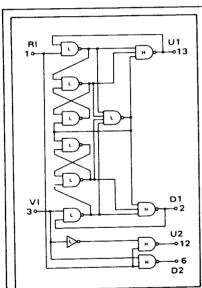

This device consists of two four-channel data selectors with common control lines, constructed from high-level AND-OR gates and low-level inverters. By selecting one of four logic combinations, information on one of the four data inputs will be routed to the output.

Data selectors are useful in applications where digital data is to be routed from one of several registers or locations to another register or location for processing.

| TYPICA | L PROP | AGATION DELAY TIMES (ns)<br>T <sub>A</sub> = 25°C |

|--------|--------|---------------------------------------------------|

| INPUT  | Z      | CONDITIONS                                        |

| Α      | 18     | X0 = X2 = X3 = logic "0", X1 =                    |

| В      | 15     | logic "1". A and B are de-                        |

| X1     | 11     | fined by the logic equations.                     |

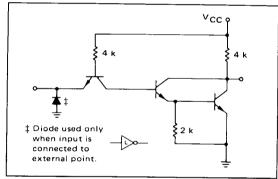

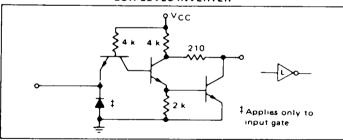

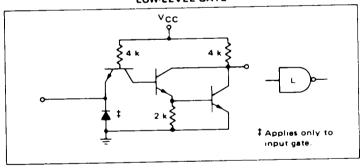

## LOW-LEVEL INVERTER

## MC4301 MC4001

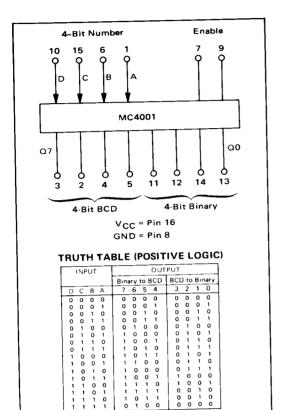

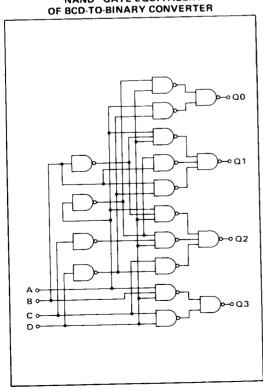

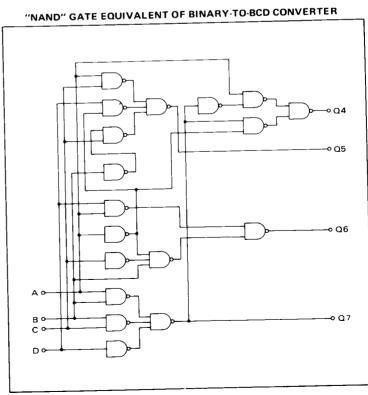

The MC4301/4001 serves as a basic building block in Binary-to-BCD and BCD- to-Binary converters. Conversion of any length binary or BCD word can be accomplished by interconnecting MC4001 packages. The MC4001 also contains a full adder and subtractor.

#### Features:

Address times < 45 ns Outputs sink 16 mA Output capacitance < 7.0 pF @ 1.5 V

## **ENABLE INPUT TRUTH TABLE (POSITIVE LOGIC)**

| E  | E              | Ω7 | Q6 | Q5   | Q4   | Q3    | Q2  | Q1 | 0.0 |

|----|----------------|----|----|------|------|-------|-----|----|-----|

| 1  | _ <del></del>  | 1  | 1  | 1    | 1    | 1     | 1   | 1  | 1   |

| 10 | <del>- 1</del> | 1  | 1  | 1    | 1    | 1     | 1   | 1  | 1   |

| 1  | 0              | 1  | 1  | 1    | 1    | 1     | 1   | 1  | 1   |

| 1  | 1              |    |    | FUNC | TION | ENABI | LED |    |     |

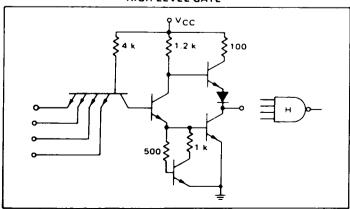

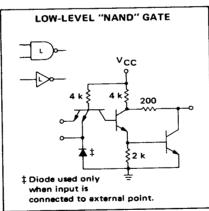

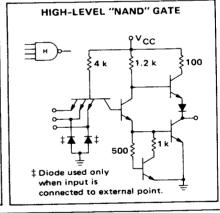

## "NAND" GATE EQUIVALENT

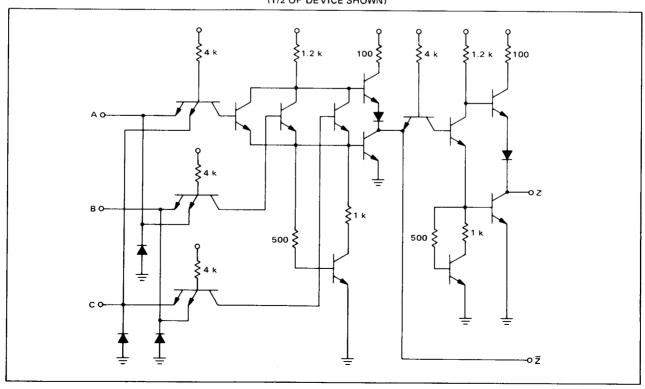

# DUAL DATA DISTRIBUTOR MC4302 MC4002

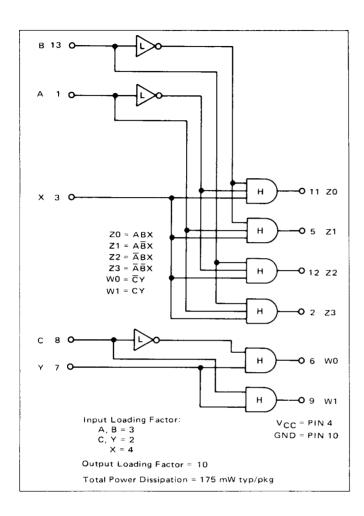

This device consists of two data distributors constructed from high-level AND gates and low-level inverters. One distributes information present at the input line to one of four output lines; the other distributes information present at the input to one of two output lines. The routing path is selected by the logic signals at the control lines A, B or C.

Data distributors are useful in applications where digital data is to be routed from a single register or location to one of several registers or locations for processing.

|       |      | 1 - 25 C   | TYPICAL PROPAGATION DELAY TIMES (ns) $T_A = 25^{\circ}C$ |      |  |  |  |  |  |  |

|-------|------|------------|----------------------------------------------------------|------|--|--|--|--|--|--|

| INPUT | ZO   | Z1         | Z2                                                       | Z3   |  |  |  |  |  |  |

| Α     | 14.5 | 10.5       | 14.5                                                     | 10.5 |  |  |  |  |  |  |

| В     | 14.5 | 14.5       | 10.5                                                     | 10.5 |  |  |  |  |  |  |

|       |      |            |                                                          |      |  |  |  |  |  |  |

| ×     | 10.5 | 10.5       | 10.5                                                     | 10.5 |  |  |  |  |  |  |

| ×     | 10.5 | 10.5<br>W0 | W1                                                       | 10.5 |  |  |  |  |  |  |

| ×     |      | T          |                                                          | 10.5 |  |  |  |  |  |  |

#### LOW-LEVEL INVERTER

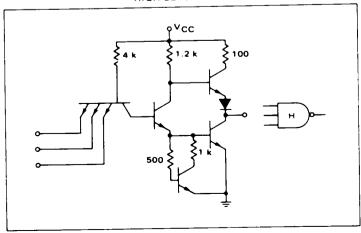

#### HIGH-LEVEL "AND" GATE

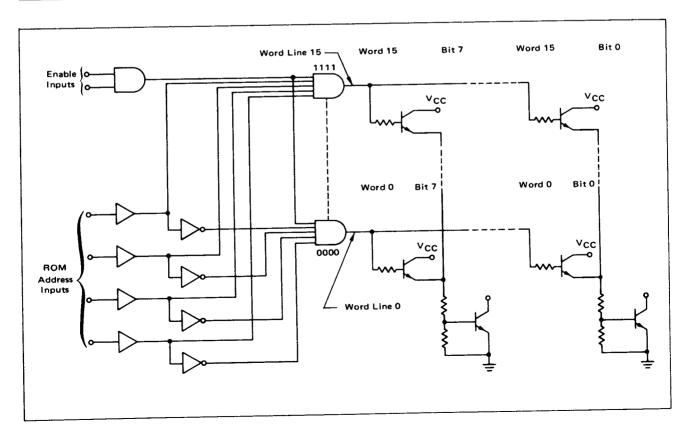

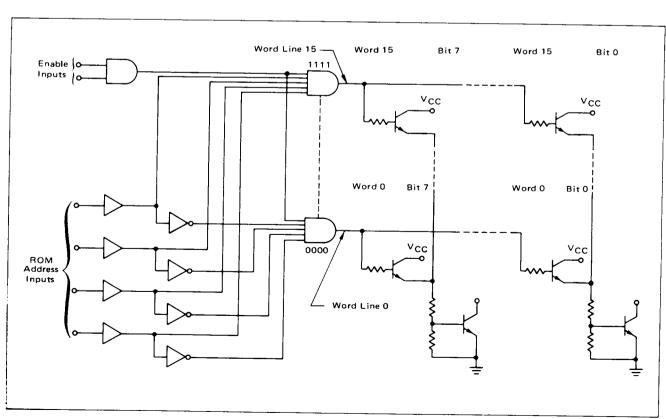

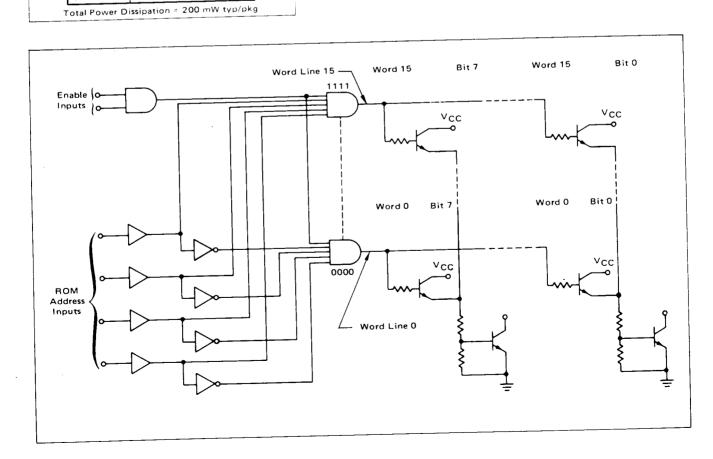

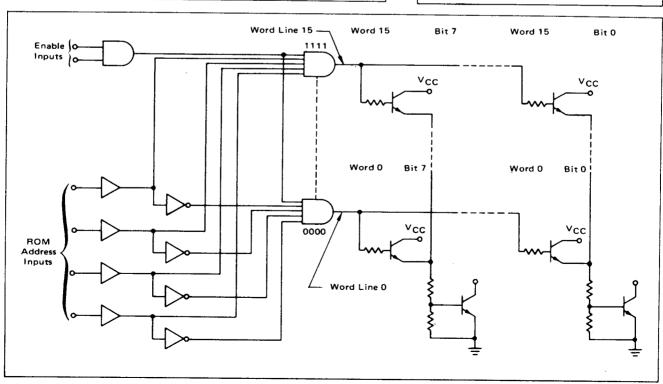

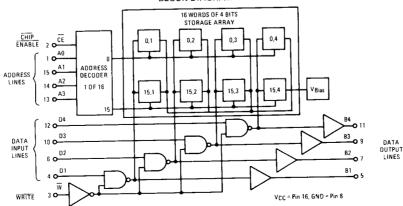

#### 16-BIT SCRATCH PAD MEMORY CELL

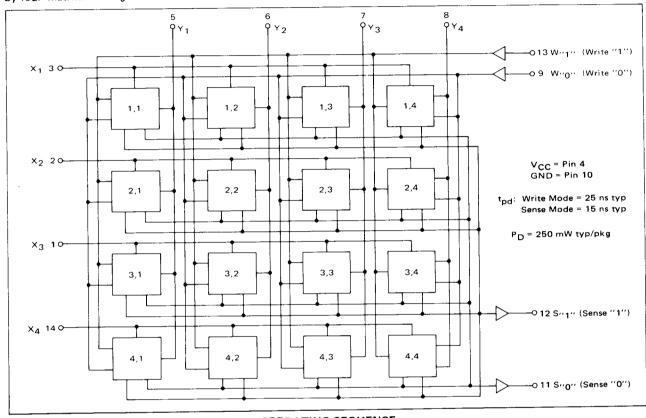

## MC4304 · MC4305 MC4004 · MC4005

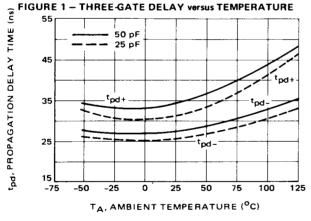

This 16-Bit memory cell serves as the basic building block for scratch pad memory systems having cycle times of less than 100 ns. The basic cell provides 16 words of one-bit memory operating in the non-destructive readout (NDRO) mode.

The memory contains 16 flip-flops arranged in a fourby-four matrix. A single bit of the matrix is selected by driving one of four X select lines and one of four Y select lines above the select threshold. Two sense amplifiers are shared by all 16 bits and provide a double rail output from the selected bit. The sense output of many devices can be "wired ORed" together since the output stage does not have a pullup resistor or network. Two write amplifiers allow a "1" or a "0" to be written into a selected bit.

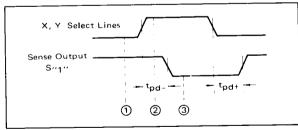

# - OPERATING SEQUENCE - FIGURE 1 - READ MODE TIMING DIAGRAM

- $\bigcirc$  All X and Y selection lines and both write inputs are low (less than +0.8 V).

- ② Desired bit selected by driving the appropriate X and Y select lines more positive than +2.1 V.

- (3) After the turn-on delay time(t<sub>pd</sub>-), the S"1" output will be low (less than +0.45 V) and the S"0" output will be high (more than +2.5 V), providing that a "1" is stored in the selected bit.

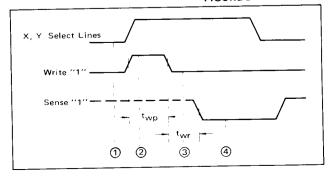

## FIGURE 2 - WRITE MODE TIMING DIAGRAM

- ① All X and Y selection lines and both write inputs are low (less than +0.8 V).

- ② Bit location selected by driving the appropriate X and Y select lines more positive than +2.1 V. To write a "1", drive the write "1" input more positive than +2.1 V for a minimum time of 25 ns (twp).

- (3) Write "1" line returned to low state.

- The stored bit can be read after the write recovery time  $(t_{Wr})$  of 40 ns. (The sense output is in an indeterminate state between steps 2 and 4.)

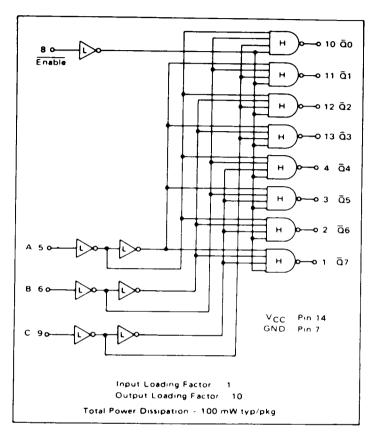

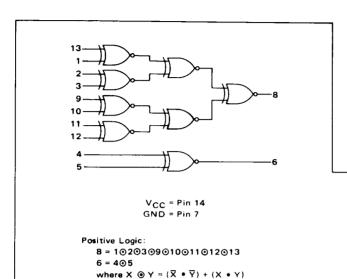

## MC4306 MC4006

#### LOW-LEVEL INVERTER

## HIGH-LEVEL GATE

This device converts three lines of input data to a one-of-eight output. The enable line provides an inhibit capability and also allows the decoder to be expanded for larger decoder systems.

The 3-input/8-output decoder consists of high-level and low-level gates internally connected for minimum power consumption and maximum driving capabilities. The enable gate must be in the low state to perform the decode operation shown in the truth table.

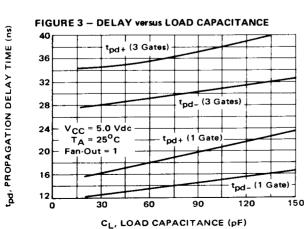

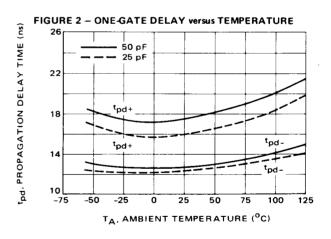

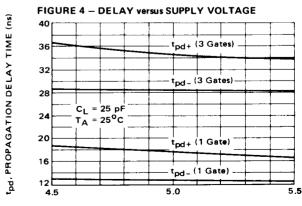

The propagation delays shown in the charts are typical and vary according to loading, interconnection wiring length, and the number of logic levels involved.

| ě o |   |   |    | TR | итн т      | ABLE |    |    |    |    |

|-----|---|---|----|----|------------|------|----|----|----|----|

| С   | В | А | ā7 | Õ6 | <u>Q</u> 5 | Q4   | Ō3 | ā2 | Ωī | ŌΩ |

| 0   | 0 | 0 | 1  | 1  | 1          | 1    | 1  | 1  | 1  | 0  |

| 0   | 0 | 1 | ,  | 1  | ,          | 1    | 1  | 1  | 0  | 1  |

| 0   | 1 | 0 | 1  | 1  | 1          | 1    | 1  | 0  | 1  | 1  |

| 0   | 1 | 1 | 1  | 1  | 1          | ,    | 0  | 1  | 1  | 1  |

| 1   | 0 | 0 | 1  | 1  | 1          | 0    | 1  | 1  | 1  | 1  |

| ,   | 0 | 1 | 1  | 1  | 0          | 1    | 1  | ,  | 1  | 1  |

| ,   | 1 | 0 | 1  | 0  | 1          | 1    | 1  | 1  | 1  | 1  |

| 1   | 1 | 1 | 0  | 1  | 1          | 1    | 1  | 1  | 1  | 1  |

1 High State 0 Low State

## TYPICAL TURN ON DELAY TIMES (ns) $T_A = 25^{\circ}\text{C}_{\odot}\text{C}_{\uparrow} = 25^{\circ}\text{F}$

INPUT ŌΟ Ō١ Ō2 Q3 Q4 Õ5 Õ7 Ō6 160 115 16.0 115 16 0 115 16 0 В 115 115 16 0 115 160 115 16.0 16.0 c 115 115 115 115 16 0 160 160 135 135 13 5 135 135 135 13 5 13.5

## TYPICAL TURN-OFF DELAY TIMES (ns) $T_A = 25^{\circ}C$ , $C_T = 25 \text{ pF}$

| INPUT | Õ0   | āı   | ā2   | āз   | Q4   | Q5   | Ō6   | <u>ā</u> 7 |

|-------|------|------|------|------|------|------|------|------------|

| Α     | 140  | 19.5 | 14.0 | 19.5 | 14.0 | 19.5 | 14.0 | 19.5       |

| В     | 14.0 | 140  | 19.5 | 19.5 | 14.0 | 14.0 | 19.5 | 19.5       |

| С     | 14.0 | 14.0 | 14.0 | 14.0 | 19.5 | 19.5 | 19.5 | 19.5       |

| Ē     | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5       |

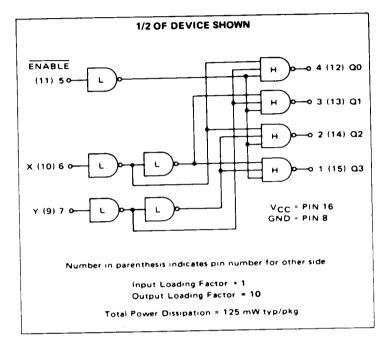

# DUAL BINARY TO ONE-OF-FOUR LINE DECODER

## MC4307 MC4007

## LOW-LEVEL GATE

#### HIGH-LEVEL GATE

This device converts two lines of input data to a one-of-four output. The enable line provides an inhibit capability and also allows the decoder to be expanded for larger decoder systems.

The dual 2-input/4-output decoder consists of high-level and low-level gates internally connected for minimum power consumption and maximum driving capabilities. The enable gate must be in the low state to perform the decode operation shown in the truth table.

The propagation delays shown in the charts are typical and vary according to loading, interconnection wiring length, and the number of logic levels involved.

TRUTH TABLE

| E - 0 |   |    |    |    |            |

|-------|---|----|----|----|------------|

| ×     | Υ | Ω0 | Q1 | Q2 | <b>Q</b> 3 |

| 0     | 0 | 0  | 1  | 1  | 1          |

| 1     | 0 | 1  | 0  | 1  | 1          |

| 0     | 1 | 1  | 1  | 0  | 1          |

| 1     | 1 | 1  | 1  | 1  | 0          |

1 = High State

E - 0

0 = Low State

TYPICAL TURN-ON DELAY TIMES (ns)  $T_A = 25^{\circ}C$

| Input | Ω0   | Q1   | Q2   | <b>Q</b> 3 |

|-------|------|------|------|------------|

| ×     | 11.5 | 15.5 | 11.5 | 15.5       |

| Y     | 11.5 | 115  | 15.5 | 15.5       |

| E     | 13.5 | 13:5 | 13.5 | 13.5       |

TYPICAL TURN-OFF DELAY TIMES (ns)  $T_{\Delta} = 25^{\circ}C$

| Input | 00   | Q1   | Ω2   | <b>Q</b> 3 |

|-------|------|------|------|------------|

| ×     | 14.0 | 19.0 | 14.0 | 19.0       |

| ٧     | 14.0 | 14.0 | 19.0 | 19.0       |

| Ē     | 14.5 | 14.5 | 14.5 | 14.5       |

## MC4308 MC4008

This device consists of seven Exclusive NOR gates connected to check even parity. The output will be in the logic "1" state as long as the "1" state is present on an even number of inputs. The additional Exclusive NOR gate can be used to connect two 8-bit parity trees to form a 16-bit parity tree, or it can be used to convert the parity tree to check odd parity by connecting one gate input to the output of the parity tree and grounding the other input. This conversion can also be accomplished by connecting a simple inverter to the output of the parity tree.

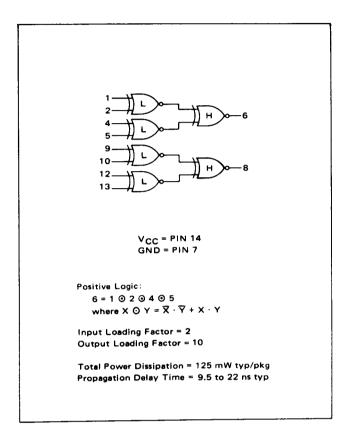

Input Loading Factor = 2

Output Loading Factor = 10

Total Power Dissipation = 150 mW typ/pkg Propagation Delay Time = 15-30 ns typ

#### TYPICAL PROPAGATION DELAY TIMES

## MC4310 MC4010

Three Exclusive NOR gates are connected together to form each of the two 4-bit parity trees in the package. An even number of logic "1" states on the inputs will result in a logic "1" output state. An odd parity checker can be made by connecting an inverter to the output of the device.

This function is constructed using low and high-level Exclusive NOR gates connected as shown in the logic diagram to maximize output drive capability and minimize power dissipation.

## LOW-LEVEL GATE

#### HIGH-LEVEL GATE

## MC4312 MC4012

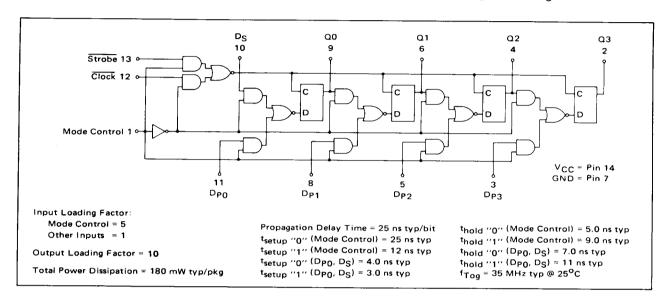

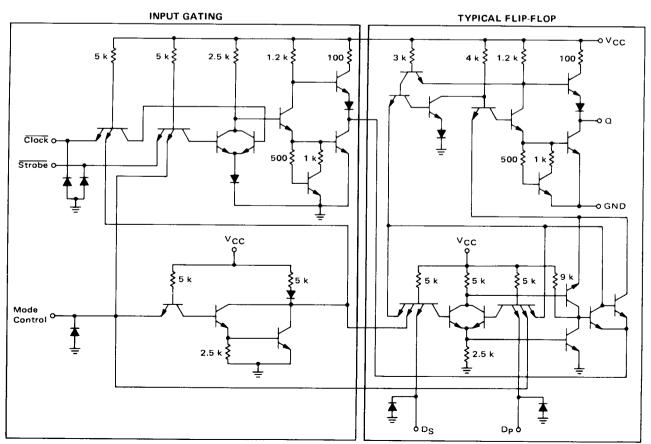

This 4-bit register provides parallel or serial data entry and retrieval, determined by the logic state of the mode control input. For parallel operation, set the mode control to the logic "1" state and strobe the information at the Dp inputs into the register. Serial left-shift operation is achieved in this mode by connecting the Q outputs to the Dp inputs of the previous stage. For serial right-shift operation, set the mode control to logic "0" and clock data into the register from Ds.

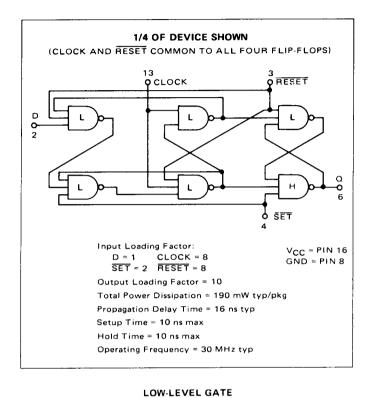

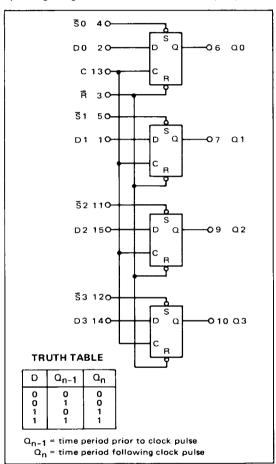

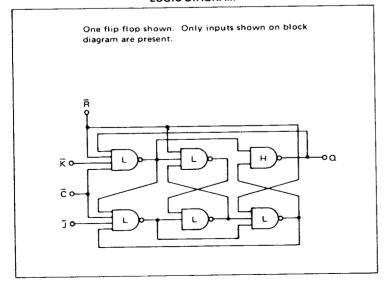

## MC4315 MC4015

# <sup>∨</sup>cc

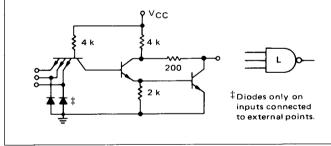

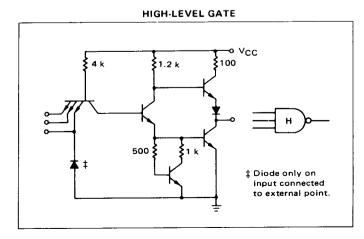

This quad type D flip-flop triggers on the positive edge of the clock input. During the clock transition the state of the D input is transferred to the Q output. The device is useful in shift registers and simple counters.

Power dissipation is minimized and output drive capability is maximized by connecting low and high-level gates as shown by the logic diagram to form each of the four flip-flops.

#### **OPERATING CHARACTERISTICS**

Data must be present at the D input 10 ns prior to the rise of the clock, and remain 10 ns after the clock signal rises. Data may be changed any time during the clock cycle except the interval between the setup time (10 ns) and the hold time (10 ns) without affecting the operation of the flip-flop. The data input is inhibited when the clock is high. When the clock is in the low state, the input steering section continually reflects the state of the D input. Information present at the D input during the time interval between the setup and hold times is transferred to the bistable section on the positive edge of the clock, and outputs Q and Q respond accordingly.

The flip-flops can be set or reset directly at any time, regardless of the state of the clock, by applying a low state to the direct Set or Reset inputs.

## PROGRAMMABLE MODULO-N COUNTERS

## MC4316 MC4016 MC4317 MC4017 MC4318 MC4018 MC4319 MC4019

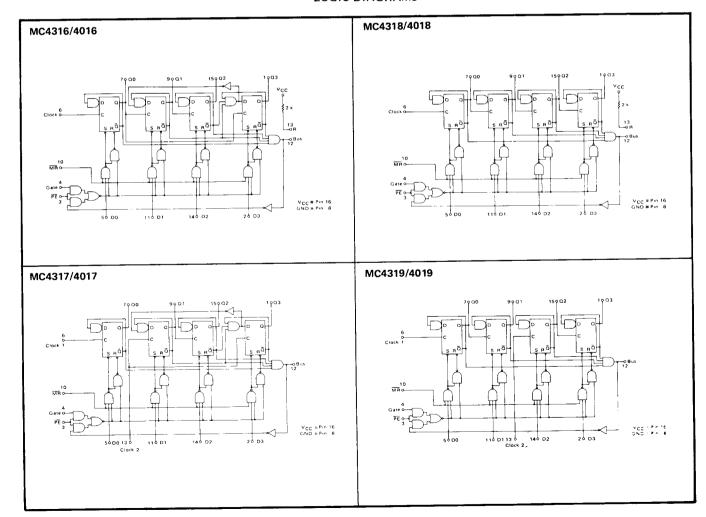

The monolithic devices are programmable, cascadable, modulo-N-counters. The MC4316/4016 can be programmed to divide by any number (N) from 0 thru 9, the MC4318/4018 from 0 thru 15. The MC4317/4017 consists of a modulo 2 counter which can be programmed to divide by 0 or 1 and a modulo 5 counter which can be programmed to divide by any number from 0 to 4. The MC4319/4019 contains two modulo 4 counters which can be programmed to divide by any number from 0 to 3.

The parallel enable  $(\overline{PE})$  input enables the parallel data inputs D0 thru D3. All zeros are entered into the counter by applying a logic "0" level to the master reset  $(\overline{MR})$  and  $\overline{PE}$  inputs. This causes the counter to stop counting (count = 0). All data inputs are independent of the logic level of the Clock.

Modulo-N counters are useful in frequency synthesizers, in phase-locked loops, and in other applications where a simple method for frequency division is needed.

#### All Types:

Input Loading Factor: Clock, PE = 2 D0, D1, D2, D3, Gate = 1

MR = 4

Output Loading Factor = 8

Total Power Dissipation = 250 mW typ/pkg

Propagation Delay Time:

Clock to Q3 = 50 ns typ Clock to Bus = 35 ns typ

#### MC4316/4016 MC4318/4018

V<sub>CC</sub> = Pin 16 Gnd = Pin 8

MC4318/4018

| MC4316/4016                               |                 |                                 |                                      |                 |  |  |  |

|-------------------------------------------|-----------------|---------------------------------|--------------------------------------|-----------------|--|--|--|

| COUNT OUTPUT                              |                 |                                 |                                      |                 |  |  |  |

|                                           | Q3              | Q2                              | Q1                                   | 00              |  |  |  |

| 9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | 1 0 0 0 0 0 0 0 | 0<br>0<br>1<br>1<br>1<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 1 0 1 0 1 0 1 0 |  |  |  |

| COUNT                      | L_      | OUT              | PUT           |             |  |  |  |

|----------------------------|---------|------------------|---------------|-------------|--|--|--|

| COONT                      | Q3      | Q2               | Q1            | QO          |  |  |  |

| 15<br>14                   | 1       | 1                | 1             | 1           |  |  |  |

| 14                         | 1       | 1 1              | 1             | 0           |  |  |  |

| 13                         | 1       | 1                | 0             | 1           |  |  |  |

| 12                         | 1       | 1                | 0             | 0           |  |  |  |

| 11                         | 1       | 0                | 1             | 1           |  |  |  |

| 10                         | 1       | 0                | 1             | 0           |  |  |  |

| 10<br>9<br>8               | 1       | 0                | 0             | 1           |  |  |  |

| 8                          | 1       | 1<br>0<br>0<br>0 | 1001100       | 1 0 1 0 1 0 |  |  |  |

| 7<br>6<br>5<br>4<br>3<br>2 | 0000000 | 1                | 1             |             |  |  |  |

| 6                          | 0       | 1                | 1             | 0           |  |  |  |

| 5                          | 0       | 1                | 0             | 1           |  |  |  |

| 4                          | 0       | 1                | 0             | o           |  |  |  |

| 3                          | 0       | 0                | 1             | 1           |  |  |  |

| 2                          | 0       | 1<br>0<br>0<br>0 | 1             | 0           |  |  |  |

| 1                          | 0       | 0                | 1 0 0 1 1 0 0 | 1 0 1 0 1 0 |  |  |  |

| 0                          | 0       | 0                | 0             | 0           |  |  |  |

|                            |         |                  |               |             |  |  |  |

#### MC4317/4017 MC4319/4019

V<sub>CC</sub> = Pin 16 Gnd = Pin 8

#### MC4317/4017

| COUNT | OUTPUT |

|-------|--------|

| COONT | Ω0     |

| 1     | 1      |

| 0     | 0      |

| COUNT  | ОИТРИТ |    |    |  |

|--------|--------|----|----|--|

| 000141 | Q3     | Q2 | Q1 |  |

| 4      | 1      | 0  | 0  |  |

| 3      | 0      | 1  | 1  |  |

| 2      | 0      | 1  | 0  |  |

| 1      | 0      | 0  | 1  |  |

| 0      | 0      | 0  | 0  |  |

## MC4319/4019

| COUNT | ООТ | PUT |

|-------|-----|-----|

| COUNT | Q1  | Q0  |

| 3     | 1   | 1   |

| 2     | 1   | 0   |

| 1     | 0   | 1   |

| 0     | 0   | 0   |

| COUNT | OUTPUT |            |  |

|-------|--------|------------|--|

| COONT | Q3     | <b>Q</b> 2 |  |

| 3     | 1      | 1          |  |

| 2     | 1      | 0          |  |

| 1 ,   | 0      | 1          |  |

| 0     | 0      | 0          |  |

MC4016 • MC4017 • MC4018 • MC4019

## **OPERATING CHARACTERISTICS**

Basic operation of the MC4316/4016 and MC4318/4018 is the same. When operated as single stages, the Gate and Clock inputs must be tied together. The internal pullup resistor must be connected to the Buss node (pin 13 to pin 12). The programmable counter is set to count down by a pre-determined number (N) before recycling, according to the binary code present at the parallel preset inputs, P0 thru P3 (see the truth table). The binary information at inputs P0 thru P3 is preset into the counter after applying a logic "0" to the PE input. Data may be entered synchronously or asynchronously while PE is low, or when outputs Q0, Q1, Q2 and Q3 are in the logic "0" state and the Clock is low.

The counters may be set to divide by 10 (MC4316/4016) or 16 (MC4318/4018) regardless of preset input states by applying a logic "0" to the Buss node. This, in effect, disables the preset inputs and

causes a logic "0" to appear at the preset of each flip-flop of the counter. If a binary number greater than nine (1001) is applied to the preset inputs of the MC4316/4016, the counter will ignore the most significant bit

Cascading of Counters

To cascade counters (Figure 1):

- Connect Gate inputs of all stages to the Clock of the first stage.

- Connect all Buss outputs to one common pullup resistor (2.0 kilohms, internal).

- 3. Connect the Clock input of each stage after the first stage to the Q3 output of the previous stage.

- 4. Take the divide-by-N pulse from the Buss outputs.

When cascaded, the count mode of the entire string of counters is defined by:

$$N = N_0 + 10 N_1 + 100 N_2 + \dots (MC4316/4016)$$

or

$$N = N_0 + 16 N_1 + 256 N_2 + \dots (MC4318/4018)$$

where  $N_0, N_1, N_2, \ldots$  are the BCD or binary numbers programmed at the zero, first, second,  $\ldots$  stages.

#### LOGIC DIAGRAMS

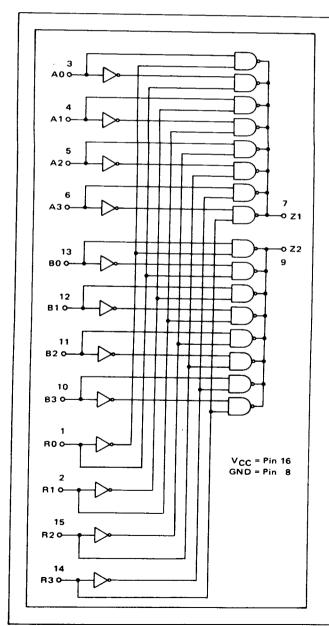

## MC4321/4021 MC4322/4022

The 4-bit comparator compares four bits of input information to four bits of reference information. When each bit of the input information is the same as its corresponding reference information, bit for bit, the output of the comparator will be in the high ("1") state. For any other condition, the output of the comparator will be in the low ("0") state.

In this dual 4-bit comparator, the four reference inputs (R) serve both comparators. There is no interrelation between the A and B data inputs of the dual comparator. Output Z1 reflects comparison of the A and R bits, while output Z2 shows conditions at inputs B and R.

The MC4021 has open-collector outputs; the MC4022 has totem-pole outputs.

| A0  | Α1 | A2 | А3  | В0 | В1 | В2 | В3 | R0 | R1 | R2 | R3 | Z1 | Z2 |

|-----|----|----|-----|----|----|----|----|----|----|----|----|----|----|

| 0   | 0  | 0  | 0   | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  |

| 0   | 0  | 0  | 0   | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | Ιo | 0  |

| 0   | 0  | 0  | 0   | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  |

| 0   | 0  | 0  | 0   | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 1  |

| 0   | 1  | 1  | 0   | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  |

| 0   | 1  | 1  | 0   | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

| 0   | 1  | 1  | 0   | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  |

| 0   | 1  | 1  | 0   | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 0  |

| ] 1 | 0  | 0  | 1   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  |

| 1   | 0  | 0  | 1   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  |

| 1   | 0  | 0  | 1   | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  |

|     | 0  | 0  | 1   | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 0  |

| 1 1 | 1  | 1  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| 1   | 1  | 1  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  |

| 1 1 | 1  | 1  | 1 ] | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

|     | 1  | 1  | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Input Loading Factor = 2 Output Loading Factor = 10 Total Power Dissipation = 250 mW typ/pkg Propagation Delay Time = 20 ns typ

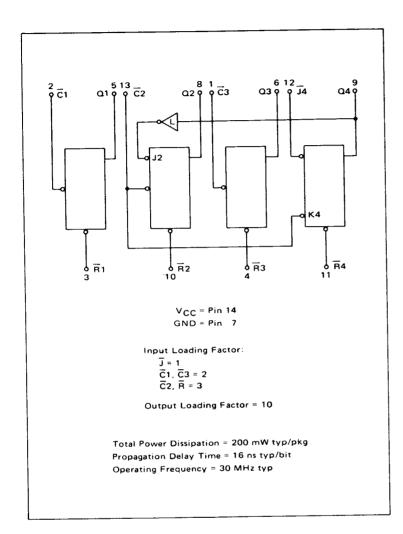

## MC4323 MC4023

## LOGIC DIAGRAM

This device is a 4-bit counter with internally connected feedback. Inputs and outputs can be connected to count to any number between two and twelve except seven and eleven. Reset inputs are provided on each flip-flop to allow direct setting of the  $\Omega$  outputs to zero any time during the counting cycle.

Each flip-flop in the counter is built from high and low-level gates as shown by the logic diagram. The flip-flops and the feedback inverter are connected as shown by the block diagram to provide minimum power dissipation and maximum drive capability.

#### **COUNTING SEQUENCES**

| DIVIDE BY 3 |    |    |  |  |  |  |

|-------------|----|----|--|--|--|--|

| Ĉ2          | Q2 | Q4 |  |  |  |  |

| 0           | 0  | 0  |  |  |  |  |

| 1           | 1  | 0  |  |  |  |  |

| 2           | 0  | 1  |  |  |  |  |

**Q**4

n

0

0

0

1

**DIVIDE BY 6**

Q2

Q1

Ĉ1

| DIVIDE BY 4 |            |            |  |  |  |

|-------------|------------|------------|--|--|--|

| Č1          | <b>Q</b> 1 | <b>Q</b> 3 |  |  |  |

| 0           | 0          | 0          |  |  |  |

| 1           | 1          | 0          |  |  |  |

| 2           | 0          | 1          |  |  |  |

| 3           | 1          | 1          |  |  |  |

0 0 Ω 1 0 2 o 3 1 4 0 0

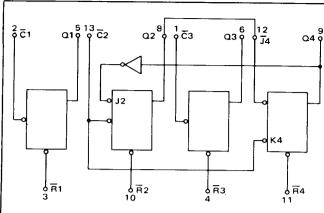

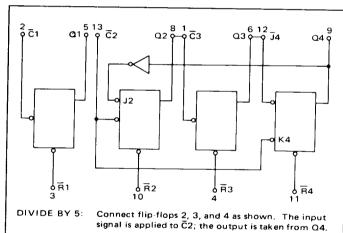

DIVIDE BY 2: Use flip-flop 1 or 3.

Use flip-flops 2 and 4, connected as shown. The input signal is DIVIDE BY 3:

applied to C2; the output is taken from Q4. DIVIDE BY 4: Use flip-flops 1 and 3; connect Q1 to C3.

Apply the input signal to C1.

DIVIDE BY 6: In addition to the connection for divide by 3, connect Q1 to  $\vec{C}2$ .

Apply the input signal to  $\vec{C}1$ .

DIVIDE BY 12: In addition to the connections for divide by 6, connect Q3 to  $\overline{C}1$ . Apply the input signal to  $\overline{C}3$ .

|     | DIVIDE BY 5 |            |    |  |  |  |  |  |

|-----|-------------|------------|----|--|--|--|--|--|

| Ē2  | Q2          | <b>Q</b> 3 | Q4 |  |  |  |  |  |

| 0   | 0           | 0          | 0  |  |  |  |  |  |

| 1 1 | 1           | 0          | 0  |  |  |  |  |  |

| 2   | 0           | 1          | 0  |  |  |  |  |  |

| 3   | 1           | 1          | 0  |  |  |  |  |  |

| 4   | 0           | 0          | 1  |  |  |  |  |  |

|     | DIVID       | E BY 8     |    |  |  |  |  |  |

|    | DIVID | E BY 8 | }  |

|----|-------|--------|----|

| Ē1 | Ω1    | 0.2    | 03 |

| 0  | 0     | 0      | 0  |

| 1  | 1     | 0      | 0  |

| 2  | 0     | 1      | 0  |

| 3  | 1     | 1      | 0  |

| 4  | 0     | 0      | 1  |

| 5  | 1     | 0      | 1  |

| 6  | 0     | 1      | 1  |

| 7  | _ 1   | _ 1    | 1  |

**DIVIDE BY 10** Ĉ1 Q2 Q3 Q4 0 0 0 2 0 0 3 0 0 0 0 5 0 O 6 0 1 0 0 8 o 0

DIVIDE BY 10: In addition to the connections for divide by 5, connect Q1 to C2. Apply the input signal to C1.

Connect flip-flops 2 and 3 as shown for divide by 5, but do not connect Q3 to  $\overline{J}4$ . Connect Q1 to  $\overline{C}2$ . The input signal is applied to  $\overline{C}1$ ; the output is taken from Q3. DIVIDE BY 8:

₽ <u>F</u>3

∂R2

|    | DIVIDE BY 9 |    |    |    |  |  |  |  |  |  |

|----|-------------|----|----|----|--|--|--|--|--|--|

| C2 | Q2          | 03 | Q1 | Q4 |  |  |  |  |  |  |

| 0  | 0           | 0  | 0  | 0  |  |  |  |  |  |  |

| 1  | 1           | 0  | 0  | 0  |  |  |  |  |  |  |

| 2  | 0           | 1  | 0  | 0  |  |  |  |  |  |  |

| 3  | 1           | 1  | 0  | 0  |  |  |  |  |  |  |

| 4  | 0           | 0  | 1  | 0  |  |  |  |  |  |  |

| 5  | 1           | 0  | 1  | 0  |  |  |  |  |  |  |

| 6  | 0           | 1  | 1  | 0  |  |  |  |  |  |  |

| 7  | 1           | 1  | 1  | 0  |  |  |  |  |  |  |

| 8  | 0           | 0  | 0  | 1  |  |  |  |  |  |  |

DIVIDE BY 9: The input signal is applied to  $\overline{C}2$ ; the output is taken from Q4.

₀ R4

## MC4324 MC4024

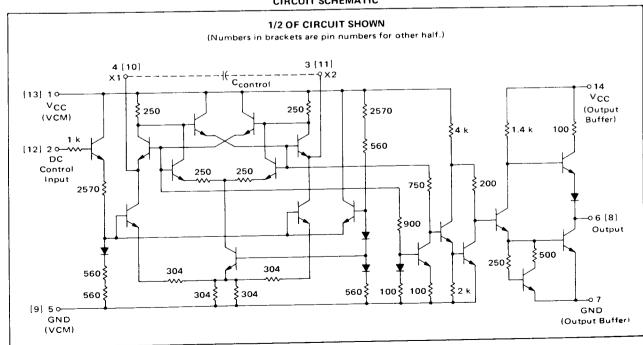

#### CIRCUIT SCHEMATIC

## MC4326 · MC4327 MC4026 · MC4027

Input Loading Factor:

A, B = 2

C<sub>in</sub>, Pins 11, 12, 13 = 1

Output Loading Factor:

MC4326 = 15 MTTL | Loads MC4327 = 7 MTTL | Loads

MC4026 = 12 MTTL | Loads

MC4027 = 6 MTTL I Loads

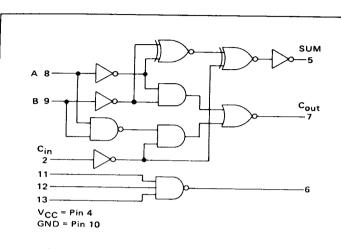

These full adders are designed for serial and ripple-carry parallel adder systems. True Sum and Carry are produced at the output from the input information. A separate 3-input NAND gate is provided on the monolithic chip to provide the inverted Sum or Carry output.

#### TRUTH TABLE

|    | Input Pins |                 |     | ut Pins |

|----|------------|-----------------|-----|---------|

| 8  | 9          | 2               | 5   | 7       |

| Α  | В          | C <sub>in</sub> | SUM | Cout    |

| 0  | 0          | 0               | 0   | 0       |

| 0  | 0          | 1               | 1   | 0       |

| 0  | 1          | 0               | 1   | 0       |

| 0  | 1          | 1               | 0   | 1       |

| 1  | 0          | 0               | 1   | 0       |

| 1  | 0          | 1               | 0   | 1       |

| 1  | 1          | 0               | 0   | 1       |

| _1 | 1          | 1               | 1   | 1       |

Total Power Dissipation = 90 mW typ/pkg

Add Delay = 25 ns typ Carry Delay = 13 ns typ

TET Edads Carry Delay - 13 list

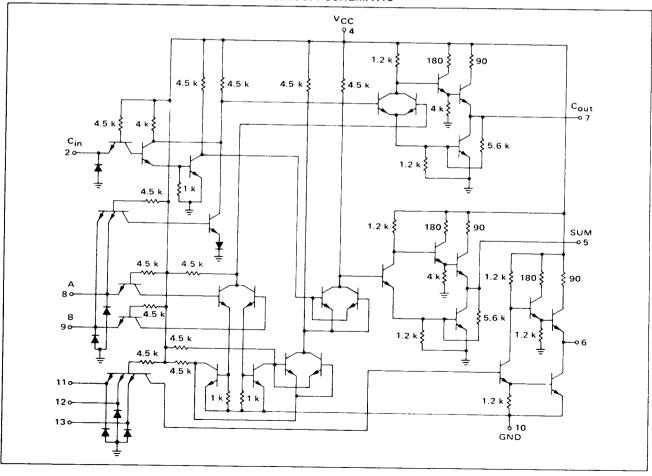

## **CIRCUIT SCHEMATIC**

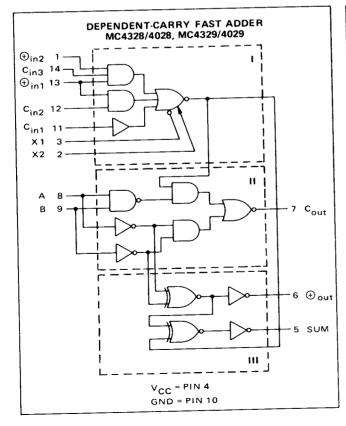

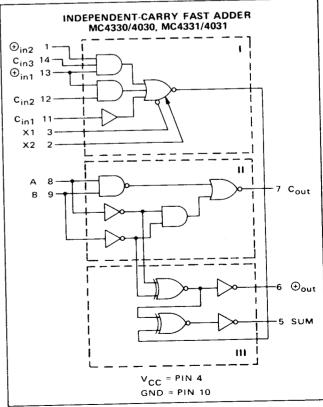

## MC4328 thru MC4331 MC4028 thru MC4031

## CONDENSED TRUTH TABLE FOR THE Nth STAGE

| Pin Numbers |           |                       |                  |             |             |              |                                    |                                    | 1                 |

|-------------|-----------|-----------------------|------------------|-------------|-------------|--------------|------------------------------------|------------------------------------|-------------------|

| 8           | 1 9 I     | 11                    | 12,13            | 13, 14, 1   | 5           | 6            |                                    |                                    | 1 1               |

|             | Bn        | C <sub>in1(n-1)</sub> | Note 1           | Note 2      | Sum         | <b>O</b> but | MC4330/4030<br>MC4331/4031<br>Cout | MC4328/4028<br>MC4329/4029<br>Cout | Comment<br>Note 3 |

| An<br>0     | 0 0       | 0                     | 0                | 0           | 0           | 0            | 0                                  | 0<br>0<br>0                        | -                 |

| 00          | 0         | 0                     | 1                | 0           | 1           | 0            | 0                                  | 0                                  | φ                 |

| 0 0         | 0 0       | 1<br>1<br>1           | 0<br>0<br>1      | 0<br>1<br>0 | 1 1 1 1     | 0<br>0<br>0  | 0<br>0<br>0                        | 0<br>0<br>0                        | φ<br>φ<br>φ       |

| 0 0         | 1 1 1     | 0<br>0<br>0           | 0<br>0<br>1      | 0<br>1<br>0 | 1<br>0<br>0 | 1<br>1<br>1  | 0<br>0<br>0<br>0                   | 0<br>1<br>1                        | -<br>-<br>•       |

| 0 0 0       | 1 1 1 1 1 | 1 1 1                 | 0<br>0<br>1      | 0<br>1<br>0 | 0 0 0       | 1<br>1<br>1  | 0<br>0<br>0                        | 1<br>1<br>1                        | φ<br>φ            |

| 1 1         | 0 0       | 0<br>0<br>0           | 0<br>0<br>1      | 0<br>1<br>0 | 1<br>0<br>0 | 1<br>1<br>1  | 0<br>0<br>0                        | 0<br>1<br>1<br>1                   | 0                 |

| 1 1 1       | 0 0 0     | 1 1 1                 | 0<br>0<br>1      | 0 1 0 1     | 0<br>0<br>0 | 1<br>1<br>1  | 0<br>0<br>0                        | 1 1 1 1                            | φ<br>φ<br>φ       |

| 1 1 1       | 1 1       | 0 0 0                 | 0<br>0<br>1<br>1 | 0<br>1<br>0 | 0<br>1<br>1 | 0<br>0<br>0  | 1<br>1<br>1<br>1                   | 1<br>1<br>1<br>1                   | o,                |

| 1 1         | 1 1 1     | 1 1 1 1               | 0 0 1            | 0<br>1<br>0 | 1<br>1<br>1 | 0<br>0<br>0  | 1<br>1<br>1<br>1                   | 1<br>1<br>1                        | ф<br>ф<br>ф       |

This column represents the AND function whose inputs are pins 13 and 12, and is defined by the expression  $(A_{n,1} \oplus B_{n,1})(C_{in} [n,2])$

expression (A<sub>n.1</sub>  $\odot$  B<sub>n.1</sub>  $\square$  C<sub>m</sub> [n.2]. Note 2. This column represents the AND function whose inputs are pins 13, 14, and 1, and is defined by the expression (A<sub>n.1</sub>  $\odot$  B<sub>n.1</sub>  $\square$  (A<sub>n.2</sub>  $\odot$  B<sub>n.2</sub>  $\square$  (C<sub>n.3</sub>). Note 3.  $\bigcirc$  Don't Care. The "Don't Care" occurs for the MC4330.31/4030.31 only, because the C<sub>n.</sub> and the  $\bigcirc$ n from any one previous stage entering a given subsequent stage cannot be simultaneously at logic "1".

This family of fast adders is designed for use in parallel look-ahead carry adder applications where high-speed addition is required. The dependentcarry fast adders have a Carry output that is dependent upon the two input bits for that stage plus the Carry input from all previous stages. The Carry output from the MC4330/31 is independent of the carry from the previous stages.

Input Loading Factor: ①<sub>in1</sub>, A, B = 2 ⊕<sub>in2</sub>, C<sub>in1</sub>, C<sub>in2</sub>, C<sub>in3</sub> = 1 Output Loading Factor: MC4328, MC4330 = 15 MTTL I Loads MC4329, MC4331 = 7 MTTL | Loads MC4028, MC4030 = 12 MTTL | Loads MC4029, MC4031 = 6 MTTL | Loads Total Power Dissipation = 125 mW typ/pkg Add Delay = 25 ns typ

Carry Delay = 13 ns typ

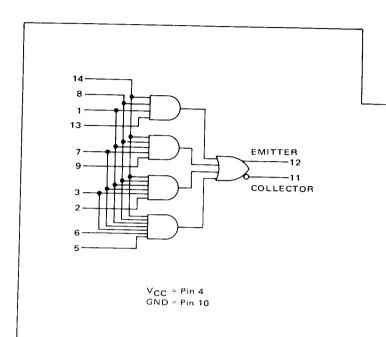

## MC4332 MC4032

This 4-wide 4, 5, 6, 7 input AND-OR expander provides the necessary logic for carry decoding between look-ahead carry adder stages using the MC4328/29 and MC4330/31 fast adders.

Input Loading Factor:

Pins 1, 8, 14 = 4

Pin 7 = 3

Pin 3 = 2

Pins 2, 5, 6, 9, 13 = 1

Total Power Dissipation = 20 mW typ/pkg  $\Delta t_{pd} = 4.0 \text{ ns typ/decoder}$  1.0 ns typ/pF at expander nodes

## TYPICAL APPLICATION

The MC4328/29 and MC4330/31 adders can be used with the MC4332 Carry Decoder to build 8-stage look-ahead carry subsystems. (See the MC4328-31) data sheet for a diagram.) Each stage examines the carry outputs from all previous stages while adding bits A and B for that stage. The carry outputs of the first and eighth stages are dependent upon the carry inputs from previous stages; thus the MC4328/29 adder is used for stages one and eight while the MC4330/31 adder is used for stages two through seven. The MC4332 Carry Decoder is used to expand the look-ahead carry input capability required for stages four through eight.

The add delay of an eight stage adder is equal to the sum of the add delay and the delay from the A and B inputs to the  $\oplus$  output of one stage. Thus the typical add delay for an 8-stage adder is 25 ns +13 ns or 38 ns typical.

When expander inputs are not used they should not be connected to any external point. This minimizes possible problems resulting from noise pick-up.

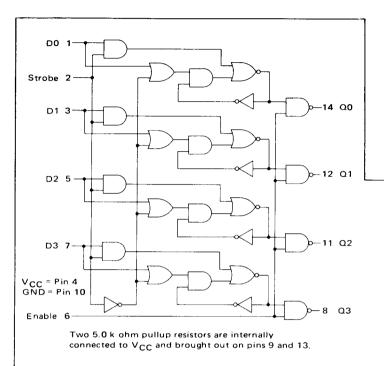

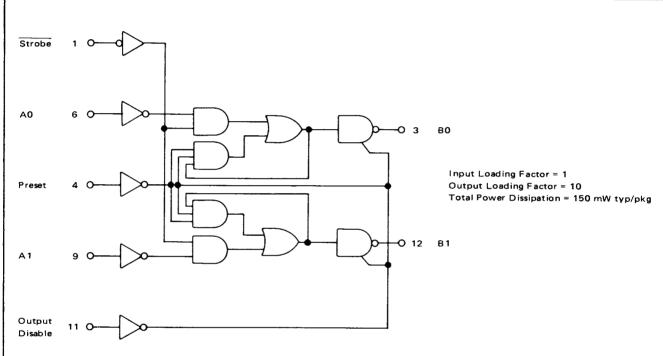

#### **QUAD LATCH** (Open Collector)

## MC4335 MC4035

This monolithic device consists of four latch circuits with open collector outputs, common Strobe input, and output enable input. The output of each latch will follow the data input when the Strobe input is in a logical "1" state. When the Strobe is in a logical "O" state, the latch will store the logic state of the data input just prior to the change of the Strobe from a "1" level to a "0" level.

The open collector outputs make this device useful for bussing or wire ORing outputs together. Two 5.0 k ohm resistors are available in the package to provide the passive pullup function in wired-OR or bussed operation. The output enable is useful where it is desirable to gate information out of the latches according to a predetermined timing scheme.

Input Loading Factor (MTTL I Loads): Data Input (Strobe High) - MC4335 = 4.2 MC4035 = 4.0Data Input (Strobe Low) - MC4335 = 1.1 MC4035 = 0.9Output Enable - MC4335 = 4.0 MC4035 = 3.6Strobe -MC4335 = 5.2MC4035 = 5.2 Output Loading Factor (MTTL I Loads): MC4335 = 7 (I<sub>OL</sub> = 9.3 mAdc) MC4035 = 7 (I<sub>OL</sub> = 11.6 mAdc) Total Power Dissipation = 140 mW typ/pkg Propagation Delay Time = 25 ns typ

#### **CIRCUIT SCHEMATIC**

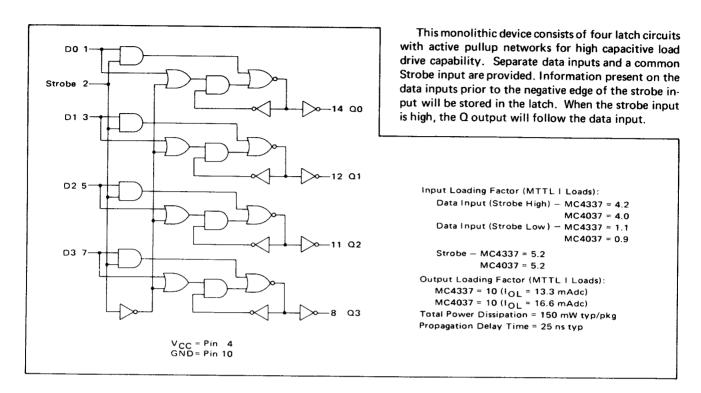

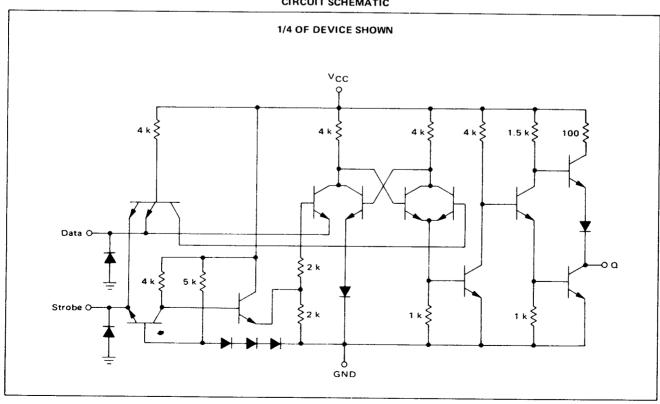

#### **QUAD LATCH**

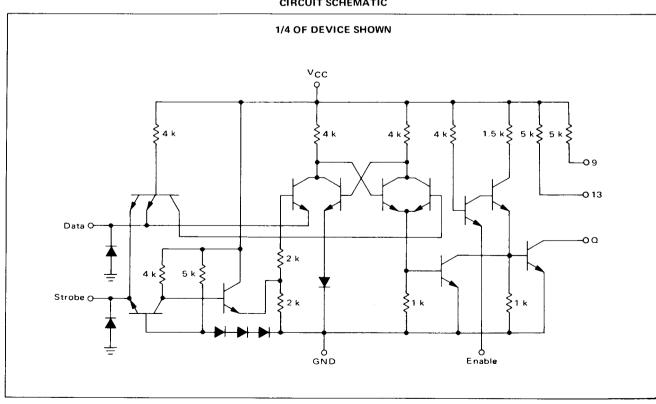

## MC4337 MC4037

### CIRCUIT SCHEMATIC

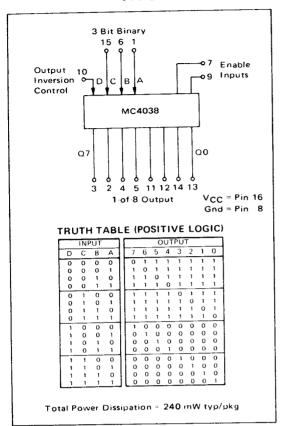

# INVERTING/NON-INVERTING ONE-OF-EIGHT DECODER

## MC4338 MC4038

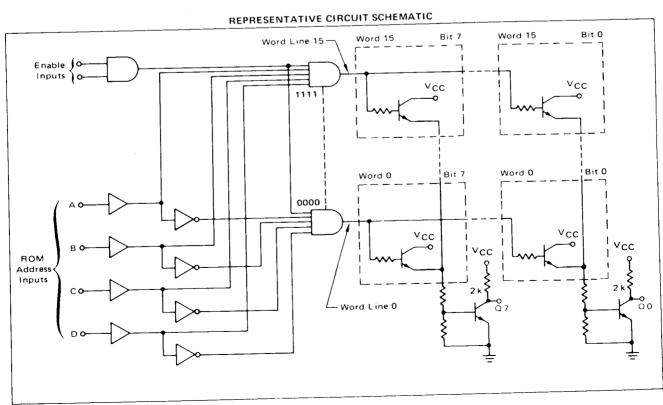

A 3-bit binary address selects the desired word for the 8-bit output. The inversion control, D, selects half of the memory chip with the bit pattern that defines a 1-of-8 decoder function. When D is a logic "0", the selected output is designated as a logic "0". A logic "1" on D produces a logic "1" on the selected output.

#### Features:

Address times < 45 ns

Outputs sink 20 mA

Output capacitance < 7.0 pF @ 1.5 V

Wired OR capability to 64 memories

| E | Ε | Ω7 | Q6 | Q5   | Q4   | <b>Q</b> 3 | Q2  | Q1 | QO |

|---|---|----|----|------|------|------------|-----|----|----|

| 0 | 0 | 1  | 1  | 1    | 1    | 1          | 1   | 1  | 1  |

| 0 | 1 | 1  | 1  | 1    | 1    | 1          | 1   | 1  | 1  |

| 1 | 0 | 1  | 1  | 1    | 1    | 1          | 1   | 1  | 1  |

| 1 | 1 |    |    | FUNC | TION | ENAB       | LED |    |    |

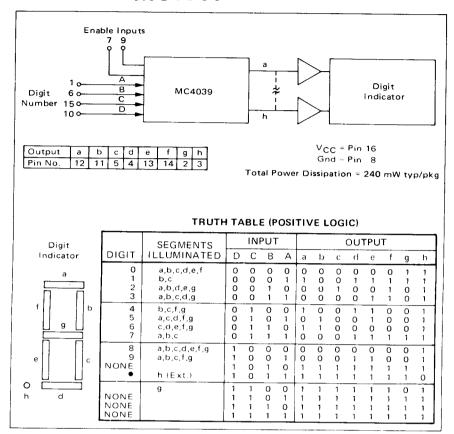

#### SEVEN-SEGMENT CHARACTER GENERATOR

## MC4339 MC4039

#### The MC4339 can directly

operate low-voltage lamp indicators. A four digit binary input is translated into combinations of the eight outputs. These combinations correspond to different illuminated segments of the seven-bar digit indicator. The input and output codes with their related numerical digits are shown in the diagram. The enable inputs can be used for automatic blanking.

#### Features:

Address times < 45 ns Outputs sink 20 mA Output capacitance < 7.0 pF @ 1.5 V Wired OR capability to 64 memories

| Ę | Е | а | b  | С    | d    | е   | f    | g   | h |

|---|---|---|----|------|------|-----|------|-----|---|

| 0 | 0 | 1 | 1  | 1    | 1    | 1   | 1    | 1   | 1 |

| 0 | 1 | 1 | 1  | 1    | 1    | 1   | 1    | 1   | 1 |

| 1 | 0 | 1 | 1  | 1    | 1    | 1   | 1    | 1   | 1 |

| 1 | 1 |   | FL | JNC. | LION | IEN | ABLE | = - |   |

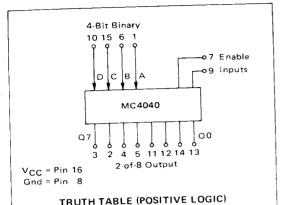

# BINARY TO TWO-OF-EIGHT DECODER

## MC4340 MC4040

| T           | RU          | тн               | TAI              | BL          | : (P             | US.         |                  | VE               | LU               | 910              |                  |

|-------------|-------------|------------------|------------------|-------------|------------------|-------------|------------------|------------------|------------------|------------------|------------------|

| - 1         | NΡ          | UΤ               |                  |             |                  | 0           | UT               | PU               | Γ_               |                  |                  |

| D           | С           | В                | А                | 7           | 6                | 5           | 4                | 3                | 2_               | 1                | 0                |

| 0 0 0       | 0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>1<br>1 | 1<br>1<br>1<br>1 | 1<br>1<br>1 | 0 0 0            | 1<br>1<br>1<br>0 | 1<br>1<br>0<br>1 | 1<br>0<br>1      | 0<br>1<br>1      |

| 0000        | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>1<br>1 | 1<br>1<br>1      | 0<br>0<br>0 | 1<br>1<br>1      | 1<br>1<br>0      | 1<br>0<br>1      | 1<br>0<br>1<br>1 | 0<br>1<br>1      |

| 1 1 1 1     | 0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1 1 1       | 0 0 0            | 1<br>1<br>1 | 1<br>1<br>1      | 1<br>1<br>1<br>0 | 1<br>0<br>1      | 1<br>0<br>1<br>1 | 0<br>1<br>1      |

| 1<br>1<br>1 | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0 0 0       | 1<br>1<br>1      | 1<br>1<br>1 | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>0 | 1<br>1<br>0<br>1 | 1<br>0<br>1<br>1 | 0<br>1<br>1<br>1 |

This device, with two enable inputs, transforms any 4-bit binary number to a 2-of-8-bit coded number. The device can also be thought of as a dual binary to 1-of-4 decoder.

#### Features:

Address times < 45 ns Outputs sink 20 mA Output capacitance < 7.0 pF @ 1.5 V Wired OR capability to 64 memories

| L      |   |   |      |      |      |     |   |     |

|--------|---|---|------|------|------|-----|---|-----|

|        | 1 | 1 | 1    | 1    | 1    | 1   | 1 | 1   |

| 1      | 1 | 1 | 1    | 1    | 1    | 1   | 1 | . 1 |

| 1      | 1 | 1 | 1    | 1    | 1    | 1   | 1 | _ 1 |

| Fi - 1 |   |   | FUNC | TION | ENAB | LED |   |     |

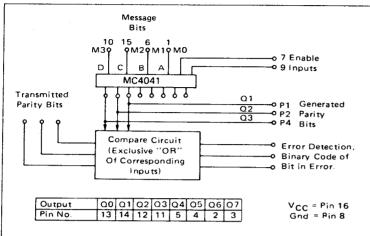

### SINGLE-ERROR HAMMING CODE DETECTOR AND GENERATOR

## MC4341 MC4041

#### TRUTH TABLE (POSITIVE LOGIC)

|             | INI     | rut              |                  |                  |                  | (           | Oυ.              | TPL              | JΤ               |                  |                  |

|-------------|---------|------------------|------------------|------------------|------------------|-------------|------------------|------------------|------------------|------------------|------------------|

| ₽           | С       | В                | Α                | 7                | 6                | 5           | 4                | 3                | 2                | 1                | 0                |

| 0000        | 0000    | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>0<br>0      | 1<br>0<br>0      | 1<br>1<br>1 | 1<br>1<br>0      | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 | 1<br>0<br>0      | 0<br>1<br>1<br>0 |

| 0 0 0       | 1 1 1 1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>0 | 0 0 0       | 1 0 0            | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>0<br>0      | 1<br>0<br>0      |

| 1<br>1<br>1 | 0 0 0   | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 0<br>1<br>1<br>0 | 0 0 0       | 0<br>0<br>1<br>1 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1<br>1<br>0 | 1<br>0<br>0      |

| 1<br>1<br>1 | 1 1 1   | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>0<br>0<br>1 | 1<br>0<br>0<br>1 | 1<br>1<br>1 | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 | 0<br>1<br>1      | 0<br>1<br>1<br>0 |

Simple Parity: The outputs of bits 0, 6, and 7 provide parity check over the 4 message bits.

Hamming Detection and Correction: Bits 1, 2, and 3 perform the parity calculations necessary for Hamming Code generation or detection on 4 message bits. For greater than 4 bits per message, ROM's may be cascaded. In these cases, bits 4, 5, 6, and 7 perform the necessary parity calculations.

Total Power Dissipation = 240 mW

For more information on this function and its uses, see Application Note AN-446.

The MC4041 is a programmed 128-Bit Read Only Memory suitable for a variety of error detection and correction applications.

Simple parity trees for error detection can be constructed using the MC4041P as the basic building block. Also, more complex error control schemes, such as Hamming single error detection and correction, can be implemented with this device.

#### Features:

Address times < 45 ns Outputs sink 20 mA Output capacitance < 7.0 pF @ 1.5 V Wired OR capability to 64 memories

| Ε | Ε | Q7               | <b>Q6</b> | Q5 | Q4 | Q3 | Q2 | Q1 | Q0 |  |  |  |  |

|---|---|------------------|-----------|----|----|----|----|----|----|--|--|--|--|

| 0 | 0 | 1                | 1         | 1  | 1  | 1  | 1  | 1  | 1  |  |  |  |  |

| 0 | 1 | 1                | 1         | 1  | 1  | 1  | 1  | 1  | 1  |  |  |  |  |

| 1 | 0 | 1                | 1         | 1  | 1  | 1  | 1  | 1  | 1  |  |  |  |  |

| 1 | 1 | FUNCTION ENABLED |           |    |    |    |    |    |    |  |  |  |  |

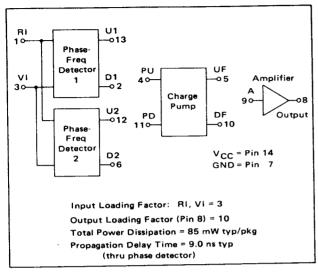

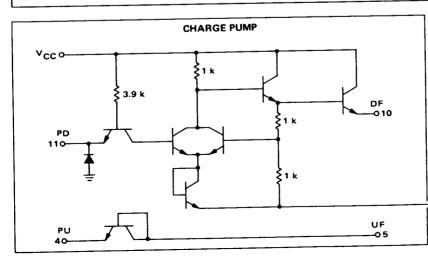

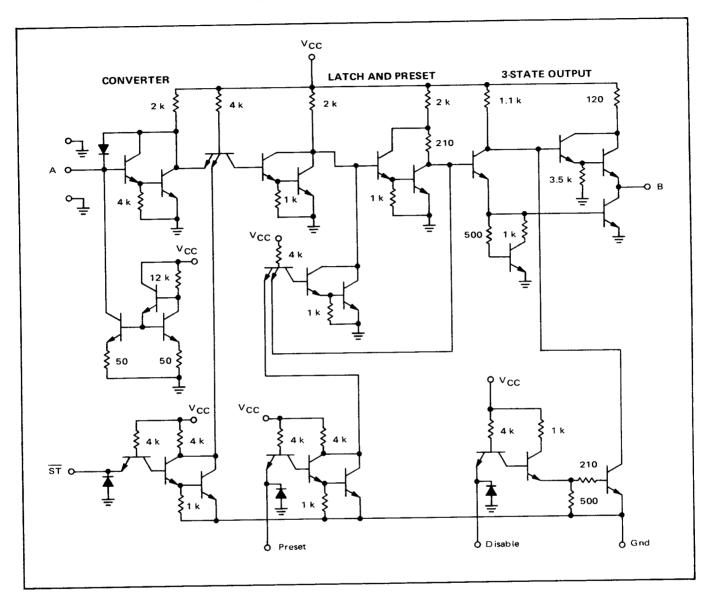

## MC4344 MC4044

This device contains two digital phase detectors and a charge pump circuit which converts MTTL inputs to a dc voltage level for use in frequency discrimination and phase-locked-loop applications.

The two phase detectors have common inputs. Phase-frequency detector 1 is locked in (indicated by both outputs high) when the negative transitions of the variable input (VI) and reference input (RI) are equal in frequency and phase. If the variable input is lower in frequency or lags in phase, the U1 (up) output goes low; conversely the D1 (down) output goes low when the variable input is higher in frequency or leads the reference input in phase. It is important to note that the duty cycles of the variable input and the reference input are not important since negative transitions control system operation.

Phase detector 2, on the other hand, is locked in when the variable input phase lags the reference phase by 90° (indicated by the U2 and D2 outputs alternately going low with equal pulse widths). If the variable input phase lags by more than 90°, U2 will remain low longer than D2, and, conversely, if the variable input phase lags the reference phase by less than 90°, D2 remains low longer. In this phase detector the variable input and the reference must have 50% duty cycles.

The charge pump accepts the phase detector outputs (U1 or U2 applied to PU, and D1 or D2 applied to PD) and converts them to fixed amplitude positive and negative pulses at the UF and DF outputs respectively. These pulses are applied to a lag-lead active filter, which incorporates external components, as well as the amplifier provided in the MC4344/4044 circuit. The filter provides a dc voltage proportional to the phase error.

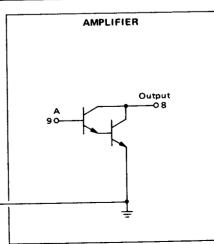

#### PHASE DETECTOR

The phase detector portion of this device is constructed using low and high-level gates interconnected as shown by the logic diagram.

#### **DUAL LINE SELECTOR**

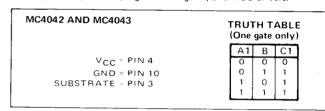

MC4342 MC4042

MC4343 MC4043

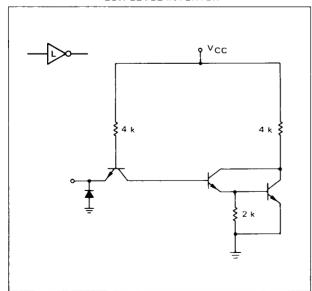

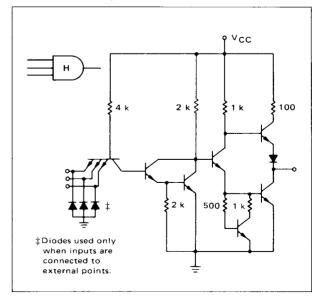

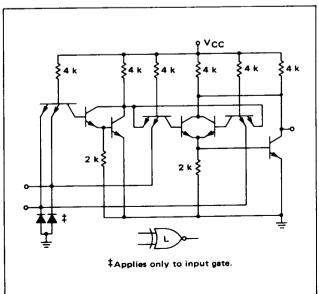

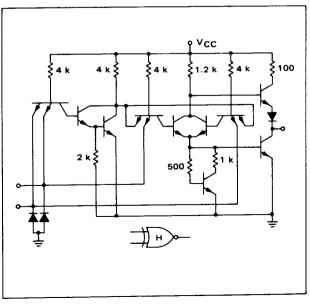

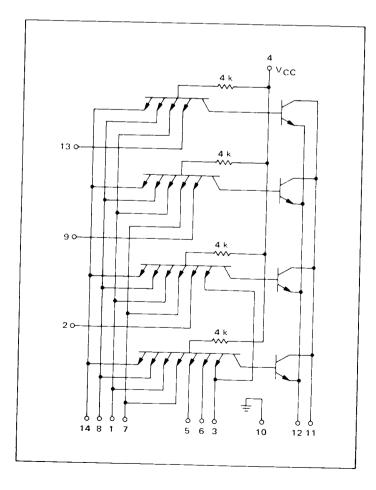

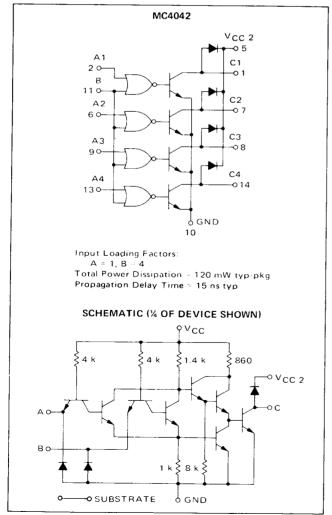

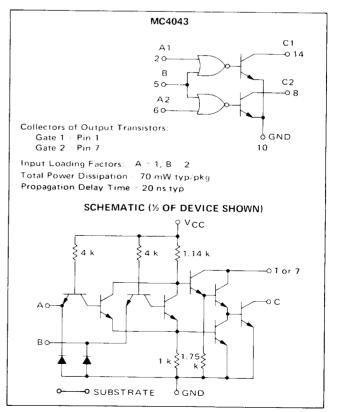

The MC4042 and MC4043 are designed for magnetic memory driver/selector applications.

The MC4042 monolithic quad predriver consists of four high-speed switching transistors, each driven by an MTTL compatible NOR gate. Each NOR gate has an individual address input and a common timing input. The inputs of the MC4042 can be driven directly with standard MTTL decoders such as the MC4006 binary to one-of-eight decoder or the MC4007 dual binary to one-of-four decoder. The open-collector output transistor of the MC4042 will sink 50 mA.

The MC4043 monolithic dual line selector consists of two high-speed 400 mA switches driven by MTTL compatible NOR gates. Each NOR gate has an individual address input and a common timing input. The address and timing inputs of the MC4043 can also be driven directly with standard MTTL decoders such as the MC4006 and MC4007.

The MC4042 and MC4043 input circuits are the same, but the output circuitry is different as shown in the device schematics. The output transistors of both devices have a minimum BV<sub>CEX</sub> of 15 volts, and are gold doped to increase switching speeds.

Many memory predriver applications employ transformer coupling between the predriver and driver stages. In such designs, large voltage overshoots occur due to the transformer inductance and high-speed switching currents. The collector of the MC4042 is internally clamped to prevent the collector from exceeding the maximum rated voltage during the switching transitions. The voltage applied to the diode clamp, pin 5, should be the same or greater than the collector voltages at pins 1, 7, 8, and 14, to prevent the diode clamp from being forward biased during nonswitching periods. The output transistor is driven with a conventional totem pole arrangement to provide active pullup and pulldown.

The collectors of the pullup transistors of the MC4043 are available at pins 1 and 7. An external load resistor to V<sub>CC</sub> must be provided. This reduces power dissipation of the package and provides a means by which the speed of the device can be varied by changing the value of the pullup resistance.

The internal decoding circuitry of the MC4043 is such that both switches can be turned on at one time. However, due to power limitations, care must be taken to ensure that only one switch is turned on at any one time.

The MC4042 and MC4043 can provide a memory system with an inexpensive, reliable, fast drive system. They are also useful as relay or lamp drivers, high fan-out gates, and MOS drivers.

## MC4348 MC4048

ENABLE INPUT TRUTH TABLE (POSITIVE LOGIC)

|   | CIVA | DEE | 1141 0     |                  |    |    |               |    |    |    |  |  |  |  |  |  |

|---|------|-----|------------|------------------|----|----|---------------|----|----|----|--|--|--|--|--|--|

| ٢ | E    | Ε   | Ω7         | Q6               | Q5 | Q4 | <b>G</b> 3    | Q2 | Q1 | 00 |  |  |  |  |  |  |

| H |      | 0   | 1          | 1                | 1  | 1  | 1             | 1  | 1  | 1  |  |  |  |  |  |  |

| ŀ |      | -   | <b>-</b> - |                  | 1  | 1  | 1             | 1  | 1  | 1  |  |  |  |  |  |  |

| Ĺ | 0    | 1_  | 1          | <u> </u>         |    |    | <del></del> - |    | 1  | 1  |  |  |  |  |  |  |

| Г | 1    | 0   | 1          | 1                | 1  | 1  | 1             | 1  |    | L' |  |  |  |  |  |  |

| t | 1    | 1   |            | FUNCTION ENABLED |    |    |               |    |    |    |  |  |  |  |  |  |

| L |      |     | <u> </u>   | FUNCTION ENABLES |    |    |               |    |    |    |  |  |  |  |  |  |

A 3-bit binary address selects the desired word for the 8-bit output, and the selected output goes to a logic "1". The function enable input, D, is useful for expansion of the decoding function. When D is a logic "0" all outputs are logic "0". A logic "1" on D produces a logic "1" on the selected output.

#### Features:

Address times < 50 ns Outputs sink 16 mA Output capacitance < 7.0 pF @ 1.5 V

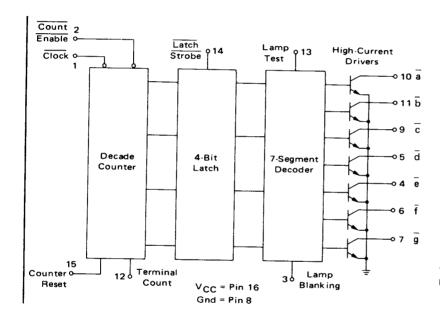

## MC4350 MC4050

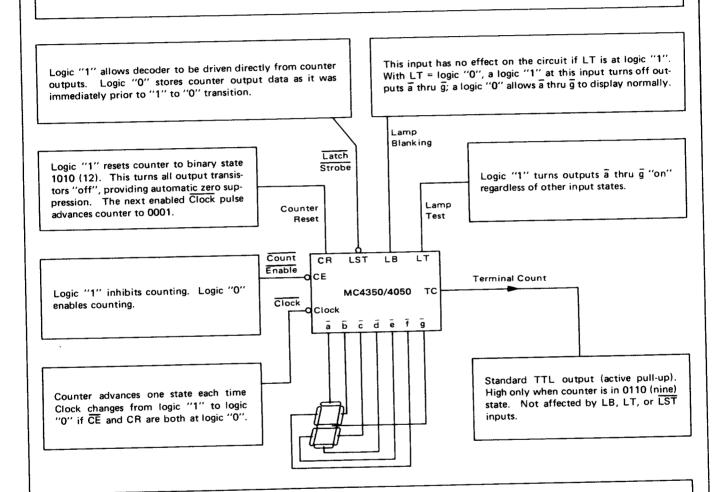

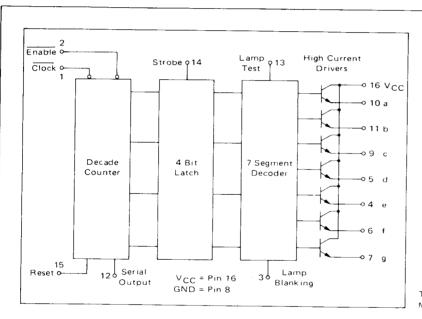

This monolithic integrated circuit combines the functions of a binary coded decimal counter, a four-bit latch, and a seven-segment decoder/driver. Designed primarily for counting applications such as frequency counters, the circuit contains a leading zero blanking feature activated through the Reset input. For this reason the MC4350/4050 is useful in systems using automatic decimal ranging and/or automatic time base selection. A Count Enable input gates the clock input without restrictions on the clock level and without false-clocking the counter. The Terminal Count is high driving the ninth count, allow-

ing synchronous or asynchronous counter operation when used in conjunction with the Count Enable input and external gating. The Counter Reset places the counter in a non-NBCD state, turning off the output driver transistors when transferred through the latch and decoded. The latch section admits information while the Latch Strobe is high and latches the data on the negative edge of the strobe. The seven-segment decoder/driver provides up to 40 mA drive capability for displays requiring current sinking in the active mode. A lamp blanking input provides intensity modulation. A lamp test feature is also available.

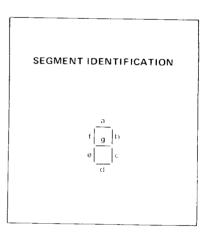

#### SEGMENT IDENTIFICATION

Total Power Dissipation = 450 mW typ/package Maximum Toggle Frequency = 40 MHz typ

## **FUNCTIONAL TRUTH TABLE**

|          |     |      |       |            | IN | PUT |    |    |    |     |     | OUT | PUT         |                  |              |     |

|----------|-----|------|-------|------------|----|-----|----|----|----|-----|-----|-----|-------------|------------------|--------------|-----|

| FUNC     | ΓΙΟ | N    | CLOCK | CE         | CR | LST | LT | LB | TC | ā   | Б   | ī   | ā           | ē                | Ŧ            | 1 = |

| Lan      |     |      | X     | ×          | X  | ×   | 1  | X  |    | 0   | 0   | 0   | 0           | 0                | <del> </del> | g   |

| Lamp Bi  | ank | ing  | ×     | <b>X</b> . | ×  | ×   | 0  | 1  | _  | 1 1 | 1 1 | 1   | •           | 1 0              | 0            | 0   |

| 1        | Re  | eset | [ ×   | X          | 1  | 1   | o  | o  | 0  | ;   | ;   |     | ;           | 1 !              | !            | 1 ! |

| L        | Ena | ble  | P     | 1          | 0  | 1   | 0  | o  | ŏ  | 1   | 1   | ;   | ;           |                  |              | 1 ! |

|          |     | / 1  | P1    | 0          | 0  | 1   | 0  | 0  | 0  | 1   | 0   | 0   | <del></del> | <del>  '</del> - | <u> </u>     |     |

|          | - 1 | 2    | P2    | 0          | ō  | 1   | ō  | o  | ٥  | اهٔ | 0   |     | 0           | '                | 1            | 1   |

| 1        | 1   | 3    | Р3    | 0          | 0  | 1   | o  | ō  | ١٥ | 0   | ő   | 6   | 0           | 0                | 1            | 0   |

|          | 1   | 4    | P4    | 0          | 0  | 1   | ō  | ŏ  | ŏ  | 1   | ő   | 0   | 1           |                  | 0            | 0   |

| State    | ,   | 5    | P5    | 0          | 0  | 1   | 0  | 0  | 0  | 0   | 1   |     | <del></del> | <u> </u>         |              | 0   |

|          | . ( | 6    | P6    | 0          | 0  | 1   | ŏ  | ő  | 0  | 0   | ;   | 0   | 0           | 1 1              | 0            | 0   |

| Sequence | , J | 7    | P7    | 0          | 0  | 1   | ō  | ő  | ő  | 0   | 0   | 0   | 0           | 0                | 0            | 0   |

| 1        | 1   | 8    | P8    | 0          | ō  | 1   | ŏ  | Ö  | Ö  | 0   | 0   | 0   | o           | 0                | 1            | 1   |

| İ        | 1   | 9    | Р9    | 0          | 0  | 1   | 0  | 0  |    | 0   |     |     |             | - 0              | 0            | 0   |

| 1        | 1   | 0    | P10   | ŏ          | ŏ  | i   | ŏ  | ŏ  | ò  | 0   | 0   | 0   | 0           | 1                | 0            | 0   |

| 1        | 1   | . 1  | P11   | 0          | ō  | 1   | ŏ  | ő  | 0  | 1   | 0   | 0   | 0           | 0                | 0            | 1   |

|          | Lat | tch  | Р     | 0          | 0  | 0   | ŏ  | ŏ  | Ö  | i   | ő   | 0   | 1           |                  | 1            | 1 1 |

P = any number of pulses may be applied

Pn = n pulses on the Clock input

X = Don't care

L 3.0 V

#### **FUNCTION DESCRIPTION**

The MC4350/4050 is suited for driving incandescent seven-segment decimal indicators. In addition, only current limiting resistors are needed to allow driving hybrid LED's in the 2.4-volt per segment capability range with commonanode configuration. Use the MC40511 for monolithic LED arrays with common-cathode connection.

#### **OPERATING DETAILS**

- Count Enable may be changed with Clock either high or low.

- Counter Reset overrides Count Enable and Clock. It may be changed regardless of levels present at Count Enable and Clock.

- Latch Strobe, Lamp Blanking, and Lamp Test may be changed regardless of levels at Count Enable, Clock, and Counter Reset.

- Refer to Timing Diagram if a logic "1" to "0" transition on Clock can occur while levels are changing on Count Enable or Latch Strobe, or if a logic "0" to "1" transition of Counter Reset can occur simultaneously with a "0" to "1" transition of Latch Strobe.

- Tie all unused inputs to ground except for Latch Strobe, which must be returned to a logic "1" level if not used.

- Outputs a thru g are open-collector transistors capable of sinking 40 mAdc with outputs low, and sustaining 8.0 Vdc minimum (15 Vdc typical) with outputs high.

## MC4351 MC4051

This device is a monolithic MSI integrated circuit combining the functions of an NBCD counter, four-bit latch, and a seven-segment decoder/driver. The counter advances on the negative edge of the Clock, subject to control by the Enable input. The Serial Output is high driving the ninth count, allowing synchronous or asynchronous counter operation when used in conjunction with the Enable input and some external gating. The counter Reset places the counter in a non-NBCD state, turning off the output driver transistors when transferred through the latch and decoded. This feature gives automatic suppression of leading zeros in the display. The latch section admits information while the Strobe is high and latches the data on the neg-

ative edge of the strobe. The seven-segment decoder/driver is active high and will source up to 40 mA at a 10% duty cycle or 15 mA at a 100% duty cycle. A lamp blanking input is provided for intensity modulation. A lamp test feature is also available.

The output structure of this device is an open emitter-follower configuration whose equivalent circuit is a voltage source with a relatively small series resistance. Although this resistance increases when the output is grounded, the situation is potentially destructive to the device. When the outputs are in the high ("1") state, they should not be connected to ground through an impedance of less than 100 ohms.

Total Power Dissipation = 450 mW typ/package Maximum Toggle Frequency = 35 MHz typ

## **FUNCTIONAL TRUTH TABLE**

| ł         |       |     |   | INI | PUT |    |    |      |   |     | OUT | PUT |    |   | ٦   |

|-----------|-------|-----|---|-----|-----|----|----|------|---|-----|-----|-----|----|---|-----|

| FUNCTI    | ON    | č   | Ē | R   | S   | LT | LB | Sout | а | ь   | С   | ď   | e  | f | g   |

| Lamp      |       | ×   | × | ×   | ×   | 1  | ×  |      | 1 | 1   | 1   | 1   | 1  | 1 | 1   |

| Lamp Blai |       | ×   | × | ×   | ×   | 0  | 1  | l    | o | 0   | Ö   | 0   | 0  | o | 0   |

|           | Reset | ×   | × | 1   | 1   | 0  | 0  | 0    | 0 | 0   | ō   | o   | ő  | 0 | 0   |

| E         | nable | Р   | 1 | 0   | 1   | 0  | 0  | 0    | 0 | 0   | 0   | ŏ   | ő  | ő | 0   |

|           | 1     | P1  | 0 | 0   | 1   | 0  | 0  | 0    | 0 | 1   | 1   | 0   | 0  | 0 | 0   |

| [         | 2     | P2  | 0 | 0   | 1   | 0  | 0  | 0    | 1 | 1   | 0   | 1   | 1  | 0 | 1 1 |

| 1         | 3     | Р3  | 0 | 0   | 1 1 | 0  | 0  | 0    | 1 | 1   | 1   | 1   | 0  | ō | 1 1 |

|           | 4     | P4  | 0 | 0   | 1   | 0  | 0  | 0    | 0 | 1   | 1   | 0   | 0  | 1 | 1   |

| State     | 5     | P5  | 0 | 0   | 1   | 0  | 0  | 0    | 1 | 0   | 1   | 1   | 0  | 1 | 1   |

| Sequence  | ( 6   | P6  | 0 | 0   | 1   | 0  | 0  | 0    | 1 | 0   | 1   | 1   | 1  | 1 | 1   |

| 0-4       | 7     | P7  | 0 | 0   | 1   | 0  | 0  | 0    | 1 | 1   | 1   | 0   | lo | 0 | o   |

|           | _8    | P8  | 0 | 0   | 1   | 0  | 0  | 1    | 1 | 1   | 1   | 1   | 1  | 1 | 1   |

|           | 9     | P9  | 0 | 0   | 1   | 0  | 0  | 0    | 1 | 1   | 1   | 1   | 0  | 1 | 1   |

|           | 0     | P10 | 0 | 0   | 1   | 0  | 0  | 0    | 1 | 1   | 1   | 1   | 1  | 1 | o l |

|           | \ 1   | P11 | 0 | 0   | 1   | 0  | 0  | 0    | 0 | 1   | 1   | 0   | 0  | Ó | ō   |

| <u> </u>  | atch  | Р   | 0 | 0   | 0   | 0  | 0  | 0    | 0 | _ 1 | 1   | 0   | 0  | 0 | 0   |

P = any number of pulses may be applied

$P_n = n$  pulses on the Clock input

X = Don't care

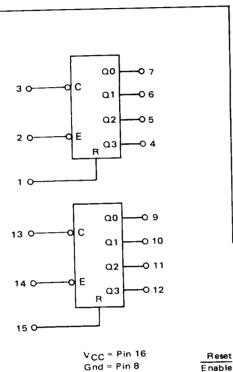

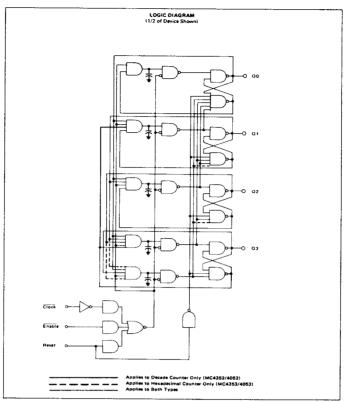

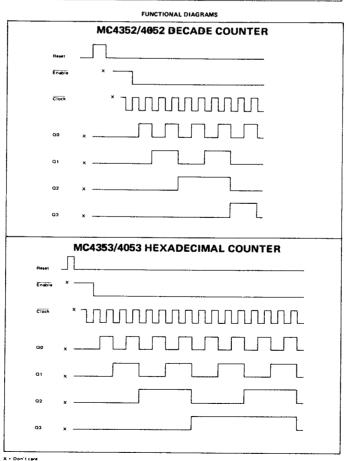

**DUAL DECADE COUNTER**

MC4352 MC4052

**DUAL HEXADECIMAL COUNTER**

MC4353 MC4053

Total Power Dissipation = 350 mW typ/pkg Maximum Toggle Frequency = 40 MHz typ

The MC4352/4052 and MC4353/4053 consist of two independent up counters. The counters advance on the negative edge of the clock when the enable input is low. The count is held when the enable input is high. The enable input should not be taken to the high level while the  $\overline{\text{clock}}$  is high, as erroneous triggering can result. A high level on the reset input places the counter in the 0000 state, overriding the clock and enable inputs. As charge control steering is utilized in this design, capacitive loading on the outputs should be kept at a minimum.

**FUNCTIONAL TRUTH TABLE**

|     |       |     | 1 0140 |       |         |    |      |     |        |      |

|-----|-------|-----|--------|-------|---------|----|------|-----|--------|------|

|     |       |     | N      | AC435 | 2/4052  |    | N    |     | 3/4053 |      |

|     | INPUT |     |        | OUT   | PUT     |    |      | OUT | PUT_   |      |

| R   | Ē     | Ē   | 03     | Q2    | Q1      | QO | Q3   | Q2  | Q1     | 0.0  |

| 1   | ×     | ×   | 0      | 0     | 0       | 0  | 0    | 0   | 0      | 0    |

|     | î     | P   | 0      | o     | 0       | 0  | 0    | 0   | _0_    | _ 0_ |

| 0   | 0     | P1  | 0      | 0     | 0       | 1  | 0    | 0   | 0      | 1    |

| ٥   | ō     | P2  | 0      | 0     | 1       | 0  | 0    | 0   | 1      | 0    |

| l ŏ | ō     | Р3  | 0      | 0     | 1       | 1  | 0    | 0   | 1      | 1    |

| ١٥  | Ö     | P4  | 0      | 1     | 0       | 0  | 0    | 1   | 0      | _ 0  |

| 0   | 0     | P5  | 0      | 1     | 0       | 1  | 0    | 1   | 0      | 1    |

| o   | ō     | Р6  | 0      | 1     | 1       | 0  | 0    | 1   | 1      | 0    |

| ١٥  | 0     | Р7  | 0      | 1     | 1       | 1  | 0    | 1   | 1      | 1    |

| 0   | 0     | Р8  | 1_     | 0     | 0       | 0  | 1_1_ | 0   | 0      | 0    |

| 0   | 0     | P9  | 1      | 0     | 0       | 1  | 1    | 0   | 0      | 1    |

| 0   | 0     | P10 | 0      | 0     | 0       | 0  | 1    | 0   | 1      | 0    |

| 0   | 0     | P11 | 0      | 0     | 0_      | 1_ | 1    | 0   | 1_     | 1_   |

| 1   | 0     | P12 |        |       |         |    | 1    | 1   | 0      | 0    |

| l ŏ | ō     | P13 |        | ۸.    | ove     |    | 1    | 1   | 0      | 1    |

| ٥   | 0     | P14 | 1      |       | uence   |    | ] 1  | 1   | 1      | 0    |

| ١٥  | 0     | P15 | 1      |       | eats    |    | 1    | 1   | 1      | 1    |

| 0   | 0     | P16 | 1      | L/et  | , ea ca |    | 0    | 0   | 0      | 0    |

| 0   | 0     | P17 | i      |       |         |    | 0    | 0   | 0      | 1_   |

Enable

P = any number of pulses may be applied

P<sub>n</sub> = n pulses on the Clock input X = Don't Care

3.0 V - 0 V

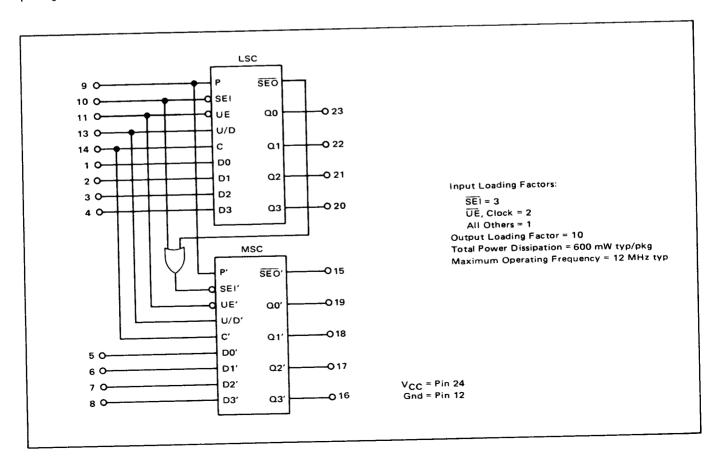

## **DUAL DECADE UP/DOWN COUNTER**

## MC4354 MC4054

**DUAL BINARY UP/DOWN COUNTER**

## MC4355 MC4055

These devices are presettable, synchronous (clocked) up/down coutners. The MC4354/4054 is a decade counter consisting of two separate but cascaded counters. One counter counts the least significant decade, and the other the most significant decade. The counter counts to 1001 1001, or 99, before resetting to 0000 0000. The MC4355/4055 is a binary counter consisting of two separate hexadecimal counters which are cascaded. This counter is essentially an 8-bit binary counter which counts to 1111 1111, or 255, before resetting to 0000 0000.

Both counters in a package are preset by means of a high level on the Preset (P) input. (The Preset input overrides all synchronous inputs: Clock,  $\overline{SEI}$ , and  $\overline{UE}$ .) Information is then loaded into the least significant counter thru inputs D0, D1, D2 and D3, and into the most significant counter thru inputs D0', D1',  $\Delta$ D2', and D3'.

The Up/Down input determines the mode of counting: up when high, down when low.

Two Enable inputs are part of these circuits. The Unit Enable  $(\overline{\text{UE}})$  affects only the counters within a specific package. The Serial Enable  $(\overline{\text{SEI}})$  not only affects a parti-

cular package, but also furnishes a signal at the Serial Enable Output (SEO) for control of succeeding packages in a counter chain. A high input to SEI forces SEO high. When SEI is low, SEO decodes the terminal state of the counter, independently from the UE control, when the counters are in the terminal state. (Terminal state is defined as 0000 0000 when counting down, and as 1111 1111 (256) for the binary counter and 1001 1001 (99) for the decade counter when counting up.)

Both the Serial Enable ( $\overline{SEI}$ ) and the Unit Enable ( $\overline{UE}$ ) must be low for the counter to be clocked. Logic levels on both of these lines must be settled prior to the trailing edge of the Clock, and must remain stable while the Clock is low.

The count state may change only on the leading edge of a Clock pulse. Any changes on the control inputs (Up/Down, SEI, and UE) must be made while the Clock is high.

Counting data is read out on Q0 thru Q3 for the least significant counter, and Q0' thru Q3' for the most significant counter.

#### MC4354/4054

|       | _        | · - |     |     |    | r      |        | UTS    |        |          |       |     |     |     |     |       | -      | DUTPU | TS  |      |     |     |

|-------|----------|-----|-----|-----|----|--------|--------|--------|--------|----------|-------|-----|-----|-----|-----|-------|--------|-------|-----|------|-----|-----|

|       |          | l   | l   | _   |    |        |        | ENS    |        | <u> </u> | UN    | ITS |     |     | TE  | NS    |        |       | UN  | IITS |     | Т   |

| OUNT  | _        | ŪĒ  | SEI | U/D | P  | D3'    | D2'    | D1'    | D0,    | D3       | D2    | D1  | DO  | Q3′ | Q2′ | Q1′   | G0,    | Q3    | Q2  | Q1   | Ω0  | SE  |

| Ŷ     | 0        | 1 1 | 0   | 1 1 |    | 0<br>X | 0<br>X | 0<br>X | 0      | 0        | 0     | 0   | 0   | 0   | 0   | 0     | 0      | 0     | 0   | 0    | 0   |     |

|       | Α        | 1   | ŏ   | 1   | ŏ  | Ιî     | Ιî     | lî     | Ϋ́     | Ι×       | X     | Ι×  | X   | 0   | 0   | 0     | 0      | 0     | 0   | 0    | 0   |     |

| 1 1   | 1        | 1   | 0   | 1   | 0  | 1   1  | ! !    |        |        |          |       | 1 1 |     | ١ŏ  | l ö | ŏ     | Ö      | 0     | 0   | 0    | 0   |     |

| -     | 1        | 0   | 1 1 | 1   | 0  | ] [    |        |        |        | 1 1      |       | l ł | 1 1 | 0   | 0   | 0     | ŏ      | ŏ     | ١ŏ  | lő   | 1 6 |     |

| 1 1   | A        | 0   | i   | 1   | 0  |        |        |        |        | i i      | 1 1   | 1 1 | 1 1 | 0   | 0   | 0     | 0      | 0     | 0   | 0    | 0   |     |

| -   - | 1        | 0   | 1   | i   | ١ŏ |        | l li   |        |        |          | i i   |     | 1 1 | 0   | 0   | 0     | 0      | 0     | 0   | 0    | 0   | 1   |

|       | 1        | 0   | 0   | 1   | 0  |        |        |        |        | 1        |       |     |     | 0   | 6   | 0     | 0      | 0     | 0   | 0    | 0   | ]   |

| 1     | 0        | 0   | 0   | 1   | 0  | 1      |        |        |        |          |       |     |     | 0   | o   | ŏ     | ŏ      | ١ŏ    | lő  | ١٥   | 0   | ĺ   |

| 2     | A        | ŏ   | 0   | 1   | 0  |        |        |        | - 1 1  |          | 1 1 . | İ   | 1   | 0   | 0   | 0     | 0      | 0     | o   | ŏ    | 1   | ļ   |

| 3     | A        | ŏ   | ŏ   | 1   | ŏ  |        |        |        |        |          |       |     |     | 0   | 0   | 0     | 0      | 0     | 0   | 1    | 0   |     |

| 4     | Α        | 0   | 0   | 1   | 0  |        |        |        | - 1 1  |          |       |     |     | 0   | 0   | 0     | 0      | 0     | 0   | 1    | 1   |     |

| 5     | A        | 0   | 0   | 1   | 0  |        |        |        |        | 1.       |       |     |     | ŏ   | ŏ   | l ŏ l | Ö      | 0     | 1 1 | 0    | 0   | ĺ   |

| 6 7   | A        | 0   | 0   | 1   | 0  |        |        |        |        |          |       |     | ' I | 0   | 0   | ō     | ŏ      | lŏ    | l i | 1    | 0   |     |

| é l   | Â        | 6   | 6   | 1   | 0  |        | - 1 1  | - 1 1  | - 1 1  |          |       | - 1 |     | 0   | 0   | 0     | 0      | 0     | 1   | 1    | Ĭ   | i   |

| 9     | A        | ō   | ō   | i   | ŏ  |        |        | -      |        |          | 1 1   |     | 1   | 0   | 0   | 0     | 0      | 1     | 0   | 0    | 0   |     |

| 10    | A        | 0   | 0   | 1   | 0  | [ ]    | -      | 11     | - 1 1  |          |       |     |     | 0   | 0   | 0     | 0<br>1 | 0     | 0   | 0    | 1   | ı   |

| 11    | A        | 0   | 0   | 1   | 0  | 11     | - 1 1  | - 1 1  | -      | - 1 1    |       | li  | ]   | ŏ   | ő   | ŏ     | i      | ŏ     | 0   | 0    | 0   |     |