# RICOH

# **RP510L Series**

# **AEC-Q100 Compliant**

## 4 A Forced PWM Step-down DC/DC Converter with Synchronous Rectifier for Automotive Applications

NO.EC-366-170710

#### OVERVIEW

The RP510L is a step-down DC/DC converter that operates the low input voltage of 2.5 V to 5.5 V. The RP510L being suitable for power supply of SoC (System-on-chip) can be output to 4 A (Max.). And, the foldback type protection, which be released automatically from the overcurrent protection, is user-selectable.

#### **KEY BENEFITS**

- The realization of the high-density mounting by the adoption of a small package DFN3030-12.

- A simplification of the power sequencing by power-good and adjustable soft-start functions.

- Selectable overcurrent protection: Latch type or Foldback type.

#### **KEY SPECIFICATIONS**

- Operating Temperature Range: −40°C ~ 105°C

- Output Voltage Range (1): 0.8 V ~ 3.3 V

- Output Voltage Accuracy<sup>(2)</sup>: ±1% (V<sub>SET</sub> ≥ 1.2V), ±12mV (V<sub>SET</sub> < 1.2V)</li>

- Feedback Voltage Accuracy(3): ±6mV (V<sub>FB</sub> = 0.6 V)

- Standby Current: Typ.0.35 μA (RP510LxxN)

- Typ.0.01  $\mu A$  or less (RP510LxxG/H/J)

- Oscillator Frequency: Typ. 2.3MHz

- Built-in Driver On-resistance (Pch./Nch.): Typ.0.04Ω(V<sub>IN</sub>=3.6V)

- Maximum Duty Cycle: Min. 100%

- Minimum On Time: Typ. 55ns

- Protection Features: UVLO, LX Peak Current Limit, Overcurrent protection (Latch/Foldback type), and Thermal shutdown.

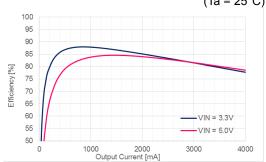

#### **TYPICAL CHARACTERISTICS**

RP510L Series  $V_{OUT} = 1.2V, V_{IN} = 3.3V / 5.0V$

$(Ta = 25^{\circ}C)$

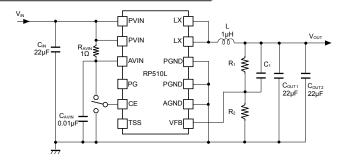

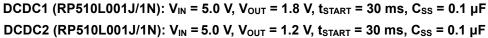

#### TYPICAL APPLICATION CIRCUIT

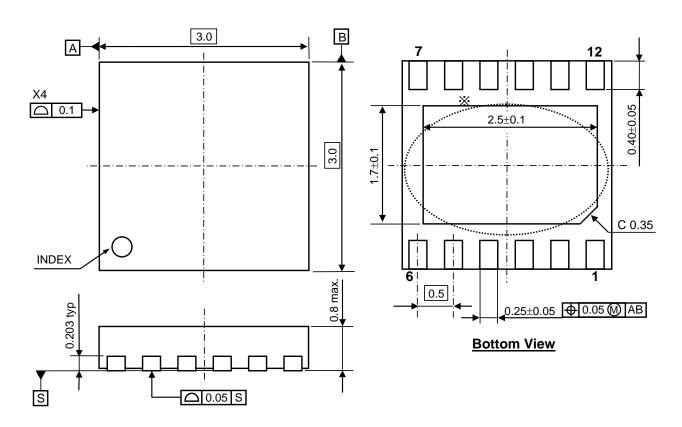

#### **PACKAGE**

DFN3030-12

Size: 3.0mm x 3.0mm, t = 0.8mm (Max.)

RP510L001J/1N/4J/4N (Adjustable Output Voltage Type)

#### **APPLICATIONS**

- SoC power supply for Car Audio Equipment, Car Navigation Systems, and ETC Systems.

- Automotive equipment using Li-ion Battery.

$<sup>^{\</sup>mbox{\scriptsize (1)}}$  Refer to the section SELECTION GUIDE for details of  $V_{\text{SET}}.$

<sup>(2)</sup> Fixed Output Voltage Type

<sup>(3)</sup> Adjustable Output Voltage Type

NO.EC-366-170710

#### **SELECTION GUIDE**

The set output voltage, the output voltage type, the auto-discharge function<sup>(1)</sup>, and the protection type are user-selectable options.

#### **Selection Guide**

| Product Name      | Package    | Quantity per Reel | Pb Free | Halogen Free |

|-------------------|------------|-------------------|---------|--------------|

| RP510Lxx\$\$-TR-# | DFN3030-12 | 3,000 pcs         | Yes     | Yes          |

xx: Specify the set output voltage (VSET).

00: Adjustable Output Voltage (0.8V to 3.3V)

xx: Selectable Fixed Output Voltage (0.8V, 1.0V, 1.1V, 1.2V, 1.3V, 1.5V, 1.8V, 3.0V, 3.3V)

\$\$: Specify the combination of the output voltage type, the auto-discharge function, and the protection type.

| Version | Output Voltage<br>Type (V <sub>SET</sub> ) | Auto-discharge<br>Function | Oscillator<br>Frequency | Protection<br>Type | Product Name |            |

|---------|--------------------------------------------|----------------------------|-------------------------|--------------------|--------------|------------|

| 1G      | Fixed                                      | No                         |                         |                    |              | RP510Lxx1G |

| 1H      | rixeu                                      | Yes                        |                         | Latch              | RP510Lxx1H   |            |

| 1J      | Adjustable                                 | No                         |                         | Laton              | RP510L001J   |            |

| 1N      | Adjustable                                 | Yes                        | 2.3 MHz                 |                    | RP510L001N   |            |

| 4G      | Fixed                                      | No                         | 2.0 111112              |                    | RP510Lxx4G   |            |

| 4H      | rixeu                                      | Yes                        |                         | Foldback           | RP510Lxx4H   |            |

| 4J      | A divistable                               | No                         |                         | Foluback           | RP510L004J   |            |

| 4N      | Adjustable                                 | Yes                        |                         |                    | RP510L004N   |            |

#: Specify the automotive class code.

Operating Temperature Range Guaranteed Specs Temperature Range Screening AEC-Q100

A -40°C to 105°C 25°C High temperature Grade 2

2

<sup>(1)</sup> Auto-discharge function quickly lowers the output voltage to 0 V, when the chip enable signal is switched from the active mode to the standby mode, by releasing the electrical charge accumulated in the external capacitor.

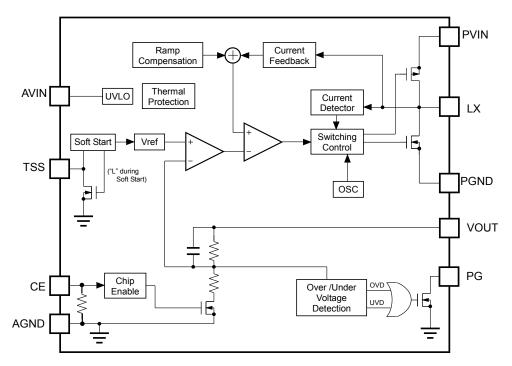

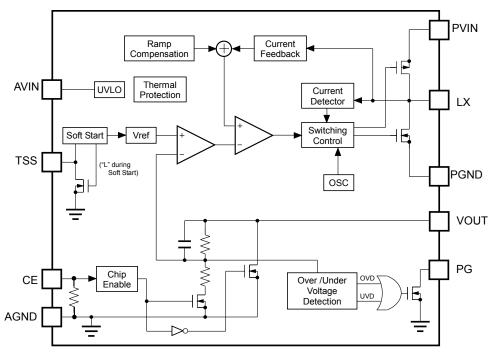

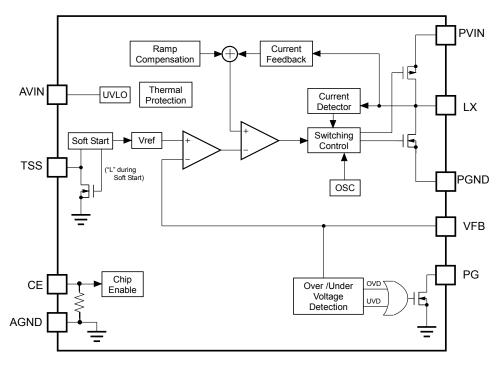

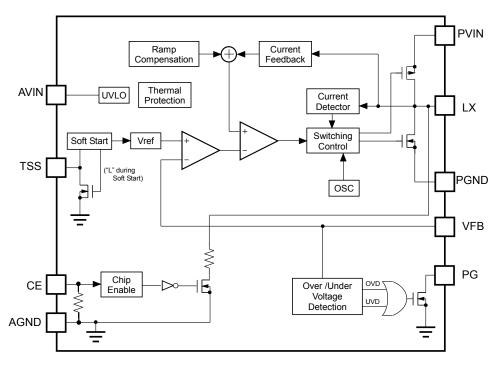

#### **BLOCK DIAGRAM**

# RP510Lxx1G/4G/1H/4H (Fixed Output Voltage Type)

RP510Lxx1G/ 4G Block Diagram

RP510Lxx1H/ 4H Block Diagram

# RP510L001J/4J/1N/4N (Adjustable Output Voltage Type)

RP510L001J/ 4J Block Diagram

RP510L001N/ 4N Block Diagram

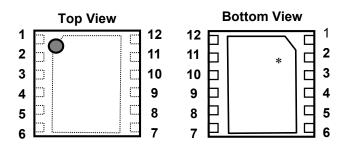

#### PIN DESCRIPTION

**DFN3030-12 Pin Configurations**

**DFN3030-12 Pin Description**

| Pin No. | Pin Name  | Description                               |

|---------|-----------|-------------------------------------------|

| 1       | PVIN (1)  | Input Voltage Pin                         |

| 2       | PVIN (1)  | Input Voltage Pin                         |

| 3       | AVIN (2)  | Input Voltage Pin                         |

| 4       | PG        | Power Good Pin (NMOS Open-drain)          |

| 5       | CE        | Chip Enable Pin (Active "H")              |

| 6       | TSS       | Soft-start Pin                            |

| 7       | VOUT/ VFB | Output Voltage Pin / Feedback Voltage Pin |

| 8       | AGND (3)  | Analog Ground Pin                         |

| 9       | PGND (3)  | Power Ground Pin                          |

| 10      | PGND (3)  | Power Ground Pin                          |

| 11      | LX        | Switching Pin                             |

| 12      | LX        | Switching Pin                             |

<sup>\*</sup> The tab on the bottom of the package must be connected to the ground plane on the board to enhance thermal performance.

$<sup>^{(1)}</sup>$  No.1 pin and No.2 pin must be wired to the  $V_{\text{IN}}$  plane when mounting on boards.

$<sup>^{(2)}</sup>$  No.3 pin must be wired to No.1 and No.2 pins via a low-pass filter (LPF:  $1\Omega$ , 10nF) when mounting on boards.

<sup>(3)</sup> No.8 pin, No.9 pin and No.10 pin must be wired to the GND plane when mounting on boards.

NO.EC-366-170710

#### ABSOLUTE MAXIMUM RATINGS

**Absolute Maximum Ratings**

(AGND = PGND = 0 V)

|                                    |                 |                                   | , -                           | /      |

|------------------------------------|-----------------|-----------------------------------|-------------------------------|--------|

| Symbol                             |                 | Item                              | Rating                        | Unit   |

| V <sub>IN</sub>                    | A/PVIN Pin Volt | age                               | -0.3 to 6.5                   | V      |

| V <sub>LX</sub>                    | LX Pin Voltage  |                                   | -0.3 to V <sub>IN</sub> + 0.3 | V      |

| Vce                                | CE Pin Voltage  |                                   | -0.3 to 6.5                   | V      |

| V <sub>OUT</sub> / V <sub>FB</sub> | Output Voltage  | Output Voltage / Feedback Voltage |                               | V      |

| $V_{PG}$                           | PG Pin Voltage  | PG Pin Voltage                    |                               | V      |

| V <sub>TSS</sub>                   | TSS Pin Voltage | TSS Pin Voltage                   |                               | V      |

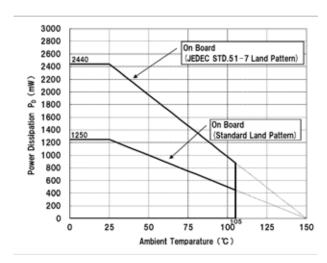

|                                    | Power           | Standard Land Pattern             | 1250                          | 100101 |

| P <sub>D</sub>                     | Dissipation (1) | JEDEC STD. 51-7 Test Land Pattern | 2440                          | - mW   |

| Tj                                 | Junction Tempe  | Junction Temperature Range        |                               | °C     |

| Tstg                               | Storage Tempe   | Storage Temperature Range         |                               | °C     |

|                                    |                 |                                   |                               |        |

#### **ABSOLUTE MAXIMUM RATINGS**

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause the permanent damages and may degrade the life time and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings are not assured.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol   | Item                        | Rating     | Unit |

|----------|-----------------------------|------------|------|

| $V_{IN}$ | Input Voltage               | 2.5 to 5.5 | V    |

| Та       | Operating Temperature Range | -40 to 105 | °C   |

#### **RECOMMENDED OPERATING CONDITIONS**

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if when they are used over such ratings by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

<sup>(1)</sup> Refer to POWER DISSIPATION for detailed information.

#### **ELECTRICAL CHARACTERISTICS**

The specification in  $\square$  is checked and guaranteed by design engineering at  $-40^{\circ}C \le Ta \le 105^{\circ}C$ .

#### RP510Lxx1/4 (-A) Electrical Caharacteristics

$(Ta = 25^{\circ}C)$

| Symbol             | Item                                                 | Co                                                                                         | nditions                       | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------|------|------|------|------|

| ISTANDBY           | Standby Current                                      | V <sub>IN</sub> = 5.5 V,<br>V <sub>CE</sub> = 0 V                                          | RP510LxxxN                     |      | 0.35 | 15.5 | μΑ   |

|                    |                                                      | VCE = U V                                                                                  | RP510LxxxG/H/J                 |      | 0.01 | 7.5  |      |

| Rce                | CE Pin Pull-down Resistance                          |                                                                                            |                                |      | 1    |      | MΩ   |

| I <sub>CEL</sub>   | CE Pin Input Current, Low                            | V <sub>IN</sub> = 5.5 V, \                                                                 | / <sub>CE</sub> = 0 V          | -1   | 0    | 1    | μΑ   |

| ILXLEAKH           | LX Pin Leakage Current, High                         | $V_{IN} = V_{LX} = 5$                                                                      | .5 V, V <sub>CE</sub> = 0 V    | -1   | 0    | 3    | μΑ   |

| ILXLEAKL           | LX Pin Leakage Current, Low                          | V <sub>IN</sub> = 5.5 V, \                                                                 | $V_{CE} = V_{LX} = 0 V$        | -10  | 0    | 1    | μΑ   |

| VCEH               | CE Pin Input Voltage, High                           | V <sub>IN</sub> = 5.5 V                                                                    |                                | 1.0  |      |      | V    |

| V <sub>CEL</sub>   | CE Pin Input Voltage, Low                            | V <sub>IN</sub> = 2.5 V                                                                    |                                |      |      | 0.4  | V    |

| tstart1            | Soft-start Time1                                     | $V_{IN} = V_{CE} = 3.6 \text{ V or } V_{SET} + 1 \text{ V},$<br>TSS = OPEN                 |                                | 75   | 150  | 300  | μs   |

| tstart2            | Soft-start Time2                                     | $V_{IN} = V_{CE} = 3.6 \text{ V or } V_{SET} + 1 \text{ V},$<br>$C_{SS} = 0.1 \mu\text{F}$ |                                | 15   | 30   | 45   | ms   |

| I <sub>LXLIM</sub> | LX Current Limit                                     | V <sub>IN</sub> = V <sub>CE</sub> = 3.6 V or V <sub>SET</sub> + 1 V                        |                                | 5000 | 6500 | 8200 | mA   |

| <b>t</b> PROT      | Protection Delay Time                                | V <sub>IN</sub> = V <sub>CE</sub> = 3.6 V or V <sub>SET</sub> + 1 V                        |                                | 0.5  | 1.5  | 5    | ms   |

| V <sub>UVLO1</sub> | UVLO Threshold Voltage                               | V <sub>IN</sub> = V <sub>CE,</sub> , Falling                                               |                                | 2.1  | 2.2  | 2.3  | V    |

| $V_{\text{UVLO2}}$ | OVEO Threshold Voltage                               | V <sub>IN</sub> = V <sub>CE</sub> , Rising                                                 |                                | 2.2  | 2.3  | 2.4  | V    |

| $T_{TSD}$          | Thermal Shutdown Threshold<br>Temperature, Detection | Tj, Rising                                                                                 |                                |      | 165  |      | °C   |

| T <sub>TSR</sub>   | Thermal Shutdown Threshold<br>Temperature, Release   | Tj, Falling                                                                                |                                |      | 115  |      | °C   |

| R <sub>PGDIS</sub> | PG Pin Low Output<br>ON Resistance                   | $V_{IN} = 3.6 \text{ V},$ $V_{OUT} = 0 \text{ V or } V_{FB} = 0 \text{ V}$                 |                                |      | 45   |      | Ω    |

| f <sub>osc</sub>   | Oscillation Frequency                                | $V_{IN} = V_{CE} = 3$                                                                      | .6 V or V <sub>SET</sub> + 1 V | 2.00 | 2.3  | 2.50 | MHz  |

All test items listed under Electrical Characteristics are done under the pulse load condition (Tj  $\approx$  Ta = 25 $^{\circ}$ C).

#### RP510L NO.EC-366-170710 The specification in \_\_\_\_ is checked and guaranteed by design engineering at −40°C ≤ Ta ≤ 105°C. RP510Lxx1G/1H/4G/4H (-A) [Fixed Output Voltage Type] $(Ta = 25^{\circ}C)$ **Conditions** Max. Unit Symbol Item Min. Тур. x0.99 x1.01 V<sub>SFT</sub> ≥ 1.2 V x0.98 x1.02 $V_{IN} = V_{CE} = 3.6 V$ Vout **Output Voltage** ٧ or $V_{SET}$ + 1 V-0.0120.012 V<sub>SFT</sub> < 1.2 V -0.024 0.024 Supply Current $V_{IN} = V_{CE} = 5.5 V$ 800 Iss μΑ VOUT Pin Current, Low $V_{IN} = 5.5 V$ , $V_{CE} = V_{OUT} = 0 V$ -1 0 1 μΑ IVOUTL $V_{\mathsf{SET}}$ **OVD Voltage** $V_{IN} = 3.6 V$ V $V_{\text{OVD}}$ × 1.2 $V_{\mathsf{SET}}$ $V_{UVD}$ **UVD** Voltage $V_{IN} = 3.6 \text{ V}$ $8.0 \times$ RP510Lxx1G/4G (-A) [Fixed Output Voltage Type, without Auto-discharge function] VOUT Pin Current, High $|V_{IN} = V_{OUT} = 5.5 \text{ V}, V_{CE} = 0 \text{ V}$ 1 μΑ RP510Lxx1H/4H (-A) [Fixed Output Voltage Type, with Auto-discharge function] **VOUT Pin Discharge** $V_{IN} = 2.5 \text{ V}, V_{CE} = 0 \text{ V}, V_{OUT} = 0.5 \text{ V}$ 45 Ω RVOUTDIS NMOS ON-resistance RP510L001J/1N/4J/4N (-A) [Adjustable Output Voltage Type] **Conditions** Symbol Item Min. Max. Unit Typ. 0.594 0.600 0.606 $V_{\mathsf{FB}}$ Feedback Voltage $V_{IN} = V_{CE} = 3.6 V$ V 0.588 0.612 0.600 $V_{IN} = V_{CE} = 5.5 V$ Supply Current 800 μΑ Iss -1 VFB Pin Current, High $V_{IN} = V_{FB} = 5.5 \text{ V}, V_{CE} = 0 \text{ V}$ $I_{VFBH}$ 0 μΑ VFB Pin Current, Low $V_{IN} = 5.5 \text{ V}, V_{CE} = V_{FB} = 0 \text{ V}$ $I_{VFBL}$ -1 0 1 μΑ $V_{\text{OVD}}$ **OVD Voltage** $V_{IN} = 3.6 V$ 0.72 V **UVD** Voltage $V_{IN} = 3.6 \text{ V}$ V $V_{\text{UVD}}$ 0.48 RP510L001N/4N (-A) [Adjustable Output Voltage Type, with Auto-discharge function] LX Pin Discharge

All test items listed under Electrical Characteristics are done under the pulse load condition (Tj ≈ Ta = 25°C).

$V_{IN} = 2.5 \text{ V}, V_{CE} = 0 \text{ V}, L_X = 0.5 \text{ V}$

Ω

**R**LXDIS

NMOS ON-resistance

|                                                                        | RP510L                 |

|------------------------------------------------------------------------|------------------------|

|                                                                        | NO.EC-366-170710       |

| The specification in is checked and guaranteed by design engineering a | at −40°C ≤ Ta ≤ 105°C. |

# RP510Lxx1G/1H/4G/4H (-A) [Fixed Output Voltage Type] Product-specific Electrical Characteristics

|                     | V <sub>OUT</sub> [V] |       |       |                    |       |       |

|---------------------|----------------------|-------|-------|--------------------|-------|-------|

| <b>Product Name</b> | ime Ta = 25°C        |       |       | -40°C ≤ Ta ≤ 105°C |       |       |

|                     | Min.                 | Тур.  | Max.  | Min.               | Тур.  | Max.  |

| RP510x08xx          | 0.788                | 0.800 | 0.812 | 0.776              | 0.800 | 0.824 |

| RP510x10xx          | 0.988                | 1.000 | 1.012 | 0.976              | 1.000 | 1.024 |

| RP510x11xx          | 1.088                | 1.100 | 1.112 | 1.076              | 1.100 | 1.124 |

| RP510x12xx          | 1.188                | 1.200 | 1.212 | 1.176              | 1.200 | 1.224 |

| RP510x13xx          | 1.287                | 1.300 | 1.313 | 1.274              | 1.300 | 1.326 |

| RP510x15xx          | 1.485                | 1.500 | 1.515 | 1.470              | 1.500 | 1.530 |

| RP510x18xx          | 1.782                | 1.800 | 1.818 | 1.764              | 1.800 | 1.836 |

| RP510x30xx          | 2.970                | 3.000 | 3.030 | 2.940              | 3.000 | 3.060 |

| RP510x33xx          | 3.267                | 3.300 | 3.333 | 3.234              | 3.300 | 3.366 |

NO.EC-366-170710

#### THEORY OF OPERATION

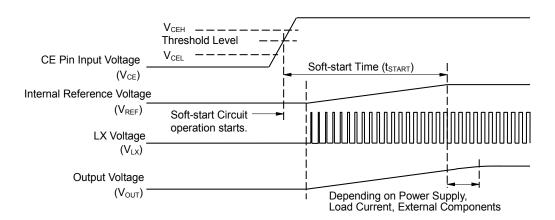

#### Soft-start

#### Starting-up with CE Pin

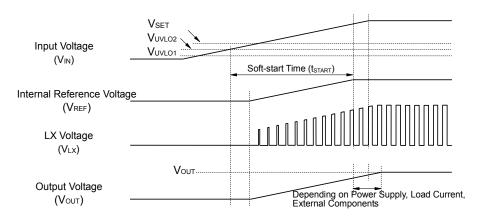

The device starts to operate when the CE pin voltage ( $V_{CE}$ ) exceeds the threshold voltage. The threshold voltage is preset between CE "High" input voltage ( $V_{CEH}$ ) and CE "Low" input voltage ( $V_{CEL}$ ). The soft-start circuit also starts to operate after the device start-up. Then, after a certain period of time, the reference voltage ( $V_{REF}$ ) in the device gradually increases up to the specified value.

Notes: Soft-start time  $(t_{START})^{(1)}$  might not be always equal to an actual turn-on speed of the output voltage. Please note that the turn-on speed could be affected by the power supply capacity, the output current, the inductance value, and the  $C_{OUT}$  value.

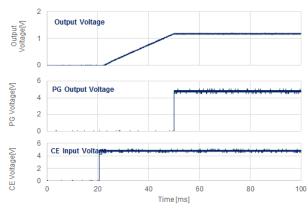

Timing Chart when Starting-up with CE Pin

#### Starting-up with Power Supply

After the power-on, the device starts to operate when  $V_{IN}$  exceeds the UVLO released voltage ( $V_{UVLO2}$ ). The soft-start circuit also starts to operate. Then after a certain period of time,  $V_{REF}$  gradually increases up to the specified value.

Notes: Please note that the turn-on speed of VouT could be affected by the following conditions.

- 1. Power supply capacity and Turn-on speed of V<sub>IN</sub> determined by C<sub>IN</sub>

- 2. Values of Inductor, Capacitor and Output current

10

<sup>(1)</sup> Soft-start time (tstart) indicates the duration until the reference voltage (VREF) reaches the specified voltage after soft-start circuit's activation.

**Timing Chart when Starting-up with Power Supply**

#### **Soft-start Time Adjustment**

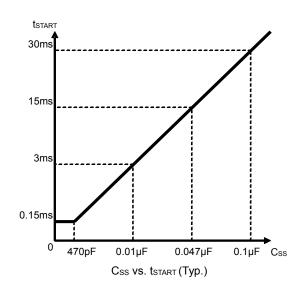

Soft-start time ( $t_{START}$ ) of the RP510L is adjustable by connecting a soft-start time adjustment capacitor ( $C_{SS}$ ) between the TSS pin and GND.  $t_{START}$  can be set from Typ. 0.15 ms as a lower limit. As the figure below shows,  $t_{START}$  is Typ. 30 ms when  $C_{SS}$  is 0.1  $\mu$ F. If not requiring to adjust  $t_{START}$ ,  $t_{START}$  is set to 0.15 ms (Typ.) by making the TSS pin open. The capacitance value for required soft-start time ( $t_{START}$ ) can be calculated by the following equation.

$$C_{SS}[nF] = 3.5 \times t_{START}[ms]$$

Soft-start Time (t<sub>START</sub>) vs. Soft-start Time Adjustment Capacitor (C<sub>SS</sub>)

NO.EC-366-170710

#### **Power Good Function**

If any condition as follows is detected, power good function with using Nch. open drain turns Nch. transistor ON and switches the PG pin to "Low". After the condition is removed, the power good function turns Nch. transistor OFF and switches the PG pin back to "High". The time until the Nch. transistor is turned OFF includes the release delay time of 0.05 ms (Typ.).

- CE = "L" (Shut down)

- UVLO

- Thermal Shutdown

- Over Voltage Detection (Typ.):

```

V_{OUT} > V_{SET} \times 1.2 \text{ V (RP510Lxx1G/1H/4G/4H)} or V_{FB} > 0.72 \text{ V (RP510L001J/1N/4J/4N)}

```

• Under Voltage Detection (Typ.):

```

V<sub>OUT</sub> < V<sub>SET</sub> x 0.8 V (RP510Lxx1G/1H/4G/4H) or V<sub>FB</sub> < 0.48 V (RP510L001J/1N/4J/4N)

```

During the Latch Type Protecting operation

Notes: When using the power good function, the resistance of PG pin ( $R_{PG}$ ) should be between 10 k $\Omega$  to 100 k $\Omega$ . The PG pin must be open or connected to GND if the power good function is not used.

#### **Under Voltage Lockout (UVLO)**

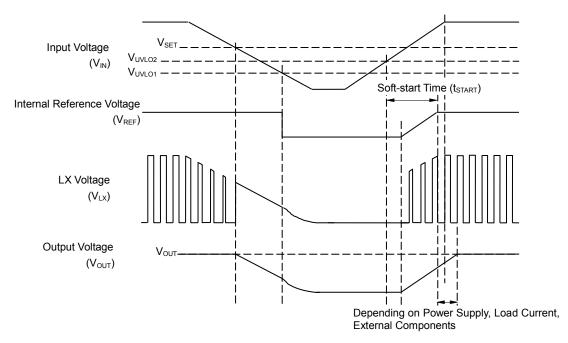

If  $V_{IN}$  becomes lower than  $V_{SET}$ , the step-down DC/DC converter stops the switching operation and ON duty becomes 100%, and then  $V_{OUT}$  gradually drops according to  $V_{IN}$ .

If the  $V_{IN}$  drops more and becomes lower than the UVLO detector threshold ( $V_{UVLO1}$ ), the UVLO circuit starts to operate,  $V_{REF}$  stops, and Pch. and Nch. built-in transistors become the OFF state. As a result,  $V_{OUT}$  drops according to the  $C_{OUT}$  capacitance value and the load.

To restart the operation,  $V_{IN}$  is required to be higher than  $V_{UVLO2}$ . The timing chart below shows the voltage shifts of  $V_{REF}$ ,  $V_{LX}$  and  $V_{OUT}$  in response to variation of the  $V_{IN}$  value.

Notes: Falling edge (operating) and rising edge (releasing) waveforms of  $V_{OUT}$  might be affected by the initial voltage of  $C_{OUT}$  and the output current of  $V_{OUT}$ .

Timing Chart with Variations in Input Voltage (VIN)

#### **Current limit Function**

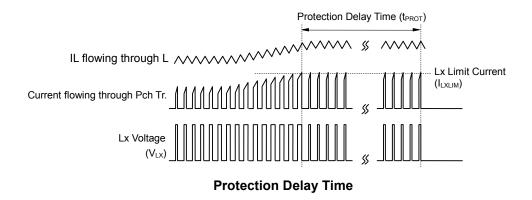

Current limit circuit supervises the inductor current flowing through the Pch. transistor in each switching cycle. If the current exceeds the LX current limit (I<sub>LXLIM</sub>, Typ.6.5A), a Pch. transistor is turned off and the upper limit of the inductor peak current is imposed.

#### Latch Type Protection (RP510Lxx1G/1H, RP510L001J/1N)

Latch type protection circuit latches Pch. and Nch. transistors in the OFF state and stops the operation of the step-down DC/DC converter when the overcurrent status or the output voltage  $(V_{OUT})$ / the feedback voltage  $(V_{FB})$  being dropped to the half of the setting voltage due to shorting continues for the protection delay time  $(t_{PROT})$ . To release the latch type protection circuit, restart the device by inputting "Low" signal to the CE pin or making the supply voltage lower than  $V_{UVLO1}$ .

#### NO.EC-366-170710

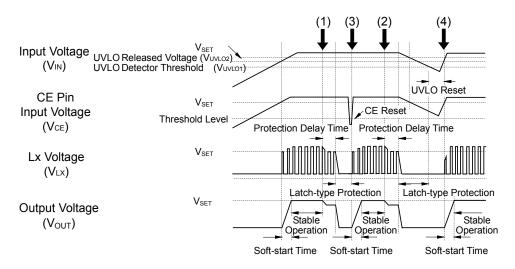

The timing chart below shows the voltage shift of  $V_{CE}$ ,  $V_{LX}$  and  $V_{OUT}$  when the device status is changed by the following orders:  $V_{IN}$  rising  $\rightarrow$  stable operation  $\rightarrow$  high load  $\rightarrow$  CE reset  $\rightarrow$  stable operation  $\rightarrow$   $V_{IN}$  falling  $\rightarrow$   $V_{IN}$  recovering (UVLO reset)  $\rightarrow$  stable operation.

- (1)(2) If the overcurrent flows through the circuit or the device goes into low V<sub>OUT</sub> condition due to short-circuit or other reasons, the latch type protection circuit latches Pch. and Nch. transistors in the OFF state after terror. Then, V<sub>LX</sub> becomes "Low" and V<sub>OUT</sub> turns OFF.

- (3) The latch type protection circuit is released by CE reset, which puts the device into "Low" once with the CE pin and back into "High".

- (4) The latch type protection circuit is released by UVLO reset, which makes  $V_{\text{IN}}$  lower than  $V_{\text{UVLO1}}$ .

**Timing Chart**

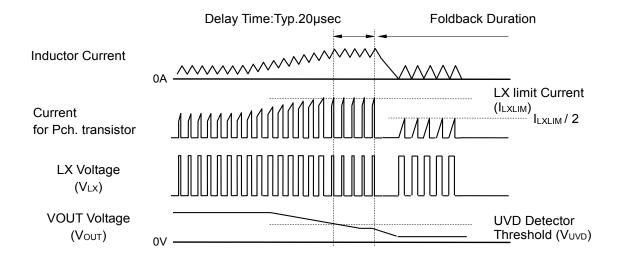

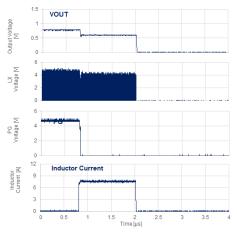

#### Foldback Protection (RP510Lxx4G/4H, RP510L004J/4N)

If the device is in a state where an overcurrent is detected during protection delay time (tprot) or a state where the output voltage (Vout) or the feedback voltage (VFB) becomes lower than UVD detector threshold (VuvD) over about 20 µsec while the overcurrent is caused by an output short-circuit, the foldback protection is enabled. During the foldback protection, the inductor current is set to the upper limit of 1/2 of LX limit current (ILXLIM) and the lower limit of 0mA. During the foldback protection, the device alternately operates the following Pch. and Nch. transistor as follows: the Pch. transistor is turned ON until the inductor current reach the upper limit and the Nch. transistor is turned ON until the inductor current reach 0mA. Therefore, the switching frequency is decreased and the upper limit of the output current (IOUT\_SHORT) during the foldback protection is limited to a current value calculated by the following equation.

IOUT\_SHORT = ILXLIM / 4

When the short-circuit and the overcurrent states are released and the output current (Iout) becomes less than Iout\_Short, the output voltage reaches the set output voltage. Then, the foldback protection is released. And also, the foldback protection is released when the device is reset by inputting CE pin to "Low" or by decreasing the input voltage to less than the UVLO detector threshold (VuVLO1). If the foldback protection occurs by the short-circuit and the overcurrent states when Iout exceed Iout\_Short, the device might not return to a normal state even if their states are released. Release of the foldback protection is required to reduce Iout less than Iout\_Short or reset the device.

Foldback Protection Timing Chart at Low Output Voltage

Note: The current limit function and the overcurrent limit protection of the latch / foldback type, as described above, becomes possible to provide a high degree of safety to the device, not to secure reliability. And,  $I_{LXLIM}$  and  $t_{PROT}$  could be easily affected by self-heating or ambient environment. If the  $V_{IN}$  drops dramatically or becomes unstable due to short-circuit, protection operation and  $t_{PROT}$  could be affected.

#### **Reverse Current Limit Function**

The reverse current limit function supervises the current on the Nch. transistor in every switching. When an overcurrent more than the threshold current (Typ. -2.0A) occur, the Nch. transistor is turned off to limit a lower of the inductor current. On the heavy-to-light load transient, the reverse current limit function may occur by the overcurrent. If this limit function occur, the reduction of the output voltage overshoot by reverse current will be limited.

#### **APPLICATION INFORMATION**

#### **Typical Application Circuit**

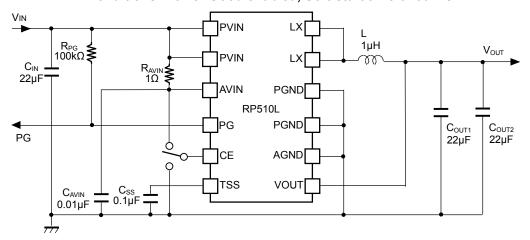

Conditions: Power Good enabled, Soft-start time of 30 ms

RP510Lxx1G/1H/4G/4H (Fixed Output Voltage Type)

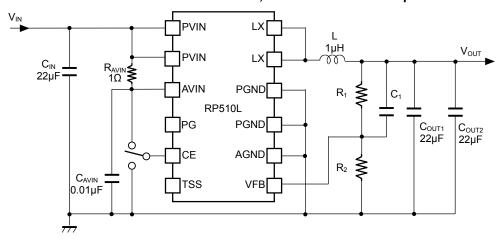

#### Conditions: Power Good disabled, Soft-start time of 150 $\mu$ s

RP510L001J/1N/4J/4N (Adjustable Output Voltage Type)

#### **Recommended External Components**

| Symbol | Descriptions                                             |  |  |

|--------|----------------------------------------------------------|--|--|

| Cin    | 22 μF, Ceramic Capacitor, CGA5L1X7R0J226M160AC (TDK)     |  |  |

| Соит   | 22 μF x 2, Ceramic Capacitor, CGA5L1X7R0J226M160AC (TDK) |  |  |

| L      | 1.0 μH, Inductor, CLF7045NIT-1R0N-D (TDK)                |  |  |

#### Cautions in selecting external components

- Choose a low ESR ceramic capacitor. The input capacitor (C<sub>IN</sub>) between PVIN and PGND should be more than 22 μF, and the output capacitor (C<sub>OUT</sub>) should be used by two or more parallel connection with ceramic capacitor of 22 μF.

- The phase compensation of this device is designed according to the C<sub>OUT</sub> and L values. The inductance value of an inductor should be 1.0µH to gain stability.

- Choose an inductor that has small DC resistance, has enough permissible current and is hard to cause magnetic saturation. If the inductance value of the inductor becomes extremely small under the load conditions, the peak current of LX may increase along with the load current. As a result, the overcurrent protection circuit may start to operate when the peak current of LX reaches to LX limit current. Therefore, choose an inductor with consideration for the value of ILXMAX. See the following page of Calculation Conditions of LX Pin Maximum Output Current (ILXMAX).

- As for the adjustable output voltage type (RP510L001J/1N/4J/4N), the output voltage (V<sub>OUT</sub>) is adjustable by changing the resistance values of R1 and R2.

$$V_{SET}^{(1)} = V_{FB} \times (R1 + R2) / R2$$

(0.8 V ≤  $V_{SET} \le 3.3 \text{ V}$ )

If R2 are too large, the impedance of  $V_{FB}$  also become large, as a result, the device could be easily affected by noise. For this reason, R2 should be  $30k\Omega$  or less. If the operation becomes unstable dues to the high impedances, the impedances should be decreased.

C1 can be calculated by the following equation. Please use the value close to the calculation result.

$$C1 = 5 \times 10^{-7} / R2 [F]$$

The recommended component values for R1, R2, and C1 are as follows.

Set Output Voltage (V<sub>SET</sub>) vs. Resistor (R1, R2), Capacitor (C1)

| Set Output Voltage   | Resistor [kΩ] |    | Capacitor [pF] |

|----------------------|---------------|----|----------------|

| V <sub>SET</sub> [V] | R1            | R2 | C1             |

| 0.8                  | 10            | 30 | 16             |

| 1.2                  | 20            | 20 | 25             |

| 1.8                  | 40            | 20 | 25             |

| 2.5                  | 95            | 30 | 16             |

| 3.3                  | 90            | 20 | 25             |

<sup>(1)</sup> V<sub>SET</sub>: set output voltage

NO.EC-366-170710

#### Calculation Conditions of LX Pin Maximum Output Current (ILXMAX)

The following equations explain the relationship to determine  $I_{LXMAX}$  at the ideal operation of the device in continuous mode.

IRP: Ripple Current P-P value

Ronp / Ronn: ON resistance of Pch. / Nch. transistor

$R_L$ : DC resistance of the inductor

First, when the Pch. transistor is "ON", Equation 1 is satisfied.

$V_{IN} = V_{OUT} + (R_{ONP} + R_L) \times I_{OUT} + L \times I_{RP} / t_{ON} \cdots$  Equation 1

Second, when the Pch. transistor is "OFF" (the Nch. transistor is "ON"), Equation 2 is satisfied.

$L \times I_{RP} \ / \ t_{OFF} = R_{ONN} \times I_{OUT} + V_{OUT} + R_L \times I_{OUT} \cdots Equation \ 2$

Put Equation 2 into Equation 1 to solve ON duty of the Pch. transistor (DoN = toN / (toff + toN)):

$D_{ON} = (V_{OUT} + R_{ONN} \times I_{OUT} + R_L \times I_{OUT}) / (V_{IN} + R_{ONN} \times I_{OUT} - R_{ONP} \times I_{OUT}) \cdots Equation 3$

Ripple Current is described as follows:

$I_{RP} = (V_{IN} - V_{OUT} - R_{ONP} \times I_{OUT} - R_{L} \times I_{OUT}) \times D_{ON} / f_{OSC} / L \cdots Equation 4$

Peak current that flows through L, and Pch.and Nch. transistors is described as follows:

I<sub>LXMAX</sub> = I<sub>OUT</sub> + I<sub>RP</sub> / 2 ····· Equation 5

#### **Example applications: Control sequencer**

Sequencer control can establishes by using the soft-start time adjustment and the power good functions of the RP510L. The following figure indicates an application circuit example with using two RP510L (DCDC1 and DCDC2).

DCDC1 starts up prior to DCDC2. After DCDC1 reaches the output voltage of typ.1.44V (V<sub>SET</sub> x 0.8), CE pin of DCDC2 receives "High" signal from PG pin of DCDC1, and the DCDC2's soft-start starts.

**Sequence Control Application Circuit Example**

NO.EC-366-170710

#### **TECHNICAL NOTES**

The performance of a power source circuit using this device is highly dependent on a peripheral circuit. A peripheral component or the device mounted on PCB should not exceed a rated voltage, a rated current or a rated power. When designing a peripheral circuit, please be fully aware of the following points.

- AGND and PGND must be wired to the GND plane when mounting on boards.

- AVIN must be connected to between an input capacitor (C<sub>IN</sub>) and PVIN via a low-pass filter (Recommended LPF: 1Ω, 10nF). Place a capacitor between AVIN and AGND as close as possible to the IC.

- Set the external components as close as possible to the IC and minimize the wiring between the components and the IC. Especially, place C<sub>IN</sub> as close as possible to PVIN pin and PGND.

- Use the VIN and the GND lines as wide and short as possible to make low impedance, since noise pickup or unstable operation occurs when their impedance are too high.

- The VIN line, the GND line, the V<sub>OUT</sub> line, an inductor, and L<sub>x</sub> should make special considerations for the large switching current flows.

- For the feedback of output voltage, the wiring to the VOUT pin (RP510Lxxx1G/1H/4G/4H) or to a resistor for setting output voltage (R1) (RP510L001J/1N/4J/4N) must be taken from the connection with the output capacitor, and also the wiring should be separated from the wiring between the output capacitor and Load.

- Overcurrent protection circuit and latch / foldback type protection circuit may be affected by self-heating or power dissipation environment.

- When not using the soft-start time adjustment, always make TSS pin open.

- When not using the power good function, PG pin should be Open or connected to GND.

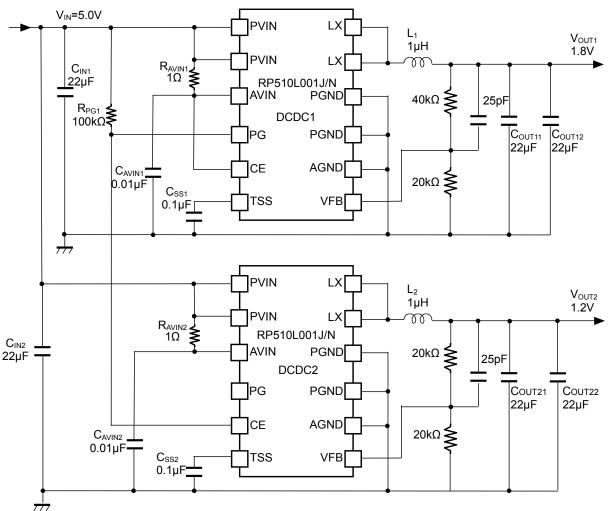

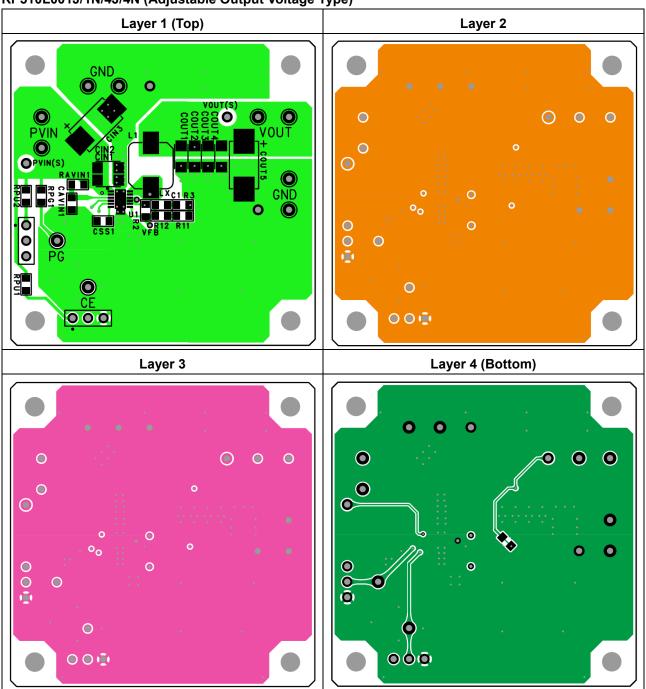

#### **PCB Layout Example**

#### RP510L001J/1N/4J/4N (Adjustable Output Voltage Type)

- \* The LPF between PVIN and AVIN is recommended to place to the layer 1 (Top) is recommended.

- \*\* R11 and R12 are arranged as a substitute for R1 so that two resistors can be connected in series.

## RP510Lxx1G/1H/4G/4H (Fixed Output Voltage Type)

\* LPF between PVIN and AVIN is recommended to place to Layer 1 (Top) is recommended.

### TYPICAL CHARACTERISTICS

Typical Characteristics are intended to be used as reference data, they are not guaranteed.

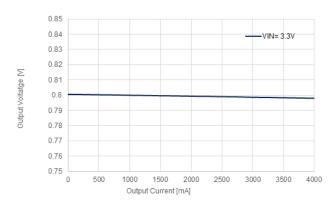

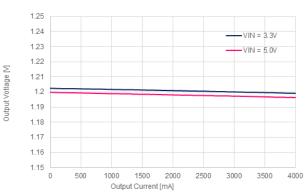

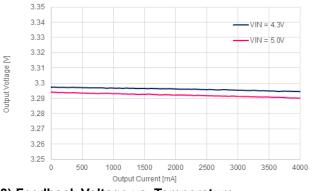

#### 1) Output Voltage vs. Output Current

$V_{OUT} = 0.8 V$

$V_{OUT} = 1.2 V$

#### $V_{OUT} = 3.3 V$

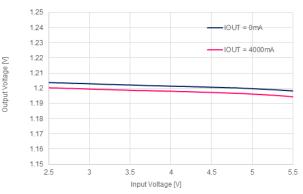

#### 2) Output Voltage vs. Input Voltage

$V_{OUT} = 1.2 V$

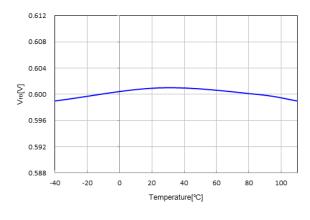

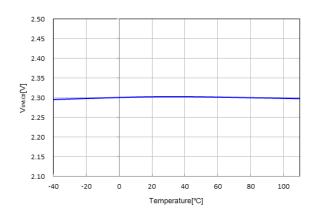

# 3) Feedback Voltage vs. Temperature

RP510L001J/1N/4J/4N

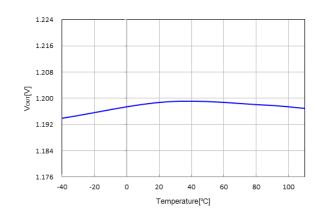

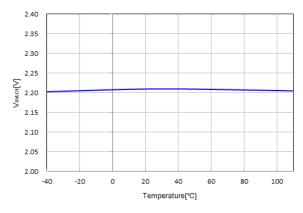

#### 4) Output Voltage vs. Temperature

RP510Lxx1G/1H/4G/4H

$V_{OUT} = 1.2 V$

#### NO.EC-366-170710

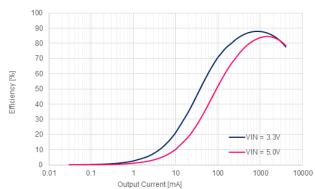

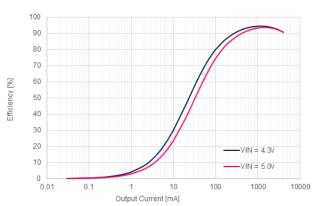

#### 5) Efficiency vs. Output Current

$V_{OUT} = 0.8 V$

$$V_{OUT}$$

= 1.2  $V$

#### $V_{OUT} = 3.3 V$

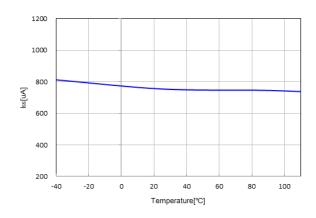

6) Current Consumption vs. Temperature  $V_{\text{IN}}$  = 5.5 V

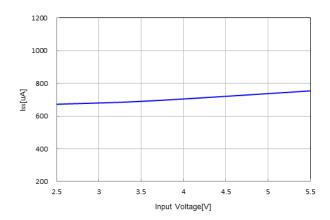

## 7) Current Consumption vs. Input Voltage

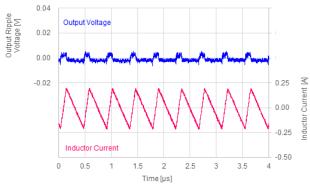

#### 8) Output Voltage Waveform

$$V_{OUT} = 1.2 \text{ V}, I_{OUT} = 0 \text{mA}$$

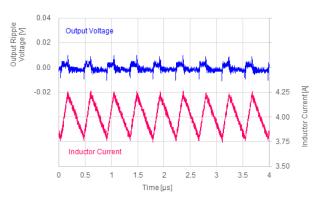

#### $V_{OUT}$ = 1.2 V, $I_{OUT}$ = 4000mA

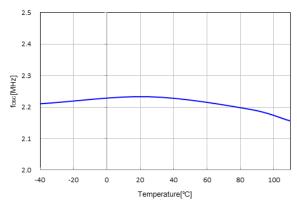

#### 9) Oscillation Frequency vs. Temperature

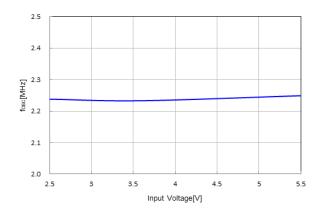

## 10) Oscillation Frequency vs. Input Voltage

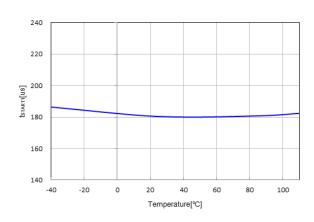

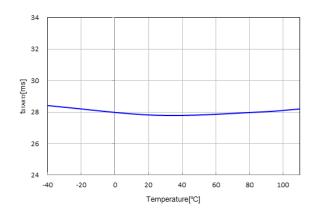

#### 11) Soft-start time vs. Temperature

Css = open

$C_{SS} = 0.1 \mu F$

NO.EC-366-170710

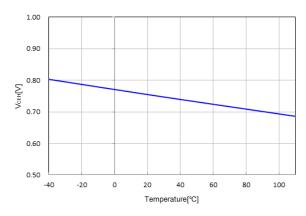

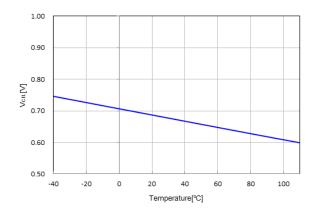

#### 12) UVLO vs. Temperature

UVLO detection voltage

#### UVLO detection voltage

#### 13) CE Input Voltage vs. Temperature

CE "H" input voltage

$V_{IN} = 5.5 \text{ V}$

CE "L" input voltage  $V_{IN} = 2.5 \text{ V}$

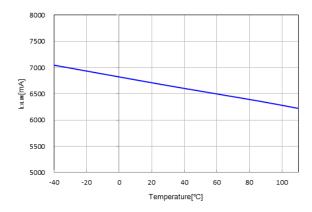

#### 14) LX Limit Current vs. Temperature

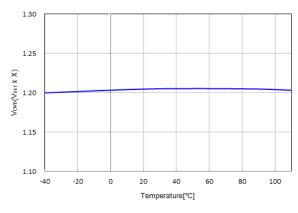

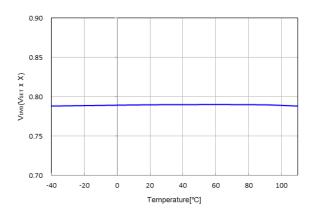

#### 15) PG Detection Voltage vs. Temperature

Over Voltage Detection

#### **Under Voltage Detection**

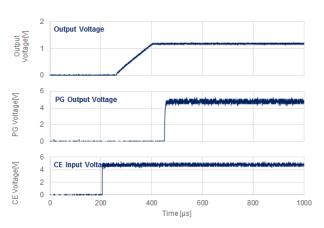

#### 16) Soft-start Waveform

$V_{OUT}$  = 1.2 V,  $C_{SS}$  = open

#### $V_{OUT} = 1.2 \text{ V}, C_{SS} = 0.1 \mu F$

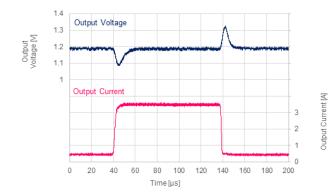

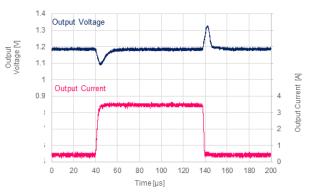

### 17) Load Transient Response

$V_{IN}$  = 3.3 V,  $V_{OUT}$  = 1.2 V  $I_{OUT}$  = 0.5 A  $\leftrightarrow$  3.5 A

$V_{IN} = 5.0 \text{ V}, V_{OUT} = 1.2 \text{ V}$  $I_{OUT} = 0.5 \text{ A} \leftrightarrow 3.5 \text{ A}$

NO.EC-366-170710

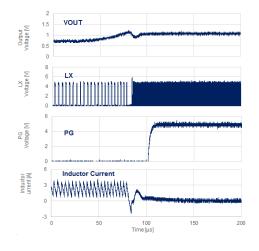

# 18) Output Short-circuit Waveform RP510Lxx1G/1H/1J/1N (Latch Type) $V_{\text{IN}}$ = 5.0 V, $V_{\text{OUT}}$ = 0.8 V

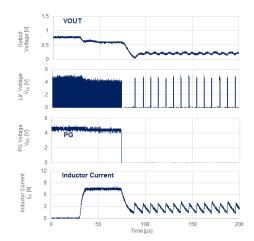

**19) Output Short-circuit Release Waveform** RP510Lxx4G/4H/4J/4N (Foldback Type) V<sub>IN</sub> = 5.0 V, V<sub>OUT</sub> = 0.8 V

# RP510Lxx4G/4H/4J/4N (Foldback Type) $V_{IN} = 5.0 \text{ V}, V_{OUT} = 0.8 \text{ V}$

Ver. A

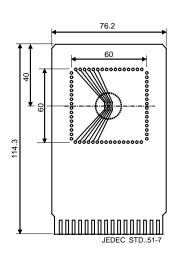

The power dissipation of the package is dependent on PCB material, layout, and environmental conditions. The following conditions are used in this measurement.

#### **Measurement Conditions**

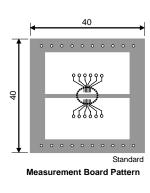

|                         | Standard Test Land Pattern | JEDEC STD.51-7 Test Land Pattern           |  |

|-------------------------|----------------------------|--------------------------------------------|--|

| Environment             | Mounting on Board          | Mounting on Board                          |  |

| Livilorinent            | (Wind Velocity=0m/s)       | (Wind Velocity = 0 m/s)                    |  |

| Board Material          | Glass cloth epoxy plastic  | Glass Cloth Epoxy Plastic                  |  |

| Board Material          | (Double sided)             | (Four-Layer Board)                         |  |

| <b>Board Dimensions</b> | 40mm x 40mm x 1.6mm        | 76.2 mm × 114.3 mm × 1.6 mm                |  |

|                         |                            | Outer Layers (First and Fourth Layers):    |  |

| Connor Potio            | Top side: Approx. 50%,     | Less than 10% of 60 mm Square              |  |

| Copper Ratio            | Back side: Approx. 50%     | Inner Layers (Second and Third Layers):    |  |

|                         |                            | 100% of 74.2 mm Square                     |  |

|                         |                            | f 0.85 mm x 64 pcs                         |  |

| Through holos           | f 0.54mm v 22noo           | * The land pattern of Tab (Heat spreader), |  |

| Through-holes           | f 0.54mm x 32pcs           | the inner layers and the backside pattern  |  |

|                         |                            | are connected by 0.3mm through-hole.       |  |

#### **Measurement Result**

$(Ta = 25^{\circ}C, Tjmax = 150^{\circ}C)$

|                    | Standard Test Land Pattern                       | JEDEC STD.51-7 Test Land Pattern                        |

|--------------------|--------------------------------------------------|---------------------------------------------------------|

| Power Dissipation  | 1250mW                                           | 2440 mW                                                 |

| Thermal Resistance | qja = (150-25°C)/1.25W = 100°C/W<br>qjc = 18°C/W | qja = (150 - 25°C) / 2.44 W = 51.2°C/W<br>qjc = 5.9°C/W |

i

()

IC Mount Area (mm)

**Power Dissipation vs. Ambient Temperature**

**Measurement Board Pattern**

**RICOH**

Ver. A

DFN3030-12 Package Dimensions (Unit: mm)

i

$<sup>\</sup>ast$  The tab on the bottom of the package is substrate level (GND). It is recommended that the tab be connected to the ground plane on the board, or otherwise be left floating.

- 1. The products and the product specifications described in this document are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to Ricoh sales representatives for the latest information thereon.

- 2. The materials in this document may not be copied or otherwise reproduced in whole or in part without prior written consent of Ricoh.

- 3. Please be sure to take any necessary formalities under relevant laws or regulations before exporting or otherwise taking out of your country the products or the technical information described herein.

- 4. The technical information described in this document shows typical characteristics of and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under Ricoh's or any third party's intellectual property rights or any other rights.

- 5. The products in this document are designed for automotive applications. However, when using the products for automotive applications, please make sure to contact Ricoh sales representative in advance due to confirming the

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order to prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. Anti-radiation design is not implemented in the products described in this document.

- 8. The X-ray exposure can influence functions and characteristics of the products. Confirm the product functions and characteristics in the evaluation stage.

- 9. WLCSP products should be used in light shielded environments. The light exposure can influence functions and characteristics of the products under operation or storage.

- 10. There can be variation in the marking when different AOI (Automated Optical Inspection) equipment is used. In the case of recognizing the marking characteristic with AOI, please contact Ricoh sales or our distributor before attempting to use AOI.

- 11. Please contact Ricoh sales representatives should you have any questions or comments concerning the products or the technical information.

Halogen Free

Ricoh is committed to reducing the environmental loading materials in electrical devices with a view to contributing to the protection of human health and the environment.

Ricoh has been providing RoHS compliant products since April 1, 2006 and Halogen-free products since April 1, 2012.

# RICOH RICOH ELECTRONIC DEVICES CO., LTD.

#### http://www.e-devices.ricoh.co.jp/en/

#### Sales & Support Offices

RICOH ELECTRONIC DEVICES CO., LTD. Higashi-Shinagawa Office (International Sales) 3-32-3, Higashi-Shinagawa, Shinagawa-ku, Tokyo 140-8655, Japan Phone: +81-3-5479-2857 Fax: +81-3-5479-0502

RICOH EUROPE (NETHERLANDS) B.V.

Semiconductor Support Centre Prof. W.H. Keesomlaan 1, 1183 DJ Amstelveen, The Netherlands

Phone: +31-20-5474-309

RICOH INTERNATIONAL B.V. - German Branch Semiconductor Sales and Support Centre Oberrather Strasse 6, 40472 Düsseldorf, Germany Phone: +49-211-6546-0

RICOH ELECTRONIC DEVICES KOREA CO., LTD.

Phone: +82-2-2135-5700 Fax: +82-2-2051-5713

RICOH ELECTRONIC DEVICES SHANGHAI CO., LTD.

Room 403, No.2 Building, No.690 Bibo Road, Pu Dong New District, Shanghai 201203

Phone: +86-21-5027-3200 Fax: +86-21-5027-3299

RICOH ELECTRONIC DEVICES CO., LTD.

Taipei office

Room 109, 10F-1, No.51, Hengyang Rd., Taipei City, Taiwan (R.O.C.)

Phone: +886-2-2313-1621/1622 Fax: +886-2-2313-1623

| , |  |

|---|--|

|   |  |

|   |  |

|   |  |