### **General Description**

The single MAX4091, dual MAX4092, and guad MAX4094 operational amplifiers combine excellent DC accuracy with Rail-to-Rail® operation at the input and output. Since the common-mode voltage extends from VCC to VEE, the devices can operate from either a single supply (2.7V to 6V) or split supplies (±1.35V to ±3V). Each op amp requires less than 130µA of supply current. Even with this low current, the op amps are capable of driving a  $1k\Omega$  load, and the input-referred voltage noise is only 12nV/\(\sqrt{Hz}\). In addition, these op amps can drive loads in excess of 2000pF.

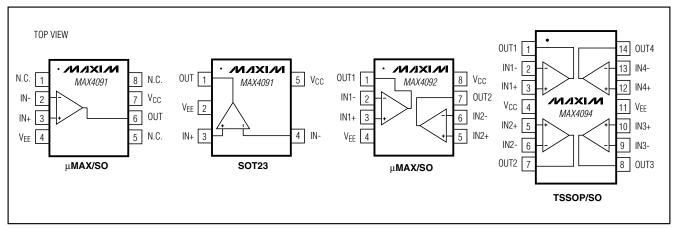

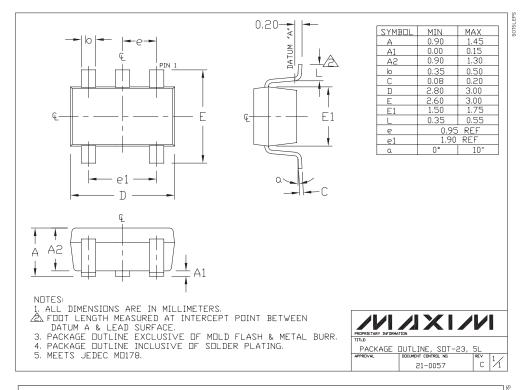

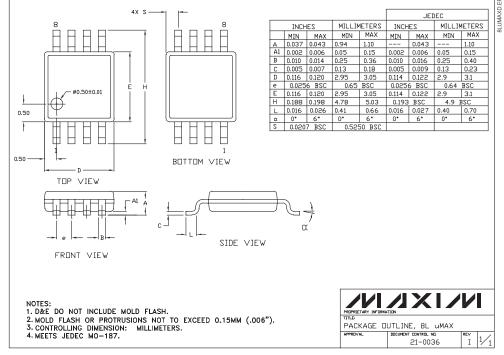

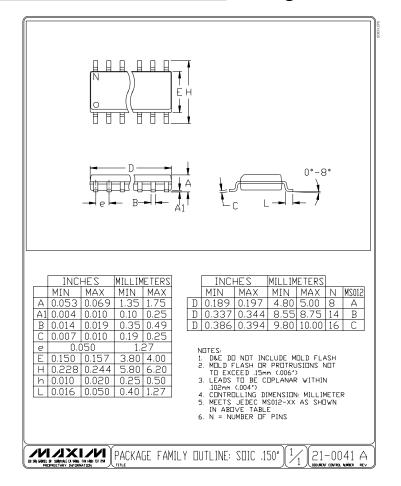

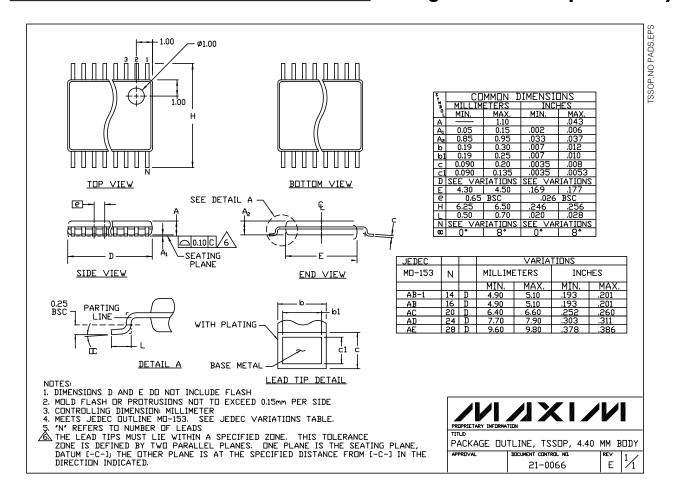

The precision performance of the MAX4091/MAX4092/ MAX4094 combined with their wide input and output dynamic range, low-voltage, single-supply operation, and very low supply current, make them an ideal choice for battery-operated equipment, industrial, and data acquisition and control applications. In addition, the MAX4091 is available in space-saving 5-pin SOT23, 8-pin µMAX, and 8-pin SO packages. The MAX4092 is available in 8-pin µMAX and SO packages, and the MAX4094 is available in 14-pin TSSOP and 14-pin SO packages.

### **Applications**

Portable Equipment **Battery-Powered Instruments** Data Acquisition and Control Low-Voltage Signal Conditioning

#### Features

- ♦ Low-Voltage, Single-Supply Operation (2.7V to 6V)

- **♦** Beyond-the-Rails<sup>™</sup> Inputs

- ♦ No Phase Reversal for Overdriven Inputs

- ♦ 30µV Offset Voltage

- ♦ Rail-to-Rail Output Swing with 1kΩ Load

- ♦ Unity-Gain Stable with 2000pF Load

- ♦ 165µA (max) Quiescent Current Per Op Amp

- ♦ 500kHz Gain-Bandwidth Product

- ♦ High Voltage Gain (115dB)

- ♦ High Common-Mode Rejection Ratio (90dB) and Power-Supply Rejection Ratio (100dB)

- **♦** Temperature Range (-40°C to +125°C)

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX4091AUK-T | -40°C to +125°C | 5 SOT23-5   |

| MAX4091ASA   | -40°C to +125°C | 8 SO        |

| MAX4091AUA   | -40°C to +125°C | 8 μMAX      |

| MAX4092ASA   | -40°C to +125°C | 8 SO        |

| MAX4092AUA   | -40°C to +125°C | 8 µMAX      |

| MAX4094AUD   | -40°C to +125°C | 14 TSSOP    |

| MAX4094ASD   | -40°C to +125°C | 14 SO       |

# Pin Configurations/Functional Diagrams

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd. Beyond-the-Rails is a trademark of Maxim Integrated Products, Inc.

MIXIM

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )7V | 8-Pin SO (derate 5   |

|--------------------------------------------------------|----------------------|

| Common-Mode Input Voltage(VCC + 0.3V) to (VEE - 0.3V)  | 8-Pin µMAX (derat    |

| Differential Input Voltage±(VCC - VEE)                 | 14-Pin SO (derate    |

| Input Current (IN+, IN-)±10mA                          | 14-Pin TSSOP (der    |

| Output Short-Circuit Duration                          | Operating Temperatu  |

| OUT shorted to GND or V <sub>CC</sub> Continuous       | Storage Temperature  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)  | Junction Temperature |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571mW         | Lead Temperature (so |

| 471mW  |

|--------|

| 330mW  |

| 667mW  |

| 727mW  |

| +125°C |

| +150°C |

| +150°C |

| +300°C |

|        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VCC = 2.7V to 6V, VEE = GND, VCM = 0, VOUT = VCC/2, TA = +25°C.)

| PARAMETER                       | SYMBOL          | CONDITION                                            | IS                 | MIN        | TYP  | MAX             | UNITS   |

|---------------------------------|-----------------|------------------------------------------------------|--------------------|------------|------|-----------------|---------|

| DC CHARACTERISTICS              |                 |                                                      |                    |            |      |                 |         |

| Supply Voltage Range            | Vcc             | Inferred from PSRR test                              |                    | 2.7        |      | 6.0             | V       |

| Supply Current                  | lcc             | $V_{CM} = V_{CC}/2$ $V_{CC} = 2$ $V_{CC} = 5$        | 7V                 |            | 115  | 165             | μΑ      |

| очры очнен                      | 100             | $V_{CM} = V_{CC/2}$ $V_{CC} = 5$                     | /                  |            | 130  | 185             | μΛ      |

| Input Offset Voltage            | Vos             | V <sub>CM</sub> = V <sub>EE</sub> to V <sub>CC</sub> |                    |            | 0.03 | 1.4             | mV      |

| Input Bias Current              | lΒ              | V <sub>CM</sub> = V <sub>EE</sub> to V <sub>CC</sub> |                    |            | 20   | 180             | nA      |

| Input Offset Current            | los             | V <sub>CM</sub> = V <sub>EE</sub> to V <sub>CC</sub> |                    |            | 0.2  | 7               | nA      |

| Input Common-Mode Range         | V <sub>CM</sub> | Inferred from CMRR test                              |                    | VEE - 0.05 |      | $V_{CC} + 0.05$ | V       |

| Common-Mode Rejection<br>Ratio  | CMRR            | $(V_{EE} - 0.05V) \le V_{CM} \le (V_{CM})$           | CC + 0.05V)        | 71         | 90   |                 | dB      |

| Power-Supply Rejection<br>Ratio | PSRR            | 2.7V ≤ V <sub>CC</sub> ≤ 6V                          |                    | 86         | 100  |                 | dB      |

|                                 |                 | $V_{CC} = 2.7V, R_L = 100k\Omega$                    | Sourcing           | 83         | 105  |                 |         |

|                                 |                 | $0.25V \le V_{OUT} \le 2.45V$                        | Sinking            | 81         | 105  |                 |         |

|                                 |                 | $V_{CC} = 2.7V$ , $R_L = 1k\Omega$                   | Sourcing           | 91         | 105  |                 |         |

| Large-Signal Voltage Gain       | ٨               | $0.5V \le V_{OUT} \le 2.2V$                          | Sinking            | 78         | 90   |                 | ٩D      |

| (Note 1)                        | Avol            | $V_{CC} = 5.0V$ , $R_L = 100k\Omega$                 | Sourcing           | 87         | 115  |                 | dB      |

|                                 |                 | $0.25V \le V_{OUT} \le 4.75V$                        | Sinking            | 83         | 115  |                 |         |

|                                 |                 | $V_{CC} = 5.0V$ , $R_L = 1k\Omega$                   | Sourcing           | 97         | 110  |                 |         |

|                                 |                 | $0.5V \le V_{OUT} \le 4.5V$                          | Sinking            | 84         | 100  |                 |         |

| Output Voltage Swing High       | Vari            | IV <sub>CC</sub> - V <sub>OUT</sub> I                | $R_L = 100k\Omega$ |            | 15   | 69              | m\/     |

| (Note 1)                        | VoH             | IACC - AOOLI                                         | $R_L = 1k\Omega$   |            | 130  | 210             | mV      |

| Output Voltage Swing Low        | Va              |                                                      | $R_L = 100k\Omega$ |            | 15   | 70              | m\/     |

| (Note 1)                        | V <sub>OL</sub> | IV <sub>OUT</sub> - V <sub>EE</sub> I                | $R_L = 1k\Omega$   |            | 80   | 220             | mV      |

| AC CHARACTERISTICS              |                 |                                                      |                    |            |      |                 |         |

| Gain-Bandwidth Product          | GBWP            | $R_L = 100k\Omega$ , $C_L = 100pF$                   |                    |            | 500  |                 | kHz     |

| Phase Margin                    | φм              | $R_L = 100k\Omega$ , $C_L = 100pF$                   |                    |            | 60   |                 | degrees |

| Gain Margin                     |                 | $R_L = 100k\Omega$ , $C_L = 100pF$                   |                    |            | 10   |                 | dB      |

| Slew Rate                       | SR              | $R_L = 100k\Omega$ , $C_L = 15pF$                    |                    |            | 0.20 |                 | V/µs    |

\_ /VI/IXI/VI

### **ELECTRICAL CHARACTERISTICS (continued)**

(VCC = 2.7V to 6V, VEE = GND, VCM = 0, VOUT = VCC/2, TA = +25°C.)

| PARAMETER                               | SYMBOL  | CONDITIONS                                                                                  | MIN TYP MAX | UNITS  |

|-----------------------------------------|---------|---------------------------------------------------------------------------------------------|-------------|--------|

| Input-Noise Voltage Density             | eN      | f = 10kHz                                                                                   | 12          | nV/√Hz |

| Input-Noise Current Density             |         | f = 10kHz                                                                                   | 1.5         | pA/√Hz |

| Noise Voltage<br>(0.1Hz to 10Hz)        |         |                                                                                             | 16          | μVRMS  |

| Total Harmonic Distortion<br>Plus Noise | THD + N | $f = 1kHz$ , $R_L = 10k\Omega$ , $C_L = 15pF$ , $A_V = 1$ , $V_{OUT} = 2V_{P-P}$            | 0.003       | %      |

| Capacitive-Load Stability               | CLOAD   | A <sub>V</sub> = 1                                                                          | 2000        | pF     |

| Settling Time                           | ts      | To 0.1%, 2V step                                                                            | 12          | μs     |

| Power-On Time                           | ton     | V <sub>CC</sub> = 0 to 3V step, V <sub>IN</sub> = V <sub>CC</sub> /2,<br>A <sub>V</sub> = 1 | 2           | μs     |

| Op-Amp Isolation                        |         | f = 1kHz (MAX4092/MAX4094)                                                                  | 125         | dB     |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.7V \text{ to 6V}, V_{EE} = GND, V_{CM} = 0, V_{OUT} = V_{CC}/2, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values specified at } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                    | SYMBOL               | CONDITION                                                      | IS                            | MIN                    | TYP | MAX        | UNITS |

|------------------------------|----------------------|----------------------------------------------------------------|-------------------------------|------------------------|-----|------------|-------|

| DC CHARACTERISTICS           |                      |                                                                |                               |                        |     |            |       |

| Supply Voltage Range         | Vcc                  | Inferred from PSRR test                                        |                               | 2.7                    |     | 6.0        | V     |

| Supply Current               | Icc                  | V <sub>CM</sub> = V <sub>CC</sub> /2                           | $V_{CC} = 2.7V$ $V_{CC} = 5V$ |                        |     | 200<br>225 | μΑ    |

| Input Offset Voltage         | Vos                  | $V_{CM} = V_{EE}$ to $V_{CC}$                                  |                               |                        |     | ±3.5       | mV    |

| Input Offset Voltage Tempco  | ΔV <sub>OS</sub> /ΔT |                                                                |                               |                        | ±2  |            | μV/°C |

| Input Bias Current           | ΙΒ                   | V <sub>CM</sub> = V <sub>EE</sub> to V <sub>CC</sub>           |                               |                        |     | ±200       | nA    |

| Input Offset Current         | los                  | V <sub>CM</sub> = V <sub>EE</sub> to V <sub>CC</sub>           |                               |                        |     | ±20        | nA    |

| Input Common-Mode Range      | V <sub>CM</sub>      | Inferred from CMRR test                                        |                               | V <sub>EE</sub> - 0.05 | Vo  | CC + 0.05  | V     |

| Common-Mode Rejection Ratio  | CMRR                 | (V <sub>EE</sub> - 0.05V) ≤ V <sub>CM</sub> ≤ (V <sub>CC</sub> | + 0.05V)                      | 62                     |     |            | dB    |

| Power-Supply Rejection Ratio | PSRR                 | 2.7V ≤ V <sub>CC</sub> ≤ 6V                                    |                               | 80                     |     |            | dB    |

|                              |                      | $V_{CC} = 2.7V$ , $R_L = 100k\Omega$                           | Sourcing                      | 82                     |     |            |       |

|                              |                      | $0.25V \le V_{OUT} \le 2.45V$                                  | Sinking                       | 80                     |     |            |       |

|                              |                      | $V_{CC} = 2.7V$ , $R_L = 1k\Omega$                             | Sourcing                      | 90                     |     |            |       |

| Large-Signal Voltage Gain    | A                    | $0.5V \le V_{OUT} \le 2.2V$                                    | Sinking                       | 76                     |     |            | ٩D    |

| (Note 1)                     | Avol                 | $V_{CC} = 5V$ , $R_L = 100k\Omega$                             | Sourcing                      | 86                     |     |            | dB    |

|                              |                      | $0.25V \le V_{OUT} \le 4.75V$                                  | Sinking                       | 82                     |     |            |       |

|                              |                      | $V_{CC} = 5V$ , $R_L = 1k\Omega$                               | Sourcing                      | 94                     |     |            |       |

|                              |                      | $0.5V \le V_{OUT} \le 4.5V$                                    | Sinking                       | 80                     |     |            |       |

| Output Voltage Swing High    | \/-··                |                                                                | $R_L = 100k\Omega$            |                        |     | 75         | \ /   |

| (Note 1)                     | VoH                  | Vcc - Vout                                                     | $R_L = 1k\Omega$              |                        |     | 250        | mV    |

| Output Voltage Swing Low     | Va                   |                                                                | $R_L = 100k\Omega$            |                        |     | 75         | m\/   |

| (Note 1)                     | V <sub>OL</sub>      | VOUT - VEE                                                     | $R_L = 1k\Omega$              |                        |     | 250        | mV    |

Note 1: R<sub>L</sub> is connected to V<sub>EE</sub> for A<sub>VOL</sub> sourcing and V<sub>OH</sub> tests. R<sub>L</sub> is connected to V<sub>CC</sub> for A<sub>VOL</sub> sinking and V<sub>OL</sub> tests.

Note 2: All specifications are 100% tested at T<sub>A</sub> = +25°C. Specification limits over temperature (T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>) are guaranteed by design, not production tested.

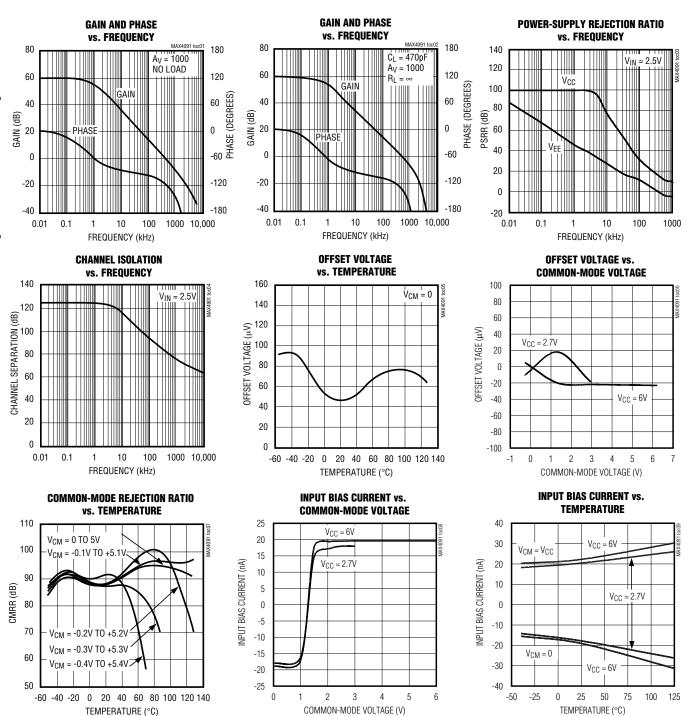

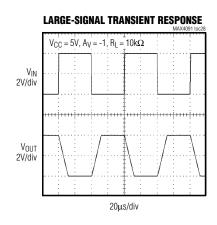

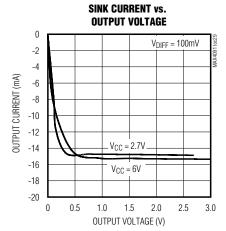

### **Typical Operating Characteristics**

( $V_{CC} = 5V$ ,  $V_{EE} = 0$ ,  $T_A = +25$ °C, unless otherwise noted.)

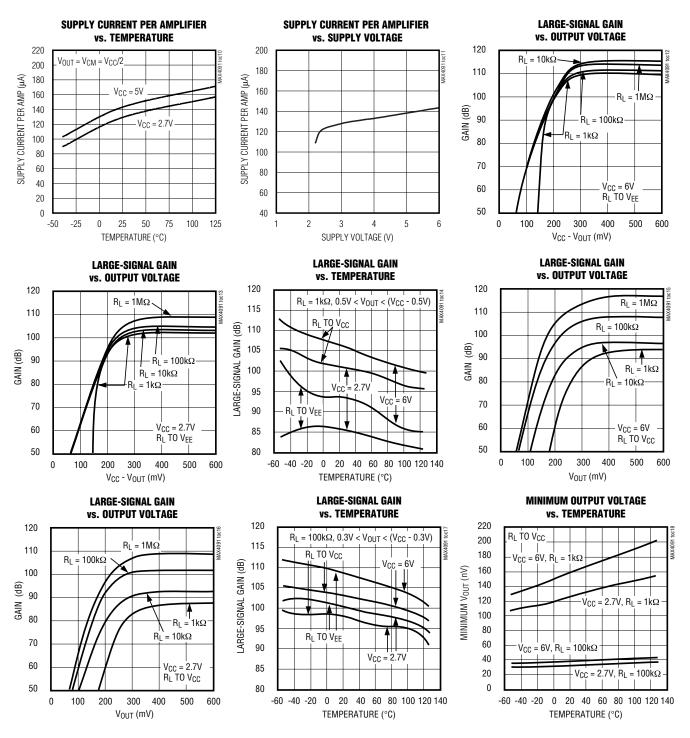

## \_Typical Operating Characteristics (continued)

$(V_{CC} = 5V, V_{EE} = 0, T_A = +25^{\circ}C, unless otherwise noted.)$

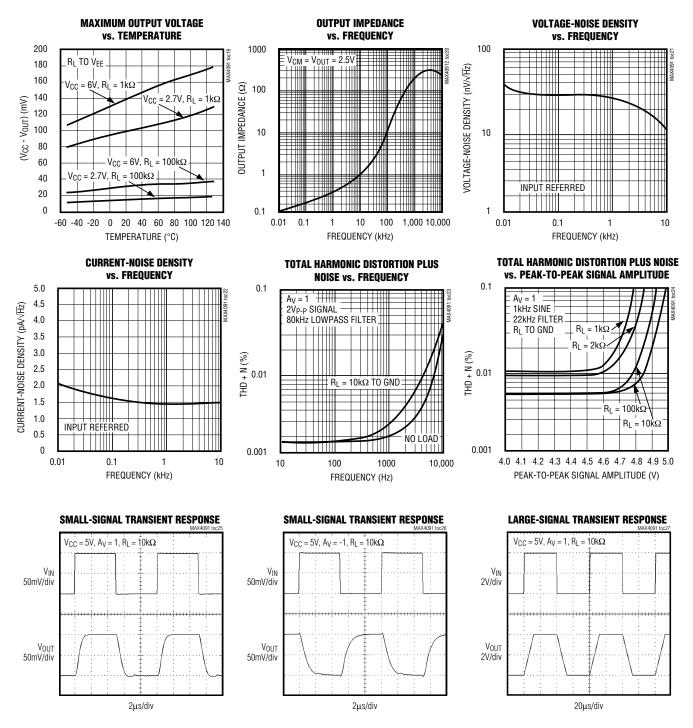

### Typical Operating Characteristics (continued)

( $V_{CC} = 5V$ ,  $V_{EE} = 0$ ,  $T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

( $V_{CC} = 5V$ ,  $V_{EE} = 0$ ,  $T_A = +25$ °C, unless otherwise noted.)

# **Pin Description**

|                  | P                  | IN      |         |      |                                          |

|------------------|--------------------|---------|---------|------|------------------------------------------|

| MAX4091<br>SOT23 | MAX4091<br>SO/μMAX | MAX4092 | MAX4094 | NAME | FUNCTION                                 |

| 1                | 6                  | _       | _       | OUT  | Amplifier Output                         |

| 2                | 4                  | 4       | 11      | VEE  | Negative Supply                          |

| 3                | 3                  | _       | _       | IN+  | Noninverting Input                       |

| 4                | 2                  | _       | _       | IN-  | Inverting Input                          |

| 5                | 7                  | 8       | 4       | Vcc  | Positive Supply                          |

| _                | 1, 5, 8            | _       | _       | N.C. | No Connection. Not internally connected. |

| _                |                    | 1       | 1       | OUT1 | Amplifier 1 Output                       |

| _                | _                  | 2       | 2       | IN1- | Amplifier 1 Inverting Input              |

| _                | _                  | 3       | 3       | IN1+ | Amplifier 1 Noninverting Input           |

| _                | _                  | 5       | 5       | IN2+ | Amplifier 2 Noninverting Input           |

| _                | _                  | 6       | 6       | IN2- | Amplifier 2 Inverting Input              |

| _                |                    | 7       | 7       | OUT2 | Amplifier 2 Output                       |

| _                | _                  | _       | 8       | OUT3 | Amplifier 3 Output                       |

| _                | _                  | _       | 9       | IN3- | Amplifier 3 Inverting Input              |

| _                | _                  | _       | 10      | IN3+ | Amplifier 3 Noninverting Input           |

|                  |                    |         | 12      | IN4+ | Amplifier 4 Noninverting Input           |

|                  | _                  | _       | 13      | IN4- | Amplifier 4 Inverting Input              |

| _                | _                  | _       | 14      | OUT4 | Amplifier 4 Output                       |

#### **Detailed Description**

The single MAX4091, dual MAX4092 and quad MAX4094 op amps combine excellent DC accuracy with rail-to-rail operation at both input and output. With their precision performance, wide dynamic range at low supply voltages, and very low supply current, these op amps are ideal for battery-operated equipment, industrial, and data acquisition and control applications.

### Applications Information

#### Rail-to-Rail Inputs and Outputs

The MAX4091/MAX4092/MAX4094's input common-mode range extends 50mV beyond the positive and negative supply rails, with excellent common-mode rejection. Beyond the specified common-mode range, the outputs are guaranteed not to undergo phase reversal or latchup. Therefore, the MAX4091/MAX4092/MAX4094 can be used in applications with common-mode signals, at or even beyond the supplies, without the problems associated with typical op amps.

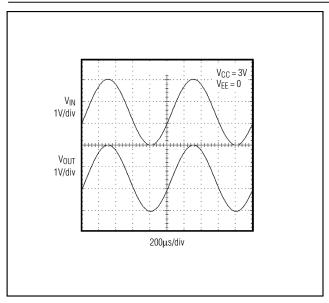

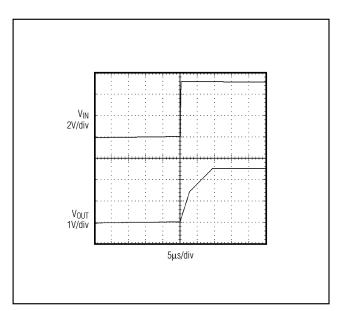

The MAX4091/MAX4092/MAX4094's output voltage swings to within 15mV of the supplies with a  $100k\Omega$  load. This rail-to-rail swing at the input and the output substantially increases the dynamic range, especially in low-supply-voltage applications. Figure 1 shows the input and output waveforms for the MAX4092, configured as a unity-gain noninverting buffer operating from a single 3V supply. The input signal is  $3.0VP_-P$ , a 1kHz sinusoid centered at 1.5V. The output amplitude is approximately  $2.98VP_-P$ .

#### **Input Offset Voltage**

Rail-to-rail common-mode swing at the input is obtained by two complementary input stages in parallel, which feed a folded cascaded stage. The PNP stage is active for input voltages close to the negative rail, and the NPN stage is active for input voltages close to the positive rail.

The offsets of the two pairs are trimmed. However, there is some residual mismatch between them. This mismatch results in a two-level input offset characteristic, with a transition region between the levels occurring at a common-mode voltage of approximately 1.3V above VEE. Unlike other rail-to-rail op amps, the transition region has been widened to approximately 600mV in order to minimize the slight degradation in CMRR caused by this mismatch.

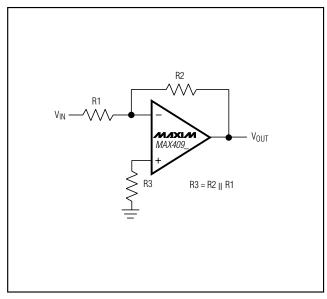

The input bias currents of the MAX4091/MAX4092/MAX4094 are typically less than 20nA. The bias current flows into the device when the NPN input stage is active, and it flows out when the PNP input stage is active. To reduce the offset error caused by input bias current flowing through external source resistances,

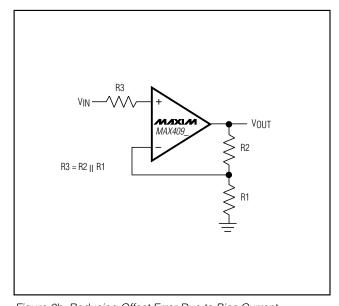

match the effective resistance seen at each input. Connect resistor R3 between the noninverting input and ground when using the op amp in an inverting configuration (Figure 2a); connect resistor R3 between the noninverting input and the input signal when using the op amp in a noninverting configuration (Figure 2b). Select R3 to equal the parallel combination of R1 and R2. High source resistances will degrade noise performance, due to the the input current noise (which is multiplied by the source resistance).

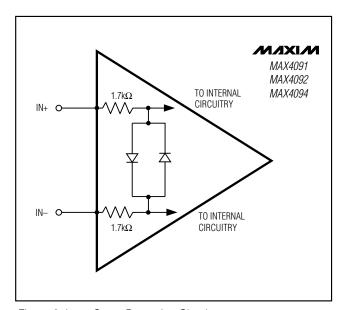

#### **Input Stage Protection Circuitry**

The MAX4091/MAX4092/MAX4094 include internal protection circuitry that prevents damage to the precision input stage from large differential input voltages. This protection circuitry consists of back-to-back diodes between IN+ and IN- with two 1.7k $\Omega$  resistors in series (Figure 3). The diodes limit the differential voltage applied to the amplifiers' internal circuitry to no more than VF, where VF is the diodes' forward-voltage drop (about 0.7V at +25°C).

Input bias current for the ICs (±20nA) is specified for small differential input voltages. For large differential input voltages (exceeding VF), this protection circuitry increases the input current at IN+ and IN-:

$$\label{eq:input_current} \text{INPUTCURRENT} = \ \frac{\left[ (V_{\text{IN}+}) \, - \, (V_{\text{IN}-}) \right] \, - V_{\text{F}}}{2 \, \times \, 1.7 \text{k} \Omega}$$

#### **Output Loading and Stability**

Even with their low quiescent current of less than 130µA per op amp, the MAX4091/MAX4092/MAX4094 are well suited for driving loads up to  $1k\Omega$  while maintaining DC accuracy. Stability while driving heavy capacitive loads is another key advantage over comparable CMOS rail-to-rail op amps.

In op amp circuits, driving large capacitive loads increases the likelihood of oscillation. This is especially true for circuits with high-loop gains, such as a unity-gain voltage follower. The output impedance and a capacitive load form an RC network that adds a pole to the loop response and induces phase lag. If the pole frequency is low enough—as when driving a large capacitive load—the circuit phase margin is degraded, leading to either an under-damped pulse response or oscillation.

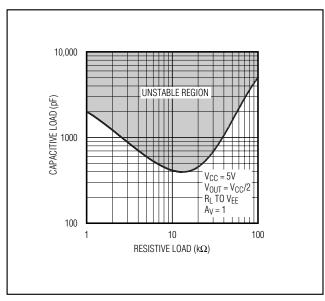

The MAX4091/MAX4092/MAX4094 can drive capacitive loads in excess of 2000pF under certain conditions (Figure 4). When driving capacitive loads, the greatest potential for instability occurs when the op amp is sourcing approximately 200µA. Even in this case, stability is maintained with up to 400pF of output capaci-

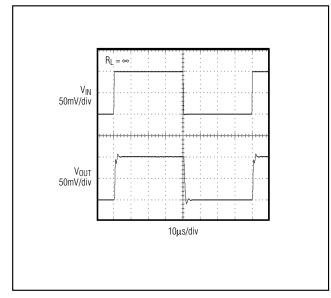

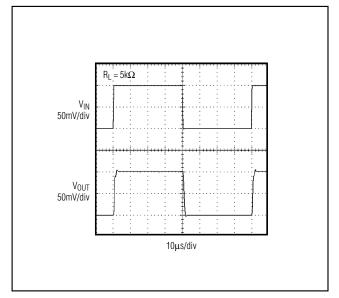

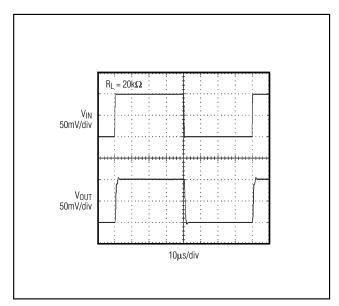

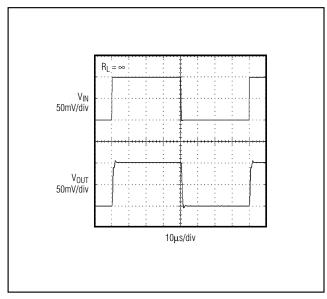

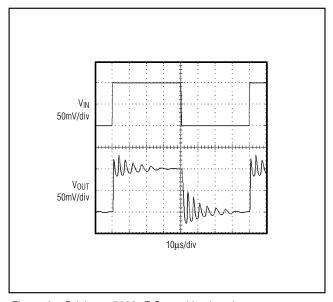

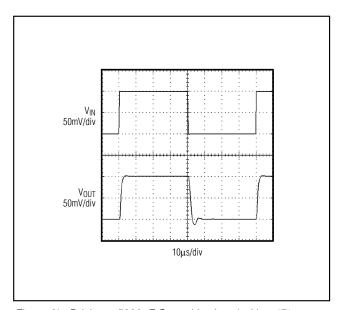

tance. If the output sources either more or less current, stability is increased. These devices perform well with a 1000pF pure capacitive load (Figure 5). Figures 6a, 6b, and 6c show the performance with a 500pF load in parallel with various load resistors.

To increase stability while driving large-capacitive loads, connect a pullup resistor to VCC at the output to decrease the current the amplifier must source. If the amplifier is made to sink current rather than source, stability is further increased.

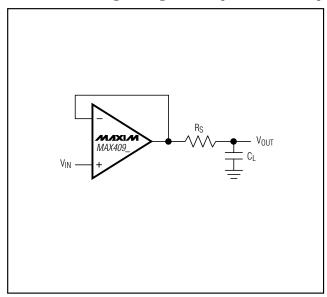

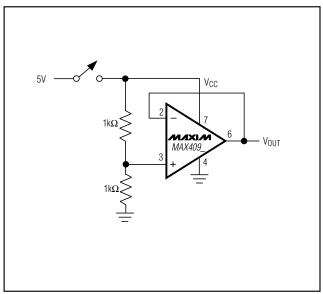

Frequency stability can be improved by adding an output isolation resistor (Rs) to the voltage-follower circuit (Figure 7). This resistor improves the phase margin of the circuit by isolating the load capacitor from the op amp's output. Figure 8a shows the MAX4092 driving 5000pF (RL  $\geq$  100k $\Omega$ ), while Figure 8b adds a 47 $\Omega$  isolation resistor.

Because the MAX4091/MAX4092/MAX4094 have excellent stability, no isolation resistor is required, except in the most demanding applications. This is beneficial because an isolation resistor would degrade the low-frequency performance of the circuit.

#### **Power-Up Settling Time**

The MAX4091/MAX4092/MAX4094 have a typical supply current of 130µA per op amp. Although supply current is already low, it is sometimes desirable to reduce it further by powering down the op amp and associated ICs for periods of time. For example, when using a MAX4092 to buffer the inputs of a multi-channel analog-to-digital converter (ADC), much of the circuitry could be powered down between data samples to increase battery life. If samples are taken infrequently, the op amps, along with the ADC, may be powered down most of the time.

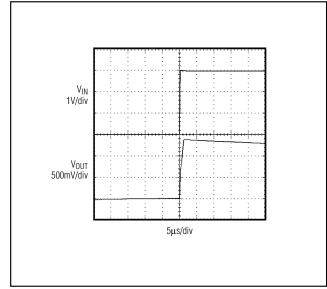

When power is reapplied to the MAX4091/MAX4092/

MAX4094, it takes some time for the voltages on the supply pin and the output pin of the op amp to settle. Supply settling time depends on the supply voltage, the value of the bypass capacitor, the output impedance of the incoming supply, and any lead resistance or inductance between components. Op amp settling time depends primarily on the output voltage and is slew-rate limited. With the noninverting input to a voltage follower held at midsupply (Figure 9), when the supply steps from 0 to  $V_{\rm CC}$ , the output settles in approximately  $2\mu s$  for  $V_{\rm CC} = 3V$  (Figure 10a) and  $8\mu s$  for  $V_{\rm CC} = 5V$  (Figure 10b).

#### **Power Supplies and Layout**

The MAX4091/MAX4092/MAX4094 operate from a single 2.7V to 6V power supply, or from dual supplies of  $\pm 1.35$ V to  $\pm 3$ V. For single-supply operation, bypass the power supply with a  $0.1\mu F$  capacitor. If operating from dual supplies, bypass each supply to ground.

Good layout improves performance by decreasing the amount of stray capacitance at the op amp's inputs and output. To decrease stray capacitance, minimize both trace lengths and resistor leads and place external components close to the op amp's pins.

## **Chip Information**

MAX4091 TRANSISTOR COUNT: 168

MAX4092 TRANSISTOR COUNT: 336

MAX4094 TRANSISTOR COUNT: 670

PROCESS: Bipolar

### Test Circuits/Timing Diagrams

Figure 1. Rail-to-Rail Input and Output Operation

Figure 2a. Reducing Offset Error Due to Bias Current: Inverting Configuration

Figure 2b. Reducing Offset Error Due to Bias Current: Noninverting Configuration

Figure 3. Input Stage Protection Circuitry

## Test Circuits/Timing Diagrams (continued)

Figure 4. Capacitive-Load Stable Region Sourcing Current

Figure 5. MAX4092 Voltage Follower with 1000pF Load

Figure 6a. MAX4092 Voltage Follower with 500pF Load ( $R_L = 5k\Omega$ )

Figure 6b. MAX4092 Voltage Follower with 500pF Load ( $R_{\rm L}=20{\rm k}\Omega$ )

## Test Circuits/Timing Diagrams (continued)

Figure 6c. MAX4092 Voltage Follower with 500pF Load ( $R_L = \infty$ )

Figure 7. Capacitive-Load Driving Circuit

Figure 8a. Driving a 5000pF Capacitive Load

Figure 8b. Driving a 5000pF Capacitive Load with a 47 $\Omega$  Isolation Resistor

# Test Circuits/Timing Diagrams (continued)

Figure 9. Power-Up Test Configuration

Figure 10a. Power-Up Settling Time ( $V_{CC} = +3V$ )

Figure 10b. Power-Up Settling Time ( $V_{CC} = +5V$ )

## **Package Information**

## Package Information (continued)

#### Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### **MAX4092**

#### **Part Number Table**

#### Notes:

- 1. See the MAX4092 QuickView Data Sheet for further information on this product family or download the MAX4092 full data sheet (PDF, 528kB).

- 2. Other options and links for purchasing parts are listed at: http://www.maxim-ic.com/sales.

- 3. Didn't Find What You Need? Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; + = RoHS/lead-free; # = RoHS/lead-exempt. More: See full data sheet or Part Naming Conventions.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number  | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE  DRAWING CODE/VAR *                               | Temp          | RoHS/Lead-Free?<br>Materials Analysis     |

|--------------|----------------|---------------|---------------------------------------------------------------------------|---------------|-------------------------------------------|

| MAX4092C/D   |                |               |                                                                           |               | RoHS/Lead-Free: No                        |

| MAX4092ASA   |                |               | SOIC;8 pin;.150"<br>Dwg: 21-0041B (PDF)<br>Use pkgcode/variation: S8-4*   | -40C to +125C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX4092ASA-T |                |               | SOIC;8 pin;.150"<br>Dwg: 21-0041B (PDF)<br>Use pkgcode/variation: S8-4*   | -40C to +125C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX4092ASA+  |                |               | SOIC;8 pin;.150"<br>Dwg: 21-0041B (PDF)<br>Use pkgcode/variation: S8+4*   | -40C to +125C | RoHS/Lead-Free: Yes<br>Materials Analysis |

| MAX4092ASA+T |                |               | SOIC;8 pin;.150"<br>Dwg: 21-0041B (PDF)<br>Use pkgcode/variation: S8+4*   | -40C to +125C | RoHS/Lead-Free: Yes<br>Materials Analysis |

| MAX4092AUA   |                |               | uMAX;8 pin;3 x 3mm<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1* | -40C to +125C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX4092AUA-T |                |               | uMAX;8 pin;3 x 3mm<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1* | -40C to +125C | RoHS/Lead-Free: No<br>Materials Analysis  |

| MAX4092AUA+                | uMAX;8 pin;3 x 3mm<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*                          | -40C to +85C | RoHS/Lead-Free: Yes<br>Materials Analysis |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------|--------------|-------------------------------------------|--|--|--|

| MAX4092AUA+T               |                                                                                                    | -40C to +85C | RoHS/Lead-Free: Yes                       |  |  |  |

| Didn't Find What You Need? |                                                                                                    |              |                                           |  |  |  |

|                            | CONTACT US: SEND US AN EMAIL                                                                       |              |                                           |  |  |  |

| Copyright 2007 by Ma       | Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy |              |                                           |  |  |  |