# LM1893/LM2893 Carrier-Current Transceiver†

# **General Description**

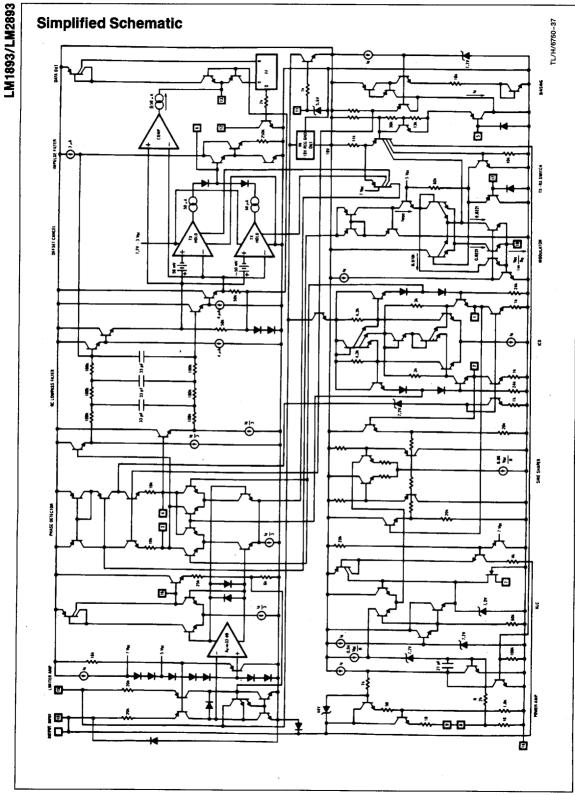

Carrier-current systems use the power mains to transfer information between remote locations. This bipolar carrier-current chip performs as a power line interface for half-duplex (bi-directional) communication of serial bit streams of virtually any coding. In transmission, a sinusoidal carrier is FSK modulated and impressed on most any power line via a rugged on-chip driver. In reception, a PLL-based demodulator and impulse noise filter combine to give maximum range. A complete system may consist of the LM1893, a COPSTM controller, and discrete components.

### **Features**

- Noise resistant FSK modulation

- User-selected impulse noise filtering

- Up to 4.8 kBaud data transmission rate

- Strings of 0's or 1's in data allowed

- Sinusoidal line drive for low RFI

- Output power easily boosted 10-fold

- 50 to 300 kHz carrier frequency choice

- TTL and MOS compatible digital levels

- Regulated voltage to power logic

- Drives all conventional power lines

# **Applications**

- Energy management systems

- Home convenience control

- Inter-office communication

- Appliance control

- Fire alarm systems

- Security systems

- Telemetry

- Computer terminal interface

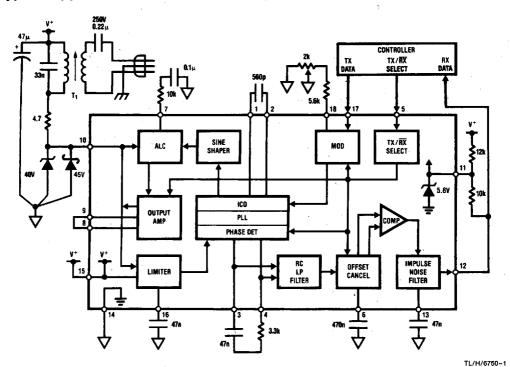

# **Typical Application**

FIGURE 1. Block diagram of carrier—current chip with a complement of discrete components making a complete F<sub>O</sub> = 125 kHz, f<sub>DATA</sub> = 360 Baud transceiver. Use caution with this circuit—dangerous line voltage is present.

†Carrier-Current Transceivers are also called Power Line Carrier (PLC) transceivers.

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply voltage                           | 30 V   |

|------------------------------------------|--------|

| Voltage on pin 12                        | 55 V   |

| Voltage on pin 10 (Note 1)               | 41 V   |

| Voltage on pins 5 and 17                 | 40 V   |

| 5.6 V DC zener current                   | 100 mA |

| Junction temperature: transmit mode      | 150°C  |

| receive mode                             | 125°C  |

| Electro-Static Discharge (120 nF, 15000) | 1KV    |

| Maximum continuous dissipation, TA = 25°C,                                                                                                                                                                   |                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| plastic DIP N (Note 2): transmit mode                                                                                                                                                                        | 1.66 W                            |

| receive mode                                                                                                                                                                                                 | 1.33 W                            |

| Operating ambient temp. range                                                                                                                                                                                | -40 to 85°C                       |

| Storage temperature range                                                                                                                                                                                    | -65 to 150°C                      |

| Lead temp., soldering, 7 seconds                                                                                                                                                                             | 260°C                             |

| Note: Absolute maximum ratings indicate which damage to the device may occur. Elections are not ensured when operating the guaranteed limits but below absolute maxinum there will be no device degradation. | trical specifica-<br>device above |

# **General Electrical Characteristics**

(Note 3). The test conditions are: V+ = 18V and FO= 125 kHz, unless otherwise noted.

| #  | Parameter                                                      | Conditions                                                                                                                          | Typical | Test<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5)                      | Limit<br>Units     |

|----|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------|--------------------------------------------------|--------------------|

| 1  | 5.6 V Zener voltage, VZ                                        | Pin 11, I <sub>Z</sub> = 2 mA                                                                                                       | 5.6     | 5.2<br>5.9                |                                                  | V min.<br>V max.   |

| 2  | 5.6 V Zener resistance, RZ                                     | Pin 11, $R_Z = (V_Z@10 \text{ mA} - V_Z@1 \text{ mA})/(10 \text{ mA} - 1 \text{ mA})$                                               | 5       |                           |                                                  | Ω                  |

| 3  | Carrier I/O peak survivable transient voltage, V <sub>OT</sub> | Pin 10, discharge 1 $\mu F$ cap. charged to $V_{OT}$ thru $<$ 1 $\Omega$                                                            | 80      | 60                        |                                                  | V max.             |

| 4  | Carrier I/O clamp voltage, V <sub>OC</sub>                     | Pin 10, I <sub>OC</sub> = 10 mA, RX mode<br>2N2222 diode pin 8 to 9                                                                 | 44      | 41<br>50                  |                                                  | V min.<br>V max.   |

| 5  | Carrier I/O clamp resistance, R <sub>10</sub>                  | Pin 10, I <sub>OC</sub> = 10 mA                                                                                                     | 20      |                           |                                                  | Ω                  |

| 6  | TX/RX low input voltage, VIL                                   | Pin 5                                                                                                                               | 1.8     | 0.8                       |                                                  | V max.             |

| 7  | TX/RX high input voltage, V <sub>IH</sub> Pin 5 (Note 9)       |                                                                                                                                     | 2.2     | 2.8                       |                                                  | V min.             |

| В  | TX/RX low input current, I <sub>IL</sub>                       | Pin 5 at 0.8 V                                                                                                                      | -2      | -20<br>1                  | 1                                                | μΑ min.<br>μΑ max. |

| 9  | TX/AX high input current, I <sub>IH</sub>                      | Pin 5 at 40 V                                                                                                                       | 10-4    | -1<br>10                  | 0                                                | μA min,<br>μA max. |

| 10 | RX-TX switch-over time, T <sub>RT</sub>                        | Time to develop 63% of full current drive thru pin 10                                                                               | 10      |                           | <del> </del>                                     | μs                 |

| 11 | TX - RX switch-over time, T <sub>TR</sub>                      | 1 bit time, T <sub>B</sub> = 1/(2F <sub>DATA</sub> ). Time T <sub>TR</sub> is user controlled with C <sub>M</sub> , see Apps. Info. | 2       |                           |                                                  | bit                |

| 12 | ICO initial accuracy of FO                                     |                                                                                                                                     |         |                           | kHz min.<br>kHz max.                             |                    |

| 13 | ICO temperature coefficient of Fo                              | TX or RX mode, (F <sub>OMAX</sub> - F <sub>OMIN</sub> )/(T <sub>JMAX</sub> - T <sub>JMIN</sub> )                                    | -100    |                           | <del>,                                    </del> | PPM/°C             |

| 14 | Temperature drift of Fo                                        | TX or RX mode, −40≤T <sub>J</sub> ≤T <sub>JMAX</sub>                                                                                | ± 2.0   | <del></del>               | ± 5.0                                            | % max.             |

**Transmitter Electrical Characteristics** (Note 3). The test conditions are:  $V^+ = 18 \text{ V}$  and  $F_O = 125 \text{ kHz}$  unless otherwise noted. The transmit center frequency is  $F_O$ , FSK low is  $F_1$ , and FSK high is  $F_2$ .

| #  | Parameter                                       | Conditions                                                                                                                                                                                                  | Typical    | Test<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Limit<br>Units     |

|----|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|-----------------------------|--------------------|

| 15 | Supply voltage, V+, range                       | Meets test 17 spec, at T <sub>J</sub> = 25°C and:<br> (F <sub>1</sub> [14V] - F <sub>1</sub> [18V])/F <sub>1</sub> [18V] <0.01<br> (F <sub>1</sub> [24V] - F <sub>1</sub> [18V])/F <sub>1</sub> [18V] <0.01 | 13<br>40   | 14<br>24                  | 15<br>23                    | V min.<br>V max.   |

| 16 | Total supply current, I <sub>QT</sub>           | Pin 15. Pin 12 high. I <sub>QT</sub> is I <sub>Q</sub> through pin 15 and the average current I <sub>ODC</sub> of the Carrier I/O through pin 10                                                            | 52         | 79                        |                             | mA max.            |

| 17 | Carrier I/O output current, IO                  | 100Ω load on pin 10                                                                                                                                                                                         | 70         | 45                        |                             | mApp min.          |

| 18 | Carrier I/O lower swing limit, V <sub>ALC</sub> | Pin 10. Set internally be ALC.<br>2N2222 diode pin 8 to 9                                                                                                                                                   | 4.7        | 4.0<br>5.7                |                             | V min.<br>V max.   |

| 19 | THD of I <sub>O</sub> (Note 6)                  | $\Omega$ of 10 tank driving 10 $\Omega$ line 100 $\Omega$ load, no tank                                                                                                                                     | 0.6<br>5.5 |                           | <b>5.0</b><br>9             | % max.<br>% max.   |

| 20 | FSK deviation, F <sub>2</sub> F <sub>1</sub>    | $(F_2-F_1)/([F_2+F_1]/2)$                                                                                                                                                                                   | 4.4        | 3.7<br>5.2                |                             | % min.<br>% max.   |

| 21 | Data In. low input voltage, VIL                 | Pin 17                                                                                                                                                                                                      | 1.7        | 0.8                       |                             | V max.             |

| 22 | Data In. high input voltage, VIH                | Pin 17 (Note 9)                                                                                                                                                                                             | 2.1        | 2.8                       |                             | V min.             |

| 23 | Data In. low input current, I <sub>IL</sub>     | Pin 17 at 0.8 V                                                                                                                                                                                             | -1         | -10<br>1                  |                             | μΑ min.<br>μΑ max. |

| 24 | Data In. high input current, I <sub>IH</sub>    | Pin 17 at 40 V                                                                                                                                                                                              | 10-4       | -1<br>10                  | 0                           | μΑ min,<br>μΑ max, |

**Receiver Electrical Characteristics** (Note 3). The test conditions are:  $V^+ = 18 \text{ V}$ ,  $F_0 = 125 \text{ kHz}$ ,  $\pm 2.2\%$  deviation FSK,  $F_{DATA} = 2.4 \text{ kHz}$ ,  $V_{IN} = 100 \text{ mVpp}$ , in the receive mode, unless otherwise noted.

| #  | Parameter                                                                                                             | Conditions                                                                                            | Typical                                   | Test<br>Limit<br>(Note 4) | Design<br>Limit<br>(Note 5) | Limit<br>Units                                                                                        |

|----|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------|

| 25 | Supply voltage, V+, range                                                                                             | Functional receiver (Note 7)                                                                          | 12<br>37                                  | 13<br>30                  | 13.5<br>28                  | V min.<br>V max.                                                                                      |

| 26 | Supply current, I <sub>QT</sub>                                                                                       | $I_{QT}$ is pin 15 (V <sup>+</sup> ) plus pin 10 (Carrier I/Q) current. 2.4 k $\Omega$ Pin 13 to GND. | 11                                        | 5<br>14                   |                             | mA min.<br>mA max.                                                                                    |

| 27 | Carrier I/O input resistance, R <sub>10</sub>                                                                         | Pin 10                                                                                                | 19.5                                      | 14<br>30                  |                             | $k\Omega$ min. $k\Omega$ max.                                                                         |

| 28 | Max. data rate, $F_{MD}$ Functional receiver (Note 7), $C_F = 100$ pF, $R_F = 0\Omega$ , no tank, 2.4 kHz = 4.8 kBaud |                                                                                                       | 10                                        | 4.8                       | 2.4                         | kBaud                                                                                                 |

| 29 | PLL capture range, F <sub>C</sub>                                                                                     | $C_F = 100 \text{ pF, R}_F = 0 \Omega$                                                                | ±40                                       | ±15                       | ± 10                        | % min.                                                                                                |

| 30 | PLL lock range, F <sub>L</sub>                                                                                        | $C_F = 100 \text{ pF}, R_F = 0 \Omega$                                                                | ± 45                                      | ±15                       |                             | % min.                                                                                                |

| 31 | (1)                                                                                                                   |                                                                                                       | 1.8<br>2.0<br>1.4<br>0.26<br>0.29<br>0.20 | 10                        | 12                          | mV <sub>RMS</sub><br>mV <sub>RMS</sub><br>mV <sub>RMS</sub><br>mV <sub>RMS</sub><br>mV <sub>RMS</sub> |

| 32 | Tolerable input dc voltage offset range, VINDC                                                                        | ' '                                                                                                   |                                           | 0.1                       |                             | V max.                                                                                                |

| 33 | Data Out. breakdown voltage                                                                                           | Pin 12, leakage l≤20 μA                                                                               | 70                                        | 55                        |                             | V min.                                                                                                |

| 34 | Data Out. low output, VOL                                                                                             | Pin 12, sat. voltage at I <sub>OL</sub> = 2 mA                                                        | 0.15                                      | 0.4                       |                             | V max.                                                                                                |

| 35 | Impulse noise filter current, I <sub>I</sub>                                                                          | Pin 13 charge and discharge current                                                                   | ±55                                       | ± 45<br>± 85              |                             | μA min.<br>μA max.                                                                                    |

| 36 | Offset hold cap. bias voltage, V <sub>CM</sub>                                                                        | ap. bias voltage, V <sub>CM</sub> Pin 6                                                               |                                           | 1.3<br>3.5                |                             | V min.<br>V max.                                                                                      |

| 37 | Offset hold capacitor max. drive current, I <sub>MCM</sub>                                                            |                                                                                                       |                                           | ±25<br>±80                |                             | μA min.<br>μA max.                                                                                    |

| 38 | Offset hold bias current, I <sub>OHB</sub>                                                                            | Pin 6, TX mode. Bias pin 6 as it self-<br>biased during test 31.                                      | -0.5                                      | -20                       | -40<br>40                   | nA min.<br>nA max.                                                                                    |

| 39 | Phase comparator current, I <sub>PC</sub> Bias pins 3 and 4 at 8.5 V I <sub>PC</sub> = I(pin 3) + I(pin 4), TX mode   |                                                                                                       | 100                                       | 50<br>200                 |                             | μA min.<br>μA max.                                                                                    |

| 40 | Phase detector output resistance,                                                                                     |                                                                                                       |                                           | 6<br>18                   |                             | kΩ min.<br>kΩ max.                                                                                    |

| 41 | Phase detector demodulated output voltage, V <sub>PD</sub>                                                            | ector demodulated output Pin 3 to 4, measured after filtering                                         |                                           | 60<br>180                 |                             | mVpp mir<br>mVpp ma:                                                                                  |

| 42 | Fast offset cancel voltage "window" -to-V <sub>PD</sub> ratio, V <sub>W</sub> /V <sub>PD</sub>                        | $V_{PIN3} - V_{PIN4} = \pm V_{WINDOW} + DC$ offset Drive for $\pm 1 \mu A$ pin 6 current              | 0.95                                      | 0.70<br>1.20              |                             | V/V min.<br>V/V max                                                                                   |

| 43 | Power supply rejection, PSRR                                                                                          | C <sub>L</sub> = 0.1 μF. PSRR = CMRR. 120 Hz                                                          | 80                                        | 1                         | 1                           | dB min.                                                                                               |

Note 1: More accurately, the maximum voltage allowed on pin 10 is V<sub>OC</sub>, and V<sub>OC</sub> ranges from 41 to 50V. Also, transients may reach above 60V; see the transient peak voltage characteristic curve.

Note 2: The maximum power dissipation rating should be derated for device operation above 25°C to insure that the junction temperature remains below the maximum rating. Use a θ<sub>JA</sub> of 75°C/W for the N package using a socket in still air (which is the worst case). Consult the Application Information section for more

Note 3: The boldface values apply over the full junction temperature range for the specified supply voltage range. All other numbers apply at T<sub>A</sub>=T<sub>J</sub>=25°C. Pin numbers refer to LM1893. LM2893 tested by shorting Carrier In to Carrier Out and testing it as an LM1893.

Note 4: Guaranteed and 100% production tested.

Note 5: Guaranteed (but not 100% production tested) over the temperature and supply voltage ranges. These limits are not used to calculate outgoing quality levels.

Note 6: Total harmonic distortion is measured using THD=[I<sub>RMS</sub> (all components at or above 2F<sub>O</sub>)]/[I<sub>RMS</sub> (fundamental)].

Note 7: Receiver function is defined as the error-free passage of 1 cycle of 50% duty-cycle 2.4 kHz square-wave data (2 sequential 208  $\mu$ S bits), with the first bit being a "1." All of the data transitions (edges) must fall within  $\pm$  10% ( $\pm$  20.8  $\mu$ s) of their noise-free positions. RX time delay is minimized by using no impulse noise filter cap. C<sub>1</sub> for this test.

Note 8: During the sensitivity check, note 7 requirements are followed with these exceptions: (1) data rate F<sub>DATA</sub>= 1.2 kHz, (2) all of the data transitions must fall within ±20% (±41.6 μs) of their noise-free positions, and (3), a time-domain filter capacitor (C<sub>I</sub>) is used. The time delay of C<sub>I</sub> is ½ bit, or 208 μs. (C<sub>I</sub> is approximately 6200 pF).

Note 9: For TTL compatibility use a pull-up resistor to increase min. VOH to above 2.8 V.

0 30 60

TJ-JUNCTION TEMPERATURE ("C)

TL/H/6750-38

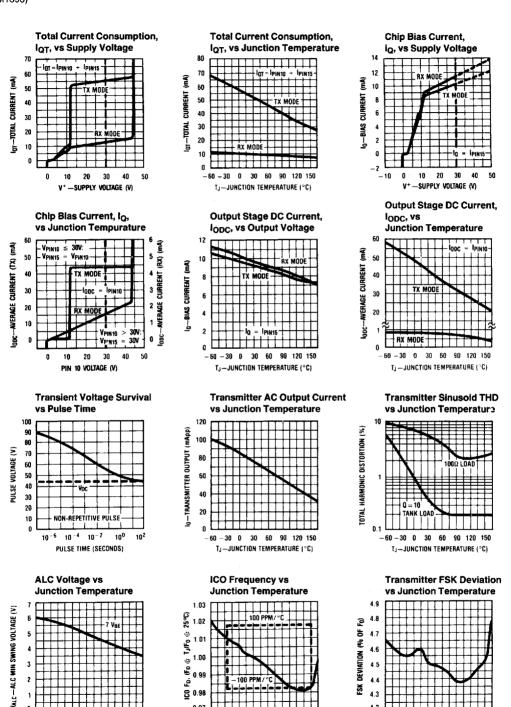

# Typical Performance Characteristics (V $^+$ = 18V, F<sub>O</sub> = 125 kHz, circuit of Figure 1, pin numbers for LM1893)

30

TJ-JUNCTION TEMPERATURE (°C)

8 0.98

60 90 120 150

TJ-JUNCTION TEMPERATURE (°C)

-60 -30 0 30

# Typical Performance Characteristics (Continued)

TL/H/6750~2

# Application Information\*

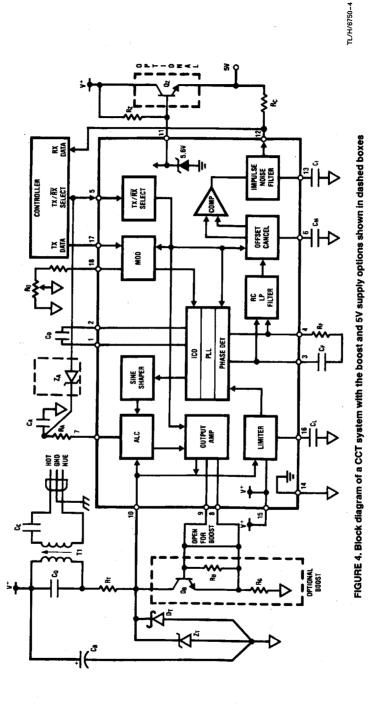

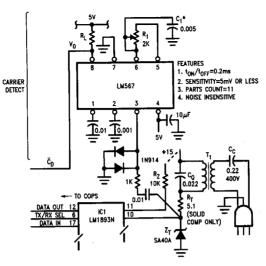

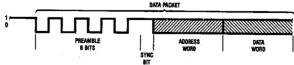

#### THE DATA PATH

The BI-LINETM chip serves as a power line interface in the carrier-current transceiver (CCT) system of *Figure 3. Figure 4* shows the interface circuit now discussed. The controller may select either the transmit (TX) or receive (RX) mode. Serial data from the controller is used to generate a FSK-modulated 50 to 300 kHz carrier on the line in the TX mode. In the RX mode line signal passes through the coupling transformer into the PLL-based receiver. The recreated serial bit stream drives the controller.

With the IC in the TX mode (pin 5 a logic high), baseband data to 5 kHz drive the modulator's Data In pin to generate a switched 0.978I/1.022I control current to drive the low TC. triangle-wave, current-controlled oscillator to ±2.2% deviation. The tri-wave passes through a differential attenuator and sine shaper which deliver a current sinusoid through an automatic level control (ALC) circuit to the gain of 200 current output amplifier. Drive current from the Carrier I/O develops a voltage swing on T<sub>1</sub>'s (Figure 4) resonant tank proportional to line impedance, then passes through the step-down transformer and coupling capacitor Co onto the line. Progressively smaller line impedances cause reduced signal swing, but never clipping-thus avoiding potential radio frequency interference. When large line impedances threaten to allow excessive output swing on pin 10, the ALC shunts current away from the output amplifier, holding the voltage swing constant and within the amp's compliance limit. The amplifier is stable with a load of any magnitude or phase angle.

In the RX mode (pin 5 a logic low), the TX sections on the chip are disabled. Carrier signal, broad-band noise, transient spikes, and power line component impinge of the receiver's input highpass filter, made up of CC and T1, and the tank bandpass filter. In-band carrier signal, band-limited noise, heavily attenuated line frequency component, and attenuated transient energy pass through to produce voltage swing on the tank, swinging about the positive supply to drive the Carrier I/O receiver input. The balanced Norton-input limiter amplifier removes DC offsets, attenuates line frequency, performs as a bandpass filter, and limits the signal to drive the PLL phase detector differentially. The differential demodulated output signal from the phase detector, containing AC and DC data signal, noise, system DC offsets, and a large twice-the-carrier-frequency component, passes through a 3-stage RC lowpass filter to drive the offset cancel circuit differentially. The offset cancelling circuit works by insuring that the (fixed)  $\pm 50~\text{mV}$  signal delivered to the data squaring ("slicing") comparator is centered around the 0 mV comparator switch point. Whenever the comparator signal plus DC offset and noise moves outside the carefully matched ±50 mV voltage "window" of the offset cancel circuit, it adjusts its DC correction voltage in series with the differential signal to force the signal back into the window. While the signal is within the ±50 mV window, the DC offset is stored on capacitor C<sub>M</sub>. By grace of the highly non-linear offset hold capacitor charging during offset cancelling, the DC cancellation is done much more quickly than with an AC coupling capacitor normally used in place of the offset cancel circuit. Since impulse noise spikes normally ring the signal symmetrically around 0 V, the fully bilateral offset cancel topology affords excellent noise rejection. The switched current output of the comparator drives the impulse noise filter integrator capacitor that rejects all data pulses of less than the integrator charge time. Noise appears as duty-cycle jitter at the open collector serial data output.

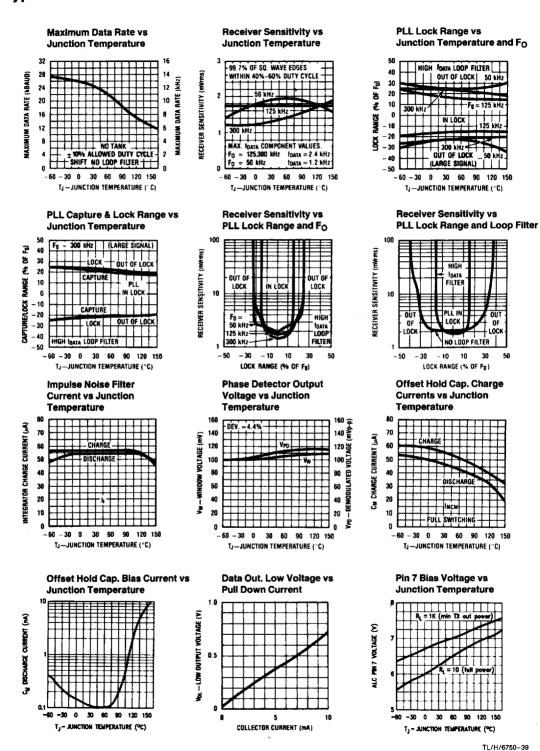

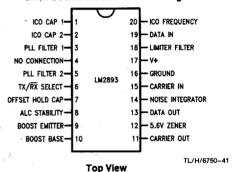

#### **Dual-In-Line Package** - ICO FREQUENCY ICO CAP 1 \_ DATA IN ICO CAP 2 -17 PLL FILTER 1 I IMITED FILTER PLL FILTER 2 -15 LM1893 TX/AX SELECT -RROUND NOISE INTEGRATOR OFFSET HOLD CAP ALC STABILITY DATA OUT - 5.6V ZENER ROOST EMITTER - CARRIER 1/0 ROOST BASE

Top View

Order Number LM1893N

See NS Package Number N18A

### Small Outline & Dual-In-Line Package

Order Number LM2893M or LM2893N See NS Package Number M20B or N20A

FIGURE 2. Connection Diagrams

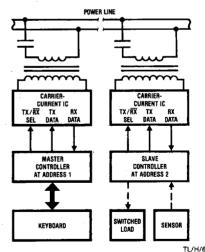

FIGURE 3. The block diagram of a carrier-current system using the Bi-Line chip to interface digital controllers via the power line

<sup>\*</sup>Unless otherwise noted, all pin references refer to LM1893, but hold true for equivalent LM2893 pin.

# **Application Information (Continued)**

| <b>Application Informa</b> | tion | (Continued) |

|----------------------------|------|-------------|

|----------------------------|------|-------------|

|                                  | Recommended                                  |                                                                                                   | Effect of making the component value:                                                                                                                                   |                                                                                                                                        | 1                                                                                                                                                                      |  |

|----------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| #                                | Value                                        | Purpose                                                                                           | Smaller                                                                                                                                                                 | Larger                                                                                                                                 | Notes                                                                                                                                                                  |  |

| C <sub>O</sub><br>R <sub>O</sub> | 560 pF<br>6.2 kΩ                             | Together, C <sub>O</sub> and R <sub>O</sub> set ICO F <sub>O</sub> .                              |                                                                                                                                                                         | Decreases F <sub>O</sub> Decreases F <sub>O</sub> >7.6 k not recommended.                                                              | $\pm$ 5% NPO ceramic. Use low TC 2 k pot and 5.6 k fixed R. Poor F <sub>O</sub> TC with <5.6 k R <sub>O</sub> .                                                        |  |

| ٠.                               | 0.047 μF<br>3.3 kΩ                           | PLL loop filter pole PLL loop filter zero                                                         | Less noise immune, higher f <sub>DATA</sub> , more PLL stability. PLL less stable, allows less C <sub>F</sub> . Less ringing.                                           | More noise immune, lower f <sub>DATA</sub> , less PLL stability. PLL more stable, allows more C <sub>F</sub> . More ringing.           | Depending on R <sub>F</sub> value and F <sub>O</sub> , PLL unstable with large C <sub>F</sub> . See Apps. Info. C <sub>F</sub> and R <sub>F</sub> values not critical. |  |

| CC                               | 0.22 μF                                      | Couples $F_O$ to line, $C_C$ and $T_1$ low-pass attenuates 60 Hz.                                 | Low TX line amplitude.<br>Less 60 Hz T <sub>1</sub> current.<br>Less stored charge.                                                                                     | Drives lower line Z.<br>More 60 Hz T <sub>1</sub> current.<br>More stored charge.                                                      | ≥250 V non-polar. Use 2C <sub>C</sub> on hot and neutral for max. line isolation, safety.                                                                              |  |

| -                                | 0.033 μF<br>Use<br>recommended<br>XFMR       | Tank matches line Z,<br>bandpass filters,<br>isolates from line,<br>and attenuates<br>transients. | Tank $F_O$ up or increase L of $T_1$ for constant $F_O$ . Smaller L: higher $F_O$ or increase $C_C$ ; decreased $F_O$ line pull.                                        | Tank $F_O$ down or decrease L of $T_1$ for constant $F_O$ . Larger L: lower $F_O$ or decrease $C_C$ ; increased $F_O$ line pull.       | 100 V nonpolar, low TC, $\pm 10\%$ High large-signal Q needed. Optimize for low F <sub>O</sub> line pull with control of F <sub>O</sub> TC and Q.                      |  |

|                                  | 0.1 μF<br>10 kΩ                              | ALC pole<br>ALC zero                                                                              | Noise spikes turn ALC off.<br>Less stable ALC.                                                                                                                          | Slower ALC response.<br>More stable ALC.                                                                                               | R <sub>A</sub> optional. ALC stable for C <sub>A</sub> ≥ 100 pF.                                                                                                       |  |

| CL                               | 0.047 μF                                     | Limiter 50 kHz pole,<br>60 Hz rejection.                                                          | Higher pole F, more 60 Hz reject. FO attenuation?                                                                                                                       | Lower pole F, less 60 Hz<br>reject, more noise BW.                                                                                     | Any reasonably low TC cap.<br>300 pF guarantees stability.                                                                                                             |  |

| C <sub>M</sub>                   | 0.47 μF                                      | Holds RX path V <sub>OS</sub>                                                                     | Less noise immune, shorter V <sub>OS</sub> hold, faster V <sub>OS</sub> aquisition, shorter preamble.                                                                   | More noise immune, longer V <sub>OS</sub> hold, slower V <sub>OS</sub> aquisition, longer preamble.                                    | Low leakage ±20% cap.<br>Scale with f <sub>DATA</sub> .                                                                                                                |  |

| Cı                               | 0.047 μF                                     | Rejects short pulses like impulse noise.                                                          | Less impulse reject, less<br>delay, more pulse jitter.                                                                                                                  | More impulse reject, more delay, less pulse jitter.                                                                                    | C <sub>I</sub> charge time ½ bit nom.<br>Must be <1 bit worst-case.                                                                                                    |  |

| Rc                               | 10 kΩ                                        | Open-col. pull-up                                                                                 | Less available sink I.                                                                                                                                                  | Less available source I.                                                                                                               | R <sub>C</sub> ≥1.5 kΩ on 5.6 V                                                                                                                                        |  |

| Ŕz                               | 12 kΩ                                        | 5.6 V Zener bias                                                                                  | Larger shunt current, more chip dissipation.                                                                                                                            | Smaller shunt current, less V+ current draw.                                                                                           | 1 < I <sub>Z</sub> < 30 mA recommended.<br>(Chip power-up needs 5.6 V)                                                                                                 |  |

|                                  | ≥ 44 V BV<br><60 V peak<br>4.7 Ω<br>≥ 44V BV | Transient clamp  Transient I limit  Over-drive Clamp                                              | Z <sub>T</sub> failure, higher series<br>R-excess peak V, Zener<br>and chip damage,<br>less ruggedness.<br>Damage Z <sub>T</sub> , pull up V +.<br>Failure on Transient | Z <sub>T</sub> costly, lower series<br>R gives enhanced<br>transient clamp,<br>more ruggedness.<br>Excessive TX attenuation.<br>Costly | Recommend Zener rated for ≥ 500 W for 1 ms.  Carbon comp. recommended. IRF 11DQ05 or 1N5819                                                                            |  |

| R <sub>B</sub>                   | 180 Ω<br>Power NPN<br>1.1 Ω                  | Base bleed<br>Boost gain device<br>Current setting R                                              | Faster, lower THD I <sub>O</sub> .<br>Excessive T <sub>J</sub> and V <sub>SAT</sub> .<br>More I <sub>O</sub> , need higher h <sub>fe</sub> .                            | Inadequate turn-off speed.<br>More rugged, but costly.<br>Less I <sub>O</sub> , lower min. h <sub>fe</sub> .                           | Boost optional. $Q_B F(-3 dB)$<br>of >200 MHz. $R_B$ > 24 Ohm.<br>$I_O = 70[(10 + R_G)/R_G]$ mApp.                                                                     |  |

|                                  | ≥47 µF                                       | Supply bypass                                                                                     | Transients destroy chip.                                                                                                                                                | Less supply spike.                                                                                                                     | V+ never over abs. max.                                                                                                                                                |  |

| ZA                               | 5.1V                                         | Stop ALC charge in RX mode                                                                        | Excess ALC current flow                                                                                                                                                 | ALC RX charging not inhibited over T <sub>J</sub>                                                                                      | Z <sub>A</sub> optional - 5.1V<br>±20% low leakage type                                                                                                                |  |

FIGURE 5. A quick explanation of the external component function using the circuit of *Figure 4*. Values given are for V + = 18 V, F<sub>O</sub> = 125 kHz, f<sub>DATA</sub> = 360 Baud (180 Hz), using a 115 V 60 Hz power line

# **Component Selection**

Assuming the circuit of *Figure 4* is used with something other than the nominal 125 kHz carrier frequency, 180 Hz data rate, 18V supply voltage, etcetera, the component values listed in *Figure 5* will need changing. This section will help direct the CCT designer in finding the required component values with emphasis placed on look-up tables and charts. It is assumed that the designer has selected values for carrier center frequency, F<sub>O</sub>; data rate, f<sub>DATA</sub>; supply voltage, V+; power line voltage, V<sub>L</sub>; and power line frequency, F<sub>L</sub>. If one or more of those parameters is not defined, one may read the data sheet and make an educated guess.

Maxims to keep in mind, based on CCT electrical perform-

ance considerations only, are: 1) the higher the  $F_O$  the better, 2) the lower the maximum data rate the better, and 3) the more time and frequency filtering the better.

Use Figure 5 as a quick reference to the external component function.

#### THE TRANSMITTER

#### Co

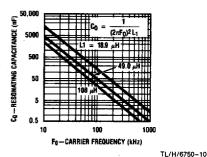

Central to chip operation is the low TC of  $F_O$  emitter-coupled oscillator. With proper  $C_O$ , the  $F_O$  of the  $2V_{BE}$  amplitude triangle-wave oscillator output may vary from near DC to above 300 kHz. While  $C_O$  may have any value,  $C_O$  should

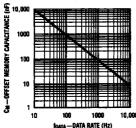

be made above 10 pF so that parasitic capacitance is not dominant. Excessive or unbalanced common-mode-toground capacitance should be avoided. A low temperature coefficient (TC) of capacitance (<100 PPM/°C), such as a monolithic NPO ceramic multilayer type, preserves low TC of FO. Figure 6 finds a CO value given FO.

Resistor RO is used by the IC to generate a VBE/R related

### Ro

current that is multiplied by 2 to produce the 200  $\mu A$  ICO control current that sets F<sub>O</sub>. The control current TC "bucks" the VBE related tri-wave amplitude across CO to effect a low TC of Fo. Vary Ro to trim Fo, within limits. Raising Fo more than 20% above its untrimmed value by means of decreasing RO more than 20% is not recommended. Low RO, and so high control current, risks ICO saturation and poor TC under worst-case conditions. Raising RO reduces the de-

modulated signal amplitude from the phase detector; raising Ro by more than a factor of 2 (1 octave) is not recommended. Since lower TC pots are relatively costly, it is recommended that R<sub>O</sub> be made up of a 5.6 k fixed (<100 PPM/°C) resistor with a 2 k $\Omega$  (<250 PPM/°C) series pot.

# CA and RA

Components CA and RA control the dynamic characteristics of the transmitter output envelope. Their values are not critical. Use the values given in Figure 5.  $C_A$  and  $R_A$  are functions of loaded  $T_1$  tank Q,  $R_0$ ,  $f_{DATA}$ , and line impulse noise. Any changes made in CA and RA should be made based on empirical measurements of a CCT on the line. Roughly, CA acts as an ALC pole and RA an ALC zero.

FIGURE 6. Find Co's value knowing Fo

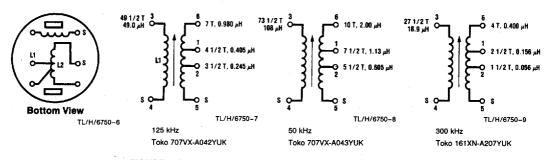

At this point, the CCT system designer may choose to use one of the recommended transformers or to design custom T<sub>1</sub>. Consult "The Coupling Transformer" section to help with the design of T<sub>1</sub> if a new or boost-capable transformer is needed. The recommended 125 kHz transformer functions with an IO of up to 600 mApp.

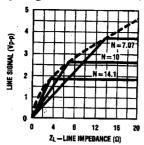

It is recommended that CCT systems use the recommended transformers, described in Figure 7, for T1. The 3 transformers are optimized for use in the ranges of 50-100 kHz, 100-200 kHz, and 200-400 kHz with unloaded Q's (Qu) of about 35, and loaded Q's (QL) of about 12. Three secondary taps are supplied with nominal 7.07, 10, and 14.1 turns ratios (N) to drive industrial and residential power line impedances of 3.5, 7, and  $14\Omega$  respectively. All are inexpensive, all have the same pin-outs for easy exchange in a PC board, and all are small - on the order of 10 mm diameter at the base.

Tank resonant frequency FQ must be correct to allow passage of transmitter signal to the line. Use Figure 8 to find CQ's value. Trimming FQ to equal FO is done with T1's trimming slug. The inductance of T<sub>1</sub> has a TC of +150 PPM/°C which may be cancelled by using a -150 PPM/°C cap such as polystyrene. Since circulating current in the tank is 1/4 A<sub>RMS</sub>,  $C_Q$  should have a low series resistance (a 1  $\Omega$  series resistance is too much). Polypropelene caps are excellent, "orange drop" mylars are adequate, while many other mylars are inadequate. A 100V rating is needed for transient protection.

FIGURE 8. Find Co's value given Fo

TL/H/6750-5

FIGURE 7. The recommended T<sub>1</sub> transformers, available through: Toko America, 1250 Feehanville Drive, Mount Prospect, IL, 60056, (312) 297-0070

CC

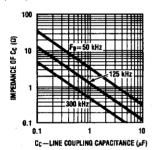

Capacitor C<sub>C</sub>'s primary function is to block the power line voltage from T1's line-side winding. Also, CC and T1's lineside winding comprise a LC highpass filter. The self-inductance of T<sub>1</sub> is far too low to support a direct line connection. Co must have a low enough impedance at Fo to allow T1 to drive transmitted energy onto the line. To drive a  $14\Omega$  power line, the impedance of  $C_C$  should be below  $14\Omega$ .

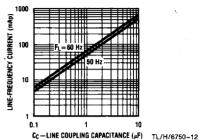

Use Figure 9 to find the reactive impedance of Co to check that it is less than the line impedance. Then check Figure 10 to see that the power line current is small enough to keep T<sub>1</sub> well out of saturation; the recommended transformers can withstand a 10 Amp-turn magnetizing force (1 Amp through the worst-case 10 turn line-side winding).

Caution is required when choosing CC to avoid series resonance of the series combination of CC, the transformer inductance, and the reflected tank impedance. The low resistance of the network under series resonance will load the line, possibly decreasing range. For your particular line coupling circuit, measure for series resonance using some expected line impedance load.

#### RB

This base-bleed resistor turns QR off quickly - important since the amplifier output swing is about 200V/µs. An RB below about  $24\Omega$  will conduct excessive current and overload the chip amplifier and is not recommended.

TL/H/6750-11

FIGURE 9. Cc's impedance should be, as a rule-of-thumb, smaller than the lowest expected line impedance

### RG

This resistor, in parallel with the internal  $10\Omega$  resistor, fixes the current gain of the output amplifier, and so the output current amplitude. Figure 11 gives output current and minimum AC current gain hfe for QB when RG is used to boost output current.

The boost gain transistor QB must be fast. Double-diffused devices with 50 MHz FT's work, slower transistors (epi-base types) do not preserve a sinusoidal waveform when Fo is high or will cause the output amp, to oscillate. Qn must have a certain minimum hfe for given boost levels, as shown in Figure 11. Figure 12 shows the power QB must dissipate continuously operating with a shorted output. BVCFR (R = RB) must be 60V or greater and QB must have adequate SOA for transient survival.

### ΖŢ

Unfortunately, potentially damaging transient energy passes through transformer T1 onto the Carrier I/O pin (instantaneous power of greater than 1 kW has been measured using the recommended transformers). For self protection, the Carrier I/O has an internal 44V voltage clamp with a 200 series resistance. A parallel low impedance 44V external transient suppression diode will then conduct the lion's share of any current when transients force the Carrier I/O to a high voltage.

FIGURE 10. The AC line-induced current passed by CC

0-CUTPUT CURRENT (MARMS 10 0.1

Re - GAIN-SETTING (Ω) FIGURE 11. Output amplifier current and required min. QB hfe versus gain-setting resistor RG

IO-OUTPUT CURRENT (mArms)

TI /H/6750-14

FIGURE 12. Boost transistor power dissipation versus amplifier output current

Z<sub>T</sub> must be used unless some precaution is taken to protect the Carrier I/O pin from line transients or transients caused when stored line energy in C<sub>C</sub> is discharged by the random phase of power line connection and disconnection. Worst case, CC may discharge a full peak-to-peak line voltage into the tuned circuit. Another way to reduce the need for Z<sub>T</sub> is by placing another magnetic circuit in the signal path that relies on a high, but easily saturated, permeability to couple a primary and secondary winding - a toroidal transformer for example. Toroids cost more than Z<sub>T</sub>.

Use an avalanche diode designed specifically for transient suppression — they have orders of magnitude higher pulse

power capability than standard avalanche diodes rated for equal DC dissipation. Metal oxide varistors have not proven useful because of their inferior clamping coefficient and are not recommended. Specifications for an example minimum diode are given in *Figure 13*.

| Glode are given in Figure 13.    |                 |

|----------------------------------|-----------------|

| Breakdown Voltage                | . 44-49V @ 1 mA |

| Maximum Leakage                  | 1μA @ 40V       |

| Capacitance                      | 300 pF @ BV     |

| Maximum Clamp Voltage            | 64.5V @ 7.8A    |

| Peak Non-Repetitive Pulse Power  | 10 kW for 1 μs  |

| (REA Standard Exponential Pulse) |                 |

FIGURE 13. Key specifications for a recommended transient suppressor Z<sub>T</sub> available from General Semiconductor, 2001 West Tenth Place, Tempe, AZ 85281, 602–968-3101, part no. SA40A

### $R_T$

Surge Current

$R_T$  acts as a voltage divider with  $Z_T$ , absorbing transient energy that attempts to pull the Carrier Input pin above 44V. Make the resistor a carbon composition 1/4W. When experiments discharging  $C_C$  charged to the peak-to-peak 620V AC thru a  $1\Omega$  power line were carried out, film resistors blew open-circuit.

#### Dτ

This Schottky diode is placed in parallel with the CCT chip's substrate diode to pass the majority of the current drawn from ground when the Carrier Input or Carrier Output is pulled below ground by a larger-than-twice-the supply-swing on the tank. Note that  $Z_{\rm T}$  is in parallel with the substrate diode, but is ineffective due to its high forward voltage drop and high diffusion capacitance caused by its low forward speed. Tests proved that a 1N5818 kept a receive-path functional with a 20X boost transmitter with a 7:1 transformer attempted to swing the receiver's Carrier I/O to  $\pm$ 100V (300 mA peak ground current in the receiver). Without  $D_{\rm T}$ , the receiver momentarily stops functioning at a 100 times lower ground current.

This diode is not needed if the Carrier 1/O never swings below ground. If your CCT systems all run on the same regulated voltage with all matched transformers and turns ratios, it is not needed. Otherwise, it is.

#### THE RECEIVER

The receiver and transmitter share components  $C_C$ ,  $T_1$ ,  $C_Q$ ,  $R_T$ ,  $Z_T$ ,  $C_O$ ,  $R_O$ , and peripheral supply and bias components that are not in need of change for RX mode operation. Values for the balance of the components are now found.

### Line-Frequency Rejection

To use the ultimate sensitivity of the device, fully 110 dB of 115 V, 60 Hz attenuation is required between the line and the limiter amplifier output. Using the circuit topology of Figure 4, the combined attenuation of the C<sub>C</sub>/T<sub>1</sub> highpass, the tuned transformer, and the bandpass filter attenuation of the limiter amplifier give far more line rejection than the above-stated minimum. However, if some other CCT line coupling circuit is used, line rejection will become important to the system designer.

Receiver input power supply rejection (PSRR) and commonmode rejection (CMRR) are one-in-the-same using the supply-referenced signal input of *Figure 4*. Ripple swings both differential inputs of the Norton amp. equally, while the single-ended input signal swings only the positive input. Overall PSRR consists of the input CMRR (set by the input stage component matching) and the ripple-frequency attenuation of the input amplifier bandpass response that passes carrier frequency but stops low frequencies. A typical 1% resistor and 1 mV n-p-n mirror offsets give 26 dB of attenuation, the bandpass gives 54 dB 120 Hz attenuation, for an overall 80 dB PSRR to allow tens of volts of ripple before impacting ultimate sensitivity.

#### CC

A value was chosen earlier. Knowing  $T_1$ 's secondary inductance allows a check of LC line attenuation using Figure 14.

#### C

70A for 1/120s

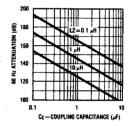

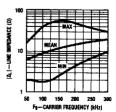

The Norton input limiter amplifier has a bandpass filter for enhanced receiver selectivity, noise immunity, and line frequency rejection. The nominal response curve for  $F_O=50\,$  kHz is shown in Figure~15. The 300 kHz pole is fixed. The 50 kHz pole is set by  $C_L$ 's value. After  $C_L$  is found, the resulting line frequency attenuation is found for the bandpass filter.

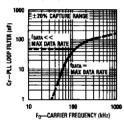

Use *Figure 15* to find a C<sub>L</sub> value given for F<sub>O</sub>. The approximate line frequency attenuation of the bandpass filter may then be found in *Figure 16*. *Figure 15* returns a value for C<sub>L</sub> 33% larger than nominal, giving a low frequency pole 33% low to allow for component tolerances.

TL/H/6750-15

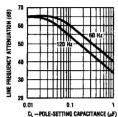

FIGURE 14. The 60 Hz line rejection of the highpass filter made up of C<sub>C</sub> and T<sub>1</sub>'s line-side winding (neglecting capacitive coupling)

FIGURE 15. Given F<sub>O</sub>, C<sub>L</sub> is found. Also shown is the input amplifier's small signal amplitude response

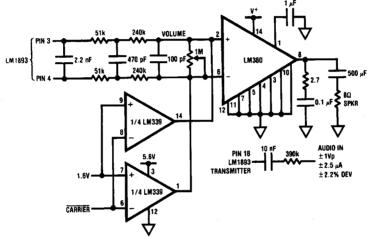

#### C<sub>F</sub> and R<sub>F</sub>

These phase-locked loop (PLL) loop filter components remove some of the noise and most of the  $2F_{O}$  components present in the demodulated differential output voltage signal from the phase detector. They affect the PLL capture range, loop bandwidth, damping, and capture time. Because the PLL has an inherent loop pole due to the integrator action of the ICO (via  $C_{O}$ ), the loop pole set by  $C_{F}$  and the zero set by  $R_{F}$  gives the loop filter a classical 2nd-order response.

TL/H/6750-18

FIGURE 16. The Norton-input limiter amplifier bandpass filter line-frequency signal attenuation given C<sub>L</sub>

TL/H/6750-19

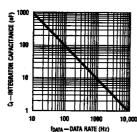

FIGURE 17. Find C<sub>F</sub> given F<sub>O</sub>. Figure 19 gives the maximum data rate

No  $C_F$  and  $R_F$  give the most stable PLL with the fastest response. Large  $C_F$ 's with a too-small  $R_F$  cause PLL loop instability leading to poor capture range and poor step response or oscillation.

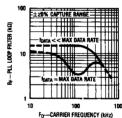

Calculation of  $C_F$  and  $R_F$  is quite difficult, involving not only the 2nd-order loop step response, but also the PLL non-dominant poles, the tuned transformer stepped-frequency response, and the RC lowpass step response (for data rates approaching 1 kHz).  $C_F$  and  $R_F$  values are best found empirically. Tolerance is not critical. Component values are selected to give the best possible impulse noise rejection while preserving a  $\pm 20\%$  capture range and wide stability margin. Figures 17 and 18 give  $C_F$  and  $R_F$  values versus  $F_{O_F}$  where "fDATA < MAX DATA RATE" means that fDATA should be less than the maximum data rate, in kHz, from Figure 19 divided by 10.

Note that  $C_F$  and  $R_F$  are a function of data rate only for high data rates and are not plotted against data rate - as one might expect. The reason for this is important to understand if the CCT system designer wishes to find  $C_F$  and  $R_F$  empirically. Data signal is, loosely speaking, passed through the PLL loop and is therefore potentially attenuated if the loop bandwidth is on the order of the 3rd harmonic of the data rate, or less. Overall loop bandwidth is held as low as possible for maximum noise rejection while passing the data. Loop bandwidth is roughly proportional to the geometric mean of the unfiltered loop bandwidth and the filter pole set by  $C_F$ . Therefore,  $C_F$  is related to data rate. Unfortunately, the loop capture range falls to critically low values when large enough values of  $C_F$  are used to reduce loop bandwidth down to the 100's of Hz range, for low data rates. The

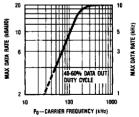

obvious way out is to then reduce the unfiltered loop bandwidth. That bandwidth is approximately proportional to the value of  $C_O$ . For a fixed  $F_O$ , unfiltered loop bandwidth reduction requires a larger  $C_O$  and larger control current. With this chip, changing the control current is not allowed. So one is forced to choose a  $C_F/R_F$  combination with some minimum capture range, say  $\pm 20\%$ , that is within some guardband from the point of loop instability. Happily, impulse noise tends to last only fractions of a millisecond so that the lack of low bandwidth loop response with low data rates is not a heavy penalty. As long as there is adequate capture range, the impulse noise filter performs admirably. Note that reducing  $F_O$  will reduce the no-filter loop bandwidth, and indeed the maximum data rate falls below the limit set by the RC lowpass filter as  $F_O$  falls below 100 kHz (*Figure 19*).

The tuned transformer characteristics will affect the demodulated data waveform more than  $C_F$  and  $R_F$  at low data rates. Tank Q and off-tuning will affect overshoot during the FSK frequency steps. This is a property of tuned circuits, The maximum data rate of Figure~19 is measured from the receiver input to the Data Out and does not include the data bandwidth reducing effects of  $T_L$ .

#### CM

Capacitor  $C_M$  stores a voltage corresponding to a correction factor required to cancel the phase detector differential output DC offsets. The stored voltage is  $\frac{5}{6}$  of the DC offset plus some bias level of about 2.2 V. A large  $C_M$  value increases the time required to bias-up the receive path at the beginning of transmission. A large  $C_M$  does filter well and store its bias voltage long. Because of the initial random charge of  $C_M$ , the receiver must be given a data transition to charge to the proper bias voltage. Therefore, reducing  $C_M$ 's value to one that may be charged in less than 2 bit-times will not save biasing time and is not recommended.

TL/H/6750-20

FIGURE 18. Find R<sub>F</sub> given F<sub>O</sub> with F<sub>DATA</sub> a parameter

TL/H/6750-21

FIGURE 19. The maximum data rate versus  $F_O$  using loop filter components optimized for max. noise performance while retaining a min.  $\pm$  20% capture range (large signal)

Use Figure 20 to find  $C_M$ 's value knowing  $f_{DATA}$ , assuming the standard 2 bit receive charge time is desired. The cap. value and TC are not critical, but the capacitor should have low leakage.

toata — DATA RATE (Hz) TL/H/6750-22 IRE 20. Size C<sub>M</sub> assuming a 2 bit-time

FIGURE 20. Size C<sub>M</sub> assuming a 2 bit-time receive bias time

C

The impulse noise filter integrator capacitor  $C_l$  is used to disallow the passage of any pulse shorter than the integrator charge time. That charge time, set to a nominal  $\frac{1}{2}$  bit time, is the time required for a  $\pm 50~\mu\text{A}$  charge current to swing  $C_l$  over a 2  $V_{BE}$  range. Charge time under worst case conditions must never be greater than a bit time since no signal could then pass. Using a  $\pm 10\%$  capacitor, full junction temperature range, and full specified current range, a maximum nominal charge time of  $\frac{1}{2}$  bit is recommended. Figure 21 gives  $C_l$  versus data rate under those conditions.

#### RÇ

The collector pull-up resistor is sized to supply adequate pull-up current drive and speed while preserving adequate output low current drive.

TL/H/6750-24

FIGURE 21. Impulse noise filter cap.  $C_1$  versus  $F_{DATA}$  where the charge time is  $\frac{1}{2}$  bit time

$Z_A$

The 5.1V silicon zener diode  $Z_A$  is required when a short RX-to-TX switch-over time is needed at the same time that the chip is operating in the RX mode with a pin 10 input signal swing approaching or exceeding twice the supply voltage. Predominant causes of these large swings impinging on the RX input are: 1) a transmitter's supply voltage higher than the receiver's supply voltage, 2) a TX and RX pair that are electrically close, or, 3) a higher RX  $T_1$  step-up turns ratio than the TX  $T_1$  step-down ratio.

Normally, when in the RX mode with small incoming signal on pin 10, the ALC remains off with pin 7 at a 6V ( $V_Z - 2V_{BE}$ ) bias voltage.  $C_A$  is then charged to 6V. TX mode may then be selected with 6V on  $C_A$  allowing 100% TX power to pump  $T_1$ 's tuned circuit, and so the AC line, quickly for fast RX-to-TX switch time. As TX output swing increases so that pin 10 swings below  $V_{ALC}$  (4.7V typically), that ALC activates to charge  $C_A$  to about 6.6V to reduce TX output drive. However, if in the RX mode pin 10 ever swings below  $V_{ALC}$ ,  $C_A$  will charge to above 6.6V. Now, when the TX mode is selected with  $C_A$  at 6.6V, somewhere from 0 to 100% TX output drive is available to pump  $T_1$ 's tuned circuit resulting in a slower rising line signal - effectively reducing the RX-to-TX switch time.

Use a 5.1V  $Z_A$  driven by a 0 to 0.8V logic low signal to guarantee over-temp. operation.  $R_A$  must be in series with  $Z_A$  to limit current flow and should never fall below 1 k $\Omega$ . If  $R_A$  is less than 1 k $\Omega$ , then put a 2 k $\Omega$  resistor in series with  $Z_A$ . Logic high voltages above 10V will cause current flow into pin 7 that must be limited to 1 mA (with  $R_A$  or a series R).

# **Breadboarding Tips**

During CCT system evaluation, some techniques listed below will simplify certain measurements.

- Use caution when working on this circuit dangerous line voltages may be present.

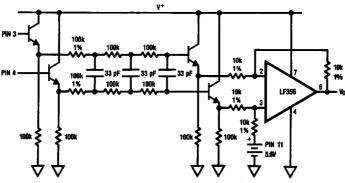

- When evaluating PLL operation, offset cancel circuit operation, and loop filter values, use the filter of Figure 22 to view the demodulated signal minus the 2F<sub>O</sub> and noise components. This filter models the RC lowpass filter on chip.

TL/H/6750-25

FIGURE 22. Circuit to view the differential demodulated data signal, minus the noise and 2F<sub>O</sub> components, conveniently with a single-ended gain-of-one output

### **Breadboarding Tips** (Continued)

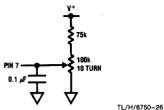

- When evaluating CCT system noise performance on a real power line, it is desirable to vary the signal amplitude to the receiver. This is not easy. An in-line lineproof L-pad is fine except that the line impedance is unknown and variable and so the L-pad will rarely match. Instead, the power output of a chip transmitter may be controlled using the circuit of Figure 23. This circuit controls the ALC.

- It is sometimes desirable to place impulse noise on the line. A simple light dimmer with a 100 W light bulb load produces representative impulse noise.

- Do not allow peak currents of over 1 A through the 5.6 V

Zener. In other words, don't short charged capacitors into this low-impedance device. Take care not to momentarily short pins 10 and 11 chip damage may result.

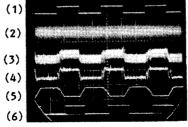

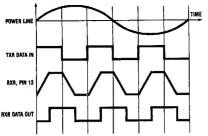

- Figure 24 shows some typical signals beginning with serial data transmitted to received signal.

# **Tuning Procedure**

This procedure applies to circuits similar to Figure 4 LM1893 or LM2893 circuit.

First, trim  $F_O$  by putting the chip in the TX mode, setting a logical high data input, and measuring the TX high frequency, 1.022  $F_O$ , on the Carrier I/O using these steps:

- 1. Take pin 17 to a logic low.

- 2. Take pin 5 to a logic high.

- 3. Place a counter on pin 10.

- 4. Adjust  $R_O$  on pin 18 for  $F = 1.022F_O$ .

Second, the line transformer is tuned. The chip is placed in the TX mode, a resistive line load is connected to disable the ALC by reducing tank voltage swing below its limit. FSK data is then passed through the tank so that the tank envelope may be adjusted for equal amplitude for high and low data frequency.

- 1. Take pin 5 to a logic high.

- Place a logic-level square wave at or below the receiver's maximum data rate on pin 17.

- 3. Temporarily place a 330  $\Omega$  resistor across the tank.

- 4. Place a scope on pin 10.

- Adjust the transformer slug for the least envelope modulation.

In lieu of the 330  $\Omega$  resistive load, T<sub>1</sub> may be coupled to the power line to better simulate actual load and tank pull conditions during tank tuning. Alternatively, a passive network

representing an average line impedance may be connected to the line side of T<sub>1</sub>. The circuit of *Figure 23* should then be used to defeat the leveling effect of the ALC.

FIGURE 23. A means of transmitter output amplitude control is shown

### **Thermal Considerations**

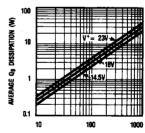

It is desirable to place the largest possible signal on the power line for maximum range, limited only by the chip power dissipation and maximum junction temperature TJ. The falling output power at elevated T<sub>J</sub> allows a more optimal power output - high power at low T<sub>J</sub> and lower power at high T<sub>.</sub>I for chip self-protection. However, it is still possible to exceed the maximum T<sub>J</sub> within the specified ambient temperature limit (TA = 85°C) under worst case conditions of 100% TX duty cyle, high supply, shorted load, poor PC board layout (with small copper foil area), and an above nominal current part. Under those conditions, a part may dissipate 2140 mW, reaching a T<sub>1</sub> = 170°C worst-case (admittedly a rare occurrence). Proper system design includes the measurement or calculation of T<sub>J</sub> max, to guarantee function under worst-case operation. Like all devices with failure modes modeled by the Arrhenius model, the high chip reliability is further enhanced by keeping the die temperature mercifully below the absolute maximum rating.

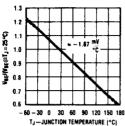

A direct method of measuring operating junction temperature is to measure the  $V_{BE}$  voltage on pin 18, which is always available under all operating modes. The graph of Figure 25 may be used to find  $T_J$ , knowing  $V_{BE}$  at the operating point in question and  $V_{BE}$  at  $T_A = T_J = 25^{\circ}\text{C}$ .  $V_{BE}$  is found by powering up a chip (in RX mode) that has been dissipating zero power at some  $T_A$  for some time and measuring  $V_{BE}$  in less than 1 s (for better than 5°C accuracy).

Alternately, T<sub>J</sub> may be calculated using:

$$T_{J} = T_{A} + \theta_{JA} P_{D} \tag{1}$$

where  $\theta_{JA}$  is 75°C/W for the plastic (N) package using a socket. That  $\theta_{JA}$  value is for a high confidence level; nomi-

10 V/Div.

10 mV/Div.

400 mV/Div.

200 mV/Div.

2 V/Div.

10 V/Div.

TL/H/6750~23

FiGURE 24. Oscillogram revealing signals at several important nodes under weak signal (0.5 mV<sub>RMS</sub>) conditions with SCR spikes on an otherwise quiet 115 V, 60 Hz power line. The signals are: 1) transmitted data, 2) RX carrier on the tuned transformer, 3) demodulated signal from the PLL after passing thru circuit of *Figure 22*, 4) signal after RC lowpass, 5) data at impulse noise filter integrator, and 6) received data. Horizontal scale is 10 ms per div.

# Thermal Considerations (Continued)

nal θ<sub>JA</sub> for an N package is 60°C/W, lower with good PC board layout. Since PD is a relatively strong function of TJ, an iterative solution process starting with an initial guess for T<sub>J</sub> is used. With the estimated T<sub>J</sub>, find the total supply current found in the typical performance characteristics.

TL/H/6750-27

FIGURE 25. TJ may be found by using the temperature coefficient of pin 18 VBE If VBE Is known at 25°C

# Transmit-To-Receive Switch-Over Time

An important figure-of-merit for a half-duplex CCT link, affecting effective data rate, is the TX-to-RX switch time TTB. Using the recommended component values gives this part a nominal 2 bit-time (1 bit time = 1/[2fDATA]) over a wide range of operating conditions, where the receiver requires 1 data transition. TTB cannot be decreased significantly but does increase as noise filtering, especially via C<sub>M</sub>, is increased. Impulse noise at switch, signals near the limiting sensitivity, poor FO match between receiver and transmitter because of poor trim or worst-case conditions, and the statistical nature of PLL signal acquisition may all contribute to increase T<sub>TR</sub> to possibly 4 bit-times.

TTR is lower when a pair of LM1893's handshake rapidly. The receiver was designed to "remember" the RX-mode DC operating points on C<sub>M</sub> and C<sub>F</sub> while in the TX mode. Under noisy worst case conditions, C<sub>M</sub> will discharge to the point of false operation after 35 bit-times in the TX mode (1400 bit times with no noise and a nominal part, fDATA = 180 Hz). T<sub>TR</sub> is about 0.8 ms (proportional to the selected FO) plus 1/2 bit-time.

The major components of TTR are described below for a nominal 125 kHz FO, 180 Hz fDATA, lightly-loaded tank with a Q of 20, and the circuit of Figure 4. The remote CCT has been operating in the TX mode with a 26.6 Vpp tank swing and is now selected as a receiver. An incoming signal requiring the ultimate receiver sensitivity immediately is placed on the line.

First, the tank stored energy at the transmit frequency must decay to a level below the 2.8 mVpp swing caused by the 0.14 mV<sub>RMS</sub> incoming line signal containing the information to be received.

decay time

$$= \frac{Q}{\pi F_O} \ln \left( \frac{V_1}{V_O} \right) =$$

$$\frac{20}{\pi \times 125\,000} \ln \left( \frac{26.6}{0.0028} \right) = 0.466 \, \text{ms} \qquad (2)$$

That is 0.47 ms of delay (proportional to I/F<sub>O</sub> and Q). Second, the PLL must acquire the signal; it must lock and settle. Acquisition time is statistical and may take any length of time, but average acquisition time depends on the loop filter components CF and RF and the difference in center frequencies,  $\Delta F_0$ , of the TX/RX pair. Using the recommended C<sub>F</sub> and R<sub>F</sub> (47 nF and 6.2 k $\Omega$ ) with a  $\pm 4.4\%$   $\Delta$ F $\alpha$ (a ± 100 mV DC offset on C<sub>F</sub> and R<sub>F</sub>), lock was measured to take less than 50 cycles of Fo. That is a 0.40 ms delay (proportional to 1/FO).

Acquisition is incomplete until the second order PLL loop settles. For the above-mentioned CF and RF, the loop natural frequency  $F_N$  and damping factor are found to be 2.3 kHz and 1.0 respectively. Settling to within ±25 mV of the ±100 mV DC offset change requires 2.7 periods of F<sub>N</sub>. or 1.2 ms (a function of CF and RF).

Third, the RC lowpass filter introduces a 0.12 ms delay.

Fourth,  $C_M$  must charge up to  $\pm (\frac{5}{6})100 = 83$  mV depending on the polarity of Fo. Borderline data squaring with zero noise immunity is possible with only  $\pm (\frac{5}{6})$  50 mV of charging. C<sub>M</sub> charge current is an asymptotic function approximated by assuming a 50 µA charge current and the full 83 mV charge voltage. C<sub>M</sub> charge time is then 1.7 ms (proportional to 1/fDATA).

Fifth, the impulse noise filter adds a 1/2 bit-time delay. Total TTR is 3.9 ms plus 1/2 bit-time for a total of 1.9 bit-times at 360 Baud.

### Receive-To-Transmit Switch-Over Time

Assume the chip has been in the RX mode and the TX mode is now selected. In less than 10 µs, full output current is exponentially building tank swing. 50% of full swing is achieved in less than 10 cycles - or under 80 µs at 125 kHz. In the same 10 us that the output amp went on, the phase detector and loop filter are disconnected and the modulator input is enabled. FSK modulation is produced in 10 µs after switching to TX mode.

# Power Line Impedance

Irrespective of how wide the limits on power line impedance Z<sub>i</sub> are placed, there are no quarantees. However, since the CCT design requires an estimate of the lowest expected line impedance Z<sub>LN</sub> encountered for the most efficient transmitter-to-line coupling, line impedance should be measured and Z<sub>L</sub> limits fixed to a given confidence level. Reasonable values for T1 turns ratio, loaded Q, and tank resonant frequency pull Fo may be found to enable a CCT system design that functions with the overwhelming majority of power

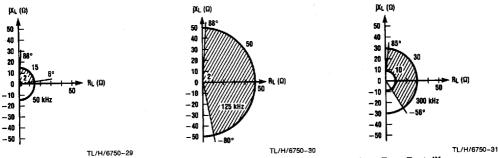

A limited sampling of Z<sub>L</sub> was made, during the LM1893 design, of residential and commercial 115V 60 Hz power line. Data was also drawn from the research of Nicholson and Malack (reference 1), among others, to produce Figures 26 and 27. All measured impedances are contained within the shaded portions of Figure 27. A nominal 3.5, 7.0 and 14  $\Omega$ Z<sub>LN</sub> is used throughout the application information with a nominal 45° phase angle (0° is sometimes used for simplici-

TL/H/8750-28

FIGURE 26. Measured line impedance range for residential and commercial 115V, 60 Hz lines

# Power Line Impedance (Continued)

FIGURE 27. Complex-plane plots of measured 115V, 60 Hz line impedance where  $Z_L = R_L + jX_L$

# **Power Line Attenuation**

The wiring in most US buildings is a flat 3 conductor cable called Amerflex, BX, or Romex. All referenced line impedances refer to hot-to-neutral impedances with a grounded center conductor. The cable has a 100  $\Omega$  characteristic impedance, a 125 kHz quarter-wavelength of 600 m (250 m at 300 kHz), and a measured 7 dB attenuation for a 50 m run with a 10  $\Omega$  termination. Generally, line loads may be treated as lumped impedances. Instrument line cords exhibit about 0.7  $\mu{\rm H}$  and 30 pF per meter.

Limited tests of CCT link range using this chip show extensive coverage while remaining on one phase of a distribution transformer (100's of m), with link failure often occuring across transformer phases or through transformers unless coupling networks are utilized. Total line attenuation allowed from full signal to limiting sensitivity is more than 70 dB. Typically, signal is coupled across transformer phases by parasitic winding capacitance, typically giving 40 dB attenuation between phased 115 V windings. Coupling capacitors may be installed for improved link operation across phases. Power factor correcting capacitor banks on industrial lines or filter capacitors across the power lines of some electronic gear short carrier signal and should be isolated with inductors. Increasing range is sometimes accomplished by electing to install the isolating inductors (Figure 28) and coupling capacitors, as well as by electing to use the boost option. Frequency translating or time division multiplexed repeaters will also increase range.

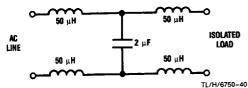

FIGURE 28. An isolation network to prevent: 1) noise from some device from polluting the AC line, and 2) to stop some low impedance device (measured at F<sub>o</sub>) from shorting carrier signal. Component values given as an example for F<sub>o</sub> = 125 kHz on residential power lines

# **The Coupling Transformer**

The design arrived at for  $T_1$  is the result of an unhappy compromise - but a workable one. The goals of 1) building

$T_1$  with a stable resonant frequency,  $F_Q$ , that is little affected by the de-tuning effect of the line impedance  $Z_L$ , and of 2) building a tightly line-coupled transformer for transmitted carrier with loose coupling for transients, are somewhat mutually exclusive. The tradeoffs are exposed in the following example for the CCT designer attempting a new boost-capable, or different core, transformer design.

The compromises are eased by separating the TX output and RX input in the LM2893. An untuned TX coupling transformer with only core coupling (not air-coupled solenoid windings) would employ a high permeability, high magnetic field, low loss, square saturating, toroidal core. The resonant RX path would be isolated from line-pull problems by a unilateral amplifier that operates at line voltages with much more than 110 dB of dynamic range, or by a capacitively coupled pulse transformer driving a unilateral amplifier and filter, for increased selectivity. See the LM2893-specific applications section.