# PART NUMBER AD624BD-G-ROCA

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

#### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### Precision Instrumentation Amplifier

**AD624**

#### 1.1 Scope.

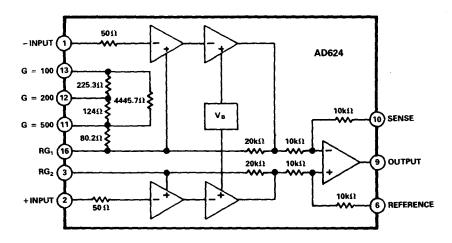

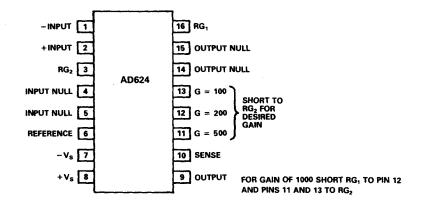

This specification covers the detail requirements for a programmable gain instrumentation amplifier. The gain equation is  $\frac{40,000}{R_G} + 1 \pm 20\%$  with external resistor gain programming.

#### 1.2 Part Number.

The complete part number per Table 1 of this specification is as follows:

Device

Part Number

-1

AD624SD/883B

#### 1.2.3 Case Outline.

See Appendix 1 of General Specification ADI-M-1000: package outline: D-16.

#### 1.3 Absolute Maximum Ratings. (T<sub>A</sub> = +25°C unless otherwise noted)

| Supply Voltage                           |  |

|------------------------------------------|--|

| Internal Power Dissipation               |  |

| Rated Operating Temperature Range        |  |

| Storage Temperature Range                |  |

| Lead Temperature Range (Soldering 10sec) |  |

#### 1.5 Thermal Characteristics.

Thermal Resistance  $\theta_{JC} = 22^{\circ}\text{C/W}$  $\theta_{JA} = 95^{\circ}\text{C/W}$

### AD624 — SPECIFICATIONS

|                            |                       |        | Design<br>Limit | Sub<br>Group | Sub | Sub<br>Group |                                          |              |

|----------------------------|-----------------------|--------|-----------------|--------------|-----|--------------|------------------------------------------|--------------|

| Test                       | Symbol                | Device | @+25°C          | 1            | 2,3 | 4            | Test Condition <sup>1</sup>              | Units        |

| Gain Error 1               | GE <sub>1</sub>       | -1     | 0.05            | 0.05         |     |              | $G=1, V_O=\pm 10V$                       | ±% max       |

| Gain Error 100             | GE <sub>100</sub>     | -1     | 0.25            | 0.25         |     |              | $G = 100, V_O = \pm 10V$                 | ±% max       |

| Gain Error 200             | GE <sub>200</sub>     | -1     | 0.5             | 0.5          |     |              | $G = 200, V_O = \pm 10V$                 | ±% max       |

| Gain Error 500             | GE <sub>500</sub>     | -1     | 0.5             | 0.5          |     |              | $G = 500, V_O = \pm 10V$                 | ±% max       |

| Gain Error Drift 1         | TCGE <sub>1</sub>     | -1     | 5               |              |     |              | $G=1, V_O=\pm 10V$                       | ± ppm/°C max |

| Gain Error Drift 100       | TCGE <sub>100</sub>   | -1     | 10              |              |     |              | $G=100, V_O=\pm 10V$                     | ± ppm/°C max |

| Gain Error Drift 200       | TCGE <sub>200</sub>   | -1     | 10              |              |     |              | $G = 200, V_O = \pm 10V$                 | ± ppm/°C max |

| Gain Error Drift 500       | TCGE <sub>500</sub>   | -1     | 15              |              |     |              | $G = 500, V_O = \pm 10V$                 | ± ppm/°C max |

| Input Offset Voltage       | V <sub>OSI</sub>      | -1     | 75              | 75           |     |              | $V_{IN} = 0V$                            | ± μV max     |

| Input Offset Voltage Drift | TCV <sub>OSI</sub>    | -1     | 2               |              | 2   |              | $G = 500, V_{IN} = 0V$                   | ±μV/°C max   |

| Output Offset Voltage      | Voso                  | -1     | 3               | 3            |     |              | $V_{IN} = 0V$                            | ± mV max     |

| Output Offset Drift        | TCV <sub>OSO</sub>    | -1     | 50              |              | 50  |              | $G=1, V_{IN}=0V$                         | ± μV/°C max  |

| Input Bias Current         | IB                    | -1     | 50              | 50           |     |              | G=1                                      | ± nA max     |

| Input Offset Current       | Ios                   | -1     | 35              | 35           |     |              | G=1                                      | ± nA max     |

| Common-Mode Rejection      | +CMRR <sub>1</sub>    | -1     | 70              | 70           |     |              | $G = 1, V_{IN} = 0V \text{ to } + 10V$   | dB min       |

| Common-Mode Rejection      | -CMRR <sub>1</sub>    | -1     | 70              | 70           |     |              | $G = 1$ , $V_{IN} = 0V$ to $-10V$        | dB min       |

| Common-Mode Rejection      | + CMRR <sub>100</sub> | -1     | 100             | 100          |     |              | $G = 100, V_{IN} = 0V \text{ to } + 10V$ | dB min       |

| Common-Mode Rejection      | -CMRR <sub>100</sub>  | -1     | 100             | 100          |     |              | $G = 100, V_{IN} = 0V \text{ to } -10V$  | dB min       |

| Common-Mode Rejection      | +CMRR <sub>200</sub>  | -1     | 100             | 100          |     |              | $G = 200, V_{IN} = 0V \text{ to } + 10V$ | dB min       |

| Common-Mode Rejection      | -CMRR <sub>200</sub>  | - 1    | 100             | 100          |     |              | $G = 200, V_{IN} = 0V \text{ to } -10V$  | dB min       |

| Common-Mode Rejection      | +CMRR <sub>500</sub>  | -1     | 110             | 110          |     |              | $G = 500, V_{IN} = 0V \text{ to } + 10V$ | dB min       |

| Common-Mode Rejection      | -CMRR <sub>500</sub>  | -1     | 110             | 110          |     |              | $G = 500, V_{IN} = 0V \text{ to } -10V$  | dB min       |

| Power Supply Current       | $I_{CC}$              | -1     | 5               | 5            |     |              | G=1                                      | mA max       |

| Power Supply Rejection     | PSRR <sub>1</sub>     | -1     | 75              | 75           |     |              | $G = 1, V_S = \pm 12V, \pm 15V$          | dB min       |

| Power Supply Rejection     | PSRR <sub>100</sub>   | -1     | 105             | 105          |     |              | $G = 100, V_S = \pm 12V, \pm 15V$        | dB min       |

| Power Supply Rejection     | PSRR <sub>200</sub>   | -1     | 105             | 105          |     |              | $G = 200, V_S = \pm 12V, \pm 15V$        | dB min       |

| Power Supply Rejection     | PSRR <sub>500</sub>   | -1     | 110             | 110          |     |              | $G = 500, V_S = \pm 12V, \pm 15V$        | dB min       |

Table 1.

NOTE  $^{1}V_{S} = \pm 15V, \ R_{L} = 2k\Omega$  unless otherwise specified.

#### 3.2.1 Functional Block Diagram and Terminal Assignments.

Pin Assignments

#### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group (49).

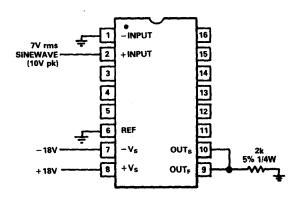

#### 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).