# HC-5502B

August 2003

```

FN2884.7

```

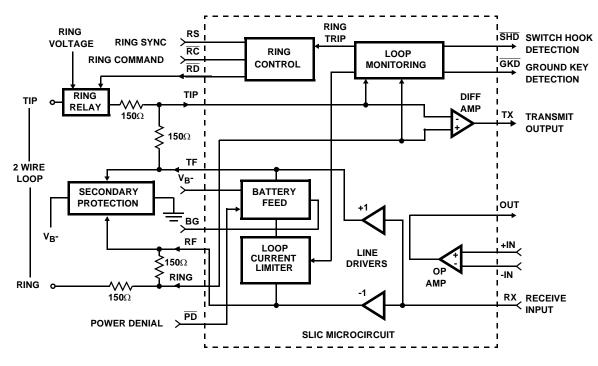

# EIA/ITU PABX SLIC with 30mA Loop Feed

The Intersil SLIC incorporates many of the BORSHT functions on a single IC chip. This includes DC battery feed, a ring relay driver, supervisory and hybrid functions. This device is designed to maintain transmission performance in the presence of externally induced longitudinal currents. Using the unique Intersil dielectric isolation process, the SLIC can operate directly with a wide range of station battery voltages.

The SLIC also provides selective denial of power. If the PBX system becomes overloaded during an emergency, the SLIC will provide system protection by denying power to selected subscriber loops.

The Intersil SLIC is ideally suited for the design of new digital PBX systems, by eliminating bulky hybrid transformers.

## Part Number Information

| PART NUMBER | TEMP. RANGE<br>( <sup>o</sup> C) | PACKAGE    | PKG. DWG. # |

|-------------|----------------------------------|------------|-------------|

| HC3-5502B-5 | 0 to 75                          | 24 Ld PDIP | E24.6       |

| HC4P5502B-5 | 0 to 75                          | 28 Ld PLCC | N28.45      |

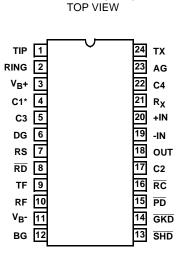

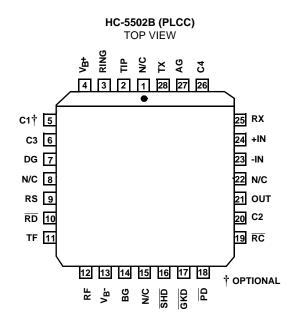

# Pinouts

HC-5502B (PDIP)

## Features

- Capable of 12V or 5V (V<sub>B</sub>+) Operation

- Monolithic Integrated Device

- DI High Voltage Process

- Compatible With Worldwide PBX Performance Requirements

- Controlled Supply of Battery Feed Current for Short Loops (30mA)

- Internal Ring Relay Driver

- Low Power Consumption During Standby

- Switch Hook, Ground Key and Ring Trip Detection Functions

- Selective Denial of Power to Subscriber Loops

## Applications

- Solid State Line Interface Circuit for Analog and Digital PBX Systems

- Direct Inward Dial (DID) Trunks

- Voice Messaging PBXs

- Related Literature

- AN549, The HC-5502S/4X Telephone Subscriber Line Interface Circuits (SLIC)

- AN571, Using Ring Sync with HC-5502A and HC-5504  $\,$  SLICs  $\,$

### Absolute Maximum Ratings (Note 1)

Supply Voltage

| (V <sub>B</sub> -)                     | <br>30 to 0.5V |

|----------------------------------------|----------------|

| (V <sub>B</sub> +)                     | <br>).5 to 15V |

| (V <sub>B</sub> + - V <sub>B</sub> -)  | <br>75V        |

| Relay Drive Voltage (V <sub>RD</sub> ) | <br>).5 to 15V |

## **Operating Conditions**

| Relay Driver Voltage (V <sub>RD</sub> )                                     |

|-----------------------------------------------------------------------------|

| Positive Supply Voltage (V <sub>B</sub> +) 4.75V to 5.25V or 10.8V to 13.2V |

| Negative Supply Voltage (V <sub>B</sub> -)                                  |

| High Level Logic Input Voltage 2.4V                                         |

| _ow Level Logic Input Voltage0.6V                                           |

| $\_$ oop Resistance (R <sub>L</sub> )                                       |

| Operating Temperature Range                                                 |

| HC-5502B-50 <sup>o</sup> C to 75 <sup>o</sup> C                             |

## **Thermal Information**

| Thermal Resistance (Typical, Note 2)                                | θ <sub>JA</sub> ( <sup>o</sup> C/W)  |

|---------------------------------------------------------------------|--------------------------------------|

| PDIP Package                                                        | 65                                   |

| PLCC Package                                                        | 65                                   |

| Maximum Junction Temperature (Hermetic Package) .                   | 175 <sup>0</sup> C                   |

| Maximum Junction Temperature (Plastic Package)                      |                                      |

| Maximum Storage Temperature Range                                   | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)<br>(PLCC - Lead Tips Only) | 300 <sup>0</sup> C                   |

## **Die Characteristics**

| Transistor Count       |

|------------------------|

| Diode Count            |

| Die Dimensions         |

| Substrate PotentialVB- |

| Process Bipolar-DI     |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. Absolute maximum ratings are limiting values, applied individually, beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied.

- 2.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

# **Electrical Specifications** Unless Otherwise Specified, $V_{B^-} = -48V$ , $V_{B^+} = 12V$ and 5V, AG = BG = DG = 0V, Typical Parameters $T_A = 25^{\circ}C$ . Min-Max Parameters are Over Operating Temperature Range

| PARAMETER                        | TEST CONDITIONS                                                      | MIN  | TYP | MAX  | UNITS       |

|----------------------------------|----------------------------------------------------------------------|------|-----|------|-------------|

| On Hook Power Dissipation        | I <sub>LONG</sub> = 0, V <sub>B</sub> + = 12V (Note 3)               | -    | 135 | 235  | mW          |

| Off Hook Power Dissipation       | $R_L = 600\Omega$ , $I_{LONG} = 0$ , $V_B + = 12V$ (Note 3)          | -    | 450 | 690  | mW          |

| Off Hook I <sub>B</sub> +        | $R_L = 600\Omega$ , $I_{LONG} = 0$ , $T_A = -40^{\circ}C$ (Note 3)   | -    | -   | 6.0  | mA          |

| Off Hook I <sub>B</sub> +        | $R_L = 600\Omega$ , $I_{LONG} = 0$ , $T_A = 25^{\circ}C$ (Note 3)    | -    | -   | 5.3  | mA          |

| Off Hook I <sub>B</sub> -        | $R_{L} = 600\Omega, I_{LONG} = 0 $ (Note 3)                          | -    | -   | 39   | mA          |

| Off Hook Loop Current            | $R_{L} = 1200\Omega, I_{LONG} = 0$ (Note 3)                          | -    | 21  | -    | mA          |

| Off Hook Loop Current            | $R_L$ = 1200Ω, $V_B$ - = -42V, $I_{LONG}$ = 0, $T_A$ = 25°C (Note 3) | 17.5 | -   | -    | mA          |

| Off Hook Loop Current            | R <sub>L</sub> = 200Ω, I <sub>LONG</sub> = 0 (Note 3)                | 25.5 | 30  | 34.5 | mA          |

| Fault Currents                   |                                                                      |      |     |      |             |

| TIP to Ground                    |                                                                      | -    | 14  | -    | mA          |

| RING to Ground                   |                                                                      | -    | 47  | -    | mA          |

| TIP to RING                      |                                                                      | -    | 30  | -    | mA          |

| TIP and RING to Ground           |                                                                      | -    | 47  | -    | mA          |

| Ring Relay Drive V <sub>OL</sub> | I <sub>OL</sub> = 62mA                                               | -    | 0.2 | 0.5  | V           |

| Ring Relay Driver Off Leakage    | $V_{RD} = 12V, \overline{RC} = 1 = HIGH, T_A = 25^{\circ}C$          | -    | -   | 100  | μΑ          |

| Ring Trip Detection Period       | $R_{L} = 600\Omega, T_{A} = 25^{o}C$                                 | -    | 2   | 3    | Ring Cycles |

| Switch Hook Detection Threshold  | $\overline{SHD} = V_{OL}$                                            | 10   | -   | -    | mA          |

|                                  | SHD = V <sub>OH</sub>                                                | -    | -   | 5    | mA          |

# **Electrical Specifications** Unless Otherwise Specified, $V_{B^-} = -48V$ , $V_{B^+} = 12V$ and 5V, AG = BG = DG = 0V, Typical Parameters $T_A = 25^{\circ}C$ . Min-Max Parameters are Over Operating Temperature Range (Continued)

| PARAMETER                                             | TEST CONDITIONS                                                                        | MIN  | TYP   | MAX   | UNITS             |

|-------------------------------------------------------|----------------------------------------------------------------------------------------|------|-------|-------|-------------------|

| Ground Key Detection Threshold                        | $\overline{\text{GKD}} = \text{V}_{\text{OL}}$                                         | 20   | -     | -     | mA                |

|                                                       | GKD = V <sub>OH</sub>                                                                  | -    | -     | 10    | mA                |

| Loop Current During Power Denial                      | R <sub>L</sub> = 200Ω                                                                  | -    | ±2    | -     | mA                |

| Dial Pulse Distortion                                 |                                                                                        | 0    | -     | 5     | ms                |

| Receive Input Impedance                               | (Note 4)                                                                               | -    | 110   | -     | kΩ                |

| Transmit Output Impedance                             | (Note 4)                                                                               | -    | 10    | 20    | Ω                 |

| 2-Wire Return Loss<br>SRL LO                          | Referenced to $600\Omega$ +2.16µF (Note 4)                                             | -    | 15.5  | -     | dB                |

| ERL                                                   | _                                                                                      | -    | 24    | -     | dB                |

| SRL HI                                                | _                                                                                      | -    | 31    | -     | dB                |

| Longitudinal Balance<br>2-Wire Off Hook               | 1V <sub>RMS</sub> 200Hz - 3400Hz, (Note 4)<br>IEEE Method                              | 58   | 65    | -     | dB                |

| 2-Wire On Hook                                        | $- 0^{\circ}C \le T_{A} \le 75^{\circ}C$                                               | 60   | 63    | -     | dB                |

| 4-Wire Off Hook                                       |                                                                                        | 50   | 58    | -     | dB                |

| Low Frequency Longitudinal Balance                    | R.E.A. Method, (Note 4)<br>$R_L = 600\Omega$ ,<br>$0^{\circ}C \le T_A \le 75^{\circ}C$ | -    | -     | 23    | dBrnC             |

|                                                       |                                                                                        | -    | -     | -67   | dBm0p             |

| Insertion Loss<br>2-Wire to 4-Wire, 4-Wire to 2-Wire  | At 1kHz, 0dBm Input Level, Referenced $600\Omega$                                      | -    | ±0.05 | ±0.2  | dB                |

| Frequency Response                                    | 200 - 3400Hz Referenced to Absolute<br>Loss at 1kHz and 0dBm Signal Level (Note 4)     | -    | ±0.02 | ±0.05 | dB                |

| Idle Channel Noise                                    | (Note 4)                                                                               | -    | 1     | 5     | dBrnC             |

| 2-Wire to 4-Wire, 4-Wire to 2-Wire                    |                                                                                        | -    | -89   | -85   | dBm0p             |

| Absolute Delay<br>2-Wire to 4-Wire, 4-Wire to 2-Wire  | (Note 4)                                                                               | -    | -     | 2     | μs                |

| Trans Hybrid Loss                                     | Balance Network Set Up for $600\Omega$<br>Termination at 1kHz                          | 36   | 40    | -     | dB                |

| Overload Level                                        | V <sub>B</sub> + = 5V                                                                  | 1.5  | -     | -     | V <sub>PEAK</sub> |

| 2-Wire to 4-Wire, 4-Wire to 2-Wire                    | V <sub>B</sub> + = 12V                                                                 | 1.75 | -     | -     | V <sub>PEAK</sub> |

| Level Linearity<br>2-Wire to 4-Wire, 4-Wire to 2-Wire | At 1kHz, (Note 4) Referenced to 0dBm Level<br>+3 to -40dBm                             | -    | -     | ±0.05 | dB                |

|                                                       | -40 to -50dBm                                                                          | -    | -     | ±0.1  | dB                |

|                                                       | -50 to -55dBm                                                                          | -    | -     | ±0.3  | dB                |

# **Electrical Specifications** Unless Otherwise Specified, $V_{B^-} = -48V$ , $V_{B^+} = 12V$ and 5V, AG = BG = DG = 0V, Typical Parameters $T_A = 25^{\circ}C$ . Min-Max Parameters are Over Operating Temperature Range (Continued)

| PARAMETER                                                  | TEST CONDITIONS                                     | MIN | TYP | MAX  | UNITS |

|------------------------------------------------------------|-----------------------------------------------------|-----|-----|------|-------|

| Power Supply Rejection Ratio<br>V <sub>B</sub> + to 2-Wire | 30 - 60Hz,<br>R <sub>L</sub> = 600Ω,<br>(Note 4)    | 15  | _   | -    | dB    |

| V <sub>B</sub> + to Transmit                               |                                                     | 15  | -   | -    | dB    |

| V <sub>B</sub> - to 2-Wire                                 |                                                     | 15  | -   | -    | dB    |

| V <sub>B</sub> - to Transmit                               |                                                     | 15  | -   | -    | dB    |

| V <sub>B</sub> + to 2-Wire                                 | 200 - 16kHz,                                        | 30  | -   | -    | dB    |

| V <sub>B</sub> + to Transmit                               | $R_L = 600\Omega$                                   | 30  | -   | -    | dB    |

| V <sub>B</sub> - to 2-Wire                                 |                                                     | 30  | -   | -    | dB    |

| V <sub>B</sub> - to Transmit                               |                                                     | 30  | -   | -    | dB    |

| Logic Input Current (RS, RC, PD)                           | $0V \le V_{IN} \le 5V$                              | -   | -   | ±100 | μA    |

| Logic Inputs<br>Logic '0' V <sub>IL</sub>                  |                                                     | -   | -   | 0.8  | V     |

| Logic '1' V <sub>IH</sub>                                  |                                                     | 2.0 | -   | 5.5  | V     |

| Logic Outputs<br>Logic '0' V <sub>OL</sub>                 | I <sub>LOAD</sub> 800μA, V <sub>B</sub> + = 12V, 5V | -   | 0.1 | 0.5  | V     |

| Logic '1' V <sub>OH</sub>                                  | I <sub>LOAD</sub> 80μA, V <sub>B</sub> + = 12V      | 2.7 | 5.0 | 5.5  | V     |

|                                                            | I <sub>LOAD</sub> 40μA, V <sub>B</sub> + = 5V       | 2.7 | -   | 5.0  | V     |

## **Uncommitted Op Amp Specifications**

| PARAMETER                     | TEST CONDITIONS                    | MIN | ТҮР  | MAX  | UNITS             |

|-------------------------------|------------------------------------|-----|------|------|-------------------|

| Input Offset Voltage          |                                    | -   | ±5   | -    | mV                |

| Input Offset Current          |                                    | -   | ±10  | -    | nA                |

| Input Bias Current            |                                    | -   | 20   | -    | nA                |

| Differential Input Resistance | (Note 4)                           | -   | 1    | -    | MΩ                |

| Output Voltage Swing          | $R_{L} = 10k\Omega, V_{B} + = 12V$ | -   | ±6.2 | ±6.6 | V <sub>PEAK</sub> |

|                               | $R_L = 10k\Omega$ , $V_B + = 5V$   | -   | ±3   | -    | V <sub>PEAK</sub> |

| Output Resistance             | A <sub>VCL</sub> = 1 (Note 4)      | -   | 10   | -    | Ω                 |

| Small Signal GBW              | (Note 4)                           | -   | 1    | -    | MHz               |

NOTES:

3.  $I_{LONG}$  = Longitudinal Current.

4. These parameters are controlled by design or process parameters and are not directly tested. These parameters are characterized upon initial design release, upon design changes which would affect these characteristics, and at intervals to assure product quality and specification compliance.

4

# **Pin Descriptions**

| 28 PIN PLCC | 24 PIN DIP | SYMBOL           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |

|-------------|------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2           | 1          | TIP              | An analog input connected to the TIP (more positive) side of the subscriber loop through a $150\Omega$ feed resistor and a ring relay contact. Functions with the Ring terminal to receive voice signals from the telephone and for loop monitoring process.                                                                                                |

| 3           | 2          | RING             | An analog input connected to the RING (more negative) side of the subscriber loop through a $150\Omega$ feed resistor and a ring relay contact. Functions with the Tip terminal to receive voice signals from the telephone and for loop monitoring purposes.                                                                                               |

| 4           | 3          | V <sub>B</sub> + | Positive Voltage Source - Most positive supply. V <sub>B</sub> + is typically 12V or 5V.                                                                                                                                                                                                                                                                    |

| 5           | 4          | C <sub>1</sub>   | Capacitor #1 - Optional Capacitor used to improve power supply rejection. This pin should be left open if unused.                                                                                                                                                                                                                                           |

| 6           | 5          | С <sub>3</sub>   | Capacitor #3 - An external capacitor to be connected between this terminal and analog ground. Required for proper operation of the loop current limiting function, and for filtering V <sub>B</sub> - supply. Typical value is $0.3\mu$ F, 30V.                                                                                                             |

| 7           | 6          | DG<br>(Note 5)   | Digital Ground - To be connected to zero potential and serves as a reference for all digital inputs and outputs on the SLIC.                                                                                                                                                                                                                                |

| 9           | 7          | RS               | Ring Synchronization Input - A TTL - compatible clock input. The clock should be arranged such that a positive transition occurs on the negative going zero crossing of the ring voltage source, ensuring that the ring relay is activated and deactivated when the instantaneous ring voltage is near zero. If synchronization is not required, tie to 5V. |

| 10          | 8          | RD               | Relay Driver - A low active open collector logic output. When enabled, the external ring relay is energized.                                                                                                                                                                                                                                                |

| 11          | 9          | TF               | Tip Feed - A low impedance analog output connected to the TIP terminal through a $150\Omega$ feed resistor. Functions with the RF terminal to provide loop current, feed voice signals to the telephone set, and sink longitudinal current.                                                                                                                 |

| 12          | 10         | RF               | Ring Feed - A low impedance analog output connected to the RING terminal through a $150\Omega$ feed resistor. Functions with the TF terminal to provide loop current, feed voice signal to the telephone set, and sink longitudinal current.                                                                                                                |

| 13          | 11         | V <sub>B</sub> - | Negative Voltage Source - Most negative supply. $V_B$ - is typically -48V with an operational range of -42V to -58V. Frequently referred to as "battery".                                                                                                                                                                                                   |

| 14          | 12         | BG<br>(Note 1)   | Battery Ground - To be connected to zero potential. All loop current and some quiescent current flows into this ground terminal.                                                                                                                                                                                                                            |

| 16          | 13         | SHD              | Switch Hook Detection - A low active LS TTL - compatible logic output. This output is enabled for loop currents exceeding 10mA and disabled for loop currents less than 5mA.                                                                                                                                                                                |

| 17          | 14         | GKD              | Ground Key Detection - A low active LS TTL - compatible logic output. This output is enabled if the DC current into the ring lead exceeds the DC current out of the tip lead by more than 20mA, and disabled if this current difference is less than 10mA.                                                                                                  |

| 18          | 15         | PD               | Power Denial - A low active TTL - Compatible logic input. When enabled the switch hook detect (SHD) and ground key detect (GKD) are not necessarily valid, and the relay driver (RD) output is disabled.                                                                                                                                                    |

| 19          | 16         | RC               | Ring Command - A low active TTL - Compatible logic input. When enabled, the relay driver $(\overline{RD})$ output goes low on the next rising edge of the ring sync $(\overline{RS})$ input, as long as the SLIC is not in the power denial state $(\overline{PD} = 0)$ or the subscriber is not already off- hook $(\overline{SHD} = 0)$ .                 |

| 20          | 17         | C <sub>2</sub>   | Capacitor #2 - An external capacitor to be connected between this terminal and digital ground. Prevents false ground key indications from occurring during ring trip detection. Typical value is $0.15\mu$ F, 10V. This capacitor is not used if ground key function is not required.                                                                       |

| 21          | 18         | OUT              | The analog output of the spare operational amplifier.                                                                                                                                                                                                                                                                                                       |

| 23          | 19         | -IN              | The inverting analog input of the spare operational amplifier.                                                                                                                                                                                                                                                                                              |

| 24          | 20         | +IN              | The non-inverting analog input of the spare operational amplifier.                                                                                                                                                                                                                                                                                          |

| Pin Desci   | riptions   | (Continued)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28 PIN PLCC | 24 PIN DIP | SYMBOL         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25          | 21         | RX             | Receive Input, 4-Wire Side - A high impedance analog input which is internally biased. Capacitive coupling to this input is required. AC signals appearing at this input differentially drive the Tip feed and Ring feed amplifiers, which in turn drive tip and ring through $300\Omega$ of feed resistance on each side of the line.                                                                                                                                                  |

| 26          | 22         | C <sub>4</sub> | Capacitor #4 - An external capacitor to be connected between this terminal and analog ground. This capacitor prevents false ground key indication and false ring trip detection from occurring when longitudinal currents are induced onto the subscriber loop from nearby power lines and other noise sources. This capacitor is also required for the proper operation of ring trip detection. Typical value is $0.5\mu$ F to $1.0\mu$ F, 20V. This capacitor should be nonpolarized. |

| 27          | 23         | AG<br>(Note 5) | Analog Ground - To be connected to zero potential and serves as a reference for the transmit output (TX) and receive input (RX) terminals.                                                                                                                                                                                                                                                                                                                                              |

| 28          | 24         | ТХ             | Transmit Output, 4-Wire Side - A low impedance analog output which represents the differential voltage across Tip and Ring. Transhybrid balancing must be performed (using the SLIC microcircuit's spare op amp) beyond this output to completely implement two to four wire conversion. This output is unbalanced and referenced to analog ground. Since the DC level of this output varies with loop current, capacitive coupling to the next stage is essential.                     |

| 1, 8, 5, 22 |            | NC             | No internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Pin Descriptions (Continued)

#### NOTE:

5. All grounds (AG, BG, and DG) must be applied before V<sub>B</sub>+ or V<sub>B</sub>-. Failure to do so may result in premature failure of the part. If a user wishes to run separate grounds off a line card, the AG must be applied first.

## Functional Diagram

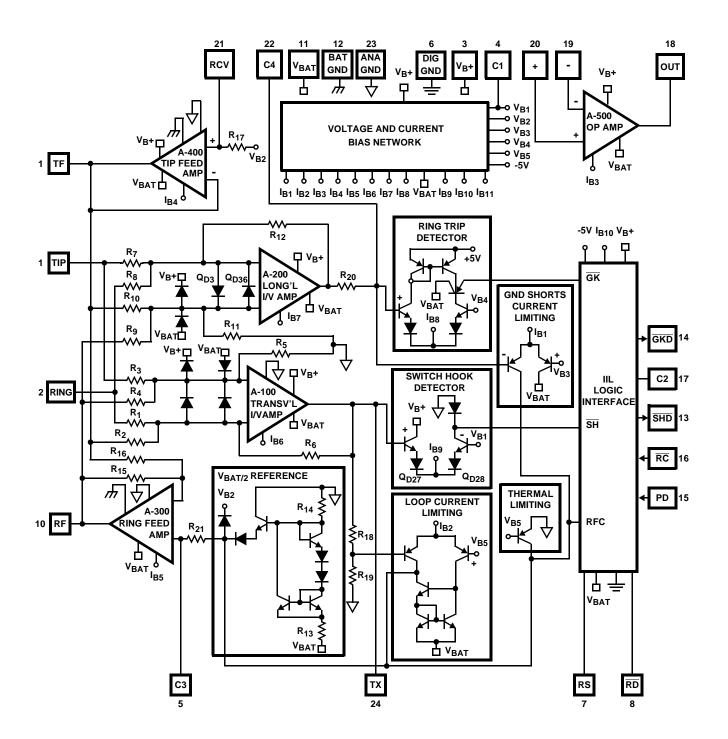

## Schematic Diagram

#### HC-5502B

Pin Numbers for DIP Package

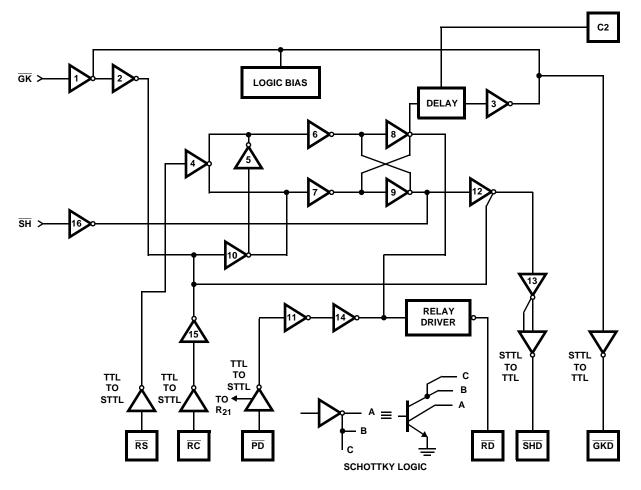

# Logic Diagram

HC-5502B LOGIC GATE SCHEMATIC

## **Overvoltage Protection and Longitudinal Current Protection**

The SLIC device, in conjunction with an external protection bridge, will withstand high voltage lightning surges and power line crosses.

High voltage surge conditions are as specified in Table 1.

The SLIC will withstand longitudinal currents up to a maximum or 30mARMS, 15mARMS per leg, without any performance degradation.

| PARAMETER             | TEST<br>CONDITION                | PERFORMANCE<br>(MAX) | UNITS             |

|-----------------------|----------------------------------|----------------------|-------------------|

| Longitudinal<br>Surge | 10μs Rise/                       | ±1000 (Plastic)      | V <sub>PEAK</sub> |

|                       | 1000μs Fall                      | ±500 (Ceramic)       | V <sub>PEAK</sub> |

| Metallic Surge        | 10µs Rise/                       | ±1000 (Plastic)      | V <sub>PEAK</sub> |

|                       | 1000µs Fall                      | ±500 (Ceramic)       | V <sub>PEAK</sub> |

| T/GND                 | 10µs Rise/                       | ±1000 (Plastic)      | V <sub>PEAK</sub> |

| R/GND                 | 1000μs Fall                      | ±500 (Ceramic)       | V <sub>PEAK</sub> |

| 50/60Hz Current       |                                  |                      | 1                 |

| T/GND                 | 11 Cycles                        | 700 (Plastic)        | V <sub>RMS</sub>  |

| R/GND                 | Limited to<br>10A <sub>RMS</sub> | 350 (Ceramic)        | V <sub>RMS</sub>  |

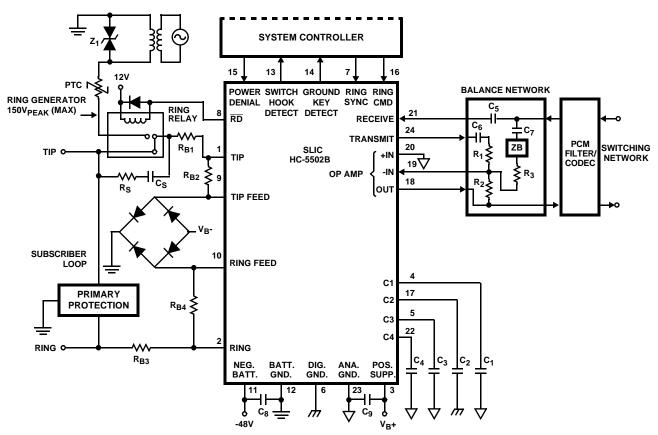

## Applications Diagram

FIGURE 1. TYPICAL LINE CIRCUIT APPLICATION WITH THE MONOLITHIC SLIC

## **Typical Component Values**

$C_1 = 0.5 \mu F$  (Note 6).

$C_2 = 0.15 \mu F$ , 10V.

$C_3 = 0.3 \mu F$ , 30V.

$C_4$  = 0.5  $\mu F$  to 1.0  $\mu F,$  10%, 20V (Should be nonpolarized).

$C_5 = 0.5 \mu F$ , 20V.

$C_6 = C_7 = 0.5 \mu F$  (10% Match Required) (Note 7), 20V.

$C_8 = 0.01 \mu F$ , 100V.

$C_9 = 0.01 \mu F$ , 20V, ±20%.

NOTES:

6.  $C_1$  is an optional capacitor used to improve  $V_B$ + supply rejection. This pin must be left open if unused.

7. To obtain the specified transhybrid loss it is necessary for the three legs of the balance network, C<sub>6</sub>-R<sub>1</sub> and R<sub>2</sub> and C<sub>7</sub>-ZB-R<sub>3</sub>, to match in impedance to within 0.3%. Thus, if C<sub>6</sub> and C<sub>7</sub> are 1µF each, a 20% match is adequate. It should be noted that the transmit output to C<sub>6</sub> sees a -22V step when the loop is closed. Too large a value for C<sub>6</sub> may produce an excessively long transient at the op amp output to the PCM Filter/CODEC.

A  $0.5\mu$ F and  $100k\Omega$  gives a time constant of 50ms. The uncommitted op amp output is internally clamped to stay within ±6.6V and is current limited.

- 8. Secondary protection diode bridge recommended is a 2A, 200V type.

- All grounds (AG, BG, and DG) must be applied before V<sub>B</sub>+ or V<sub>B</sub>-. Failure to do so may result in premature failure of the part. If a user wishes to run separate grounds off a line card, the AG must be applied first.

- 10. Pin numbers given for DIP package.

$R_1 = R_2 = R_3 = 100$ kΩ (0.1% Match Required, 1% absolute value), ZB = 0 for 600Ω Terminations (Note 7).

$R_{B1}$  =  $R_{B2}$  =  $R_{B3}$  =  $R_{B4}$  = 150 $\Omega$  (0.1% Match Required, 1% absolute value).

$R_S$  = 1k\Omega,  $C_S$  = 0.1 $\mu F,$  200V typically, depending on  $V_{RING}$  and line length.

$Z_1 = 150V$  to 200V transient protection. PTC used as ring generator ballast.

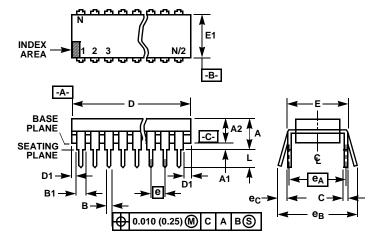

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- 10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 0.045 inch (0.76 1.14mm).

#### **E24.6** (JEDEC MS-011-AA ISSUE B) 24 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| А              | -         | 0.250 | -           | 6.35  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.125     | 0.195 | 3.18        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.030     | 0.070 | 0.77        | 1.77  | 8     |

| С              | 0.008     | 0.015 | 0.204       | 0.381 | -     |

| D              | 1.150     | 1.290 | 29.3        | 32.7  | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| E              | 0.600     | 0.625 | 15.24       | 15.87 | 6     |

| E1             | 0.485     | 0.580 | 12.32       | 14.73 | 5     |

| е              | 0.100 BSC |       | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.600 BSC |       | 15.24 BSC   |       | 6     |

| е <sub>В</sub> | -         | 0.700 | -           | 17.78 | 7     |

| L              | 0.115     | 0.200 | 2.93        | 5.08  | 4     |

| N              | 24        |       | 24          |       | 9     |

Rev. 0 12/93

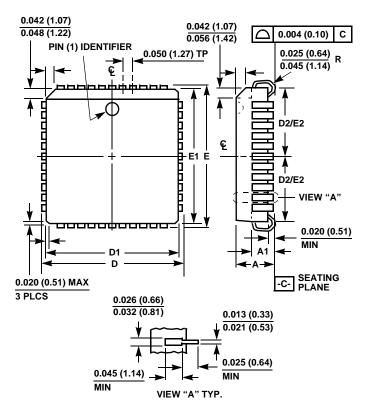

## Plastic Leaded Chip Carrier Packages (PLCC)

#### N28.45 (JEDEC MS-018AB ISSUE A) 28 LEAD PLASTIC LEADED CHIP CARRIER PACKAGE

|        | INCHES |       | MILLIMETERS |       |       |

|--------|--------|-------|-------------|-------|-------|

| SYMBOL | MIN    | MAX   | MIN         | MAX   | NOTES |

| А      | 0.165  | 0.180 | 4.20        | 4.57  | -     |

| A1     | 0.090  | 0.120 | 2.29        | 3.04  | -     |

| D      | 0.485  | 0.495 | 12.32       | 12.57 | -     |

| D1     | 0.450  | 0.456 | 11.43       | 11.58 | 3     |

| D2     | 0.191  | 0.219 | 4.86        | 5.56  | 4, 5  |

| Е      | 0.485  | 0.495 | 12.32       | 12.57 | -     |

| E1     | 0.450  | 0.456 | 11.43       | 11.58 | 3     |

| E2     | 0.191  | 0.219 | 4.86        | 5.56  | 4, 5  |

| Ν      | 28     |       | 28          |       | 6     |

Rev. 2 11/97

#### NOTES:

- 1. Controlling dimension: INCH. Converted millimeter dimensions are not necessarily exact.

- 2. Dimensions and tolerancing per ANSI Y14.5M-1982.

- Dimensions D1 and E1 do not include mold protrusions. Allowable mold protrusion is 0.010 inch (0.25mm) per side. Dimensions D1 and E1 include mold mismatch and are measured at the extreme material condition at the body parting line.

- 4. To be measured at seating plane -C- contact point.

- 5. Centerline to be determined where center leads exit plastic body.

- 6. "N" is the number of terminal positions.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com