# PART NUMBER

# EP610LI-15-ROCA

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# EP610-910-1810

Classic EPLD Family

The Altera Classic<sup>™</sup> device family offers a solution to high-speed, low-power logic integration. Fabricated on advanced CMOS technology, Classic devices also have a Turbo-only version, which is described in the data sheet.

Classic devices support 100% TTL emulation and can easily integrate multiple PAL- and GAL-type devices with densities ranging from 300 to 900 usable gates. The Classic family provides pin-to-pin logic delays as low as 10 ns and counter frequencies as high as 100 MHz. Classic devices are available in a wide range of packages, including ceramic dual in-line package (CerDIP), plastic dual in-line package (PDIP), plastic J-lead chip carrier (PLCC), ceramic J-lead chip carrier JLCC), pin-grid array (PGA), and small-outline integrated circuit (SOIC) packages.

#### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

#### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### FOR REFERENCE ONLY

# General Description

The Altera Classic<sup>™</sup> device family offers a solution to high-speed, lowpower logic integration. Fabricated on advanced CMOS technology, Classic devices also have a Turbo-only version, which is described in this data sheet.

Classic devices support 100% TTL emulation and can easily integrate multiple PAL- and GAL-type devices with densities ranging from 300 to 900 usable gates. The Classic family provides pin-to-pin logic delays as low as 10 ns and counter frequencies as high as 100 MHz. Classic devices are available in a wide range of packages, including ceramic dual in-line package (CerDIP), plastic dual in-line package (PDIP), plastic J-lead chip carrier (PLCC), ceramic J-lead chip carrier (JLCC), pin-grid array (PGA), and small-outline integrated circuit (SOIC) packages.

EPROM-based Classic devices can reduce active power consumption without sacrificing performance. This reduced power consumption makes the Classic family well suited for a wide range of low-power applications.

Classic devices are 100% generically tested devices in windowed packages and can be erased with ultra-violet (UV) light, allowing design changes to be implemented quickly.

Classic devices use sum-of-products logic and a programmable register. The sum-of-products logic provides a programmable-AND/fixed-OR structure that can implement logic with up to eight product terms. The programmable register can be individually programmed for D, T, SR, or JK flipflop operation or can be bypassed for combinatorial operation. In addition, macrocell registers can be individually clocked either by a global clock or by any input or feedback path to the AND array. Altera's proprietary programmable I/O architecture allows the designer to program output and feedback paths for combinatorial or registered operation in both active-high and active-low modes. These features make it possible to implement a variety of logic functions simultaneously.

Classic devices are supported by Altera's MAX+PLUS II development system, a single, integrated package that offers schematic, text—including VHDL, Verilog HDL, and the Altera Hardware Description Language (AHDL)—and waveform design entry, compilation and logic synthesis, simulation and timing analysis, and device programming. The MAX+PLUS II software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and workstationbased EDA tools. The MAX+PLUS II software runs on Windows-based PCs, as well as Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations. These devices also contain on-board logic test circuitry to allow verification of function and AC specifications during standard production flow.

#### **Rochester Ordering Guide**

\*Most products can also be offered as RoHS compliant, designated by a –G suffix. Please contact factory for more information.

| Rochester Part Number | Altera Part Number | Package          | Temperature    |

|-----------------------|--------------------|------------------|----------------|

| EP600DI-25            | EP600DI-25         | CDIP-24          | -40° to +85°C  |

| EP600DI-25T           | EP600DI-25T        | CDIP-24          | -40° to +85°C  |

| EP600DI-30            | EP600DI-30         | CDIP-24          | -40° to +85°C  |

| EP600DI-35            | EP600DI-35         | CDIP-24          | -40° to +85°C  |

| EP600DI-45            | EP600DI-45         | CDIP-24          | -40° to +85°C  |

| EP600DM-25/B          | EP600DM-25/B       | CDIP-24          | -55° to +125°C |

| EP600DM-25T/B         | EP600DM-25T/B      | CDIP-24          | -55° to +125°C |

| EP600DM-30/B          | EP600DM-30/B       | CDIP-24          | -55° to +125°C |

| EP600DM-35/B          | EP600DM-35/B       | CDIP-24          | -55° to +125°C |

| EP600DM-45/B          | EP600DM-45/B       | CDIP-24          | -55° to +125°C |

| EP600IDC-25           | EP600IDC-25        | CDIP-24          | 0° to +70°C    |

| EP600IDC-30           | EP600IDC-30        | CDIP-24          | 0° to +70°C    |

| EP600IDC-35           | EP600IDC-35        | CDIP-24          | 0° to +70°C    |

| EP600IDC-45           | EP600IDC-45        | CDIP-24          | 0° to +70°C    |

| EP600ILC-45           | EP600ILC-45        | LDCC-28, Plastic | 0° to +70°C    |

| EP600IPC-25           | EP600IPC-25        | PDIP-24          | 0° to +70°C    |

| EP600IPC-30           | EP600IPC-30        | PDIP-24          | 0° to +70°C    |

| EP600IPC-35           | EP600IPC-35        | PDIP-24          | 0° to +70°C    |

| EP600IPC-45           | EP600IPC-45        | PDIP-24          | 0° to +70°C    |

| EP600IPC-45           | EP600IPC-45        | PDIP-24          | 0° to +70°C    |

| EP600IPC-45AB         | EP600IPC-45AB      | PDIP-24          | 0° to +70°C    |

| EP610DC-25            | EP610DC-25         | CDIP-24          | 0° to +70°C    |

| EP610DC-30            | EP610DC-30         | CDIP-24          | 0° to +70°C    |

| EP610DC-35            | EP610DC-35         | CDIP-24          | 0° to +70°C    |

| EP610DC-35AA          | EP610DC-35AA       | CDIP-24          | 0° to +70°C    |

| EP610DC-45            | EP610DC-45         | CDIP-24          | 0° to +70°C    |

| EP610DI-15            | EP610DI-15         | CDIP-24          | -40° to +85°C  |

| EP610DI-20            | EP610DI-20         | CDIP-24          | -40° to +85°C  |

| EP610DI-25            | EP610DI-25         | CDIP-24          | -40° to +85°C  |

| EP610DI-25T           | EP610DI-25T        | CDIP-24          | -40° to +85°C  |

| EP610DI-30            | EP610DI-30         | CDIP-24          | -40° to +85°C  |

| EP610DI-35            | EP610DI-35         | CDIP-24          | -40° to +85°C  |

| EP610DM-25            | EP610DM-25         | CDIP-24          | -55° to +125°C |

| EP610DM-25T           | EP610DM-25T        | CDIP-24          | -55° to +125°C |

| EP610DM-30            | EP610DM-30         | CDIP-24          | -55° to +125°C |

| EP610DM-35            | EP610DM-35         | CDIP-24          | -55° to +125°C |

| EP610DM-35/B          | EP610DM-35/B       | CDIP-24          | -55° to +125°C |

| EP610DM-25/R          | EP610DM-25/R       | CDIP-24          | -55° to +125°C |

| EP610DM-25T/R         | EP610DM-25T/R      | CDIP-24          | -55° to +125°C |

| EP610DM-30/R          | EP610DM-30/R       | CDIP-24          | -55° to +125°C |

| EP610DM-35/R          | EP610DM-35/R       | CDIP-24          | -55° to +125°C |

| EP610LC-15            | EP610LC-15         | LDCC-28, Plastic | 0° to +70°C    |

| EP610LC-20            | EP610LC-20         | LDCC-28, Plastic | 0° to +70°C    |

| EP610LC-20T           | EP610LC-20T        | LDCC-28, Plastic | 0° to +70°C    |

| EP610LC-25            | EP610LC-25         | LDCC-28, Plastic | 0° to +70°C    |

| EP610LC-35            | EP610LC-35         | LDCC-28, Plastic | 0° to +70°C    |

| EP610LC-45            | EP610LC-45         | LDCC-28, Plastic | 0° to +70°C    |

Specification Number EP610\_910\_1810-CI (AT) Rev B

| Rochester Part Number | Altera Part Number | Package          | Temperature   |

|-----------------------|--------------------|------------------|---------------|

| EP610LI-15            | EP610LI-15         | LDCC-28, Plastic | -40° to +85°C |

| EP610LI-20            | EP610LI-20         | LDCC-28, Plastic | -40° to +85°C |

| EP610LI-20T           | EP610LI-20T        | LDCC-28, Plastic | -40° to +85°C |

| EP610LI-25            | EP610LI-25         | LDCC-28, Plastic | -40° to +85°C |

| EP610LI-35            | EP610LI-35         | LDCC-28, Plastic | -40° to +85°C |

| EP610LI-45            | EP610LI-45         | LDCC-28, Plastic | -40° to +85°C |

| EP610PC-15            | EP610PC-15         | PDIP-24          | 0° to +70°C   |

| EP610PC-20            | EP610PC-20         | PDIP-24          | 0° to +70°C   |

| EP610PC-20T           | EP610PC-20T        | PDIP-24          | 0° to +70°C   |

| EP610PC-25            | EP610PC-25         | PDIP-24          | 0° to +70°C   |

| EP610PC-25T           | EP610PC-25T        | PDIP-24          | 0° to +70°C   |

| EP610PC-30            | EP610PC-30         | PDIP-24          | 0° to +70°C   |

| EP610PC-35            | EP610PC-35         | PDIP-24          | 0° to +70°C   |

| EP610PC-45            | EP610PC-45         | PDIP-24          | 0° to +70°C   |

| EP610PI-15            | EP610PI-15         | PDIP-24          | -40° to +85°C |

| EP610PI-20            | EP610PI-20         | PDIP-24          | -40° to +85°C |

| EP610PI-25            | EP610PI-25         | PDIP-24          | -40° to +85°C |

| EP610PI-30            | EP610PI-30         | PDIP-24          | -40° to +85°C |

| EP610PI-35            | EP610PI-35         | PDIP-24          | -40° to +85°C |

| EP610PI-45            | EP610PI-45         | PDIP-24          | -40° to +85°C |

| EP610SC-15            | EP610SC-15         | SOP-24, Plastic  | 0° to +70°C   |

| EP610SC-20            | EP610SC-20         | SOP-24, Plastic  | 0° to +70°C   |

| EP610SC-25            | EP610SC-25         | SOP-24, Plastic  | 0° to +70°C   |

| EP610SI-25            | EP610SI-25         | SOP-24, Plastic  | -40° to +85°C |

| EP610SI-30            | EP610SI-30         | SOP-24, Plastic  | -40° to +85°C |

| EP610SI-35            | EP610SI-35         | SOP-24, Plastic  | -40° to +85°C |

| EP610SI-45            | EP610SI-45         | SOP-24, Plastic  | -40° to +85°C |

| EP900ILC-50           | EP900ILC-50        | LDCC-44, Plastic | 0° to +70°C   |

| EP900ILC-50H          | EP900ILC-50H       | LDCC-44, Plastic | 0° to +70°C   |

| EP900IPC-50           | EP900IPC-50        | PDIP-40          | 0° to +70°C   |

| EP910DC-25            | EP910DC-25         | CDIP-40          | 0° to +70°C   |

| EP910DC-30            | EP910DC-30         | CDIP-40          | 0° to +70°C   |

| EP910DC-35            | EP910DC-35         | CDIP-40          | 0° to +70°C   |

| EP910DC-45            | EP910DC-45         | CDIP-40          | 0° to +70°C   |

| EP910DI-12            | EP910DI-12         | CDIP-40          | -40° to +85°C |

| EP910DI-15            | EP910DI-15         | CDIP-40          | -40° to +85°C |

| EP910DI-25            | EP910DI-25         | CDIP-40          | -40° to +85°C |

| EP910DI-30            | EP910DI-30         | CDIP-40          | -40° to +85°C |

| EP910DI-35            | EP910DI-35         | CDIP-40          | -40° to +85°C |

| EP910DI-40            | EP910DI-40         | CDIP-40          | -40° to +85°C |

| EP910DI-50            | EP910DI-50         | CDIP-40          | -40° to +85°C |

| EP910IDC-15           | EP910IDC-15        | CDIP-40          | 0° to +70°C   |

| EP910IDI-15           | EP910IDI-15        | CDIP-40          | -40° to +85°C |

| EP910ILC-12           | EP910ILC-12        | LDCC-44, Plastic | 0° to +70°C   |

| EP910ILC-12H          | EP910ILC-12H       | LDCC-44, Plastic | 0° to +70°C   |

| EP910ILC-15           | EP910ILC-15        | LDCC-44, Plastic | 0° to +70°C   |

\*Most products can also be offered as RoHS compliant, designated by a –G suffix. Please contact factory for more information.

| Rochester Part Number | Altera Part Number | Package          | Temperature   |

|-----------------------|--------------------|------------------|---------------|

| EP910ILC-15H          | EP910ILC-15H       | LDCC-44, Plastic | 0° to +70°C   |

| EP910ILI-12           | EP910ILI-12        | LDCC-44, Plastic | -40° to +85°C |

| EP910IPC-12           | EP910IPC-12        | PDIP-40          | 0° to +70°C   |

| EP910IPC-25           | EP910IPC-25        | PDIP-40          | 0° to +70°C   |

| EP910LC-30            | EP910LC-30         | LDCC-44, Plastic | 0° to +70°C   |

| EP910LC-30T           | EP910LC-30T        | LDCC-44, Plastic | 0° to +70°C   |

| EP910LC-35            | EP910LC-35         | LDCC-44, Plastic | 0° to +70°C   |

| EP910LC-35H           | EP910LC-35H        | LDCC-44, Plastic | 0° to +70°C   |

| EP910LC-40            | EP910LC-40         | LDCC-44, Plastic | 0° to +70°C   |

| EP910LC-40H           | EP910LC-40H        | LDCC-44, Plastic | 0° to +70°C   |

| EP910LI-12            | EP910LI-12         | LDCC-44, Plastic | -40° to +85°C |

| EP910LI-15            | EP910LI-15         | LDCC-44, Plastic | -40° to +85°C |

| EP910LI-25            | EP910LI-25         | LDCC-44, Plastic | -40° to +85°C |

| EP910LI-30            | EP910LI-30         | LDCC-44, Plastic | -40° to +85°C |

| EP910LI-35            | EP910LI-35         | LDCC-44, Plastic | -40° to +85°C |

| EP910LI-40            | EP910LI-40         | LDCC-44, Plastic | -40° to +85°C |

| EP910LI-50            | EP910LI-50         | LDCC-44, Plastic | -40° to +85°C |

| EP910PC-30            | EP910PC-30         | PDIP-40          | 0° to +70°C   |

| EP910PI-12            | EP910PI-12         | PDIP-40          | -40° to +85°C |

| EP910PI-15            | EP910PI-15         | PDIP-40          | -40° to +85°C |

| EP910PI-25            | EP910PI-25         | PDIP-40          | -40° to +85°C |

| EP910PI-30            | EP910PI-30         | PDIP-40          | -40° to +85°C |

| EP910PI-35            | EP910PI-35         | PDIP-40          | -40° to +85°C |

| EP910PI-40            | EP910PI-40         | PDIP-40          | -40° to +85°C |

| EP910PI-50            | EP910PI-50         | PDIP-40          | -40° to +85°C |

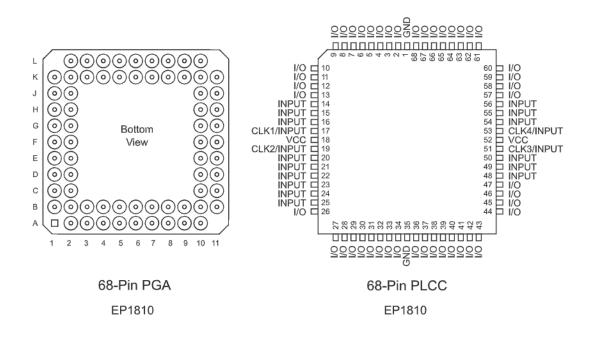

| EP1810GC-35           | EP1810GC-35        | PGA-68, Ceramic  | 0° to +70°C   |

| EP1810GC-45           | EP1810GC-45        | PGA-68, Ceramic  | 0° to +70°C   |

| EP1810GC-70           | EP1810GC-70        | PGA-68, Ceramic  | 0° to +70°C   |

| EP1810GI-35           | EP1810GI-35        | PGA-68, Ceramic  | -40° to +85°C |

| EP1810GI-45           | EP1810GI-45        | PGA-68, Ceramic  | -40° to +85°C |

| EP1810GI-70           | EP1810GI-70        | PGA-68, Ceramic  | -40° to +85°C |

| EP1810LC-45           | EP1810LC-45        | LDCC-68, Plastic | 0° to +70°C   |

| EP1810LC-45AA         | EP1810LC-45AA      | LDCC-68, Plastic | 0° to +70°C   |

| EP1810LC-45H          | EP1810LC-45H       | LDCC-68, Plastic | 0° to +70°C   |

| EP1810LC-70           | EP1810LC-70        | LDCC-68, Plastic | 0° to +70°C   |

| EP1810LI-35           | EP1810LI-35        | LDCC-68, Plastic | -40° to +85°C |

| EP1810LI-45           | EP1810LI-45        | LDCC-68, Plastic | -40° to +85°C |

| EP1810LI-70           | EP1810LI-70        | LDCC-68, Plastic | -40° to +85°C |

\*Most products can also be offered as RoHS compliant, designated by a –G suffix. Please contact factory for more information.

# Functional Description

The Classic architecture includes the following elements:

- Macrocells

- Programmable registers

- Output enable/clock select

- Feedback select

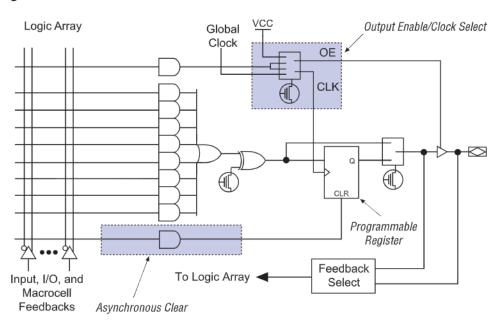

#### Macrocells

Classic macrocells, shown in Figure 1, can be individually configured for both sequential and combinatorial logic operation. Eight product terms form a programmable-AND array that feeds an OR gate for combinatorial logic implementation. An additional product term is used for asynchronous clear control of the internal register; another product term implements either an output enable or a logic-array-generated clock. Inputs to the programmable-AND array come from both the true and complement signals of the dedicated inputs, feedbacks from I/O pins that are configured as inputs, and feedbacks from macrocell outputs. Signals from dedicated inputs are globally routed and can feed the inputs of all device macrocells. The feedback multiplexer controls the routing of feedback signals from macrocells and from I/O pins.

#### Figure 1. Classic Device Macrocell

The eight product terms of the programmable-AND array feed the 8-input OR gate, which then feeds one input to an XOR gate. The other input to the XOR gate is connected to a programmable bit that allows the array output to be inverted. Altera's MAX+PLUS II software uses the XOR gate to implement either active-high or active-low logic, or De Morgan's inversion to reduce the number of product terms needed to implement a function.

#### **Programmable Registers**

To implement registered functions, each macrocell register can be individually programmed for D, T, JK, or SR operation. If necessary, the register can be bypassed for combinatorial operation. During design compilation, the MAX+PLUS II software selects the most efficient register operation for each registered function to minimize the logic resources needed by the design. Registers have an individual asynchronous clear function that is controlled by a dedicated product term. These registers are cleared automatically during power-up.

In addition, macrocell registers can be individually clocked by either a global clock or any input or feedback path to the AND array. Altera's proprietary programmable I/O architecture allows the designer to program output and feedback paths for combinatorial or registered operation in both active-high and active-low modes. These features make it possible to simultaneously implement a variety of logic functions.

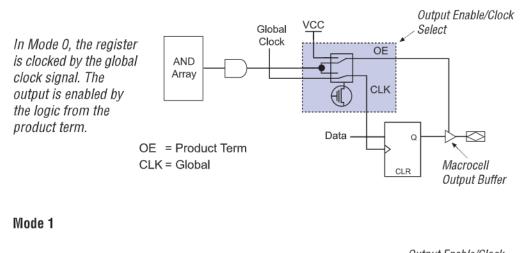

### **Output Enable/Clock Select**

Figure 2 shows the two operating modes (Modes 0 and 1) provided by the output enable/clock (OE/CLK) select. The OE/CLK select, which is controlled by a single programmable bit, can be individually configured for each macrocell. In Mode 0, the tri-state output buffer is controlled by a single product term. If the output enable is high, the output buffer is enabled. If the output enable is low, the output has a high-impedance value. In Mode 0, the macrocell flipflop is clocked by its global clock input signal.

In Mode 1, the output enable buffer is always enabled, and the macrocell register can be triggered by an array clock signal generated by a product term. This mode allows registers to be individually clocked by any signal on the AND array. With both true and complement signals in the AND array, the register can be configured to trigger on a rising or falling edge. This product-term-controlled clock configuration also supports gated clock structures.

#### Mode O

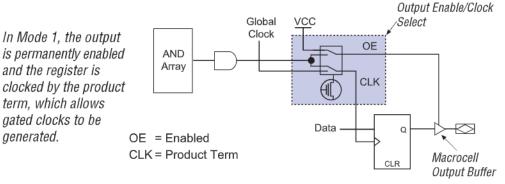

#### **Feedback Select**

Each macrocell in a Classic device provides feedback selection that is controlled by the feedback multiplexer. This feedback selection allows the designer to feed either the macrocell output or the I/O pin input associated with the macrocell back into the AND array. The macrocell output can be either the Q output of the programmable register or the combinatorial output of the macrocell. Different devices have different feedback multiplexer configurations. See Figure 3.

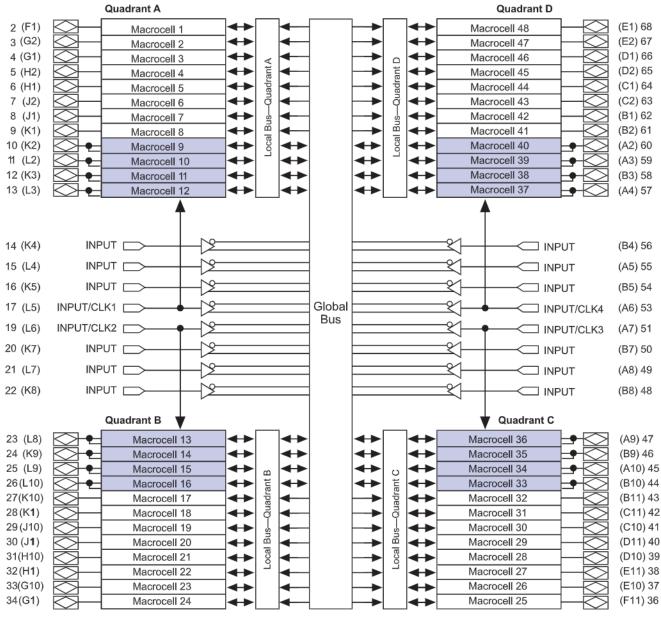

EP610, EP610I, EP910, and EP910I devices have a global feedback configuration; either the macrocell output (Q) or the I/O pin input (I/O) can feed back to the AND array so that it is accessible to all other macrocells.

EP1810 macrocells can have either of two feedback configurations: quadrant or dual. Most macrocells in EP1810 devices have a quadrant feedback configuration; either the macrocell output or I/O pin input can feed back to other macrocells in the same quadrant. Selected macrocells in EP1810 devices have a dual feedback configuration: the output of the macrocell feeds back to other macrocells in the same quadrant, and the I/O pin input feeds back to all macrocells in the device. If the associated I/O pin is not used, the macrocell output can optionally feed all macrocells in the device. In this case, the output of the macrocell passes through the tri-state buffer and uses the feedback path between the buffer and the I/O pin.

# **Design Security** Classic devices contain a programmable security bit that controls access to the data programmed into the device. When this bit is programmed, a proprietary design implemented in the device cannot be copied or retrieved. This feature provides a high level of design security because data within configuration elements is invisible. The security bit that controls this function and other program data is reset only when the device is erased.

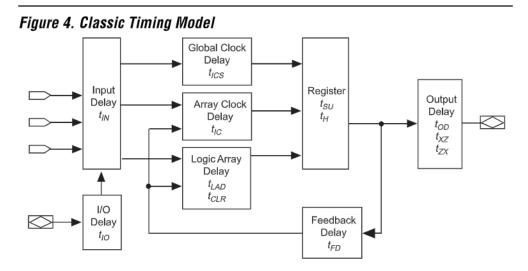

# **Timing Model**

Device timing can be analyzed with the MAX+PLUS II software, with a variety of popular industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 4. Devices have fixed internal delays that allow the user to determine the worst-case timing for any design. The MAX+PLUS II software provides timing simulation, point-to-point delay prediction, and detailed timing analysis for system-level performance evaluation.

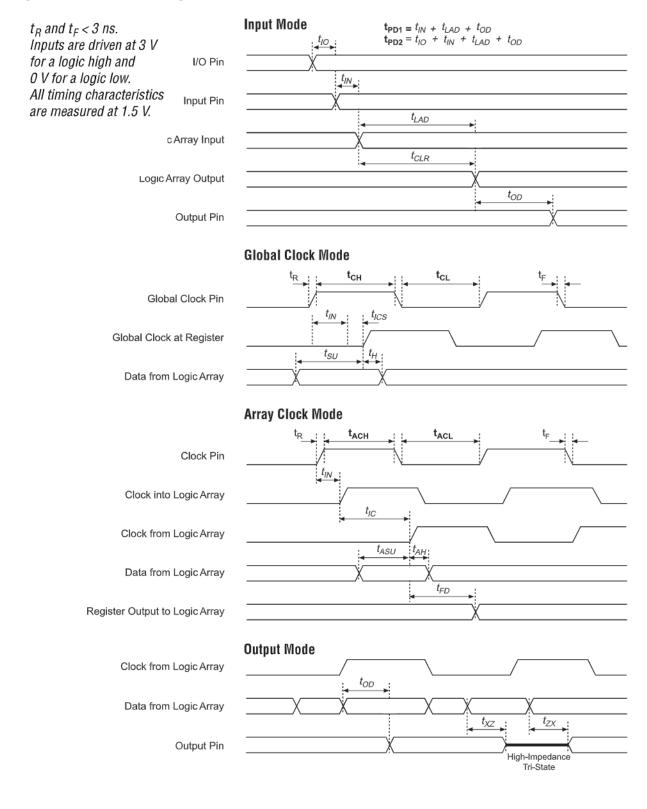

#### Figure 5. Classic Switching Waveforms

# Turbo Bit<br/>OptionMany Classic devices contain a programmable Turbo Bit™ option to<br/>control the automatic power-down feature that enables the low-standby-<br/>power mode. When the Turbo Bit option is turned on, the low-standby-<br/>power mode is disabled. All AC values are tested with the Turbo Bit<br/>option turned on. When the device is operating with the Turbo Bit option<br/>turned off (non-Turbo mode), a non-Turbo adder must be added to the<br/>appropriate AC parameter to determine worst-case timing. The non-<br/>Turbo adder is specified in the "AC Operating Conditions" tables for each<br/>Classic device that supports the Turbo mode.

# **Generic Testing**

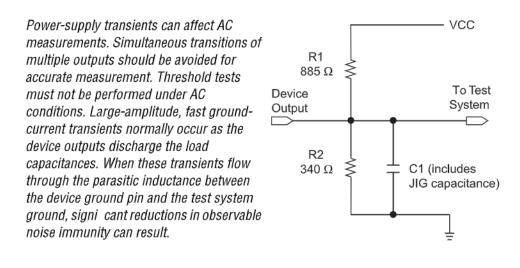

Classic devices are fully functionally tested. Complete testing of each programmable EPROM configuration element and all internal logic elements before and after packaging ensures 100% programming yield. See Figure 6 for AC test measurement conditions. These devices also contain on-board logic test circuitry to allow verification of function and AC specifications during standard production flow.

#### Figure 6. AC Test Conditions

# Device Programming

Classic devices can be programmed on 486- and Pentium-based PCs with the MAX+PLUS II Programmer, an Altera Logic Programmer card, the MPU, and the appropriate device adapter. The MPU performs continuity checking to ensure adequate electrical contact between the adapter and the device.

Rochester EPLD devices normally sold in the un-configured state are tested using the original manufacturer's test software to guarantee the data sheet specifications. In some cases, EPLD devices can be configured to the customer's design and fully tested as such.

Notes:

# EP610 EPLD

# Features

- High-performance, 16-macrocell Classic EPLD

- Combinatorial speeds with **t**<sub>PD</sub> as fast as 10 ns

- Counter frequencies of up to 100 MHz

- Pipelined data rates of up to 125 MHz

- Programmable I/O architecture with up to 20 inputs or 16 outputs and 2 clock pins

- EP610 and EP610I devices are pin-, function-, and programming file-compatible

- Programmable clock option for independent clocking of all registers

- Macrocells individually programmable as D, T, JK, or SR flipflops, or for combinatorial operation

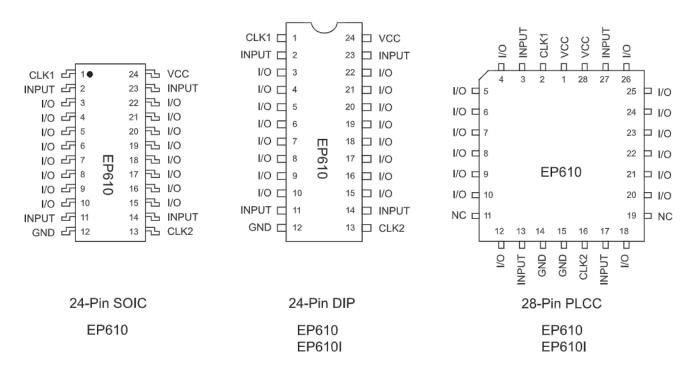

- Available in the following packages (see Figure 7):

- 24-pin small-outline integrated circuit (plastic SOIC only)

- 24-pin ceramic and plastic dual in-line package (CerDIP and PDIP)

- 28-pin plastic J-lead chip carrier (PLCC)

#### Figure 7. EP610 Package Pin-Out Diagrams

Package outlines not drawn to scale. Windows in ceramic packages only.

# General Description

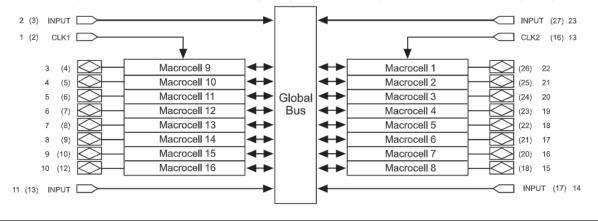

EP610 devices have 16 macrocells, 4 dedicated input pins, 16 I/O pins, and 2 global clock pins (see Figure 8). Each macrocell can access signals from the global bus, which consists of the true and complement forms of the dedicated inputs and the true and complement forms of either the output of the macrocell or the I/O input. The CLK1 signal is a dedicated global clock input for the registers in macrocells 9 through 16. The CLK2 signal is a dedicated global clock input for registers in macrocells 1 through 8.

#### Figure 8. EP610 Block Diagram

Numbers without parentheses are for DIP and SOIC packages. Numbers in parentheses are for J-lead packages.

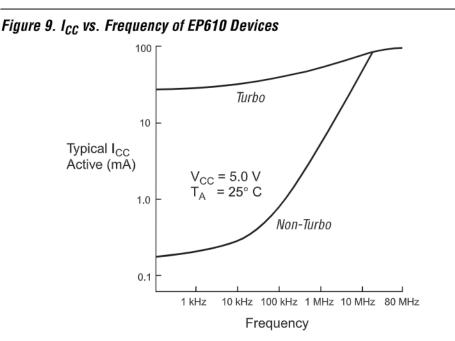

Figure 9 shows the typical supply current (I $_{\rm CC}$ ) versus frequency of EP610 devices.

Drive characteristics may exceed shown curves.

# Operating Conditions

Tables 2 through 7 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for EP610 and EP610I devices.

| Symbol           | Parameter                            | Conditions                   | EP   | EP610 EP610I |      | Unit                  |    |

|------------------|--------------------------------------|------------------------------|------|--------------|------|-----------------------|----|

|                  |                                      |                              | Min  | Max          | Min  | Max                   |    |

| V <sub>CC</sub>  | Supply voltage                       | With respect to ground (2)   | -2.0 | 7.0          | -2.0 | 7.0                   | V  |

| VI               | DC input voltage                     |                              | -2.0 | 7.0          | -0.5 | V <sub>CC</sub> + 0.5 | V  |

| I <sub>MAX</sub> | DC V <sub>CC</sub> or ground current |                              | -175 | 175          |      |                       | mA |

| I <sub>OUT</sub> | DC output current, per pin           |                              | -25  | 25           |      |                       | mA |

| T <sub>STG</sub> | Storage temperature                  | No bias                      | -65  | 150          | -65  | 150                   | °C |

| T <sub>AMB</sub> | Ambient temperature                  | Under bias                   | -65  | 135          | -65  | 135                   | °C |

| Т <sub>Ј</sub>   | Junction temperature                 | Ceramic packages, under bias |      | 150          |      | 150                   | °C |

|                  |                                      | Plastic packages, under bias |      | 135          |      | 135                   | °C |

| Symbol          | Parameter             | Conditions         | EP         | 610                   | EP   | Unit                  |    |

|-----------------|-----------------------|--------------------|------------|-----------------------|------|-----------------------|----|

|                 |                       |                    | Min        | Max                   | Min  | Max                   |    |

| V <sub>CC</sub> | Supply voltage        | (3)                | 4.75 (4.5) | 5.25 (5.5)            | 4.75 | 5.25                  | V  |

| VI              | Input voltage         |                    | -0.3       | V <sub>CC</sub> + 0.3 | -0.3 | V <sub>CC</sub> + 0.3 | V  |

| Vo              | Output voltage        |                    | 0          | V <sub>CC</sub>       | 0    | V <sub>CC</sub>       | V  |

| T <sub>A</sub>  | Operating temperature | For commercial use | 0          | 70                    | 0    | 70                    | °C |

|                 |                       | For industrial use | -40        | 85                    | -40  | 85                    | °C |

| t <sub>R</sub>  | Input rise time       | (4)                |            | 100 (50)              |      | 500                   | ns |

| t <sub>F</sub>  | Input fall time       | (4)                |            | 100 (50)              |      | 500                   | ns |

| Table 4         | . EP610 & EP610I Device DC Operat               | ing Conditions Note (5)                      |      |                       |      |

|-----------------|-------------------------------------------------|----------------------------------------------|------|-----------------------|------|

| Symbol          | Parameter                                       | Conditions                                   | Min  | Max                   | Unit |

| VIH             | High-level input voltage                        |                                              | 2.0  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low-level input voltage                         |                                              | -0.3 | 0.8                   | V    |

| V <sub>OH</sub> | High-level TTL output voltage                   | I <sub>OH</sub> = –4 mA DC <i>(</i> б)       | 2.4  |                       | V    |

|                 | High-level CMOS output voltage                  | I <sub>OH</sub> = -0.6 mA DC <i>(6), (7)</i> | 3.84 |                       | V    |

| V <sub>OL</sub> | Low-level output voltage                        | I <sub>OL</sub> = 4 mA DC <i>(</i> 6)        |      | 0.45                  | V    |

| II              | I/O pin leakage current of dedicated input pins | V <sub>I</sub> = V <sub>CC</sub> or ground   | -10  | 10                    | μA   |

| I <sub>OZ</sub> | Tri-state output leakage current                | $V_{O} = V_{CC}$ or ground                   | -10  | 10                    | μA   |

| Table 5           | Table 5. EP610 & EP610I Device Capacitance     Note (8) |                                     |                      |     |     |     |      |                      |     |      |      |

|-------------------|---------------------------------------------------------|-------------------------------------|----------------------|-----|-----|-----|------|----------------------|-----|------|------|

| Symbol            | Parameter                                               | Conditions                          | EP610-15<br>EP610-20 |     |     |     | EP61 | 0-25<br>0-30<br>0-35 | EP6 | 610I | Unit |

|                   |                                                         |                                     | Min                  | Max | Min | Max | Min  | Max                  |     |      |      |

| C <sub>IN</sub>   | Input pin capacitance                                   | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |                      | 10  |     | 20  |      | 8                    | pF  |      |      |

| C <sub>I/O</sub>  | I/O pin capacitance                                     | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |                      | 12  |     | 20  |      | 8                    | pF  |      |      |

| C <sub>CLK1</sub> | CLK1 pin capacitance                                    | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |                      | 20  |     | 20  |      | 10                   | pF  |      |      |

| C <sub>CLK2</sub> | CLK2 pin capacitance                                    | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |                      | 20  |     | 50  |      | 12                   | pF  |      |      |

### Table 6. EP610 Device I<sub>CC</sub> Supply Current Note (1), (9)

| Symbol           | Parameter                                              |                                                                   |                  |     | Unit |          |    |

|------------------|--------------------------------------------------------|-------------------------------------------------------------------|------------------|-----|------|----------|----|

|                  |                                                        |                                                                   | Grade            | Min | Тур  | Max      |    |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current<br>(non-Turbo, standby) | V <sub>I</sub> = V <sub>CC</sub> or ground, no load<br>(10), (11) |                  |     | 20   | 150      | μA |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current<br>(non-Turbo, active)  | $V_{I} = V_{CC}$ or ground, no load,<br>f = 1.0 MHz (10), (11)    |                  |     | 5    | 10 (15)  | mA |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current                         | $V_{I} = V_{CC}$ or ground, no load,                              | -15, -20         |     | 60   | 90 (115) | mA |

|                  | (Turbo, active)                                        | f = 1.0 MHz (11)                                                  | -25, -30,<br>-35 |     | 45   | 60 (75)  | mA |

### Table 7. EP610I Device I<sub>CC</sub> Supply Current Note (9)

| Symbol           | Parameter                                              | Conditions                                                         | EP610I |     |     | Unit |

|------------------|--------------------------------------------------------|--------------------------------------------------------------------|--------|-----|-----|------|

|                  |                                                        |                                                                    | Min    | Тур | Max |      |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current<br>(non-Turbo, standby) | V <sub>I</sub> = V <sub>CC</sub> or ground, no load,<br>(10), (11) |        | 20  | 150 | μA   |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current<br>(non-Turbo, active)  | $V_{I} = V_{CC}$ or ground, no load,<br>f = 1.0 MHz (10), (11)     |        | 3   | 8   | mA   |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current<br>(Turbo, active)      | $V_I = V_{CC}$ or ground, no load,<br>f = 1.0 MHz (11)             |        | 65  | 105 | mA   |

- (1) Numbers in parentheses are for industrial-temperature-range devices.

- (2) The minimum DC input is -0.3 V. During transitions, the inputs may undershoot to -2.0 V (EP610) or -0.5 V (EP610I) or overshoot to 7.0 V (EP610) or V<sub>CC</sub> + 0.5 V (EP610I) for input currents less than 100 mA and periods less than 20 ns.

- (3) For EP610 devices, maximum V<sub>CC</sub> rise time is 50 ms. For EP610I devices, maximum V<sub>CC</sub> rise time is unlimited with monotonic rise.

- (4) For EP610-15 and EP610-20 devices:  $t_R$  and  $t_F = 40$  ns. For EP610-15 and EP610-20 clocks:  $t_R$  and  $t_F = 20$  ns.

- (5) These values are specified in Table 3

- (6) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current; the I<sub>OL</sub> parameter refers to low-level TTL output current.

- (7) This parameter does not apply to EP610I devices.

- (8) The device capacitance is measured at 25° C and is sample-tested only.

- (9) Typical values are for  $T_A = 25^\circ C$  and  $V_{CC} = 5 V$ .

- (10) When the Turbo Bit option is not set (non-Turbo mode), EP610 devices enter standby mode if no logic transitions occur for 100 ns after the last transition. When the Turbo Bit option is not set, EP610I devices enter standby mode if no logic transitions occur for 75 ns after the last transition.

- (11) Measured with a device programmed as a 16-bit counter.

| Table 8           | 8. EP610-15 & EP610-20 Externa             | I Timing Parameters | No   | tes (1) | )    |      |                    |      |

|-------------------|--------------------------------------------|---------------------|------|---------|------|------|--------------------|------|

| Symbol            | Parameter                                  | Conditions          | EP61 | 0-15    | EP61 | 0-20 | Non-Turbo<br>Adder | Unit |

|                   |                                            |                     | Min  | Max     | Min  | Max  | (2)                |      |

| t <sub>PD1</sub>  | Input to non-registered output             | C1 = 35 pF          |      | 15.0    |      | 20.0 | 20.0               | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered output         | C1 = 35 pF          |      | 17.0    |      | 22.0 | 20.0               | ns   |

| t <sub>PZX</sub>  | Input to output enable                     | C1 = 35 pF          |      | 15.0    |      | 20.0 | 20.0               | ns   |

| t <sub>PXZ</sub>  | Input to output disable                    | C1 = 5 pF (3)       |      | 15.0    |      | 20.0 | 20.0               | ns   |

| t <sub>CLR</sub>  | Asynchronous output clear time             | C1 = 35 pF          |      | 15.0    |      | 20.0 | 20.0               | ns   |

| f <sub>MAX</sub>  | Maximum clock frequency                    | (4)                 | 83.3 |         | 62.5 |      | 0.0                | MHz  |

| t <sub>SU</sub>   | Global clock input setup time              |                     | 9.0  |         | 11.0 |      | 20.0               | ns   |

| t <sub>H</sub>    | Global clock input hold time               |                     | 0.0  |         | 0.0  |      | 0.0                | ns   |

| t <sub>CH</sub>   | Global clock high time                     |                     | 6.0  |         | 8.0  |      | 0.0                | ns   |

| t <sub>CL</sub>   | Global clock low time                      |                     | 6.0  |         | 8.0  |      | 0.0                | ns   |

| t <sub>CO1</sub>  | Global clock to output delay               |                     |      | 11.0    |      | 13.0 | 0.0                | ns   |

| t <sub>CNT</sub>  | Global clock minimum period                |                     |      | 12.0    |      | 16.0 | 0.0                | ns   |

| f <sub>CNT</sub>  | Maximum internal global clock<br>frequency | (5)                 | 83.3 |         | 62.5 |      | 0.0                | MHz  |

| t <sub>ASU</sub>  | Array clock input setup time               |                     | 6.0  |         | 8.0  |      | 20.0               | ns   |

| t <sub>AH</sub>   | Array clock input hold time                |                     | 6.0  |         | 8.0  |      | 0.0                | ns   |

| t <sub>ACH</sub>  | Array clock high time                      |                     | 7.0  |         | 9.0  |      | 0.0                | ns   |

| t <sub>ACL</sub>  | Array clock low time                       |                     | 7.0  |         | 9.0  |      | 0.0                | ns   |

| t <sub>ODH</sub>  | Output data hold time after clock          | C1 = 35 pF (6)      | 1.0  |         | 1.0  |      | 1.0                | ns   |

| t <sub>ACO1</sub> | Array clock to output delay                |                     |      | 15.0    |      | 20.0 | 20.0               | ns   |

| t <sub>ACNT</sub> | Array clock minimum period                 |                     |      | 14.0    |      | 18.0 | 0.0                | ns   |

| f <sub>acnt</sub> | Array clock internal maximum<br>frequency  | (5)                 | 71.4 |         | 55.6 |      | 0.0                | MHz  |

| Table 9          | Table 9. EP610-15 & EP610-20 Internal Timing Parameters (Part 1 of 2) |            |      |                  |     |          |    |  |  |  |

|------------------|-----------------------------------------------------------------------|------------|------|------------------|-----|----------|----|--|--|--|

| Symbol           | Parameter                                                             | Conditions | EP61 | EP610-15 EP610-2 |     | EP610-20 |    |  |  |  |

|                  |                                                                       |            | Min  | Max              | Min | Max      |    |  |  |  |

| t <sub>IN</sub>  | Input pad and buffer delay                                            |            |      | 4.0              |     | 4.0      | ns |  |  |  |

| t <sub>IO</sub>  | I/O input pad and buffer delay                                        |            |      | 2.0              |     | 2.0      | ns |  |  |  |

| t <sub>LAD</sub> | Logic array delay                                                     |            |      | 6.0              |     | 11.0     | ns |  |  |  |

| t <sub>OD</sub>  | Output buffer and pad delay                                           | C1 = 35 pF |      | 5.0              |     | 5.0      | ns |  |  |  |

| t <sub>ZX</sub>  | Output buffer enable delay                                            | C1 = 35 pF |      | 5.0              |     | 5.0      | ns |  |  |  |

| $t_{XZ}$         | Output buffer disable delay                                           | C1 = 5 pF  |      | 5.0              |     | 5.0      | ns |  |  |  |

| Table 9          | Table 9. EP610-15 & EP610-20 Internal Timing Parameters (Part 2 of 2) |                             |     |             |     |      |      |  |  |  |

|------------------|-----------------------------------------------------------------------|-----------------------------|-----|-------------|-----|------|------|--|--|--|

| Symbol           | Parameter                                                             | Conditions EP610-15 EP610-2 |     | 610-15 EP61 |     | 0-20 | Unit |  |  |  |

|                  |                                                                       |                             | Min | Max         | Min | Max  |      |  |  |  |

| t <sub>SU</sub>  | Register setup time                                                   |                             | 5.0 |             | 4.0 |      | ns   |  |  |  |

| t <sub>H</sub>   | Register hold time                                                    |                             | 4.0 |             | 7.0 |      | ns   |  |  |  |

| t <sub>IC</sub>  | Array clock delay                                                     |                             |     | 6.0         |     | 11.0 | ns   |  |  |  |

| t <sub>ICS</sub> | Global clock delay                                                    |                             |     | 2.0         |     | 4.0  | ns   |  |  |  |

| t <sub>FD</sub>  | Feedback delay                                                        |                             |     | 1.0         |     | 1.0  | ns   |  |  |  |

| t <sub>CLR</sub> | Register clear time                                                   |                             |     | 6.0         |     | 11.0 | ns   |  |  |  |

Tables 10 and 11 show the timing parameters for EP610-25, EP610-30 and EP610-35 devices.

| Table 1           | Table 10. EP610-25, EP610-30 & EP610-35 External Timing Parameters       Notes (1) |                |      |      |      |      |      |      |                    |      |  |  |

|-------------------|------------------------------------------------------------------------------------|----------------|------|------|------|------|------|------|--------------------|------|--|--|

| Symbol            | Parameter                                                                          | Conditions     | EP61 | 0-25 | EP61 | 0-30 | EP61 | 0-35 | Non-Turbo<br>Adder | Unit |  |  |

|                   |                                                                                    |                | Min  | Max  | Min  | Max  | Min  | Max  | (2)                |      |  |  |

| t <sub>PD1</sub>  | Input to non-registered output                                                     | C1 = 35 pF     |      | 25.0 |      | 30.0 |      | 35.0 | 30.0               | ns   |  |  |

| t <sub>PD2</sub>  | I/O input to non-registered output                                                 |                |      | 27.0 |      | 32.0 |      | 37.0 | 30.0               | ns   |  |  |

| t <sub>PZX</sub>  | Input to output enable                                                             |                |      | 25.0 |      | 30.0 |      | 35.0 | 30.0               | ns   |  |  |

| t <sub>PXZ</sub>  | Input to output disable                                                            | C1 = 5 pF (3)  |      | 25.0 |      | 30.0 |      | 35.0 | 30.0               | ns   |  |  |

| t <sub>CLR</sub>  | Asynchronous output clear time                                                     | C1 = 35 pF     |      | 27.0 |      | 32.0 |      | 37.0 | 30.0               | ns   |  |  |

| f <sub>MAX</sub>  | Maximum frequency                                                                  | (4)            | 47.6 |      | 41.7 |      | 37.0 |      | 0.0                | MHz  |  |  |

| t <sub>SU</sub>   | Global clock input setup time                                                      |                | 21.0 |      | 24.0 |      | 27.0 |      | 30.0               | ns   |  |  |

| t <sub>H</sub>    | Global clock input hold time                                                       |                | 0.0  |      | 0.0  |      | 0.0  |      | 0.0                | ns   |  |  |

| t <sub>CH</sub>   | Global clock high time                                                             |                | 10.0 |      | 11.0 |      | 12.0 |      | 0.0                | ns   |  |  |

| t <sub>CL</sub>   | Global clock low time                                                              |                | 10.0 |      | 11.0 |      | 12.0 |      | 0.0                | ns   |  |  |

| t <sub>CO1</sub>  | Global clock to output delay                                                       |                |      | 15.0 |      | 17.0 |      | 20.0 | 0.0                | ns   |  |  |

| t <sub>CNT</sub>  | Global clock minimum period                                                        |                |      | 25.0 |      | 30.0 |      | 35.0 | 0.0                | ns   |  |  |

| f <sub>CNT</sub>  | Maximum internal global clock<br>frequency                                         | (5)            | 40.0 |      | 33.3 |      | 28.6 |      | 0.0                | MHz  |  |  |

| t <sub>ASU</sub>  | Array clock input setup time                                                       |                | 8.0  |      | 8.0  |      | 8.0  |      | 30.0               | ns   |  |  |

| t <sub>AH</sub>   | Array clock input hold time                                                        |                | 12.0 |      | 12.0 |      | 12.0 |      | 0.0                | ns   |  |  |

| t <sub>ACH</sub>  | Array clock high time                                                              |                | 10.0 |      | 11.0 |      | 12.0 |      | 0.0                | ns   |  |  |

| t <sub>ACL</sub>  | Array clock low time                                                               |                | 10.0 |      | 11.0 |      | 12.0 |      | 0.0                | ns   |  |  |

| t <sub>ODH</sub>  | Output data hold time after clock                                                  | C1 = 35 pF (6) | 1.0  |      | 1.0  |      | 1.0  |      |                    | ns   |  |  |

| t <sub>ACO1</sub> | Array clock to output delay                                                        |                |      | 27.0 |      | 32.0 |      | 37.0 | 30.0               | ns   |  |  |

| t <sub>ACNT</sub> | Array clock minimum period                                                         |                |      | 25.0 |      | 30.0 |      | 35.0 | 0.0                | ns   |  |  |

| f <sub>acnt</sub> | Maximum internal global clock<br>frequency                                         | (5)            | 40.0 |      | 33.3 |      | 28.6 |      | 0.0                | MHz  |  |  |

| Table 1          | Table 11. EP610-25, EP610-30 & EP610-35 Internal Timing Parameters |            |          |      |          |      |          |      |      |  |  |  |

|------------------|--------------------------------------------------------------------|------------|----------|------|----------|------|----------|------|------|--|--|--|

| Symbol           | Parameter                                                          | Condition  | EP610-25 |      | EP610-30 |      | EP610-35 |      | Unit |  |  |  |

|                  |                                                                    |            | Min      | Max  | Min      | Мах  | Min      | Max  | 1    |  |  |  |

| t <sub>IN</sub>  | Input pad and buffer delay                                         |            |          | 8.0  |          | 9.0  |          | 11.0 | ns   |  |  |  |

| t <sub>IO</sub>  | I/O input pad and buffer delay                                     |            |          | 2.0  |          | 2.0  |          | 2.0  | ns   |  |  |  |

| t <sub>LAD</sub> | Logic array delay                                                  |            |          | 11.0 |          | 14.0 |          | 15.0 | ns   |  |  |  |

| t <sub>OD</sub>  | Output buffer and pad delay                                        | C1 = 35 pF |          | 6.0  |          | 7.0  |          | 9.0  | ns   |  |  |  |

| $t_{ZX}$         | Output buffer enable delay                                         | C1 = 35 pF |          | 6.0  |          | 7.0  |          | 9.0  | ns   |  |  |  |

| t <sub>XZ</sub>  | Output buffer disable delay                                        | C1 = 5 pF  |          | 6.0  |          | 7.0  |          | 9.0  | ns   |  |  |  |

| t <sub>SU</sub>  | Register setup time                                                |            | 11.0     |      | 11.0     |      | 12.0     |      | ns   |  |  |  |

| t <sub>H</sub>   | Register hold time                                                 |            | 10.0     |      | 10.0     |      | 10.0     |      | ns   |  |  |  |

| t <sub>IC</sub>  | Array clock delay                                                  |            |          | 13.0 |          | 16.0 |          | 17.0 | ns   |  |  |  |

| t <sub>ICS</sub> | Global clock delay                                                 |            |          | 1.0  |          | 1.0  |          | 0.0  | ns   |  |  |  |

| t <sub>FD</sub>  | Feedback delay                                                     |            |          | 3.0  |          | 5.0  |          | 8.0  | ns   |  |  |  |

| t <sub>CLR</sub> | Register clear time                                                |            |          | 13.0 |          | 16.0 |          | 17.0 | ns   |  |  |  |

# Γ

#### Notes to tables:

- (1) These values are specified in Table 3

- The non-Turbo adder must be added to this parameter when the Turbo Bit option is off. (2)

- (3) Sample-tested only for an output change of 500 mV.

- (4) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- (5) Measured with a device programmed as a 16-bit counter.

- (6) Sample-tested only. This parameter is a guideline based on extensive device characterization. This parameter applies for both global and array clocking.

٦

| Table 12          | 2. EP610I External Timing Par              | ameters           | Votes ( | 1)    |           |       |      |               |                    |      |

|-------------------|--------------------------------------------|-------------------|---------|-------|-----------|-------|------|---------------|--------------------|------|

| Symbol            | Parameter                                  | Conditions        | EP61    | 0I-10 | EP61      | 0I-12 | EP61 | <b>0I-1</b> 5 | Non-Turbo<br>Adder | Unit |

|                   |                                            |                   | Min     | Max   | Min       | Max   | Min  | Max           | (2)                |      |

| t <sub>PD1</sub>  | Input to non-registered output             | C1 = 35 pF        |         | 10.0  |           | 12.0  |      | 15.0          | 25.0               | ns   |

| t <sub>PD2</sub>  | I/O input to non-registered output         |                   |         | 10.0  |           | 12.0  |      | 15.0          | 25.0               | ns   |

| t <sub>PZX</sub>  | Input to output enable                     |                   |         | 15.0  |           | 15.0  |      | 18.0          | 25.0               | ns   |

| t <sub>PXZ</sub>  | Input to output disable                    | C1 = 5 pF (3)     |         | 13.0  |           | 15.0  |      | 18.0          | 25.0               | ns   |

| t <sub>CLR</sub>  | Asynchronous output clear time             | C1 = 35 pF        |         | 13.0  |           | 15.0  |      | 18.0          | 25.0               | ns   |

| f <sub>MAX</sub>  | Maximum frequency                          | (4)               | 125.0   |       | 100.<br>0 |       | 83.3 |               | 0.0                | MHz  |

| t <sub>SU</sub>   | Global clock input setup time              |                   | 7.0     |       | 9.0       |       | 12.0 |               | 25                 | ns   |

| t <sub>H</sub>    | Global clock input hold time               |                   | 0.0     |       | 0.0       |       | 0.0  |               | 0.0                | ns   |

| t <sub>CH</sub>   | Global clock high time                     |                   | 5.0     |       | 5.0       |       | 5.0  |               | 0.0                | ns   |

| t <sub>CL</sub>   | Global clock low time                      |                   | 5.0     |       | 5.0       |       | 5.0  |               | 0.0                | ns   |

| t <sub>CO1</sub>  | Global clock to output delay               |                   |         | 6.5   |           | 8.0   |      | 8.0           | 0.0                | ns   |

| t <sub>CNT</sub>  | Global clock minimum period                |                   |         | 10.0  |           | 12.0  |      | 15.0          | 25.0               | ns   |

| f <sub>CNT</sub>  | Maximum internal global clock<br>frequency | (5)               | 100.0   |       | 83.3      |       | 66.0 |               | 0.0                | MHz  |

| t <sub>ASU</sub>  | Array clock input setup time               |                   | 1.5     |       | 3.0       |       | 4.0  |               | 25.0               | ns   |

| t <sub>AH</sub>   | Array clock input hold time                |                   | 5.5     |       | 6.0       |       | 6.0  |               | 0.0                | ns   |

| t <sub>ACH</sub>  | Array clock high time                      |                   | 5.0     |       | 5.0       |       | 6.0  |               | 0.0                | ns   |

| t <sub>ACL</sub>  | Array clock low time                       |                   | 5.0     |       | 5.0       |       | 6.0  |               | 0.0                | ns   |

| t <sub>odh</sub>  | Output data hold time after clock          | C1 = 35 pF<br>(6) | 1.0     |       | 1.0       |       | 1.0  |               |                    | ns   |

| t <sub>ACO1</sub> | Array clock to output delay                |                   |         | 12.0  |           | 14.0  |      | 16.0          | 25.0               | ns   |

| t <sub>ACNT</sub> | Array clock minimum period                 |                   |         | 10.0  |           | 12.0  |      | 15.0          | 25.0               | ns   |

| f <sub>acnt</sub> | Maximum internal array clock<br>frequency  | (5)               | 100.0   |       | 83.3      |       | 66.0 |               | 0.0                | MHz  |

| Table 13.        | EP610 Internal Timing Para     | nmeters    |      |           |     |           |     |           |    |

|------------------|--------------------------------|------------|------|-----------|-----|-----------|-----|-----------|----|

| Symbol           | Parameter                      | Conditions | EP61 | EP610I-10 |     | EP610I-12 |     | EP610I-15 |    |

|                  |                                |            | Min  | Max       | Min | Max       | Min | Max       |    |

| t <sub>IN</sub>  | Input pad and buffer delay     |            |      | 1.5       |     | 4.0       |     | 4.0       | ns |

| t <sub>IO</sub>  | I/O input pad and buffer delay |            |      | 0.0       |     | 0.0       |     | 0.0       | ns |

| t <sub>LAD</sub> | Logic array delay              |            |      | 5.5       |     | 6.0       |     | 9.0       | ns |

| t <sub>OD</sub>  | Output buffer and pad delay    | C1 = 35 pF |      | 3.0       |     | 2.0       |     | 2.0       | ns |

| t <sub>ZX</sub>  | Output buffer enable delay     | C1 = 35 pF |      | 8.0       |     | 5.0       |     | 6.0       | ns |

| t <sub>XZ</sub>  | Output buffer disable delay    | C1 = 5 pF  |      | 6.0       |     | 5.0       |     | 6.0       | ns |

| t <sub>SU</sub>  | Register setup time            |            | 3.5  |           | 5.0 |           | 5.0 |           | ns |

| t <sub>H</sub>   | Register hold time             |            | 3.5  |           | 4.0 |           | 7.0 |           | ns |

| t <sub>IC</sub>  | Array clock delay              |            |      | 7.5       |     | 8.0       |     | 10.0      | ns |

| t <sub>ICS</sub> | Global clock delay             |            |      | 2.0       |     | 2.0       |     | 2.0       | ns |

| t <sub>FD</sub>  | Feedback delay                 |            |      | 1.0       |     | 1.0       |     | 1.0       | ns |

| t <sub>CLR</sub> | Register clear time            |            |      | 8.5       |     | 9.0       |     | 12.0      | ns |

#### Table do EDCADIAL . .... \_ .

#### Notes to tables:

- These values are specified in Table 3 (1)

- (2) The non-Turbo adder must be added to this parameter when the Turbo Bit option is off.

- (3) Sample-tested only for an output change of 500 mV.

- (4) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

- Measured with a device programmed as a 16-bit counter. (5)

- (6) Sample-tested only. This parameter is a guideline based on extensive device characterization. This parameter applies for both global and array clocking.

Rochester EPLD devices normally sold in the un-configured state are tested using the original manufacturer's test software to guarantee the data sheet specifications. In some cases, EPLD devices can be configured to the customer's design and fully tested as such.

Notes:

# EP910 EPLD

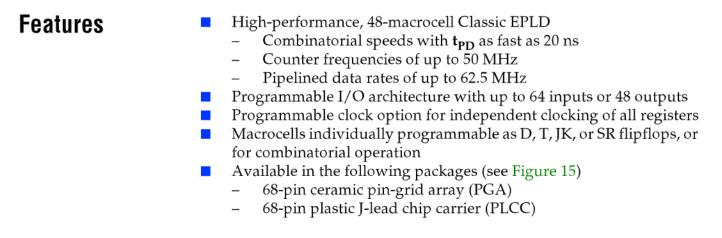

# Features

- High-performance, 24-macrocell Classic EPLD

- Combinatorial speeds with **t**<sub>PD</sub> as fast as 12 ns

- Counter frequencies of up to 76.9 MHz

- Pipelined data rates of up to 125 MHz

- Programmable I/O architecture with up to 36 inputs or 24 outputs

- EP910 and EP910I devices are pin-, function-, and programming filecompatible

- Programmable clock option for independent clocking of all registers

- Macrocells individually programmable as D, T, JK, or SR flipflops, or for combinatorial operation

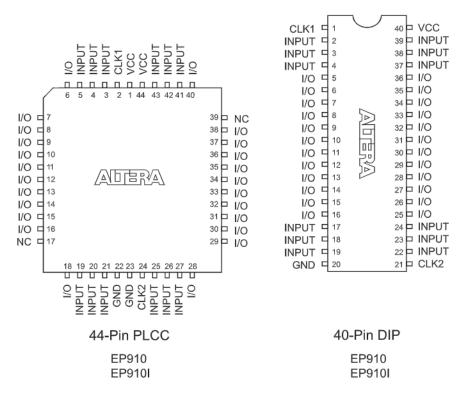

- Available in the following packages (see Figure 11)

- 44-pin plastic J-lead chip carrier (PLCC)

- 40-pin ceramic and plastic dual in-line packages (CerDIP and PDIP)

Package outlines are not drawn to scale. Windows in ceramic packages only.

# General Description

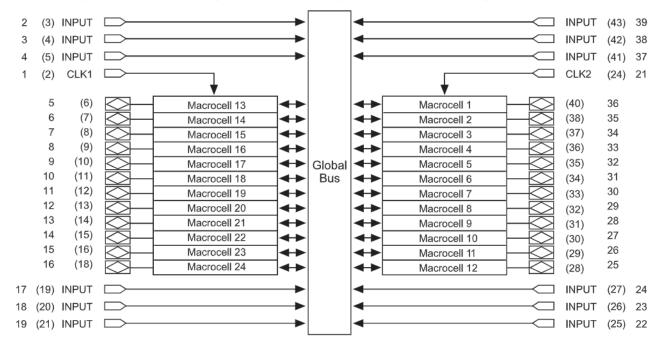

EP910 devices can implement up to 450 usable gates of SSI and MSI logic functions. EP910 devices have 24 macrocells, 12 dedicated input pins, 24 I/O pins, and 2 global clock pins. Each macrocell can access signals from the global bus, which consists of the true and complement forms of the dedicated inputs and the true complement forms of either the output of the macrocell or the I/O input. The CLK1 and CLK2 signals are the dedicated clock inputs for the registers in macrocells 13 through 24 and 1 through 12, respectively.

#### Figure 12. EP910 Block Diagram

Numbers without parentheses are for DIP packages. Numbers in parentheses are for J-lead packages.

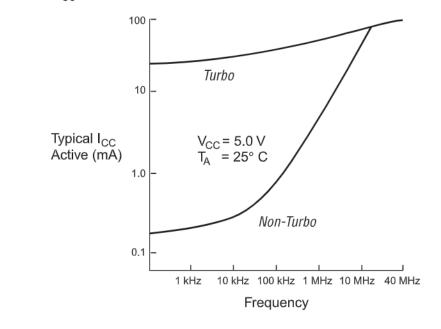

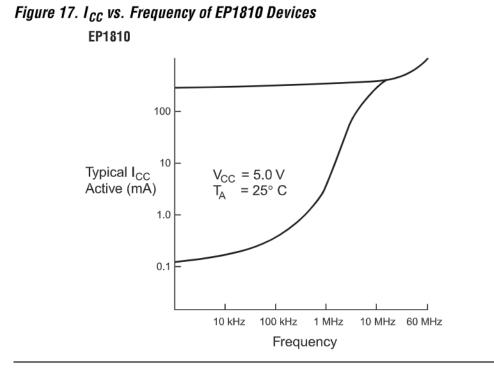

Figure 13. I<sub>CC</sub> vs. Frequency of EP910 Devices

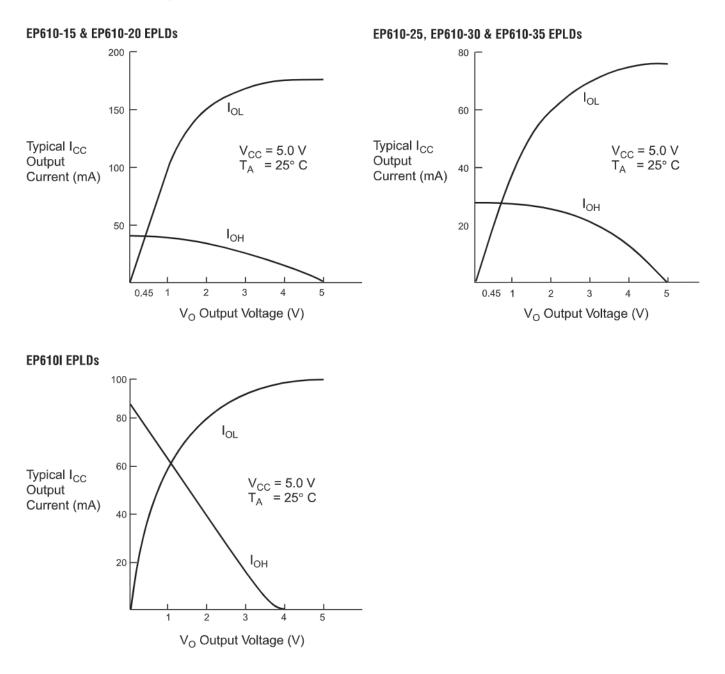

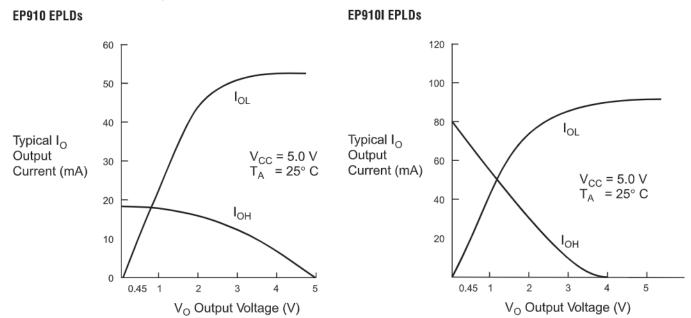

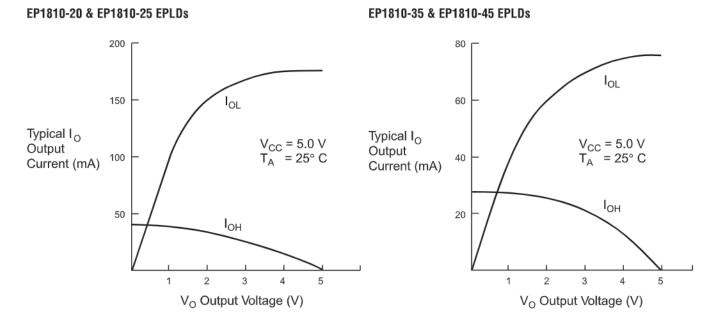

Figure 14 shows the typical output drive characteristics of EP910 devices.

Drive characteristics may exceed shown curves.

Specification Number EP610\_910\_1810-CI (AT) Rev B

# Operating Conditions

Tables 14 through 18 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for EP910 and EP910I devices.

| Table 1          | 4. EP910 & EP910I Device Ab   | solute Maximum Ratings          | Notes | s (1) |      |                       |      |

|------------------|-------------------------------|---------------------------------|-------|-------|------|-----------------------|------|

| Symbol           | Parameter                     | Conditions EP910 EP910I         |       |       |      | 910I                  | Unit |

|                  |                               |                                 | Min   | Max   | Min  | Max                   |      |

| V <sub>CC</sub>  | Supply voltage                | With respect to ground (2)      | -2.0  | 7.0   | -2.0 | 7.0                   | V    |

| VI               | DC input voltage              |                                 | -2.0  | 7.0   | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>MAX</sub> | DC $V_{CC}$ or ground current |                                 | -250  | 250   |      |                       | mA   |

| I <sub>OUT</sub> | DC output current, per pin    |                                 | -25   | 25    |      |                       | mA   |

| T <sub>STG</sub> | Storage temperature           | No bias                         | -65   | 150   | -65  | 150                   | °C   |

| T <sub>AMB</sub> | Ambient temperature           | Under bias                      | -65   | 135   | -65  | 135                   | °C   |

| TJ               | Junction temperature          | Ceramic packages, under bias    |       | 150   |      | 150                   | °C   |

|                  |                               | Plastic packages, under<br>bias |       | 135   |      | 135                   | °C   |

| Table 15. EP910 & EP910I Device Recommended Operating Conditions       Notes (1) |                       |                    |            |                       |      |                       |    |  |  |  |

|----------------------------------------------------------------------------------|-----------------------|--------------------|------------|-----------------------|------|-----------------------|----|--|--|--|

| Symbol                                                                           | Parameter             | Conditions         | EP         | 910                   | EP   | Unit                  |    |  |  |  |

|                                                                                  |                       |                    | Min        | Min Max               |      | Max                   | 1  |  |  |  |

| V <sub>CC</sub>                                                                  | Supply voltage        | (3)                | 4.75 (4.5) | 5.25 (5.5)            | 4.75 | 5.25                  | V  |  |  |  |

| VI                                                                               | Input voltage         |                    | -0.3       | V <sub>CC</sub> + 0.3 | -0.3 | V <sub>CC</sub> + 0.3 | V  |  |  |  |

| Vo                                                                               | Output voltage        |                    | 0          | V <sub>CC</sub>       | 0    | V <sub>CC</sub>       | V  |  |  |  |

| T <sub>A</sub>                                                                   | Operating temperature | For commercial use | 0          | 70                    | 0    | 70                    | °C |  |  |  |

|                                                                                  |                       | For industrial use | -40        | 85                    |      |                       | °C |  |  |  |

| t <sub>R</sub>                                                                   | Input rise time       | (4)                |            | 100 (50)              |      | 500                   | ns |  |  |  |

| t <sub>F</sub>                                                                   | Input fall time       | (4)                |            | 100 (50)              |      | 500                   | ns |  |  |  |

Table 16. EP910 & EP910I Device DC Operating Conditions

Notes (5), (6)

| Symbol          | Parameter                                   | Conditions                                   | Min  | Max                   | Unit |

|-----------------|---------------------------------------------|----------------------------------------------|------|-----------------------|------|

| VIH             | High-level input voltage                    |                                              | 2.0  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low-level input voltage                     |                                              | -0.3 | 0.8                   | V    |

| V <sub>OH</sub> | High-level TTL output voltage               | I <sub>OH</sub> =4 mA DC (7)                 | 2.4  |                       | V    |

|                 | High-level CMOS output voltage              | I <sub>OH</sub> = –0.6 mA DC <i>(7), (8)</i> | 3.84 |                       | V    |

| V <sub>OL</sub> | Low-level output voltage                    | I <sub>OL</sub> = 4 mA DC <i>(7)</i>         |      | 0.45                  | V    |

| I <sub>I</sub>  | I/O leakage current of dedicated input pins | $V_{I} = V_{CC}$ or ground                   | -10  | 10                    | μA   |

| I <sub>OZ</sub> | Tri-state output leakage current            | $V_{O} = V_{CC}$ or ground                   | -10  | 10                    | μA   |

| Table 1           | Table 17. EP910 & EP910I Device Capacitance     Notes (5) |                                     |     |     |     |     |      |  |  |  |  |

|-------------------|-----------------------------------------------------------|-------------------------------------|-----|-----|-----|-----|------|--|--|--|--|

| Symbol            | Parameter                                                 | Conditions                          | EP  | 910 | EP9 | 101 | Unit |  |  |  |  |

|                   |                                                           |                                     | Min | Max | Min | Max |      |  |  |  |  |

| C <sub>IN</sub>   | Input pin capacitance                                     | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 20  |     | 8   | pF   |  |  |  |  |

| C <sub>I/O</sub>  | I/O pin capacitance                                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 20  |     | 8   | pF   |  |  |  |  |

| C <sub>CLK1</sub> | CLK1 pin capacitance                                      | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 20  |     | 10  | pF   |  |  |  |  |

| C <sub>CLK2</sub> | CLK2 pin capacitance                                      | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 60  |     | 12  | pF   |  |  |  |  |

| Table 18. EP910 & EP910I Device I <sub>cc</sub> Supply Current | Notes (1), (5), (6) |

|----------------------------------------------------------------|---------------------|

|----------------------------------------------------------------|---------------------|

| Symbol           | Parameter                                              | Conditions                                                       |     | EP910 EP910I |             | I   | Unit |     |    |

|------------------|--------------------------------------------------------|------------------------------------------------------------------|-----|--------------|-------------|-----|------|-----|----|

|                  |                                                        |                                                                  | Min | Тур          | Max         | Min | Тур  | Max |    |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current<br>(non-Turbo, standby) | V <sub>I</sub> = V <sub>CC</sub> or ground, no load<br>(9), (10) |     | 20           | 150         |     | 60   | 150 | μA |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current<br>(non-Turbo, active)  | $V_{I} = V_{CC}$ or ground, no load,<br>f = 1.0 MHz (9), (10)    |     | 6            | 20          |     | 4    | 12  | mA |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current<br>(Turbo, active)      | $V_I = V_{CC}$ or ground, no load,<br>f = 1.0 MHz (10)           |     | 45           | 80<br>(100) |     | 120  | 150 | mA |

- (1) Numbers in parentheses are for industrial-temperature-range devices.

- (2) The minimum DC input is -0.3 V. During transitions, the inputs may undershoot to -2.0 V (EP910) or

- (3) -0.5 V (EP910I) or overshoot to 7.0 V (EP910) or V<sub>CC</sub> + 0.5 V (EP910I) for input currents less than 100 mA and periods less than 20 ns.

Maximum  $V_{CC}$  rise time for EP910 devices = 50 ms; for EP910I devices, maximum  $V_{CC}$  rise time is unlimited with (4) monotonic rise.

- For all clocks:  $t_R$  and  $t_F$  = 100 ns (50 ns for the industrial-temperature-range version).

- (5) These values are specified in Table 15

- (6) The device capacitance is measured at 25° C and is sample-tested only.

- (7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current; the I<sub>OL</sub> parameter refers to low-level TTL

- (8) output current. This parameter does not apply to EP910I devices

- This parameter does not apply to EP910I devices.

- (9) When the Turbo Bit option is not set (non-Turbo mode), an EP910 device will enter standby mode if no logic

- (10) transitions occur for 100 ns after the last transition, and an EP910I device will enter standby mode if no logic transitions occur for 75 ns after the last transition.

Magnute device programmed as a 24 bit counter.

Measured with a device programmed as a 24-bit counter.

| Table 1           | Table 19. EP910 External Timing Parameters     Notes (1) |               |      |      |      |      |      |      |                    |      |  |  |

|-------------------|----------------------------------------------------------|---------------|------|------|------|------|------|------|--------------------|------|--|--|

| Symbol            | Parameter                                                | Conditions    | EP91 | 0-30 | EP91 | 0-35 | EP91 | 0-40 | Non-               | Unit |  |  |

|                   |                                                          |               | Min  | Max  | Min  | Max  | Min  | Max  | Turbo<br>Adder (2) |      |  |  |

| t <sub>PD1</sub>  | Input to non-registered output                           | C1 = 35 pF    |      | 30.0 |      | 35.0 |      | 40.0 | 30.0               | ns   |  |  |

| t <sub>PD2</sub>  | I/O input to non-registered output                       | C1 = 35 pF    |      | 33.0 |      | 38.0 |      | 43.0 | 30.0               | ns   |  |  |

| t <sub>PZX</sub>  | Input to output enable                                   | C1 = 35 pF    |      | 30.0 |      | 35.0 |      | 40.0 | 30.0               | ns   |  |  |

| t <sub>PXZ</sub>  | Input to output disable                                  | C1 = 5 pF (3) |      | 30.0 |      | 35.0 |      | 40.0 | 30.0               | ns   |  |  |

| t <sub>CLR</sub>  | Asynchronous output clear time                           | C1 = 35 pF    |      | 33.0 |      | 38.0 |      | 43.0 | 30.0               | ns   |  |  |

| f <sub>MAX</sub>  | Maximum frequency                                        | (4)           | 41.7 |      | 37.0 |      | 32.3 |      | 0.0                | MHz  |  |  |

| t <sub>su</sub>   | Global clock input setup time                            |               | 24.0 |      | 27.0 |      | 31.0 |      | 30.0               | ns   |  |  |

| t <sub>H</sub>    | Global clock input hold time                             |               | 0.0  |      | 0.0  |      | 0.0  |      | 0.0                | ns   |  |  |

| t <sub>CH</sub>   | Global clock high time                                   |               | 12.0 |      | 13.0 |      | 15.0 |      | 0.0                | ns   |  |  |

| t <sub>CL</sub>   | Global clock low time                                    |               | 12.0 |      | 13.0 |      | 15.0 |      | 0.0                | ns   |  |  |

| t <sub>CO1</sub>  | Global clock to output delay                             | C1 = 35 pF    |      | 18   |      | 21.0 |      | 24.0 | 0.0                | ns   |  |  |

| t <sub>CNT</sub>  | Global clock minimum clock period                        | (5)           |      | 30.0 |      | 35.0 |      | 40.0 | 0.0                | ns   |  |  |

| f <sub>CNT</sub>  | Maximum internal global clock<br>frequency               | (5)           | 33.3 |      | 28.6 |      | 25.0 |      | 0.0                | MHz  |  |  |

| t <sub>ASU</sub>  | Array clock input setup time                             |               | 10.0 |      | 10.0 |      | 10.0 |      | 30.0               | ns   |  |  |

| t <sub>AH</sub>   | Array clock input hold time                              |               | 15.0 |      | 15.0 |      | 15.0 |      | 0.0                | ns   |  |  |

| t <sub>ACH</sub>  | Array clock high time                                    |               | 15.0 |      | 16.0 |      | 17.0 |      | 0.0                | ns   |  |  |

| t <sub>ACL</sub>  | Array clock low time                                     |               | 15.0 |      | 16.0 |      | 17.0 |      | 0.0                | ns   |  |  |

| t <sub>ODH</sub>  | Output data hold time after clock                        | C1 = 35 pF(6) | 1.0  |      | 1.0  |      | 1.0  |      |                    | ns   |  |  |

| t <sub>ACO1</sub> | Array clock to output delay                              | C1 = 35 pF    |      | 33.0 |      | 38.0 |      | 43.0 | 30.0               | ns   |  |  |

| t <sub>ACNT</sub> | Array clock minimum clock period                         |               |      | 30.0 |      | 35.0 |      | 40.0 | 0.0                | ns   |  |  |

| f <sub>acnt</sub> | Maximum internal array clock<br>frequency                | (5)           | 33.3 |      | 28.6 |      | 25.0 |      | 0.0                | MHz  |  |  |

| Table 20. EP910 Internal Timing Parameters |                                |            |      |          |      |      |          |      |      |  |  |

|--------------------------------------------|--------------------------------|------------|------|----------|------|------|----------|------|------|--|--|