# 93847 0/0543

### HIGH SPEED 6-BIT IDENTITY COMPARATOR

**DESCRIPTION** — The '47 is a very high speed 6-bit identity comparator. The device features an open-collector output for wired-OR expansion and active LOW Enable. The '47 is fabricated with the Schottky barrier diode process for high speed, and is completely compatible with all TTL families. This device is recommended for applications where wired-OR expansion is desired and the speed of an active pull-up is not required. The '47 is a pin-for-pin replacement for the DM7160/8160.

- SCHOTTKY PROCESS FOR HIGH SPEED

- COMPARE TWO 6-BIT WORDS IN 15 ns

- OPEN-COLLECTOR OUTPUT FOR WIRED-OR EXPANSION

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                          | PKG<br>TYPE |  |

|--------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------|--|

| PKGS               | ОUТ | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C} \text{ to } +125^{\circ} \text{ C}$ |             |  |

| Plastic<br>DIP (P) | А   | 93S47PC                                                                                  |                                                                                                         | 9B          |  |

| Ceramic<br>DIP (D) | А   | 93S47DC                                                                                  | 93S47DM                                                                                                 | 6B          |  |

| Flatpak<br>(F)     | Α   | 93S47FC                                                                                  | 93S47FM                                                                                                 | 4L          |  |

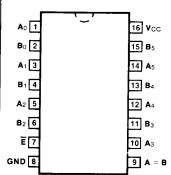

## CONNECTION DIAGRAM PINOUT A

#### INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                                                        | DESCRIPTION                                                               | 93S (U.L.)<br>HIGH/LOW                          |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------|

| A <sub>0</sub> — A <sub>5</sub><br>B <sub>0</sub> — B <sub>5</sub><br>E<br>A = B | Word A Inputs Word B Inputs Enable Input (Active LOW) A Equal to B Output | 1.25/1.25<br>1.25/1.25<br>1.25/1.25<br>OC'/12.5 |

\*OC - Open Collector

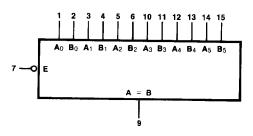

#### LOGIC SYMBOL

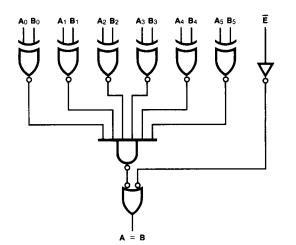

Vcc = Pin 16 GND = Pin 8 **FUNCTIONAL DESCRIPTION** — The '47 is a very high speed 6-bit identity comparator. When enabled ( $\overline{E}$  input LOW), the A = B output is HigHif the two 6-bit words are equal. When disabled ( $\overline{E}$  input HIgH), the A = B output is forced HIGH. Equality is determined by Exclusive-NOR circuits which individually compare the equivalent bits from each word. Since the A = B output state is determined by the equality of each pair of inputs, the equivalent  $A_n$  and  $B_n$  pins can be interchanged to facilitate board layout or wiring. The active LOW Enable ( $\overline{E}$ ) can be used as a high speed strobe. When the Enable is HIGH, the A = B output is forced HIGH. This allows devices tied to a common wired-OR (actually wired-AND) node to be strobed individually or in groups. Only the enabled devices will determine the state of the output node.

$$(\mathsf{A} = \mathsf{B}) = \overline{\mathsf{E}} + (\overline{\mathsf{A}_0 \oplus \mathsf{B}_0}) \bullet (\overline{\mathsf{A}_1 \oplus \mathsf{B}_1}) \bullet (\overline{\mathsf{A}_2 \oplus \mathsf{B}_2}) \bullet (\overline{\mathsf{A}_3 \oplus \mathsf{B}_3}) \bullet (\overline{\mathsf{A}_4 \oplus \mathsf{B}_4}) \bullet (\overline{\mathsf{A}_5 \oplus \mathsf{B}_5})$$

#### LOGIC DIAGRAM

#### TRUTH TABLE

| INPUTS |                | OUTPUT |  |  |

|--------|----------------|--------|--|--|

| E      | An, Bn         | A = B  |  |  |

| L      | $A_n = B_n$    | Ħ      |  |  |

| L      | $A_n \neq B_n$ | L      |  |  |

| н      | $A_n \neq B_n$ | н      |  |  |

| Н      | $A_n = B_n$    | н      |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 938 |     | UNITS | CONDITIONS            |

|--------|----------------------|-----|-----|-------|-----------------------|

| 01202  |                      | Min | Max |       |                       |

| lcc    | Power Supply Current |     | 65  | mA    | V <sub>CC</sub> = Max |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C (See Section 3 for waveforms and load configurations)

|              |                                     | 9          | 93S<br>C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 280 Ω |    | CONDITIONS                                                                        |

|--------------|-------------------------------------|------------|---------------------------------------------------------|----|-----------------------------------------------------------------------------------|

| SYMBOL       | PARAMETER                           | . –        |                                                         |    |                                                                                   |

|              |                                     | Min        | Max                                                     |    |                                                                                   |

| tpLH<br>tpHL | Propagation Delay An or Bn to A = B | 5.0<br>5.0 | 17<br>17                                                | ns | E = Gnd, Other Inputs<br>= 4.5 V, Test each input<br>individually, Figs. 3-2, 3-5 |

| tpLH<br>tpHL | Propagation Delay An or Bn to A = B | 4.0<br>4.0 | 14<br>15                                                | ns | E = Gnd, Other Inputs<br>= Gnd, Test each input<br>individually, Figs. 3-2, 3-4   |

| tpLH<br>tpHL | Propagation Delay E to A = B        | 3.0<br>3.0 | 10<br>10                                                | ns | A <sub>n</sub> ≠ B <sub>n</sub><br>Figs. 3-2, 3-5                                 |