**Features**

## **High-Efficiency CCFL Backlight Controller with SMBus Interface**

### **General Description**

The MAX8709/MAX8709A integrated backlight controller are optimized to drive cold-cathode fluorescent lamps (CCFLs) using a resonant full-bridge inverter architecture. The resonant operation maximizes striking capability and provides near-sinusoidal waveforms over the entire input range to improve CCFL lifetime. The controller operates over a wide input voltage range of 4.6V to 28V with high power-to-light efficiency. The device also includes safety features that effectively protect against many single-point fault conditions including lamp-out and short-circuit faults.

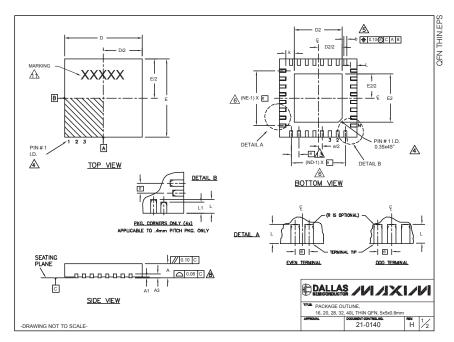

The MAX8709/MAX8709A achieve 10:1 dimming range by "chopping" the lamp current on and off using a digital pulse-width-modulation (DPWM) method. The minimum DPWM duty cycle of the MAX8709 is 9.375% and the minumum duty cycle of the MAX8709A is 12.5%. The brightness is controlled with a 2-wire SMBus™-compatible interface. The device directly drives the four external N-channel power MOSFETs of the full-bridge inverter. An internal 5.3V linear regulator powers the MOSFET drivers, the DPWM oscillator, and most of the internal circuitry. The MAX8709/MAX8709A are available in a space-saving 28-pin thin QFN package and operates over a -40°C to +85°C temperature range.

### **Applications**

LCD TVs

Notebook Computer Displays LCD Monitors

**Automotive Displays**

SMBus is a trademark of Intel Corp.

## **♦** Synchronized to Resonant Frequency

- **Longer Lamp Life Guaranteed Striking Capability High Power-to-Light Efficiency**

- ♦ Wide Input Voltage Range (4.6V to 28V)

- **♦** Feed Forward for Excellent Line Rejection

- **♦ SMBus Dimming Control Interface**

- ♦ 10:1 Dimming Range

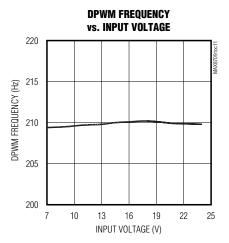

- ♦ Guaranteed 200Hz to 220Hz DPWM Frequency

- ♦ Secondary Voltage Limit Reduces Transformer **Stress**

- ♦ Adjustable Lamp-Out Protection with 1s Timer

- ♦ Secondary Current Limit Protects Against High-**Voltage Short Circuits to Ground**

- ♦ Small 5mm x 5mm Thin QFN Package

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE           |

|-------------|----------------|-----------------------|

| MAX8709ETI  | -40°C to +85°C | 28 Thin QFN 5mm x 5mm |

| MAX8709AETI | -40°C to +85°C | 28 Thin QFN 5mm x 5mm |

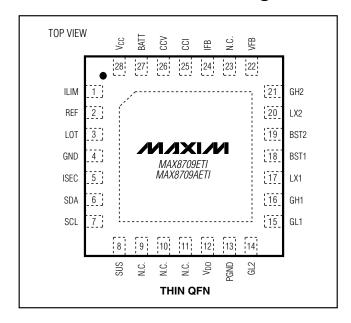

Pin Configuration appears at end of data sheet.

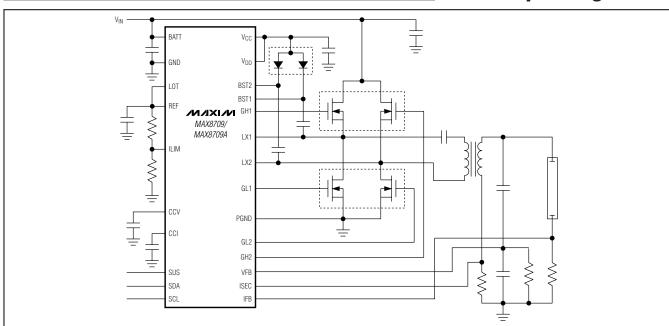

## **Minimal Operating Circuit**

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| BATT to GND                              | 0.3V to +30V                       | IFB, ISEC, VFB to GND6V to +6V                        |

|------------------------------------------|------------------------------------|-------------------------------------------------------|

| BST1, BST2 to GND                        | 0.3V to +36V                       | SDA, SCL, SUS to GND0.3V to +6V                       |

| BST1 to LX1, BST2 to LX2                 | 0.3V to +6V                        | PGND to GND0.3V to +0.3V                              |

| GH1 to LX1                               | 0.3V to (V <sub>BST1</sub> + 0.3V) | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| GH2 to LX2                               | 0.3V to (V <sub>BST2</sub> + 0.3V) | 28-Pin Thin QFN (derate 20.84mW/°C above +70°C)1667mW |

| V <sub>CC</sub> , V <sub>DD</sub> to GND | 0.3V to +6V                        | Operating Temperature Range40°C to +85°C              |

| REF, ILIM to GND                         | 0.3V to (V <sub>CC</sub> + 0.3V)   | Junction Temperature+150°C                            |

| GL1, GL2 to GND                          | 0.3V to (V <sub>DD</sub> + 0.3V)   | Storage Temperature Range65°C to +150°C               |

| CCI, CCV, LOT to GND                     | 0.3V to +6V                        | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1.  $V_{BATT} = 12V$ ,  $V_{LOT} = V_{REF}$ ,  $V_{CC} = V_{DD}$ ,  $V_{SUS} = 5.3V$ ,  $V_{A} = 0^{\circ}C$  to  $V_{BATT} = 12V$ . Typical values are at  $V_{A} = 12V$  unless otherwise noted.)

| PARAMETER                                                                                                                    | COND                                                                           | TIONS                    | MIN  | TYP  | MAX  | UNITS |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|------|------|------|-------|--|

| Value Input Voltage Dange                                                                                                    | VCC = VDD = VBATT                                                              |                          | 4.6  |      | 5.5  | V     |  |

| V <sub>BATT</sub> Input Voltage Range                                                                                        | $V_{CC} = V_{DD} = open$                                                       |                          | 5.5  |      | 28.0 | V     |  |

| Value Ouissaant Current                                                                                                      | Value F FV                                                                     | V <sub>BATT</sub> = 28V  |      | 1.5  | 3    | mA    |  |

| VBATT Quiescent Current                                                                                                      | $V_{SUS} = 5.5V$                                                               | $V_{BATT} = V_{CC} = 5V$ |      |      | 3    | IIIA  |  |

| VBATT Quiescent Current, Shutdown                                                                                            | SUS = GND                                                                      |                          |      | 6    | 20   | μΑ    |  |

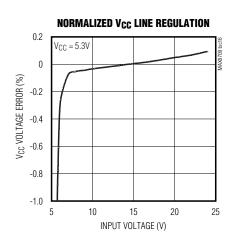

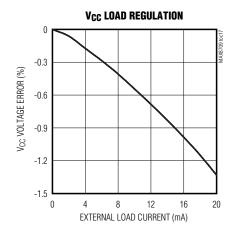

| V <sub>CC</sub> Output Voltage, Normal Operation                                                                             | V <sub>SUS</sub> = 5.5V, 6V < V <sub>B</sub> ,<br>0 < I <sub>LOAD</sub> < 20mA | ATT < 28V,               | 5.0  | 5.35 | 5.5  | V     |  |

| V <sub>CC</sub> Output Voltage, Shutdown                                                                                     | 3.5                                                                            | 4.6                      | 5.5  | V    |      |       |  |

| /CC Undervoltage-Lockout Threshold /CC Undervoltage-Lockout Hysteresis /CC Power-On Reset (POR) Threshold /CC POR Hysteresis | V <sub>CC</sub> rising (leaving loc                                            | kout)                    |      |      | 4.5  | V     |  |

|                                                                                                                              | V <sub>CC</sub> falling (entering lo                                           | ockout)                  | 4.0  |      |      | V     |  |

| V <sub>CC</sub> Undervoltage-Lockout Hysteresis                                                                              |                                                                                |                          |      | 200  |      | mV    |  |

| V <sub>CC</sub> Power-On Reset (POR) Threshold                                                                               | Rising edge                                                                    |                          | 0.90 | 1.75 | 2.70 | V     |  |

| V <sub>CC</sub> POR Hysteresis                                                                                               |                                                                                |                          |      | 50   |      | mV    |  |

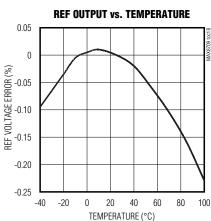

| REF Output Voltage, Normal Operation                                                                                         | 4.5V < V <sub>CC</sub> < 5.5V, I <sub>L</sub>                                  | $DAD = 40\mu A$          | 1.96 | 2.00 | 2.04 | V     |  |

| GH1, GH2, GL1, GL2 On-Resistance                                                                                             | ITEST = 100mA, V <sub>CC</sub> =                                               | $V_{DD} = 5.3V$          |      | 9    | 18   | Ω     |  |

| GH1, GH2, GL1, GL2 Output Current                                                                                            |                                                                                |                          |      | 0.5  |      | Α     |  |

| BST1, BST2 Leakage Current                                                                                                   | V <sub>BST</sub> _ = 12V, V <sub>L</sub> X_ = 7                                | 'V                       |      |      | 5    | μΑ    |  |

| Input Resonant Frequency                                                                                                     | Guaranteed by design                                                           | )                        | 25   |      | 300  | kHz   |  |

| Minimum Off-Time                                                                                                             |                                                                                |                          | 180  | 280  | 380  | ns    |  |

| Maximum Off-Time                                                                                                             |                                                                                |                          |      |      |      | μs    |  |

| Current-Limit Threshold<br>LX1 - GND, LX2 - GND (Fixed)                                                                      | ILIM = VCC                                                                     | ILIM = VCC               |      |      | 220  | mV    |  |

| Current-Limit Threshold                                                                                                      | V <sub>ILIM</sub> = 0.5V                                                       | VILIM = 0.5V             |      |      |      | ma\/  |  |

| LX1 - GND, LX2 - GND (Adjustable)                                                                                            | V <sub>ILIM</sub> = 2.0V                                                       |                          | 370  | 400  | 430  | mV    |  |

| Minimum Current Threshold<br>LX1 - GND, LX2 - GND                                                                            |                                                                                |                          |      | 6    |      | mV    |  |

\_\_ /N/XI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1.  $V_{BATT} = 12V$ ,  $V_{LOT} = V_{REF}$ ,  $V_{CC} = V_{DD}$ ,  $V_{SUS} = 5.3V$ ,  $T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                                          | CONDITIONS                       | MIN  | TYP  | MAX              | UNITS |

|--------------------------------------------------------------------|----------------------------------|------|------|------------------|-------|

| LOT Input Voltage Range                                            |                                  | 0.5  |      | V <sub>REF</sub> | V     |

| LOT Input Bias Current                                             |                                  | -2   |      | +2               | μΑ    |

| IFB Input Voltage Range                                            |                                  | -1.7 |      | +1.7             | V     |

| IFB Regulation Point                                               |                                  | 380  | 400  | 420              | mV    |

| IFB Input Bias Current                                             | V <sub>IFB</sub> = 0.4V          | -2   |      | +2               | μΑ    |

| IFB Lamp-Out Threshold                                             | LOT = REF                        | 500  | 600  | 700              | mV    |

| IFB to CCI Transconductance                                        | 1V < V <sub>CCI</sub> < 2.5V     |      | 100  |                  | μS    |

| CCI Output Impedance                                               |                                  |      | 20   |                  | МΩ    |

| ISEC Input Voltage Range                                           |                                  | -2   |      | +2               | V     |

| ISEC Regulation Threshold                                          |                                  | 1.20 | 1.25 | 1.30             | V     |

| ISEC Input Bias Current                                            | VISEC = 1.25V                    | -2   |      | +2               | μΑ    |

| VFB Input Voltage Range                                            |                                  | -2   |      | +2               | V     |

| VFB Input Bias Current                                             | V <sub>VFB</sub> = 0.5V          | -0.5 |      | +0.5             | μΑ    |

| VFB Regulation Point                                               |                                  | 490  | 510  | 530              | mV    |

| VFB to CCV Transconductance                                        | 1V < V <sub>CCV</sub> < 2.7V     |      | 40   |                  | μS    |

| VFB Zero-Voltage Crossing Threshold                                |                                  | -10  |      | +10              | mV    |

| CCV Output Impedance                                               |                                  |      | 20   |                  | МΩ    |

| Digital DWM Channing Fraguency                                     | MAX8709                          | 200  | 210  | 220              | Цэ    |

| Digital PWM Chopping Frequency                                     | MAX8709A                         | 204  | 210  | 216              | Hz    |

| Lamp-Out Detection Timeout Timer                                   | V <sub>IFB</sub> < 0.1V (Note 1) | 1.14 | 1.22 | 1.30             | S     |

| SDA, SCL, SUS Input Low Voltage                                    |                                  |      |      | 0.8              | V     |

| SDA, SCL, SUS Input High Voltage                                   |                                  | 2.1  |      |                  | V     |

| SDA, SCL, SUS Input Hysteresis                                     |                                  |      | 300  |                  | mV    |

| SDA, SCL, SUS Input Bias Current                                   |                                  | -1   |      | +1               | μΑ    |

| SDA Output Low Sink Current                                        | $V_{SDA} = 0.4V$                 | 4    |      |                  | mA    |

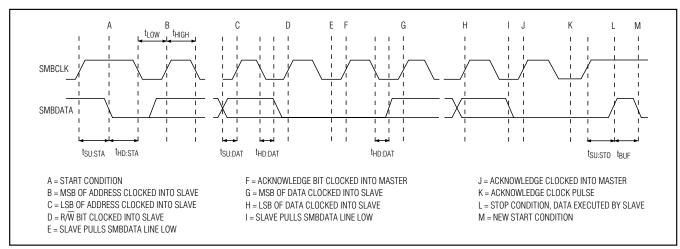

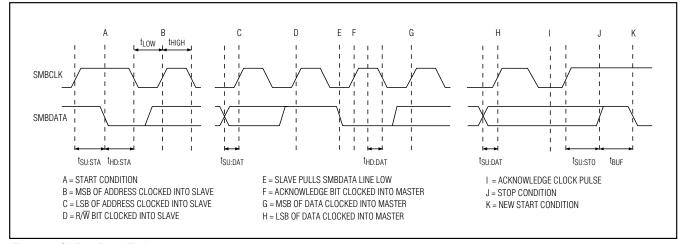

| SCL Serial Clock High Period                                       | THIGH                            | 4    |      |                  | μs    |

| SCL Serial Clock Low Period                                        | T <sub>LOW</sub>                 | 4.7  |      |                  | μs    |

| Start-Condition Setup Time                                         | tsu:sta                          | 4.7  |      |                  | μs    |

| Start-Condition Hold Time                                          | thd:sta                          | 4    |      |                  | μs    |

| SDA Valid to SCL Rising-Edge Setup Time,<br>Slave Clocking-In Data | tsu:dat                          | 250  |      |                  | ns    |

| SCL Falling Edge to SDA Transition                                 | thd:dat                          | 0    |      |                  | ns    |

| SCL Falling Edge to SDA Valid,<br>Reading Out Data                 | T <sub>DV</sub>                  |      | 700  |                  | ns    |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1.  $V_{BATT}$  = 12V,  $V_{LOT}$  =  $V_{REF}$ ,  $V_{CC}$  =  $V_{DD}$ ,  $V_{SUS}$  = 5.3V,  $T_A$  = -40°C to +85°C. Typical values are at  $T_A$  = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                               | CONDI                                                                         | TIONS                                                                                  | MIN  | TYP | MAX              | UNITS |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|------------------|-------|--|

|                                                         | V <sub>CC</sub> = V <sub>DD</sub> = V <sub>BATT</sub>                         |                                                                                        | 4.6  |     | 5.5              | .,    |  |

| V <sub>BATT</sub> Input Voltage Range                   | V <sub>CC</sub> = V <sub>DD</sub> = open                                      |                                                                                        | 5.5  |     | 28.0             | V     |  |

| V 0: 10 1                                               |                                                                               | V <sub>BATT</sub> = 28V                                                                |      |     | 3                |       |  |

| V <sub>BATT</sub> Quiescent Current                     | $V_{SUS} = 5.5V$ $V_{BATT} = V_{CC} =$                                        |                                                                                        |      |     | 3                | mA    |  |

| VBATT Quiescent Current, Shutdown                       | SUS = GND                                                                     |                                                                                        |      |     | 20               | μΑ    |  |

| V <sub>CC</sub> Output Voltage, Normal Operation        | V <sub>SUS</sub> = 5.5V, 6V < V <sub>BA</sub><br>0 < I <sub>LOAD</sub> < 20mA | V <sub>SUS</sub> = 5.5V, 6V < V <sub>BATT</sub> < 28V,<br>0 < I <sub>LOAD</sub> < 20mA |      |     |                  | V     |  |

| V <sub>CC</sub> Output Voltage, Shutdown                | SUS = GND, no load                                                            |                                                                                        | 3.5  |     | 5.5              | V     |  |

| V Hadaw salta sa Laguar t Taraghald                     | V <sub>CC</sub> rising (leaving loc                                           | kout)                                                                                  |      |     | 4.5              | V     |  |

| VCC Undervoltage-Lockout Threshold                      | V <sub>CC</sub> falling (entering lo                                          | ckout)                                                                                 | 4.0  |     |                  | V     |  |

| V <sub>CC</sub> Power-On Reset (POR) Threshold          | Rising edge                                                                   |                                                                                        | 0.90 |     | 2.70             | V     |  |

| REF Output Voltage, Normal Operation                    | 4.5V < V <sub>C</sub> C < 5.5V, I <sub>L</sub> C                              | AD = 40μA                                                                              | 1.95 |     | 2.05             | V     |  |

| GH1, GH2, GL1, GL2 On-Resistance                        | I <sub>TEST</sub> = 100mA, V <sub>CC</sub> =                                  | V <sub>DD</sub> = 5.3V                                                                 |      |     | 18               | Ω     |  |

| BST1, BST2 Leakage Current                              | V <sub>BST</sub> _ = 12V, V <sub>L</sub> X_ = 7                               | V                                                                                      |      |     | 5                | μΑ    |  |

| Input Resonant Frequency                                | Guaranteed by design                                                          |                                                                                        | 25   |     | 300              | kHz   |  |

| Minimum Off-Time                                        |                                                                               |                                                                                        | 180  |     | 380              | ns    |  |

| Maximum Off-Time                                        |                                                                               |                                                                                        | 18   |     | 38               | μs    |  |

| Current-Limit Threshold<br>LX1 - GND, LX2 - GND (Fixed) | ILIM = VCC                                                                    |                                                                                        | 180  |     | 220              | mV    |  |

| Current-Limit Threshold                                 | V <sub>ILIM</sub> = 0.5V                                                      |                                                                                        | 80   |     | 120              | .,    |  |

| LX1 - GND, LX2 - GND (Adjustable)                       | V <sub>ILIM</sub> = 2.0V                                                      |                                                                                        | 370  |     | 430              | mV    |  |

| Current-Limit Leading-Edge Blanking                     |                                                                               |                                                                                        | 250  |     | 450              | ns    |  |

| LOT Input Voltage Range                                 |                                                                               |                                                                                        | 0.5  |     | V <sub>REF</sub> | V     |  |

| LOT Input Bias Current                                  |                                                                               |                                                                                        | -2   |     | +2               | μΑ    |  |

| IFB Input Voltage Range                                 |                                                                               |                                                                                        | -1.7 |     | +1.7             | V     |  |

| IFB Regulation Point                                    |                                                                               |                                                                                        | 380  |     | 420              | mV    |  |

| IFB Input Bias Current                                  | V <sub>IFB</sub> = 0.4V                                                       |                                                                                        | -2   |     | +2               | μΑ    |  |

| IFB Lamp-Out Threshold                                  | LOT = REF                                                                     |                                                                                        | 500  |     | 700              | mV    |  |

| ISEC Input Voltage Range                                |                                                                               |                                                                                        | -2   |     | +2               | V     |  |

| ISEC Regulation Point                                   |                                                                               |                                                                                        | 1.20 |     | 1.30             | V     |  |

| ISEC Input Bias Current                                 | V <sub>ISEC</sub> = 1.25V                                                     |                                                                                        | -2   |     | +2               | μΑ    |  |

| VFB Input Voltage Range                                 |                                                                               |                                                                                        | -2   |     | +2               | V     |  |

| VFB Input Bias Current                                  | $V_{VFB} = 0.5V$                                                              |                                                                                        | -0.5 |     | +0.5             | μΑ    |  |

| VFB Regulation Point                                    |                                                                               |                                                                                        | 490  |     | 530              | mV    |  |

| VFB Zero-Voltage Crossing Threshold                     |                                                                               |                                                                                        | -10  |     | +10              | mV    |  |

|                                                         | MAX8709                                                                       |                                                                                        | 200  |     | 220              | Hz    |  |

| Digital PWM Chopping Frequency                          | MAX8709A                                                                      |                                                                                        | 204  |     | 216              |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1. VBATT = 12V, VLOT = VREF, VCC = VDD, VSUS = 5.3V, **T<sub>A</sub> = -40°C to +85°C**. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                          | CONDITIONS                       | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------------------------------|----------------------------------|------|-----|------|-------|

| Lamp-Out Detection Timeout Timer                                   | V <sub>IFB</sub> < 0.1V (Note 1) | 1.14 |     | 1.30 | S     |

| SDA, SCL, SUS Input Low Voltage                                    |                                  |      |     | 8.0  | V     |

| SDA, SCL, SUS Input High Voltage                                   |                                  | 2.1  |     |      | V     |

| SDA, SCL, SUS Input Bias Current                                   |                                  | -1   |     | +1   | μΑ    |

| SDA Output Low Sink Current                                        | $V_{SDA} = 0.4V$                 | 4    |     |      | mA    |

| SCL Serial Clock High Period                                       | THIGH                            | 4    |     |      | μs    |

| SCL Serial Clock Low Period                                        | T <sub>LOW</sub>                 | 4.7  |     |      | μs    |

| Start-Condition Setup Time                                         | tsu:sta                          | 4.7  |     |      | μs    |

| Start-Condition Hold Time                                          | thd:sta                          | 4    |     |      | μs    |

| SDA Valid to SCL Rising-Edge Setup Time,<br>Slave Clocking-In Data | tsu:DAT                          | 250  |     |      | ns    |

| SCL Falling Edge to SDA Transition                                 | thd:dat                          | 0    |     |      | ns    |

Note 1: Corresponds to 256 DPWM cycles.

Note 2: Specifications to -40°C are guaranteed by design based on final characterization results.

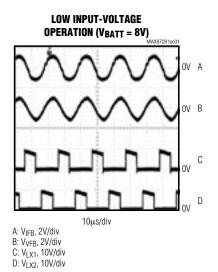

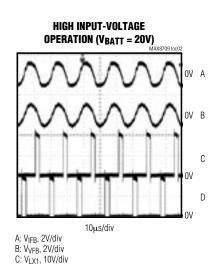

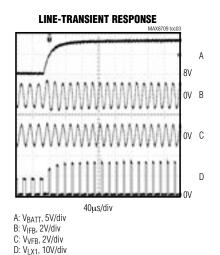

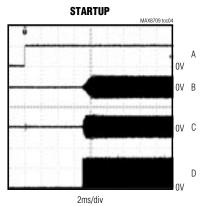

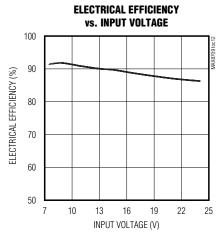

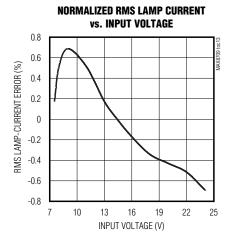

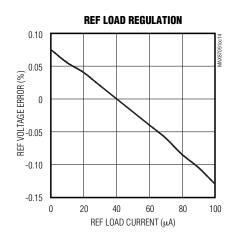

### Typical Operating Characteristics

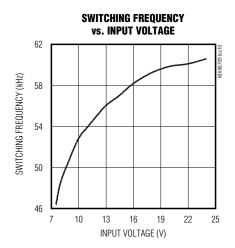

(Circuit of Figure 1. VBATT = 12V, VLOT = VREF, VCC = VDD, VSUS = 5.3V, TA = +25°C, unless otherwise noted.)

D: V<sub>LX2</sub>, 10V/div

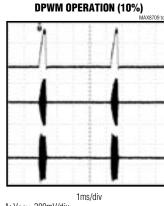

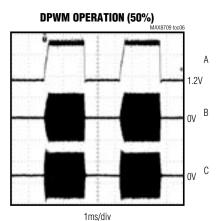

### Typical Operating Characteristics (continued)

1.2V

ov B

OV C

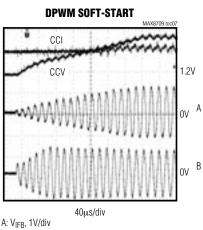

(Circuit of Figure 1. VBATT = 12V, VLOT = VREF, VCC = VDD, VSUS = 5.3V, TA = +25°C, unless otherwise noted.)

A: V<sub>CCV</sub>, 200mV/div B: V<sub>IFB</sub>, 1V/div C: V<sub>VFB</sub>, 1V/div

A: V<sub>CCV</sub>, 200mV/div B: V<sub>IFB</sub>, 1V/div C: V<sub>VFB</sub>, 1V/div

A: V<sub>IFB</sub>, 1V/div B: V<sub>VFB</sub>, 1V/div

A: V<sub>IFB</sub>, 1V/div B: V<sub>VFB</sub>, 1V/div

A: V<sub>VFB</sub>, 1V/div B: V<sub>IFB</sub>, 1V/div

### Typical Operating Characteristics (continued)

(Circuit of Figure 1. VBATT = 12V, VLOT = VREF, VCC = VDD, VSUS = 5.3V, TA = +25°C, unless otherwise noted.)

## Pin Description

| DIN           | NAME     | FINATION FINATION                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| PIN           | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| 1             | ILIM     | Current-Limit Threshold Adjustment. Connect a resistive voltage-divider between REF or V <sub>CC</sub> and GND. The current-limit threshold measured between LX_ and GND is 1/5th the voltage forced at ILIM. The ILIM adjustment range is 0 to 3V. Connect ILIM to V <sub>CC</sub> to select the default current-limit threshold of 0.2V.                                 |  |  |  |  |  |  |  |  |  |  |

| 2             | REF      | 2V Reference Output. Bypass REF to GND with a 0.1μF ceramic capacitor. REF is discharged to GND during shutdown.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

| 3             | LOT      | Lamp-Out Threshold Adjustment. The lamp-out threshold is 30% of the voltage at LOT. The LOT adjustment range is from 0.5V to V <sub>REF</sub> .                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |

| 4             | GND      | Analog Ground. The ground return for V <sub>CC</sub> , REF, and other analog circuitry. Connect GND to PGND under the IC at the IC's backside exposed metal pad.                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |  |

| 5             | ISEC     | Secondary Current-Limit Sense Input. The secondary current limit controls the transformer secondary current even if the IFB sense resistor is shorted. See the Secondary Current Limit (ISEC) section.                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| 6             | SDA      | SMBus Serial Data Input                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| 7             | SCL      | SMBus Serial Clock Input                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| 8             | SUS      | SMBus Suspend Input                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |

| 9, 10, 11, 23 | N.C.     | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| 12            | $V_{DD}$ | Gate-Driver Supply Input. Connect $V_{DD}$ to $V_{CC}$ , the output of the linear regulator. Bypass $V_{DD}$ with a 0.1 $\mu$ F capacitor to PGND.                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| 13            | PGND     | Power Ground. Gate-driver current flows through this pin.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |

| 14            | GL2      | Low-Side MOSFET NL2 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| 15            | GL1      | Low-Side MOSFET NL1 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| 16            | GH1      | High-Side MOSFET NH1 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| 17            | LX1      | Switching Node Connection. LX1 is the internal gate driver's (GH1's) source connection for the high-side MOSFET NH1. LX1 is also the sense input to the current comparators.                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| 18            | BST1     | Driver Bootstrap Input for High-Side MOSFET NH1. Connect BST1 through a diode to V <sub>DD</sub> and through a 0.1µF capacitor to LX1 (Figure 1).                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| 19            | BST2     | Driver Bootstrap Input for High-Side MOSFET NH2. Connect BST2 through a diode to V <sub>DD</sub> and through a 0.1µF capacitor to LX2 (Figure 1).                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| 20            | LX2      | Switching Node Connection. LX2 is the internal gate driver's (GH2's) source connection for the high-side MOSFET NH2. LX2 is also the sense input to the current comparators.                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |

| 21            | GH2      | High-Side MOSFET NH2 Gate-Driver Output                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| 22            | VFB      | Lamp Output Feedback Sense Input. The average value on VFB is regulated during startup and open-<br>lamp conditions to 0.5V by controlling the on-time of high-side switches. A capacitive voltage-divider<br>between the CCFL lamp output and GND is sensed to set the maximum average lamp output voltage.                                                               |  |  |  |  |  |  |  |  |  |  |

| 24            | IFB      | Lamp Current-Sense Input. The voltage on IFB is used to regulate the lamp current. If the IFB input falls below 30% of the LOT voltage for 1.22s, then the MAX8709/MAX8709A activate the lamp-out fault latch.                                                                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| 25            | CCI      | Current-Loop Compensation Pin. CCI is the output of the current-loop transconductance amplifier (GMI) that regulates the CCFL current. The CCI voltage controls the time interval during which the full bridge applies the input voltage (BATT) to the transformer primary. Connect CCI to GND through a 0.1µF capacitor. CCI is internally discharged to GND in shutdown. |  |  |  |  |  |  |  |  |  |  |

## Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26  | CCV  | Voltage-Loop Compensation Pin. CCV is the output of the voltage-loop transconductance amplifier (GMV) that regulates the maximum average secondary transformer voltage. The CCV voltage controls the time interval during which the full bridge applies the input voltage (BATT) to the transformer primary. The CCV capacitor also sets the rise time and fall time of the lamp current in DPWM. Connect CCV to GND with a 6.8nF capacitor. CCV is internally discharged to GND in shutdown. |

| 27  | BATT | MAX8709/MAX8709A Supply Input. Input to the internal 5.3V linear regulator (V <sub>CC</sub> ) that provides power to the device. Bypass BATT to GND with a 0.1μF capacitor.                                                                                                                                                                                                                                                                                                                   |

| 28  | Vcc  | 5.3V Linear-Regulator Output. $V_{CC}$ is the supply voltage for the MAX8709/MAX8709A. Bypass $V_{CC}$ to GND with a 0.47 $\mu$ F ceramic capacitor. $V_{CC}$ can also be connected to BATT if $V_{BATT}$ < 5.5V.                                                                                                                                                                                                                                                                             |

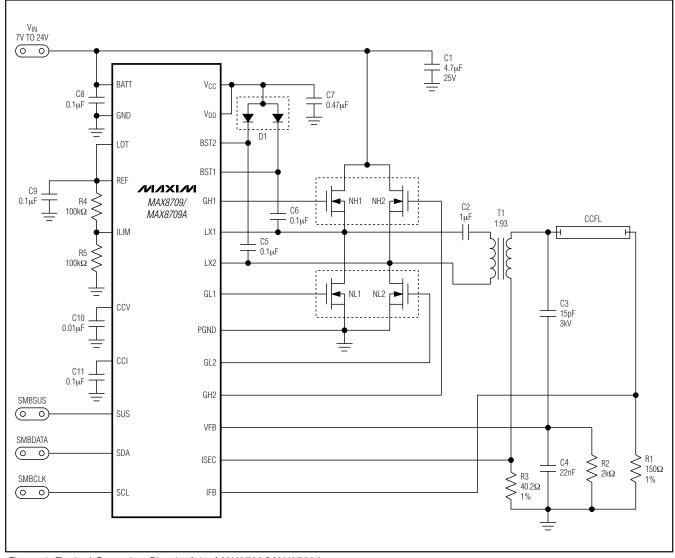

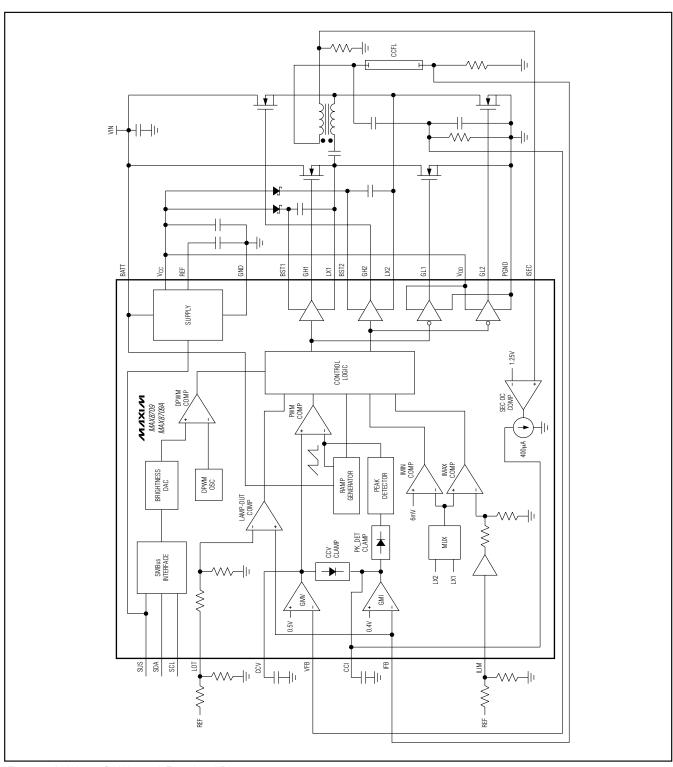

Figure 1. Typical Operating Circuit of the MAX8709/MAX8709A

Figure 2. MAX8709/MAX8709A Functional Diagram

01 \_\_\_\_\_\_ **// | X | // |**

**Table 1. Component List**

| DESIGNATION    | DESCRIPTION                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| C1             | 4.7µF ±20%, 25V X5R<br>ceramic capacitor (1210)<br>Murata GRM32RR61E475K<br>Taiyo Yuden TMK325BJ475MN<br>TDK C3225X7R1E475M |

| C2             | 1µF ±10%, 25V X7R ceramic capacitor (1206) Murata GRM31MR71E105K Taiyo Yuden TMK316BJ105KL TDK C3216X7R1E105K               |

| C3             | 15pF ±1pF, 3kVhigh-voltage<br>ceramic capacitor (1808)<br>Murata GRM42D1X3F150J<br>TDK C4520C0G3F150F                       |

| C4             | 0.022µF ±10%, 16V X7R ceramic capacitor (0402) Murata GRP155R71C223K Taiyo Yuden EMK105BJ223KV TDK C1005X7R1C223K           |

| C5, C6, C8, C9 | 0.1µF ±10%, 25V X7R ceramic capacitors (0603) Murata GRM188R71E104K Taiyo Yuden TMK107BJ104KA TDK C1608X7R1E104K            |

### **Table 2. Component Suppliers**

| SUPPLIER                | WEBSITE                |

|-------------------------|------------------------|

| Central Semiconductor   | www.centralsemi.com    |

| Fairchild Semiconductor | www.fairchildsemi.com  |

| Murata                  | www.murata.com         |

| Sumida                  | www.sumida.com         |

| Taiyo Yuden             | www.t-yuden.com        |

| TDK                     | www.components.tdk.com |

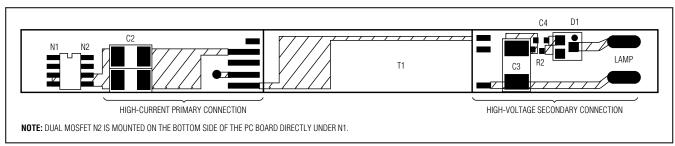

### Typical Operating Circuit

The Typical Operating Circuit of the MAX8709/MAX8709A (Figure 1) is a complete CCFL backlight inverter for notebook TFT LCD panels. The circuit works over an input voltage range of 7V to 24V with an RMS lamp current of 6mA. The circuit's maximum RMS open-lamp voltage is limited to 1600V. Table 1 lists recommended component options, and Table 2 lists the component suppliers' contact information.

| DESIGNATION  | DESCRIPTION                                                                                                             |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| C7           | 0.47µF ±10%, 10V X5R ceramic capacitor (0603) Taiyo Yuden LMK107BJ474KA TDK C1608X5R1A474K                              |  |  |  |  |  |

| D1           | Dual silicon switching diode,<br>common anode (SOT-323)<br>Central Semiconductor CMSD2836<br>Diodes Incorporated BAW56W |  |  |  |  |  |

| NH1/2, NL1/2 | 30V, 0.095 dual N-channel MOSFETs<br>(6-pin SOT23)<br>Fairchild FDC6561AN                                               |  |  |  |  |  |

| R1           | 150Ω ±1% resistor (0603)                                                                                                |  |  |  |  |  |

| R2           | 2kΩ ±5% resistor (0603)                                                                                                 |  |  |  |  |  |

| R3           | 39Ω ±1% (resistor (0603)                                                                                                |  |  |  |  |  |

| R4, R5       | 100kΩ ±5% resistors (0603)                                                                                              |  |  |  |  |  |

| T1           | CCFL transformer, 1:93 turns ratio<br>Sumida 5371-400-W1423<br>TOKO T912MG-1018                                         |  |  |  |  |  |

### **Detailed Description**

The MAX8709/MAX8709A control a full-bridge resonant inverter to convert an unregulated DC input into a near-sinusoidal AC output for powering CCFLs. The lamp brightness is adjusted by turning the lamp on and off with an internal DPWM signal. The duty cycle of the DPWM signal is set through an SMBus-compatible 2-wire serial interface. Figure 2 shows the functional diagram of the MAX8709/MAX8709A.

#### **Resonant Operation**

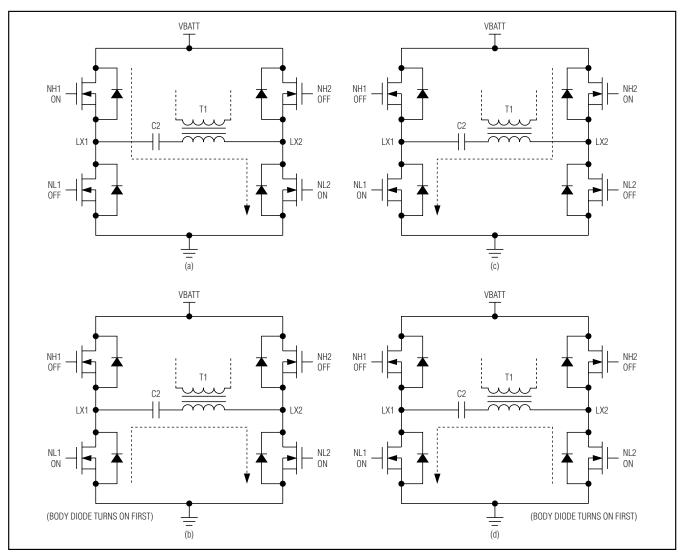

The MAX8709/MAX8709A drive the four N-channel power MOSFETs that make up the zero-voltage-switching (ZVS) full-bridge inverter as shown in Figure 3. Assume that NH1 and NL2 are turned on at the beginning of a switching cycle as shown in Figure 3(a). The primary current flows through MOSFET NH1, DC blocking cap C2, the primary side of transformer T1, and MOSFET NL2. During this interval, the primary current ramps up until the controller turns off NH1. When NH1 turns off, the primary current forward biases the body diode of NL1, which clamps the LX1 voltage just below ground as shown in Figure 3(b). When the controller turns on NL1, its drain-to-source voltage is near zero because its forward-biased body diode clamps the drain. Since NL2 is still on, the primary current flows through NL1, C2, the primary side of T1, and NL2. Once the primary current drops to the minimum current threshold (6mV / RDS(ON)), the controller turns off NL2. The remaining energy in T1 charges up the LX2

Figure 3. Resonant Operation

node until the body diode of NH2 is forward biased.

When NH2 turns on, it does so with near-zero drain-to-source voltage. The primary current reverses polarity as shown in Figure 3(c), beginning a new cycle with the current flowing in the opposite direction, with NH2 and NL1 on. The primary current ramps up until the controller turns off NH2. When NH2 turns off, the primary current forward biases the body diode of NL2, which clamps the LX2 voltage just below ground as shown in Figure 3(d). After the LX2 node goes low, the controller losslessly turns on NL2. Once the primary current drops to the minimum current threshold, the controller turns off NL1. The remaining energy charges up the LX1 node until the body diode of

NH1 is forward biased. Finally, NH1 losslessly turns on, beginning a new cycle as shown in Figure 3(a). Note that switching transitions on all four power MOSFETs occur under ZVS conditions, which reduce transient power losses and EMI.

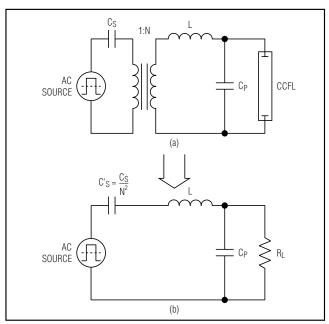

The simplified CCFL inverter circuit is shown in Figure 4(a). The full-bridge power stage is simplified and represented as a square-wave AC source. The resonant tank circuit can be further simplified to Figure 4(b) by removing the transformer. Cs is the primary series capacitor, C's is the series capacitance reflected to the secondary, Cp is the secondary parallel capacitor, N is the transformer turns ratio, L is the transformer sec-

Figure 4. Equivalent Resonant Tank Circuit

ondary leakage inductance, and  $R_L$  is an idealized resistance that models the CCFL in normal operation.

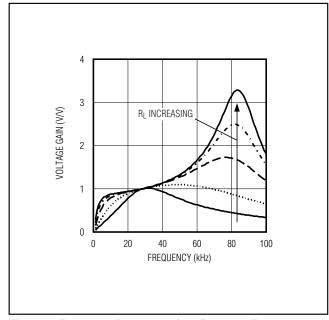

Figure 5 shows the frequency response of the resonant tank's voltage gain under different load conditions. The primary series capacitor is  $1\mu F$ , the secondary parallel capacitor is 15pF, the transformer turns ratio is 1:93, and the secondary leakage inductance is 260mH. Notice there are two peaks, fs and fp, in the frequency response. The first peak, fs, is the series resonant peak determined by the reflected series capacitor and the secondary leakage inductance:

$$f_{S} = \frac{1}{2\pi\sqrt{LC'_{S}}}$$

The second peak, fp, is the parallel resonant peak determined by the reflected series capacitor, the parallel capacitor, and the secondary leakage inductance:

$$f_{P} = \frac{1}{2\pi \sqrt{L \frac{C'_{S}C_{P}}{C'_{S} + C_{P}}}}$$

These two frequencies set the lower and upper boundaries of resonant operation. When the lamp is off, the operating point of the resonant tank is close to the parallel resonant peak due to the infinite lamp impedance. The circuit displays the characteristics of a parallel-loaded resonant converter, acting like a voltage source to generate the necessary striking voltage. Theoretically,

Figure 5. Frequency Response of the Resonant Tank

the output voltage of the resonant converter keeps going until the lamp is ionized.

Once the lamp is ionized, the equivalent load resistance decreases rapidly and the operating point moves toward the series resonant peak. The series resonant operation causes the circuit to behave like a current source.

#### Current and Voltage Control Loops (CCI, CCV)

The MAX8709/MAX8709A use a current loop and a voltage loop to control the power delivered to the CCFL. The current loop is the dominant loop in regulating the lamp current. The voltage loop limits the transformer secondary voltage and is active during startup, the DPWM off-time, and open-lamp fault.

Both the current and the voltage loops use transconductance error amplifiers for regulation. The AC lamp current is measured with a sense resistor in series with the CCFL. The voltage across this resistor is applied to the IFB input and is internally half-wave rectified. The current-loop transconductance error amplifier compares the rectified IFB voltage with a 400mV internal threshold to create an error current. The error current charges and discharges a capacitor connected between CCI and ground to generate an error voltage VCCI. Similarly, the AC voltage across the transformer secondary winding is measured through a capacitive voltage-divider. The sense voltage is applied to the VFB input and is internally half-wave rectified. The volt-

age-loop transconductance error amplifier compares the rectified VFB voltage with a 500mV internal threshold to create an error current. The error current charges and discharges a capacitor connected between CCV and ground to generate an error voltage VCCV. The lower of VCCI and VCCV takes control and is compared with an internal ramp signal to set the high-side MOSFET switch on-time (ton).

#### Lamp Startup

A CCFL is a gas discharge lamp that is normally driven in the avalanche mode. To start ionization in a nonionized lamp, the applied voltage (striking voltage) must be increased to the level required for the start of avalanche. The striking voltage can be several times the typical operating voltage.

Because of the resonant topology, the striking voltage is guaranteed regardless of the temperature. Before the lamp is ionized, the lamp impedance is infinite. The transformer secondary leakage inductance and the high-voltage parallel capacitor determine the unloaded resonant frequency. Since the unloaded resonant circuit has a high Q, it is easy to generate high voltages across the lamp.

Operation during startup differs from the steady-state condition described in the *Current and Voltage Control Loops* section. Upon power-up, V<sub>CCI</sub> slowly rises, increasing the duty cycle, which provides soft-start. During this time, V<sub>CCV</sub> is limited to 150mV above V<sub>CCI</sub>. Once the secondary voltage reaches the strike voltage, the lamp current begins to increase. When the lamp current reaches the regulation point, V<sub>CCI</sub> exceeds V<sub>CCV</sub> and it reaches steady state.

#### Feed-Forward Control and Dropout Operation

The MAX8709/MAX8709A are designed to maintain tight control of the transformer secondary under all transient conditions including dropout. The feed-forward control instantaneously adjusts the ton time for changes in input voltage (VBATT). This feature provides immunity to input voltage variations and simplifies loop compensation over wide input voltage ranges. The feed-forward control also improves the line regulation for short DPWM on-times and makes startup transients less dependent on the input voltage.

Feed-forward control is implemented by increasing the PWM's internal voltage ramp rate for higher VBATT. This has the effect of varying ton as a function of the input voltage while maintaining about the same signal levels at VCCI and VCCV. Since the required voltage change across the compensation capacitors is minimal, the

controller's response to input voltage changes is essentially instantaneous.

To maximize run time, it may be desirable to allow the circuit to operate in dropout if the backlight's performance is not critical. When  $V_{BATT}$  is very low, the controller loses current regulation and runs at maximum duty cycle. Under these circumstances, a transient overvoltage condition could occur when the AC adapter is suddenly applied to power the circuit. The feed-forward circuitry minimizes variations in lamp voltage due to such input voltage steps. The regulator also clamps the voltage on  $V_{CCI}$ . These two features together ensure that overvoltage transients do not appear on the transformer when leaving dropout.

The V<sub>CCI</sub> clamp is unique in that it limits V<sub>CCI</sub> to the peak voltage of the PWM ramp. As the circuit reaches dropout, V<sub>CCI</sub> approaches the PWM ramp's peak in order to reach maximum t<sub>ON</sub>. If V<sub>BATT</sub> decreases further, the control loop loses regulation and V<sub>CCI</sub> tries to reach its positive supply rail. The clamp on V<sub>CCI</sub> prevents this from happening and V<sub>CCI</sub> rides just above the PWM ramp's peak. If V<sub>BATT</sub> continues to decrease, the feed-forward control reduces the amplitude of the PWM ramp and the clamp pulls V<sub>CCI</sub> down. When V<sub>BATT</sub> suddenly steps out of dropout, V<sub>CCI</sub> is still low and maintains the drive on the transformer at the old dropout level. The control loop then slowly corrects and increases V<sub>CCI</sub> to bring the circuit back into regulation.

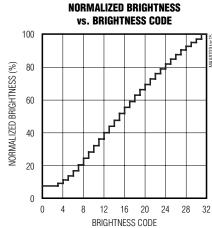

#### **DPWM Dimming Control**

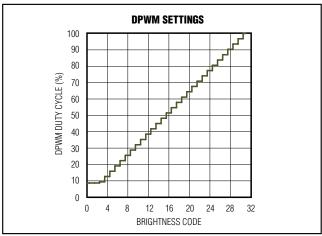

The MAX8709/MAX8709A control the brightness of the CCFL by "chopping" the lamp current on and off using an internal DPWM signal. The frequency of the DPWM signal is 210Hz. The brightness code set through the SMBus interface determines the duty cycle of the DPWM signal. A brightness code of 0b00000 corresponds to a 9.375% DPWM duty cycle for MAX8709, and a 12.5% duty cycle for MAX8709A. A brightness code of 0b11111 corresponds to a 100% DPWM duty cycle. The duty cycle changes by 3.125% per step, but codes 0b00000 to 0b00010 all produce 9.375% for MAX8709 as shown in Figure 6. Codes 0b000000 to 0b00011 all produce 12.5% for MAX8709A.

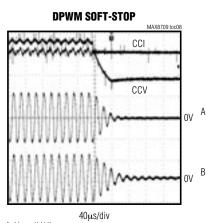

In DPWM operation, the CCI and CCV control loops work together to regulate the lamp current, limit the secondary voltage, and control the rising and falling of the lamp current. During the DPWM off-cycle, the output of the voltage-loop error amplifier (CCV) is set to 1.15V and the current-loop error-amplifier output (CCI) is high impedance. The high-impedance output acts like a sample-and-hold circuit to keep VCCI from changing during the off-cycles. At the beginning of the DPWM on-cycle, VCCV

Figure 6. DPWM Settings

linearly rises, gradually increasing  $t_{ON}$ , which provides soft-start. Once  $V_{CCV}$  exceeds  $V_{CCI}$ , the current-loop error amplifier takes control and starts to regulate the lamp current. In the meantime,  $V_{CCV}$  continues to rise and is limited to 150mV above  $V_{CCI}$ . At the end of the DPWM on-cycle, the CCV capacitor discharges linearly, gradually decreasing  $t_{ON}$  and providing soft-stop.

#### **POR and UVLO**

The MAX8709/MAX8709A include power-on-reset (POR) and undervoltage-lockout (UVLO) circuits. The POR resets all internal registers such as DAC outputs, fault latches, and all SMBus registers. POR occurs when VCC is below 1.5V. The SMBus input logic thresholds are only guaranteed to meet electrical characteristic limits for VCC as low as 3.5V, but the interface continues to function down to the POR threshold.

The UVLO is activated and disables both high-side and low-side switch drivers when V<sub>CC</sub> is below 4.2V (typ).

#### **Low-Power Shutdown (SUS)**

When the MAX8709/MAX8709A are placed in shutdown, all functions of the IC are turned off except for the 5.3V linear regulator that powers all internal registers and the SMBus interface. The SMBus interface is accessible in shutdown. In shutdown, the linear-regulator output voltage drops to about 4.5V and the supply current is 6 $\mu$ A (typ), which is the required power to maintain all internal register states. While in shutdown, lamp-out detection and short-circuit detection latches are reset. The device can be placed into shutdown either by writing to the shutdown-mode register or pulling SUS low.

#### **Lamp-Out Protection**

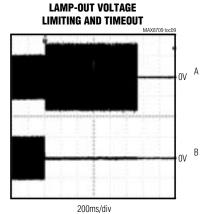

For safety, the MAX8709/MAX8709A monitor the lamp-current feedback (IFB) to detect faulty or open CCFL tubes and secondary short circuits in the lamp and IFB sense resistor. If the voltage on IFB is continuously below 30% of the LOT voltage for greater than 1.22s (typ), the MAX8709/MAX8709A latch off the full bridge. Unlike the normal shutdown mode, the linear-regulator output (VCC) remains at 5.3V. Toggling SUS or cycling the input power reactivates the device.

During the 1.22s delay, V<sub>CCI</sub> slowly rises, increasing t<sub>ON</sub> in an attempt to maintain lamp current regulation. As V<sub>CCI</sub> rises, V<sub>CCV</sub> rises with it until the secondary voltage reaches its preset limit. At this point, V<sub>CCV</sub> stops and limits the secondary voltage by limiting t<sub>ON</sub>. Because V<sub>CCV</sub> is limited to 150mV above V<sub>CCI</sub>, the voltage control loop is able to quickly limit the secondary voltage. Without this clamping feature, the transformer voltage overshoots to dangerous levels because V<sub>CCV</sub> takes time to slew down from its supply rail.

#### **Primary Overcurrent Protection (ILIM)**

The MAX8709/MAX8709A sense primary current in each switching cycle. When the regulator turns on the low-side MOSFET, a comparator monitors the voltage drop from LX\_ to GND. If the voltage exceeds the current-limit threshold, the regulator turns off the high-side switch at the opposite side of the primary to prevent the transformer primary current from increasing further.

The current-limit threshold can be adjusted using the ILIM input. Connect a resistive voltage-divider between REF or  $V_{CC}$  and GND with the midpoint connected to ILIM. The current-limit threshold measured between LX\_ and GND is 1/5th the voltage at ILIM. The ILIM adjustment range is 0 to 3V. Connect ILIM to  $V_{CC}$  to select the default current-limit threshold of 0.2V.

#### Secondary Current Limit (ISEC)

The secondary current limit provides failsafe current limiting in case a failure, such as a short circuit or leakage from the lamp high-voltage terminal to ground, prevents the CCI current control loop from functioning properly. ISEC monitors the voltage across a sense resistor placed between the transformer's low-voltage secondary terminal and ground. The ISEC voltage is internally half-wave rectified and continuously compared to the ISEC regulation threshold (1.25V typ). Any time the ISEC voltage exceeds the threshold, a controlled current is drawn from CCI to reduce the on-time of the bridge's high-side switches.

#### Reference Output (REF)

The reference output is nominally 2V, and can source at least 40µA (see the *Typical Operating Characteristics*).

| Writ            | te-Byte Fo           | rmat | t     |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                           |                             |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |        |     |                                                                        |                                                                                          |                                    |              |   |

|-----------------|----------------------|------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------|-----------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|-----|------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------|--------------|---|

|                 | S .                  | ADD  | RESS  |              | WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AC                                      | K                         | СО                          | MMAN   | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ACK            | (      |     | ATA                                                                    | s 1b  ata goes into the remmand byte  DATA 8 bits  a Byte: reads fro register set by the | ACK                                |              | Р |