FAIRCHILD

SEMICONDUCTOR

# DM74AS240 • DM74AS244 **3-STATE Bus Driver/Receiver**

# **General Description**

This family of Advance Schottky 3-STATE Bus circuits are designed to provide either bidirectional or unidirectional buffer interface in Memory, Microprocessor, and Communication Systems. The output characteristics of the circuits have low impedance sufficient to drive terminated transmission lines down to  $133\Omega$ . The input characteristics of the circuits likewise have a high impedance so it will not significantly load the transmission line. The package contains eight 3-STATE buffers organized with four buffers having a common 3-STATE enable gate. The DM74AS240 and DM74AS244 are eight wide in a 20 pin package, and may be used as a 4 wide bidirectional or eight wide unidirectional. The buffer selection includes inverting and noninverting, with enable or disable 3-STATE control.

### **Features**

■ Advanced oxide-isolated, ion-implanted Schottky TTL process

October 1986

Revised March 2000

- Improved switching performance with less power dissipation compared with Schottky counterpart

- Functional and pin compatible with 74LS and Schottky counterpart

- $\blacksquare$  Switching response specified into 500 $\Omega$  and 50 pF

- Specified to interface with CMOS at  $V_{OH} = V_{CC} 2V$

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                       |

|--------------|----------------|---------------------------------------------------------------------------|

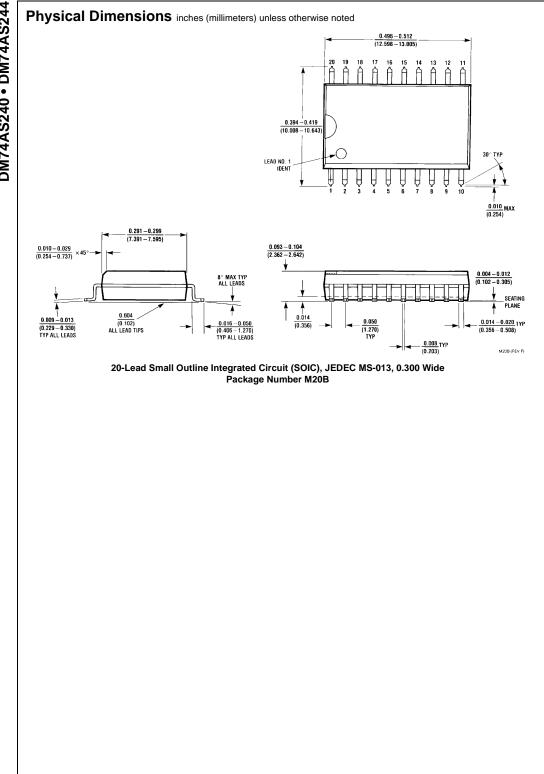

| DM74AS240WM  | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

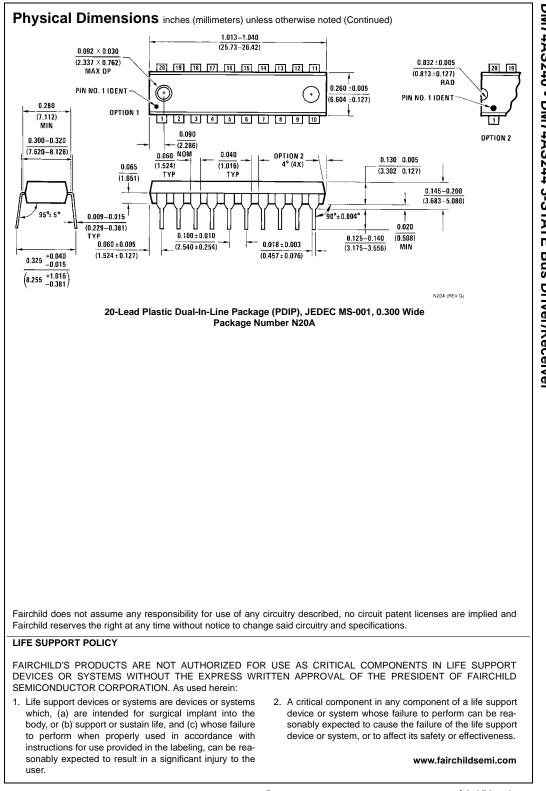

| DM74AS240N   | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |

| DM74AS244WM  | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| DM74AS244N   | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

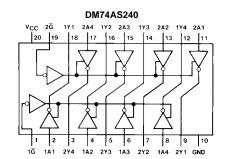

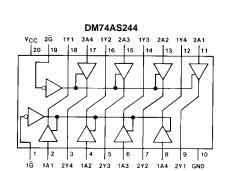

## **Connection Diagrams**

# **Function Tables**

DM74AS240 DM74AS244 Inputs Output Output Inputs G Α Υ G Α Y н Ι Ι Τ Τ Ι н L L н Н L 7 н х 7 н х L = LOW Logic Level H = HIGH Logic Level X = Either LOW or HIGH Logic Level Z = High Impedance

© 2000 Fairchild Semiconductor Corporation DS006298

# Absolute Maximum Ratings(Note 1)

| Supply Voltage, V <sub>CC</sub>      | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Voltage Applied to Disabled Output   | 5.5V                              |

| Operating Free Air Temperature Range | 0°C to +70°C                      |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Typical θ <sub>JA</sub>              |                                   |

| N Package                            | 57.0°C/W                          |

| M Package                            | 76.0°C/W                          |

|                                      |                                   |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min | Nom | Max | Units |

|-----------------|--------------------------------|-----|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.5 | 5   | 5.5 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2   |     |     | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |     |     | 0.8 | V     |

| I <sub>OH</sub> | HIGH Level Output Current      |     |     | -15 | mA    |

| I <sub>OL</sub> | LOW Level Output Current       |     |     | 64  | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0   |     | 70  | °C    |

# **Electrical Characteristics**

over recommended operating free air temperature range. All typical values are measured at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

| Symbol                  | Parameter                          | Conditions                                                                                            |                        | Min               | Тур  | Max  | Units |    |

|-------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------|-------------------|------|------|-------|----|

| V <sub>IK</sub>         | Input Clamp Voltage                | $V_{CC} = 4.5V, I_{IN} = -18 \text{ mA}$                                                              |                        |                   |      |      | -1.2  | V  |

| V <sub>OH</sub>         | HIGH Level                         | $V_{CC} = 4.5V, I_{OH}$                                                                               | = -3 mA                |                   | 2.4  | 3.2  |       |    |

|                         | Output Voltage                     | $V_{CC} = 4.5V, I_{OH}$                                                                               | = Max                  |                   | 2.4  |      |       | V  |

|                         |                                    | $I_{OH} = -2$ mA, $V_{CC} = 4.5V$ to 5.5V                                                             |                        |                   |      |      |       | 1  |

| V <sub>OL</sub>         | LOW Level Output Voltage           | $V_{CC} = 4.5V, I_{OL} = Max$                                                                         |                        |                   | 0.35 | 0.55 | V     |    |

| l <sub>l</sub>          | Input Current at Max Input Voltage | $V_{CC} = 5.5V$                                                                                       | $V_{IN} = 7V$          | Others            |      |      | 100   | μA |

| I <sub>IH</sub>         | HIGH Level Input Current           | $V_{CC} = 5.5V, V_{IN} = 2.7V$ Others                                                                 |                        |                   |      | 20   | μA    |    |

| I <sub>IL</sub>         | LOW Level Input Current            | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 0.4V<br>(Control Inputs),<br>DM74AS244 (G)<br>DM74AS244 (A) |                        |                   |      |      |       |    |

|                         |                                    |                                                                                                       |                        | (Control Inputs), |      |      | -500  | μΑ |

|                         |                                    |                                                                                                       |                        | DM74AS244 (G)     |      |      |       |    |

|                         |                                    |                                                                                                       |                        | DM74AS244 (A)     |      |      | -1000 |    |

| I <sub>OZH</sub>        | HIGH Level 3-STATE Output Current  | V <sub>CC</sub> = 5.5V, V= 2.7V                                                                       |                        |                   |      |      | 50    | μA |

| I <sub>OZL</sub>        | LOW Level 3-STATE                  |                                                                                                       | 0.414                  | DM74AS240,        |      |      | -50   | μΑ |

|                         | Output Current                     | V <sub>CC</sub> = 5.5V, V =                                                                           | 0.4V                   | DM74AS244         |      |      |       |    |

| I <sub>O</sub> (Note 2) | Output Drive Current               | $V_{CC} = 5.5 V, V_{OI}$                                                                              | <sub>DUT</sub> = 2.25V |                   | -50  | -115 | -150  | mA |

| I <sub>CC</sub>         | DM74AS240                          | $V_{CC} = 5.5V$                                                                                       | Outp                   | uts HIGH          |      | 11   | 17    |    |

|                         | Supply Current                     |                                                                                                       | Outp                   | uts LOW           |      | 51   | 75    | mA |

|                         |                                    | 3-STATE                                                                                               |                        |                   | 24   | 38   |       |    |

| I <sub>CC</sub>         | DM74AS244                          | $V_{CC} = 5.5V$                                                                                       | Outp                   | uts HIGH          |      | 22   | 34    |    |

|                         | Supply Current                     |                                                                                                       | Outp                   | uts LOW           |      | 60   | 90    | mA |

|                         |                                    | 3-STATE                                                                                               |                        | STATE             |      | 34   | 54    |    |

Note 2: The output conditions have been chosen to produce a current that closely approximates one half the true short-circuit output current, IOS.

| Symbol           | Parameter                                          | Conditions                                                  | From    | To            | Min | Max | Units |

|------------------|----------------------------------------------------|-------------------------------------------------------------|---------|---------------|-----|-----|-------|

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | $V_{CC} = 4.5V \text{ to } 5.5V$<br>$R_1 = R_2 = 500\Omega$ | (Input) | (Output)<br>Y | 2   | 6.5 | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | $C_L = 50 \text{ pF}$                                       | A       | Y             | 2   | 5.7 | ns    |

| t <sub>PZL</sub> | Output Enable to LOW Level                         |                                                             | G       | Y             | 2   | 9   | ns    |

| t <sub>PZH</sub> | Output Enable to HIGH Level                        | 1                                                           | G       | Y             | 2   | 6.4 | ns    |

| t <sub>PLZ</sub> | Output Disable from LOW Level                      | 1                                                           | G       | Y             | 2   | 9.5 | ns    |

| t <sub>PHZ</sub> | Output Disable from HIGH Level                     | 1                                                           | G       | Y             | 2   | 5   | ns    |

# 2340 DM7409344

# DM74AS244 Switching Characteristics

| Symbol           | Parameter                                          | Conditions                                         | From<br>(Input) | To<br>(Output) | Min | Max | Units |

|------------------|----------------------------------------------------|----------------------------------------------------|-----------------|----------------|-----|-----|-------|

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | $V_{CC} = 4.5V$ to 5.5V<br>$R_1 = R_2 = 500\Omega$ | A               | Y              | 2   | 6.2 | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | C <sub>L</sub> = 50 pF                             | A               | Y              | 2   | 6.2 | ns    |

| t <sub>PZL</sub> | Output Enable to LOW Level                         |                                                    | G               | Y              | 2   | 7.5 | ns    |

| t <sub>PZH</sub> | Output Enable to HIGH Level                        |                                                    | G               | Y              | 2   | 9   | ns    |

| t <sub>PLZ</sub> | Output Disable from LOW Level                      |                                                    | G               | Y              | 2   | 9   | ns    |

| t <sub>PHZ</sub> | Output Disable from HIGH Level                     |                                                    | G               | Y              | 2   | 6   | ns    |

# DM74AS240 • DM74AS244

DM74AS240 • DM74AS244 3-STATE Bus Driver/Receiver

Fairchild Semiconductor

Datasheet

datasheet

PDF

[E-

This page

Print version

Download this

e-mail this datasheet

Product Folders and

Applica

# find products Products groups Analog and Mixed Signal Discrete Interface Logic Microcontrollers Non-Volatile Memory **Optoelectronics** Markets and applications New products Product selection and parametric search **Cross-reference** search technical information buy products technical support mv Fairchild company

# Home >> Find products >>

DM74AS244 Octal 3-STATE Inverting Buffer/Line Drivers/Line Receiver

Contents General description | Features | Product status/pricing/packaging

General description

This family of Advance Schottky 3-STATE Bus circuits are designed to provide either bidirectional or unidirectional buffer interface in Memory, Microprocessor, and Communication Systems. The output characteristics of the circuits have low impedance sufficient to drive terminated transmission lines down to 1330hm. The input characteristics of the circuits likewise have a high impedance so it will not significantly load the transmission line. The package contains eight 3-STATE buffers organized with four buffers having a common 3-STATE enable gate. The DM74AS240 and DM74AS244 are eight wide in a 20 pin package, and may be used as a 4 wide bidirectional or eight wide unidirectional. The buffer selection includes inverting and non-inverting, with enable or disable 3-STATE control.

back to top

Features

# Related Links

Request samples

Dotted line How to order products

Product Change Notices

(PCNs)

Dotted line Support

Dotted line

Distributor and field sales

representatives

Dotted line

Quality and reliability

Design tools

- Advanced oxide-isolated, ion-implanted Schottky TTL process

- Improved switching performance with less power dissipation compared with Schottky counterpart

- Functional and pin compatible with 74LS and Schottky counterpart

- Switching response specified into 5000hm and 50 pF

- Specified to interface with CMOS at  $V_{OH} = V_{CC} 2V$

# back to top

Product status/pricing/packaging

| Product      | Product status  | Pricing* | Package type | Leads | Package marking              | Packing<br>method |

|--------------|-----------------|----------|--------------|-------|------------------------------|-------------------|

| DM74AS244N   | Full Production | \$1.28   | DIP          | 20    | \$Y&Z&4&T&P<br>DM74AS244N    | RAIL              |

| DM74AS244SJ  | Full Production | \$1.48   | SOP          | 20    | \$Y&Z&2&T<br>AS244SJ         | RAIL              |

| DM74AS244WM  | Full Production | \$1.28   | SOIC-Wide    | 20    | \$Y&Z&2&T<br>DM74AS<br>244WM | RAIL              |

| DM74AS244SJX | Full Production | \$1.48   | SOP          | 20    | \$Y&Z&2&T<br>AS244SJ         | TAPE REEL         |

| DM74AS244WMX | Full Production | \$1.28   | SOIC-Wide    | 20    | \$Y&Z&2&T<br>DM74AS<br>244WM | TAPE REEL         |

\* 1,000 piece Budgetary Pricing

# back to top

<u>Home</u> | <u>Find products</u> | <u>Technical information</u> | <u>Buy products</u> | <u>Support</u> | <u>Company</u> | <u>Contact us</u> | <u>Site index</u> | <u>Privacy policy</u>

© Copyright 2002 Fairchild Semiconductor