## ±14,000°/sec Digital Gyroscope Sensor

### **Data Sheet**

### **ADIS16266**

#### **FEATURES**

Yaw rate gyroscope with range scaling ±3500°/sec, ±7000°/sec, and ±14,000°/sec settings 2429 SPS sample rate Wide sensor bandwidth: 360 Hz No external configuration required to start data collection Start-up time: 170 ms Sleep mode recovery time: 2.5 ms Factory-calibrated sensitivity and bias Calibration temperature range: -40°C to +70°C SPI-compatible serial interface **Embedded temperature sensor** Programmable operation and control Automatic and manual bias correction controls Bartlett window FIR filter length, number of taps Digital input/output: data ready, alarm indicator, general-purpose Alarms for condition monitoring Sleep mode for power management **DAC output voltage** Single-command self-test Single-supply operation: 4.75 V to 5.25 V 3.3 V compatible digital lines 2000 g shock survivability Operating temperature range: -40°C to +105°C

#### **APPLICATIONS**

Platform control and stabilization Navigation **Medical instrumentation** Robotics

#### **GENERAL DESCRIPTION**

The ADIS16266 is a programmable digital gyroscope that combines industry-leading MEMS and signal processing technology in a single compact package. It provides accuracy performance that would otherwise require full motion calibration with any other MEMS gyroscope in this performance class. When power is applied, the ADIS16266 automatically starts up and begins sampling sensor data, without requiring configuration commands from a system processor. An addressable register structure and a common serial peripheral interface (SPI) provide simple access to sensor data and configuration settings. Many digital processor platforms support the SPI with simple firmware level instructions.

The ADIS16266 provides several programmable features for in-system optimization. The Bartlett window FIR filter length and sample rate settings provide users with controls that enable noise vs. bandwidth optimization. The digital input/output lines offer options for a data ready signal that helps the master processor efficiently manage data coherency, an alarm indicator signal for triggering master processor interrupts, and a general-purpose function for setting and monitoring system level digital controls/ conditions.

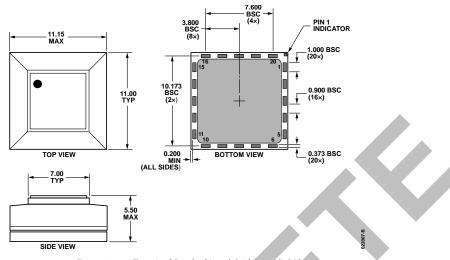

The ADIS16266 is pin-compatible with the ADIS16265 and comes in an LGA package (11.2 mm  $\times$  11.2 mm  $\times$  5.5 mm) that meets Pb-free solder reflow profile requirements, per JEDEC J-STD-020. It offers an extended operating temperature range of -40°C to +105°C.

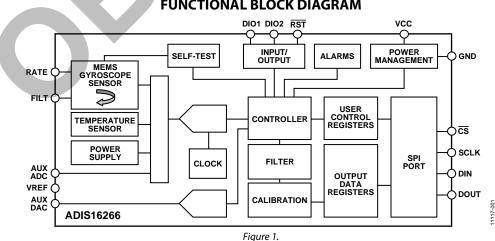

#### FUNCTIONAL BLOCK DIAGRAM

#### Rev. B

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2012–2015 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

### TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| General Description 1                        |

| Functional Block Diagram1                    |

| Revision History 2                           |

| Specifications                               |

| Timing Specifications                        |

| Absolute Maximum Ratings 6                   |

| ESD Caution 6                                |

| Pin Configuration and Function Descriptions7 |

| Typical Performance Characteristics          |

| Theory of Operation9                         |

| Sensing Element                              |

| Data Sampling and Processing9                |

| User Interface                               |

| Basic Operation10                            |

| Reading Sensor Data10                        |

| User Registers                               |

#### **REVISION HISTORY**

#### 1/14—Rev. 0 to Rev. A

10/12—Revision 0: Initial Version

| Output Data Registers 12          |

|-----------------------------------|

| Device Configuration13            |

| Digital Signal Processing         |

| Decimation Filter (Update Rate)14 |

| Frequency Response14              |

| Dynamic Range14                   |

| Calibration                       |

| System Tools                      |

| Diagnostics                       |

| Alarms                            |

| Product Identification19          |

| Applications Information          |

| Assembly                          |

| Bias Optimization                 |

| Interface PCB                     |

| Outline Dimensions                |

| Ordering Guide                    |

### **SPECIFICATIONS**

$T_A = -40^{\circ}$ C to  $+105^{\circ}$ C, VCC = 5.0 V, angular rate =  $0^{\circ}$ /sec,  $\pm 1 g$ ,  $\pm 14,000^{\circ}$ /sec range setting, unless otherwise noted.

#### Table 1.

| Parameter                        | Test Conditions/Comments                                                 | Min | Тур  | Мах  | Unit          |

|----------------------------------|--------------------------------------------------------------------------|-----|------|------|---------------|

| SENSITIVITY <sup>1</sup>         | Clockwise rotation is positive output                                    |     |      |      |               |

|                                  | 25°C, dynamic range = $\pm 14,000^{\circ}/\text{sec}^2$                  |     | 4.17 |      | °/sec/LSB     |

|                                  | $25^{\circ}$ C, dynamic range = $\pm 7000^{\circ}$ /sec                  |     | 2.08 |      | °/sec/LSB     |

|                                  | $25^{\circ}$ C, dynamic range = $\pm 3500^{\circ}$ /sec                  |     | 1.04 |      | °/sec/LSB     |

| Initial Tolerance                | $25^{\circ}$ C, dynamic range = $\pm 14000^{\circ}$ /sec, VDD = 5 V      |     | ±0.5 | ±2   | %             |

| Temperature Coefficient          | 4.75 V < VDD < 5.25 V                                                    |     | 200  |      | ppm/°C        |

| Nonlinearity                     | Best fit straight line                                                   |     | 0.1  |      | % of FS       |

| BIAS                             |                                                                          |     |      |      |               |

| Initial Error                    |                                                                          |     | ±15  |      | °/sec         |

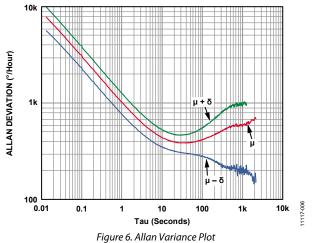

| In-Run Bias Stability            | 25°C, 1 σ                                                                |     | 470  |      | °/hour        |

| Angular Random Walk              | 25°C, 1 σ                                                                |     | 21.5 |      | °/√hour       |

| Linear Acceleration Effect       | 25°C, 1 σ                                                                |     | 0.1  |      | °/sec/g       |

| Temperature Coefficient          |                                                                          |     | 0.35 |      | °/sec/°C      |

| Voltage Sensitivity              | VCC = 4.75 V to 5.25 V, $\mu \pm 1 \sigma$                               |     | 7.5  |      | °/sec/V       |

| NOISE PERFORMANCE                |                                                                          |     |      |      |               |

| Output Noise                     | 25°C, ±14,000°/sec range, no filtering                                   |     | 11.2 |      | °/sec rms     |

|                                  | 25°C, ±7000°/sec range, 4-tap filter setting                             |     | 7.2  |      | °/sec rms     |

|                                  | 25°C, ±3500°/sec range, 16-tap filter setting                            |     | 3.4  |      | °/sec rms     |

| Rate Noise Density               | $25^{\circ}$ C, f = 25 Hz, $\pm 14,000^{\circ}$ /sec range, no filtering |     | 0.44 |      | °/sec/√Hz rms |

| FREQUENCY RESPONSE               |                                                                          |     |      |      |               |

| 3 dB Bandwidth                   |                                                                          |     | 360  |      | Hz            |

| Sensor Resonant Frequency        |                                                                          | 16  | 18   | 20   | kHz           |

| SELF-TEST STATE                  |                                                                          |     |      |      |               |

| Change for Positive Stimulus     | ±14,000°/sec dynamic range setting                                       | 150 |      | 500  | LSB           |

| Change for Negative Stimulus     | ±14,000°/sec dynamic range setting                                       |     |      | -150 | LSB           |

| Internal Self-Test Cycle Time    |                                                                          | 30  |      |      | ms            |

| ADC INPUT                        |                                                                          |     |      |      |               |

| Resolution                       |                                                                          |     | 12   |      | Bits          |

| Integral Nonlinearity            |                                                                          |     | ±2   |      | LSB           |

| Differential Nonlinearity        |                                                                          |     | ±1   |      | LSB           |

| Offset Error                     |                                                                          |     | ±4   |      | LSB           |

| Gain Error                       |                                                                          |     | ±2   |      | LSB           |

| Input Range                      | ×                                                                        | 0   |      | 2.5  | V             |

| Input Capacitance                | During acquisition                                                       |     | 20   |      | pF            |

| ON-CHIP VOLTAGE REFERENCE        |                                                                          |     | 2.5  |      | V             |

| Accuracy                         | 25°C                                                                     | -10 |      | +10  | mV            |

| Temperature Coefficient          |                                                                          |     | ±40  |      | ppm/°C        |

| Output Impedance                 |                                                                          |     | 70   |      | Ω             |

| DAC OUTPUT                       | 5 kΩ/100 pF to GND                                                       |     |      |      |               |

| Resolution                       |                                                                          |     | 12   |      | Bits          |

| Relative Accuracy                | For Code 101 to Code 4095                                                |     | 4    |      | LSB           |

| Differential Nonlinearity        |                                                                          |     | 1    |      | LSB           |

| Offset Error                     |                                                                          |     | ±5   |      | mV            |

| Gain Error                       |                                                                          |     | ±0.5 |      | %             |

|                                  |                                                                          | 1   | _0.0 |      |               |

| Output Bange                     |                                                                          | 0   |      | 2.5  | V             |

| Output Range<br>Output Impedance |                                                                          | 0   | 2    | 2.5  | V<br>Ω        |

| Parameter                               | Test Conditions/Comments             | Min    | Тур  | Max  | Unit   |

|-----------------------------------------|--------------------------------------|--------|------|------|--------|

| LOGIC INPUTS                            | Internal 3.3 V interface             |        |      |      |        |

| Input High Voltage, V <sub>INH</sub>    |                                      | 2.0    |      |      | V      |

| Input Low Voltage, VINL                 |                                      |        |      | 0.8  | V      |

| Logic 1 Input Current, IINH             | $V_{IH} = 3.3 V$                     |        | ±0.2 | ±10  | μΑ     |

| Logic 0 Input Current, I <sub>INL</sub> | $V_{IL} = 0 V$                       |        |      |      |        |

| All Except RST                          |                                      |        | -40  | -60  | μΑ     |

| RST                                     | The RST pin has an internal pull-up. |        | -1   |      | mA     |

| Input Capacitance, C <sub>IN</sub>      |                                      |        | 10   |      | pF     |

| DIGITAL OUTPUTS                         | Internal 3.3 V interface             |        |      |      |        |

| Output High Voltage, V <sub>он</sub>    | I <sub>SOURCE</sub> = 1.6 mA         | 2.4    |      |      | V      |

| Output Low Voltage, Vol                 | I <sub>SINK</sub> = 1.6 mA           |        |      | 0.4  | V      |

| SLEEP TIMER                             |                                      |        |      |      |        |

| Timeout Period <sup>3</sup>             |                                      | 0.5    |      | 128  | sec    |

| START-UP TIME                           |                                      |        |      |      |        |

| Initial Start-Up Time                   |                                      |        | 170  |      | ms     |

| Sleep Mode Recovery                     |                                      |        | 2.5  |      | ms     |

| Reset Recovery                          |                                      | · .    | 78   |      | ms     |

| Flash Memory Update Time                |                                      |        | 40   |      | ms     |

| Flash Memory Test Time                  |                                      |        | 18   |      | ms     |

| Self-Test Time                          |                                      |        | 30   |      | ms     |

| FLASH MEMORY                            |                                      |        |      |      |        |

| Endurance⁴                              |                                      | 20,000 |      |      | Cycles |

| Data Retention <sup>5</sup>             | T <sub>J</sub> = 55°C                | 10     |      |      | Years  |

| CONVERSION RATE                         |                                      |        |      |      |        |

| Sample Rate                             |                                      |        | 2429 |      | SPS    |

| Sample Rate Tolerance                   |                                      |        |      | ±3   | %      |

| POWER SUPPLY                            |                                      |        |      |      |        |

| Operating Voltage Range, Vcc            |                                      | 4.75   | 5.0  | 5.25 | V      |

| Power Supply Current                    |                                      |        | 41   |      | mA     |

|                                         | Sleep mode                           |        | 400  |      | μA     |

<sup>1</sup> Characterization data represents ±4σ to fall within the ±1% limit.

<sup>2</sup> The maximum guaranteed measurement range is ±14,000°/sec. The sensor outputs measure beyond this range, but performance is guaranteed.

<sup>3</sup> Guaranteed by design.

<sup>4</sup> Endurance is qualified as per JEDEC Standard 22, Method A117, and measured at -40°C, +25°C, +85°C, and +125°C.

<sup>5</sup> Retention lifetime equivalent at a junction temperature (T<sub>i</sub>) of 55°C, as per JEDEC Standard 22, Method A117. Retention lifetime decreases with junction temperature.

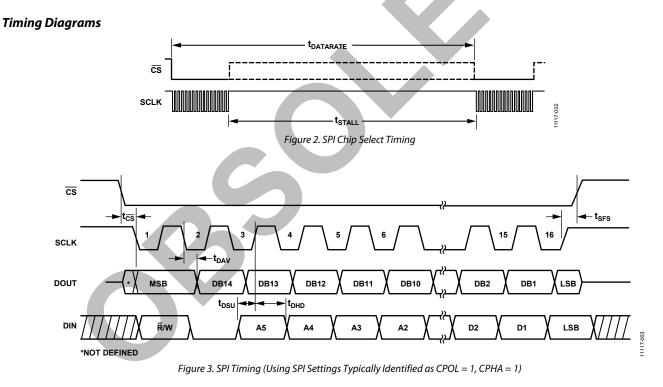

#### TIMING SPECIFICATIONS

$T_A = -40^{\circ}$ C to +85°C, VCC = 5.0 V, unless otherwise noted.

#### Table 2.

| Parameter         | Description                                            | Min <sup>1</sup> | Тур | Max <sup>1</sup> | Unit |

|-------------------|--------------------------------------------------------|------------------|-----|------------------|------|

| fsclk             | Serial clock (not shown in figures)                    | 0.01             |     | 2.5              | MHz  |

| <b>t</b> DATARATE | Data rate period                                       | 32               |     |                  | μs   |

| tstall            | Stall period between data                              | 9                |     |                  | μs   |

| t <sub>cs</sub>   | Chip select to clock edge                              | 48.8             |     |                  | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLK falling edge <sup>2</sup> |                  |     | 100              | ns   |

| t <sub>DSU</sub>  | Data input setup time before SCLK rising edge          | 24.4             |     |                  | ns   |

| t <sub>DHD</sub>  | Data input hold time after SCLK rising edge            | 48.8             |     |                  | ns   |

| t <sub>DF</sub>   | Data output fall time (not shown in figures)           |                  | 5   | 12.5             | ns   |

| t <sub>DR</sub>   | Data output rise time (not shown in figures)           |                  | 5   | 12.5             | ns   |

| tsfs              | CS high after SCLK edge <sup>3</sup>                   | 5                |     |                  | ns   |

<sup>1</sup> Guaranteed by design; not production tested.

<sup>2</sup> The MSB presents an exception to this parameter. The MSB clocks out on the falling edge of  $\overline{CS}$ . The remaining DOUT bits are clocked after the falling edge of SCLK and are governed by this specification.

<sup>3</sup> This parameter may need to be expanded to allow for proper capture of the LSB. After CS goes high, the DOUT line enters a high impedance state.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Table 5.                                 |                  |

|------------------------------------------|------------------|

| Parameter                                | Rating           |

| Acceleration                             |                  |

| Any Axis, Unpowered, 0.5 ms              | 2000 g           |

| Any Axis, Powered, 0.5 ms                | 2000 g           |

| VCC to GND                               | –0.3 V to +6.0 V |

| Digital Input/Output Voltage to GND      | –0.3 V to +5.3 V |

| Analog Inputs to GND                     | –0.3 V to +3.5 V |

| Operating Temperature Range <sup>1</sup> | -40°C to +105°C  |

| Storage Temperature Range <sup>1</sup>   | –65°C to +150°C  |

<sup>1</sup> Extended exposure to temperatures outside the temperature range of  $-40^{\circ}$ C to +85°C can adversely affect the accuracy of the factory calibration. For best accuracy, store the part within the temperature range of  $-40^{\circ}$ C to +85°C.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

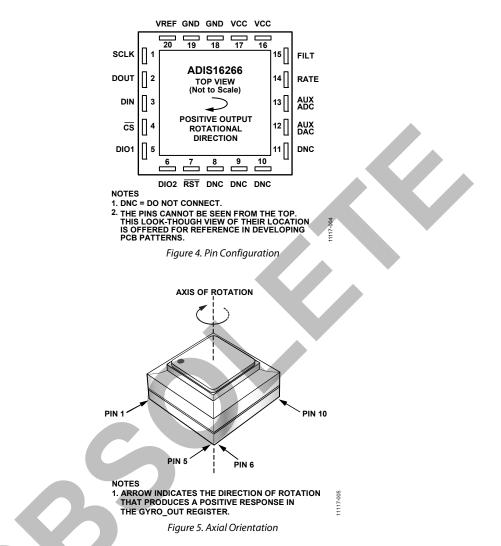

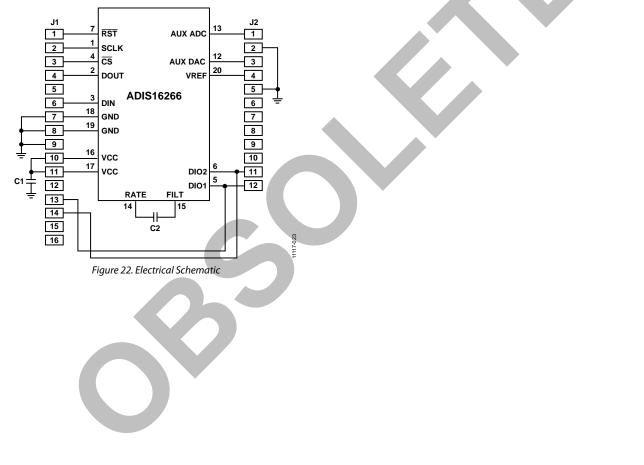

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### **Table 4. Pin Function Descriptions**

| Pin No.      | Mnemonic   | Type <sup>1</sup> | Description                                                             |

|--------------|------------|-------------------|-------------------------------------------------------------------------|

| 1            | SCLK       |                   | SPI Serial Clock.                                                       |

| 2            | DOUT       | 0                 | SPI Data Output. DOUT clocks the output on the falling edge of SCLK.    |

| 3            | DIN        | 1                 | SPI Data Input. DIN clocks the input on the rising edge of SCLK.        |

| 4            | <u>CS</u>  | T                 | SPI Chip Select. Active low.                                            |

| 5, 6         | DIO1, DIO2 | I/O               | Configurable Digital Input/Output.                                      |

| 7            | RST        | I                 | Reset. Active low.                                                      |

| 8, 9, 10, 11 | DNC        |                   | Do Not Connect.                                                         |

| 12           | AUX DAC    | 0                 | Auxiliary DAC Output.                                                   |

| 13           | AUX ADC    | I                 | Auxiliary ADC Input.                                                    |

| 14           | RATE       | 0                 | Rate Output. For bandwidth reduction only, the output is not specified. |

| 15           | FILT       | I                 | Filter Terminal.                                                        |

| 16, 17       | VCC        | S                 | 5.0 V Power Supply.                                                     |

| 18, 19       | GND        | S                 | Ground.                                                                 |

| 20           | VREF       | 0                 | Precision Reference Output.                                             |

$^{1}$  I = input, I/O = input/output, O = output, and S = supply.

80 60 40

20 0 -20 -40 -60

–80 ∟ –40

-20

0

20

**TEMPERATURE (°C)** Figure 7. Bias vs. Temperature

40

RELATIVE ERROR (°/sec)

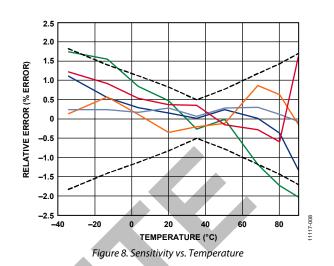

### **TYPICAL PERFORMANCE CHARACTERISTICS**

17-007

80

60

### THEORY OF OPERATION

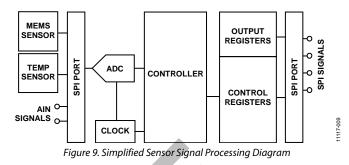

The ADIS16266 integrates a MEMS gyroscope with data sampling, signal processing, and calibration functions, along with a simple user interface. This sensing system collects data autonomously and makes it available to any processor system that supports a 4-wire serial peripheral interface (SPI).

#### SENSING ELEMENT

The sensing element operates on the principle of a resonator gyro. Two polysilicon sensing structures each contain a dither frame that is electrostatically driven to resonance, producing the necessary velocity element to generate a Coriolis force during angular rate. At two of the outer extremes of each frame, orthogonal to the dither motion, movable fingers are placed between fixed pickoff fingers to form a capacitive pickoff structure that senses Coriolis motion. The resulting signal is fed into a series of gain and demodulation stages that produce the electrical rate signal output. The differential structure minimizes the response to linear acceleration (gravity, vibration, and so on) and EMI.

### DATA SAMPLING AND PROCESSING

The ADIS16266 runs autonomously, based on the configuration in the user control registers. The analog gyroscope signal feeds into an analog-to-digital converter (ADC) stage, which passes digitized data into the controller for data processing and register loading. Data processing in the embedded controller includes correction formulas, filtering, and checking for preset alarm conditions. The correction formulas are unique for each individual ADIS16266 and come from the factory characterization of each device over a temperature range of  $-40^{\circ}$ C to  $+70^{\circ}$ C.

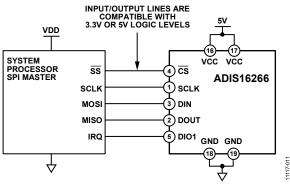

#### USER INTERFACE SPI Interface

Data collection and configuration commands both use the SPI, which consists of four wires. The chip select  $\overline{(CS)}$  signal activates the SPI interface, and the serial clock (SCLK) signal synchronizes the serial data lines. The serial input data clocks into DIN on the SCLK rising edge, and the serial output data clocks out of DOUT on the SCLK falling edge. Many digital processor platforms support this interface with dedicated serial ports and simple instruction sets.

#### **User Registers**

The user registers provide addressing for all input/output operations on the SPI interface. Each 16-bit register has its own unique bit assignment and has two 7-bit addresses: one for its upper byte and one for its lower byte. Table 7 provides a memory map of the user registers, along with the function of each register.

### **BASIC OPERATION**

The ADIS16266 is an autonomous system that requires no user initialization. As soon as it has a valid power supply, it initializes and starts sampling, processing, and loading sensor data into the output registers. After each sample cycle concludes, DIO1 pulses high. The SPI interface enables simple integration with many embedded processor platforms, as shown in Figure 10 (electrical connection) and Table 5 (processor pin names and functions).

Figure 10. Electrical Connection Diagram

| Table 5. Generic Master Processor | Pin Names and Functions |

|-----------------------------------|-------------------------|

|-----------------------------------|-------------------------|

| Pin Name | Function                   |

|----------|----------------------------|

| SS       | Slave select               |

| IRQ      | Interrupt request          |

| MOSI     | Master output, slave input |

| MISO     | Master input, slave output |

| SCLK     | Serial clock               |

|          |                            |

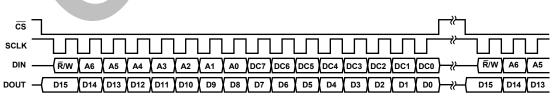

The SPI interface of the ADIS16266 supports full duplex serial communication (simultaneous transmit and receive) and uses the bit sequence shown in Figure 13. Table 6 provides a list of the most common settings that require attention to initialize a processor serial port for the SPI interface of the ADIS16266.

#### Table 6. Generic Master Processor SPI Settings

| Processor Setting   | Description                           |

|---------------------|---------------------------------------|

| Master              | ADIS16266 operates as a slave         |

| SCLK Rate ≤ 2.5 MHz | Maximum serial clock rate             |

| SPI Mode 3          | CPOL = 1 (polarity), CPHA = 1 (phase) |

| MSB First Mode      | Bit sequence                          |

| 16-Bit Mode         | Shift register/data length            |

#### **READING SENSOR DATA**

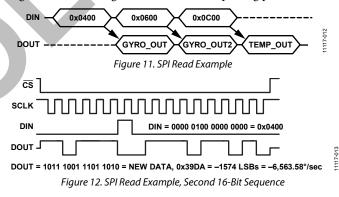

A single register read requires two 16-bit SPI cycles. The first cycle requests the contents of a register using the bit assignments in Figure 13. Then, the register contents follow on DOUT during the second sequence. Figure 11 includes three single register reads in succession. In this example, the process starts with Pin 3, DIN = 0x0400, to request the contents of the GYRO\_OUT register and follows with 0x0600 to request the contents of the GYRO\_OUT register and follows with 0x0600 to request the contents of the GYRO\_OUT2 register and with 0x0C00 to request the contents of the TEMP\_OUT register. Full duplex operation enables processors to use the same 16-bit SPI cycle to read data from DOUT while requesting the next set of data on the DIN pin. Figure 12 provides an example of the four SPI signals when reading GYRO\_OUT in a repeating pattern.

1117-014

NOTES

1. DOUT BITS ARE PRODUCED ONLY WHEN THE PREVIOUS 16-BIT DIN SEQUENCE STARTS WITH  $\overline{R}/W = 0$ .

2. WHEN CS IS HIGH, DOUT IS IN A THREE-STATE, HIGH IMPEDANCE MODE, WHICH ALLOWS MULTIFUNCTIONAL USE OF THE LINE FOR OTHER DEVICES.

Figure 13. SPI Communication Bit Sequence

### **USER REGISTERS**

| Name       | R/W              | Flash Backup     | Address <sup>1</sup> | Default          | Register Description                          | <b>Bit Descriptions</b> |

|------------|------------------|------------------|----------------------|------------------|-----------------------------------------------|-------------------------|

| FLASH_CNT  | R                | Yes              | 0x00                 | N/A <sup>2</sup> | Flash memory write count                      | See Table 27            |

| SUPPLY_OUT | R                | No               | 0x02                 | N/A <sup>2</sup> | Output, power supply                          | See Table 13            |

| GYRO_OUT   | R                | No               | 0x04                 | N/A <sup>2</sup> | Output, gyroscope                             | See Table 8             |

| GYRO_OUT2  | R                | No               | 0x06                 | N/A <sup>2</sup> | Output, gyroscope, bit growth from decimation | See Table 10            |

| Reserved   | N/A <sup>2</sup> | N/A <sup>2</sup> | 0x08                 | N/A <sup>2</sup> | Reserved                                      |                         |

| AUX_ADC    | R                | No               | 0x0A                 | N/A <sup>2</sup> | Output, auxiliary ADC measurement             | See Table 15            |

| TEMP_OUT   | R                | No               | 0x0C                 | N/A <sup>2</sup> | Output, temperature (internal)                | See Table 11            |

| Reserved   | N/A <sup>2</sup> | N/A <sup>2</sup> | 0x0F to 0x13         | N/A <sup>2</sup> | Reserved                                      |                         |

| GYRO_OFF   | R/W              | Yes              | 0x14                 | 0x0000           | Gyroscope bias correction                     | See Table 19            |

| GYRO_SCALE | R/W              | Yes              | 0x16                 | 0x0800           | Gyroscope scale correction                    | See Table 20            |

| Reserved   | $N/A^2$          | N/A <sup>2</sup> | 0x18 to 0x1F         | N/A <sup>2</sup> | Reserved                                      |                         |

| ALM_MAG1   | R/W              | Yes              | 0x20                 | 0x0000           | Alarm 1 trigger setting                       | See Table 30            |

| ALM_MAG2   | R/W              | Yes              | 0x22                 | 0x0000           | Alarm 2 trigger setting                       | See Table 31            |

| ALM_SMPL1  | R/W              | Yes              | 0x24                 | 0x0000           | Alarm 1 sample period                         | See Table 32            |

| ALM_SMPL2  | R/W              | Yes              | 0x26                 | 0x0000           | Alarm 2 sample period                         | See Table 33            |

| ALM_CTRL   | R/W              | Yes              | 0x28                 | 0x0000           | Alarm configuration                           | See Table 34            |

| Reserved   | $N/A^2$          | N/A <sup>2</sup> | 0x2B to 0x2F         | N/A <sup>2</sup> | Reserved                                      |                         |

| AUX_DAC    | R/W              | No               | 0x30                 | 0x0000           | Control, DAC output voltage setting           | See Table 25            |

| GPIO_CTRL  | R/W              | No               | 0x32                 | 0x0000           | Control, digital input/output line            | See Table 23            |

| MSC_CTRL   | R/W              | Yes              | 0x34                 | 0x0006           | Control, data ready, self-test settings       | See Table 24            |

| SMPL_PRD   | R/W              | Yes              | 0x36                 | 0x0000           | Control, internal sample rate                 | See Table 17            |

| SENS_AVG   | R/W              | Yes              | 0x38                 | 0x0401           | Control, dynamic range, filtering             | See Table 18            |

| SLP_CNT    | W                | Yes              | 0x3A                 | N/A <sup>2</sup> | Control, sleep mode initiation                | See Table 22            |

| DIAG_STAT  | R                | No               | 0x3C                 | N/A <sup>2</sup> | Diagnostic, error flags                       | See Table 29            |

| GLOB_CMD   | W                | No               | 0x3E                 | N/A <sup>2</sup> | Control, global commands                      | See Table 21            |

|            |                  |                  | 0x40 to 0x51         | N/A <sup>2</sup> | Reserved                                      |                         |

| LOT_ID1    | R                | Yes              | 0x52                 | N/A              | Lot Identification Code 1                     | See Table 37            |

| LOT_ID2    | R                | Yes              | 0x54                 | N/A <sup>2</sup> | Lot Identification Code 2                     | See Table 37            |

| PROD_ID    | R                | Yes              | 0x56                 | 0x3F8A           | Product identifier; 16,266                    | See Table 37            |

| SERIAL_NUM | R                | Yes              | 0x58                 | N/A <sup>2</sup> | Serial number                                 | See Table 37            |

<sup>1</sup> Each register contains two bytes. The address column in this table only offers the address of the lower byte. Add 1 to it to calculate the address of the upper byte. <sup>2</sup> N/A means not applicable.

#### **OUTPUT DATA REGISTERS**

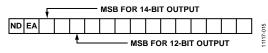

Figure 14 displays the generic pattern for the format of the output registers. The ND bit is equal to 1 when the register contains unread data. The EA bit is high when any error/alarm flag in the DIAG\_STAT register is equal to 1.

Figure 14. Output Register Bit Assignments

#### Rotation Rate (Gyroscope)

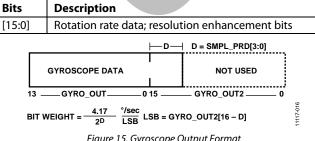

GYRO\_OUT (see Table 8) is the primary register for gyroscope output data and uses 14-bit twos complement format for its data. Table 9 provides several examples for converting digital data into °/sec.

#### Table 8. GYRO\_OUT Bits (Base Address = 0x04)

| Bits   | Description                                                                         |

|--------|-------------------------------------------------------------------------------------|

| 15     | New (unread) data indicator; bit = 1 indicates new,<br>unread data in this register |

| 14     | Error/alarm; bit = 1 when DIAG_STAT $\neq$ 0x0000                                   |

| [13:0] | Gyroscope data; twos complement, 4.17°/sec per LSB,<br>0°/sec = 0x0000              |

#### Table 9. GYRO\_OUT, Twos Complement Format

| _ / I                |         |        |                     |

|----------------------|---------|--------|---------------------|

| <b>Rotation Rate</b> | Decimal | Hex    | Binary              |

| +14000°/sec          | +3357   | 0x0D1D | xx00 1101 0001 1101 |

| +8.34°/sec           | +2      | 0x0002 | xx00 0000 0000 0010 |

| +4.17°/sec           | +1      | 0x0001 | xx00 0000 0000 0001 |

| 0°/sec               | 0       | 0x0000 | xx00 0000 0000 0000 |

| -4.17°/sec           | -1      | 0x3FFF | xx11 1111 1111 1111 |

| -8.34°/sec           | -2      | 0x3FFE | xx11 1111 1111 1110 |

| -14000°/sec          | -3357   | 0x32E3 | xx11 0010 1110 0011 |

The GYRO\_OUT2 register (see Table 10) captures the bit growth associated with the decimation filter (see Figure 19) using an MSB justified format. The bit growth starts with the MSB (GYRO\_OUT2[15]), is equal to the decimation rate setting in SMPL\_PRD[3:0] (see Table 17), and grows in the LSB direction as the decimation rate increases.

#### Table 10. GYRO OUT2 Bits (Base Address = 0x06)

Figure 15. Gyroscope Output Format

#### Internal Temperature

The TEMP\_OUT register (see Table 11) provides access to a sensor that monitors internal temperature, which influences the calibration correction formulas for the gyroscope data. Note that this difference between internal and ambient temperatures is dependent on many factors, which can introduce variation that can approach ±10°C. This temperature measurement is useful for tracking relative changes in temperature.

#### Table 11. TEMP\_OUT Bits (Base Address = 0x0C)

| Bits    | Description                                                                            |

|---------|----------------------------------------------------------------------------------------|

| 15      | New (unread) data indicator; bit = 1 indicates new,<br>unread data in this register    |

| 14      | Error/alarm; bit = 1 when DIAG_STAT $\neq$ 0x0000                                      |

| [13:12] | Not used                                                                               |

| [11:0]  | Temperature data; twos complement, $0.1447^{\circ}$ C per LSB, $0^{\circ}$ C = $0x000$ |

#### Table 12. Temperature, Twos Complement Format

| Temperature | Decimal  | Hex   | Binary Output       |

|-------------|----------|-------|---------------------|

| +105°C      | +544 LSB | 0x220 | xxxx 0010 0010 0000 |

| +25.2894°C  | +2 LSB   | 0x002 | xxxx 0000 0000 0010 |

| +25.1447°C  | +1 LSB   | 0x001 | xxxx 0000 0000 0001 |

| +25°C       | 0 LSB    | 0x000 | xxxx 0000 0000 0000 |

| +24.8553°C  | –1 LSB   | 0xFFF | xxxx 1111 1111 1111 |

| +24.7106°C  | –2 LSB   | 0xFFE | xxxx 1111 1111 1110 |

| -40°C       | -449 LSB | 0xE3F | xxxx 1110 0011 1111 |

#### **Power Supply Voltage**

The SUPPLY\_OUT (see Table 13) register provides a digital representation of the power supply voltage, across VDD and GND.

#### Table 13. SUPPLY\_OUT Bits (Base Address = 0x02)

| Bits    | Description                                                                         |

|---------|-------------------------------------------------------------------------------------|

| 15      | New (unread) data indicator; bit = 1 indicates new,<br>unread data in this register |

| 14      | Error/alarm; bit = 1 when DIAG_STAT $\neq$ 0x0000                                   |

| [13:12] | Not used                                                                            |

| [11:0]  | Power supply (VDD) data, binary (0 V = 0x000)<br>1.83 mV/LSB                        |

#### Table 14. Power Supply Voltage Data Format Examples

|                    | 17 0     |       | 1                   |

|--------------------|----------|-------|---------------------|

| Supply Voltage (V) | Decimal  | Hex   | Binary Output       |

| 5.25               | 2867 LSB | 0xB33 | xxxx 1011 0011 0011 |

| 5.0 + 0.00183      | 2731 LSB | 0xAAB | xxxx 1010 1010 1011 |

| 5.0                | 2730 LSB | 0xAAA | xxxx 1010 1010 1010 |

| 5.0 - 0.00183      | 2729 LSB | 0xAA9 | xxxx 1010 1010 1001 |

| 4.75               | 2594 LSB | 0xA22 | xxxx 1010 0010 0010 |

|                    |          |       | •                   |

#### Auxiliary Input Voltage (AUX\_ADC)

The AUX\_ADC (see Table 15) register provides a digital representation of the voltage on the AUX\_ADC pin.

#### Table 15. AUX\_ADC Bits (Base Address = 0x0A)

| Bits    | Description                                                                         |

|---------|-------------------------------------------------------------------------------------|

| 15      | New (unread) data indicator; bit = 1 indicates new,<br>unread data in this register |

| 14      | Error/alarm; bit = 1 when DIAG_STAT $\neq$ 0x0000                                   |

| [13:12] | Not used                                                                            |

| [11:0]  | Auxiliary input voltage, binary (0 V = 0x000)<br>0.6105 mV/LSB                      |

#### Table 16. AUX\_ADC Voltage Data Format Examples

| Input (mV) | Decimal  | Hex   | Binary Output       |

|------------|----------|-------|---------------------|

| 2500       | 4095 LSB | 0xFFF | xxxx 1111 1111 1111 |

| 1200       | 1966 LSB | 0x7AE | xxxx 0111 1010 1110 |

| 0.6105     | 1 LSB    | 0x001 | xxxx 0000 0000 0001 |

| 0          | 0 LSB    | 0x000 | xxxx 0000 0000 0000 |

#### **DEVICE CONFIGURATION**

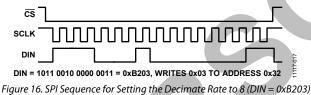

The control registers listed in Table 7 provide a variety of user configuration options. The SPI provides access to these registers, one byte at a time, using the bit assignments shown in Figure 13. Each register has 16 bits, wherein Bits[7:0] represent the lower address, and Bits[15:8] represent the upper address. Figure 16 provides an example of writing 0x03 to Address 0x32 (GPIO\_CTRL[7:0], see Table 23).

#### **Dual Memory Structure**

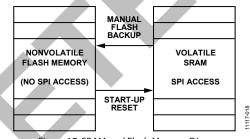

Writing configuration data to a control register updates its SRAM contents, which are volatile. After optimizing each relevant control register setting in a system, set  $GLOB\_CMD[3] = 1$  (DIN = 0xBE08) to back up these settings in the nonvolatile flash memory. The flash backup process requires a valid power supply level for the entire 40 ms process time. Table 7 provides a register memory map that includes a column of flash backup information. A yes in this column indicates that a register has a mirror location in flash and, when backed up properly, automatically restores itself during startup or after a reset. Figure 17 provides a diagram of the dual memory structure that is used to manage operation and store critical user settings.

Figure 17. SRAM and Flash Memory Diagram

### **DIGITAL SIGNAL PROCESSING**

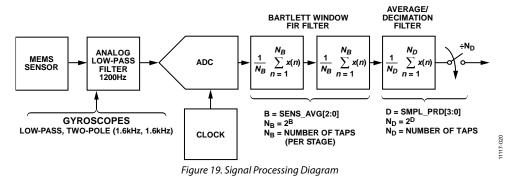

Figure 19 provides a signal processing diagram that describes all of the user-configurable options, which influence sample rate and the frequency response. Using the factory default settings for the SMPL\_PRD and SENS\_AVG registers, the effective sensor bandwidth is 360 Hz.

#### **DECIMATION FILTER (UPDATE RATE)**

The internal sampling system produces new data in the output data registers at a rate of 2429 SPS. The SMPL\_PRD register (see Table 17) provides the functional control for the decimation filter stage, which provides a user control input for reducing the update rate in the output registers. The decimation filter reduces the update rate, using an averaging filter with a decimated output. These bits provide a binomial control that divides the data rate by a factor of 2 every time this number increases by 1. For example, set SMPL\_PRD[3:0] = 00100 (DIN = 0xB604) to set the decimation factor to 16. This reduces the update rate to 151.8 SPS and the bandwidth (-3 dB) to approximately 75 Hz.

#### Table 17. SMPL\_PRD Bits (Base Address = 0x36)

| Bits   | Description (Default = 0x0000)        |  |  |

|--------|---------------------------------------|--|--|

| [15:4] | Not used                              |  |  |

| [3:0]  | Decimation setting (D), see Figure 19 |  |  |

#### FREQUENCY RESPONSE

#### Analog Filter

Prior to the analog-to-digital conversion stage, the ADIS16266 has a two-pole analog filter, with both poles located at approximately 1.6 kHz. The RATE and FILT pins provide access to the amplifier feedback path on one of these filters. This provides an opportunity to reduce the cut-off frequency associated with this filter pole, according to the following relationship.

$$f_C = \frac{1}{2\pi \times 180000 \times (C + 560 \text{ pF})}$$

For example, adding a 1000 pF capacitor reduces this pole to approximately 567 Hz.

#### **Digital Filtering**

A programmable low-pass filter provides additional noise reduction on the inertial sensor outputs. This filter contains two cascaded averaging filters that provide a Bartlett window, FIR filter response (see Figure 19). For example, set SENS\_AVG[2:0] = 100 (DIN = 0xB804) to set each stage to 16 taps. When used with the default sample rate of 2429 SPS (no decimation), this reduces the bandwidth of the digital filter to approximately 49 Hz. The minimum setting for this filter is two taps per stage (SENS\_AVG[2:0]  $\ge$  001).

| Table 18. SENS_AVG Dits (Dase Address – 0x36) |                                                                                      |  |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Bits                                          | Description (Default = 0x0401)                                                       |  |  |

| [15:11]                                       | Not used.                                                                            |  |  |

| [10:8]                                        | Measurement range (sensitivity) selection.                                           |  |  |

|                                               | $100 = \pm 14,000^{\circ}/\text{sec}$ , filter taps $\ge 2$ (Bits[2:0] $\ge 0x01$ ). |  |  |

|                                               | $010 = \pm 7000^{\circ}/\text{sec}$ , filter taps $\ge 4$ (Bits[2:0] $\ge 0x02$ ).   |  |  |

|                                               | $001 = \pm 3500^{\circ}$ /sec, filter taps $\ge 16$ (Bits[2:0] $\ge 0x04$ ).         |  |  |

| [7:3]                                         | Not used.                                                                            |  |  |

| [2:0]                                         | Number of taps in each stage; value of m in $N = 2^{m}$ .                            |  |  |

|                                               |                                                                                      |  |  |

| 0                                             |                                                                                      |  |  |

| -20                                           |                                                                                      |  |  |

| -20                                           |                                                                                      |  |  |

| -40                                           |                                                                                      |  |  |

| (gp)<br>–60                                   |                                                                                      |  |  |

| 09- 0<br>8- 08-                               |                                                                                      |  |  |

| LIN -80                                       |                                                                                      |  |  |

| MAC                                           |                                                                                      |  |  |

| -100                                          |                                                                                      |  |  |

| -120                                          | N = 2                                                                                |  |  |

| -120                                          | N = 16                                                                               |  |  |

| -140                                          | N = 64                                                                               |  |  |

| 0.                                            | 001 0.01 0.1 1 6<br>FREQUENCY (f/f <sub>S</sub> )                                    |  |  |

|                                               |                                                                                      |  |  |

| Fig                                           | ure 18. Digital Filter Frequency, Bartlett Window FIR Filter                         |  |  |

Figure 18. Digital Filter Frequency, Bartlett Window FIR Filter (Phase = N Samples)

#### **DYNAMIC RANGE**

The SENS\_AVG[10:8] bits provide three dynamic range settings for this gyroscope. The lower dynamic range settings ( $\pm 3500^{\circ}$ /sec and  $\pm 7000^{\circ}$ /sec) limit the minimum filter tap sizes to maintain resolution. For example, set SENS\_AVG[10:8] = 010 (DIN = 0xB902) for a measurement range of  $\pm 7000^{\circ}$ /sec. Because this setting can influence the filter settings, program SENS\_AVG[10:8] and then SENS\_AVG[2:0] if more filtering is required.

Rev. B | Page 14 of 24

### CALIBRATION

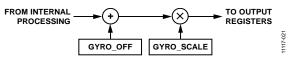

The GYRO\_OFF and GYRO\_SCALE registers provide user controls for making in-system adjustments to offset and the scale factor.

Figure 20. User Calibration Registers

#### Table 19. GYRO\_OFF Bits (Base Address = 0x14)

| Bits    | Description (Default = 0x0000)                    |

|---------|---------------------------------------------------|

| [15:12] | Not used.                                         |

| [11:0]  | Offset adjustment factor, twos complement format, |

|         | 1.04°/sec per LSB. Examples:                      |

|         | 0x000: add 0°/sec to gyroscope data.              |

|         | 0x001: add 1.04°/sec to gyroscope data.           |

|         | 0x0AA: add 176.8°/sec to gyroscope data.          |

|         | 0xF0F: subtract 250.64°/sec from gyroscope data.  |

|         | 0xFFF: subtract 1.04°/sec from gyroscope data.    |

| Table 20. GYRO | _SCALE Bits | (Base Address = 0x16 | j) |

|----------------|-------------|----------------------|----|

|----------------|-------------|----------------------|----|

| Bits    | Description (Default = 0x0800)                                           |

|---------|--------------------------------------------------------------------------|

| [15:12] | Not used.                                                                |

| [11:0]  | Scale adjustment factor, offset binary format, 0.00048828/LSB. Examples: |

|         | 0x000: multiply output by 0.                                             |

|         | 0x7F0: multiply gyroscope data by 0.99218.                               |

|         | 0x800: multiply output by 1.                                             |

|         | 0x8A0: multiply output by 1.078122.                                      |

|         | 0xFFF: multiply output by 1.9995.                                        |

### SYSTEM TOOLS Global Commands

The GLOB\_CMD register provides trigger bits for several functions. Setting the assigned bit to 1 starts each operation, which returns the bit to 0 after completion. For example, set  $GLOB\_CMD[7] = 1$  (DIN = 0xBE80) to execute a software reset, which stops the sensor operation and runs the device through its start-up sequence. This sequence includes loading the control registers with the contents of their respective flash memory locations prior to producing new data.

#### Table 21. GLOB\_CMD Bits (Base Address = 0x3E)

| Bits   | Description                          |

|--------|--------------------------------------|

| [15:8] | Not used.                            |

| 7      | Software reset command.              |

| 6:4    | Not used.                            |

| 3      | Flash update command.                |

| 2      | Auxiliary DAC data latch.            |

| 1      | Factory calibration restore command. |

| 0      | Autonull command.                    |

#### **Power Management**

Use SLP\_CNT[7:0] to put the device into sleep mode for a specified period. For example, SLP\_CNT[7:0] = 0x64 (DIN = 0xBA64) puts the ADIS16266 to sleep for 50 seconds.

#### Table 22. SLP\_CNT Bits (Base Address = 0x3A)

| Bits   | Description                                  |

|--------|----------------------------------------------|

| [15:8] | Not used.                                    |

| [7:0]  | Programmable sleep time bits, 0.5 sec/LSB. T |

#### General-Purpose Input/Output

DIO1 and DIO2 are configurable, general-purpose input/output lines that serve multiple purposes according to the following control register priority: MSC\_CTRL, ALM\_CTRL, and GPIO\_CTRL. For example, set GPIO\_CTRL = 0x0202 (DIN = 0xB302, and then 0xB202) to configure DIO1 as an input and DIO2 as an output that is set high.

#### Table 23. GPIO\_CTRL Bits (Base Address = 0x32)

| Bits    | Description (Default = 0x0000)                                |

|---------|---------------------------------------------------------------|

| [15:10] | Not used.                                                     |

| 9       | General-Purpose input/output Line 2 (DIO2) data level.        |

| 8       | General-Purpose input/output Line 1 (DIO1) data level.        |

| [7:2]   | Not used.                                                     |

| 1       | General-Purpose input/output Line 2 (DIO2) direction control. |

|         | 1 = output, 0 = input.                                        |

| 0       | General-Purpose input/output Line 1 (DIO1) direction control. |

|         | 1 = output, 0 = input.                                        |

#### Data Ready Input/Output Indicator

The MSC\_CTRL[2:0] bits configure one of the digital input/output lines as a data ready signal for driving an interrupt. For example, set MSC\_CTRL[2:0] = 100 (DIN = 0xB404) to configure DIO1 as a negative-pulse data ready signal. The pulse width is between 100  $\mu$ s and 200  $\mu$ s over all conditions.

| Table 24. MSC_ | _CTRL Bits (Bas | e Address = 0x34) |

|----------------|-----------------|-------------------|

|----------------|-----------------|-------------------|

| <b>D</b> ' |                                                      |  |

|------------|------------------------------------------------------|--|

| Bits       | Description (Default = 0x0006)                       |  |

| [15:12]    | Not used.                                            |  |

| 11         | Memory test (cleared upon completion).               |  |

|            | 1 = enabled, 0 = disabled.                           |  |

| 10         | Internal self-test enable (cleared upon completion). |  |

|            | 1 = enabled, 0 = disabled.                           |  |

| 9          | Manual self-test, negative stimulus.                 |  |

|            | 1 = enabled, 0 = disabled.                           |  |

| 8          | Manual self-test, positive stimulus.                 |  |

|            | 1 = enabled, 0 = disabled.                           |  |

| 7:3        | Not used.                                            |  |

| 2          | Data ready enable.                                   |  |

|            | 1 = enabled, 0 = disabled.                           |  |

| 1          | Data ready polarity.                                 |  |

|            | 1 = active high, 0 = active low.                     |  |

| 0          | Data ready line select.                              |  |

|            | 1 = DIO2, 0 = DIO1.                                  |  |

|            |                                                      |  |

#### Auxiliary DAC

The 12-bit AUX\_DAC line can drive its output to within 5 mV of the ground reference when it is not sinking current. As the output approaches 0 V, the linearity begins to degrade (approximately 100 LSB starting point). As the sink current increases, the nonlinear range increases. The DAC latch command (GLOB\_CMD[2]) moves the values of the AUX\_DAC register into the internal DAC control register, enabling both bytes to take effect at the same time.

#### Table 25. AUX\_DAC Bits (Base Address = 0x30)

| Bits Description (Default = 0x0000) |                                                                                                        |

|-------------------------------------|--------------------------------------------------------------------------------------------------------|

| [15:12]                             | Not used.                                                                                              |

| [11:0]                              | Data bits, scale factor = $0.6105 \text{ mV/code}$ .<br>Offset binary format, $0 \text{ V} = 0$ codes. |

#### Table 26. Setting AUX\_DAC = 2 V

| DIN    | Description                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------------|

| 0xB0CC | AUX_DAC[7:0] = 0xCC (204 LSB).                                                                                           |

| 0xB10C | AUX_DAC[15:8] = 0x0C (3072 LSB).                                                                                         |

| 0xBE04 | $GLOB\_CMD[2] = 1.$                                                                                                      |

|        | Latch AUX_DAC values into the internal DAC control register which causes the output voltage to settle at a value of 2 V. |

#### Memory Management

The FLASH\_CNT register (see Table 27) tracks the number of write cycles for the flash memory to help manage the total cycles against the endurance ratings in Table 1.

#### Table 27. FLASH\_CNT Bits (Base Address = 0x00)

| Bits   | Description          |

|--------|----------------------|

| [15:0] | Flash update counter |

#### DIAGNOSTICS

#### Self-Test

The self-test function allows the user to verify the mechanical integrity of each MEMS sensor. It applies an electrostatic force to each sensor element, which results in mechanical displacement that simulates a response to actual motion. Table 1 lists the expected response for the sensor, which provides pass/fail criteria.

Set MSC\_CTRL[10] = 1 (DIN = 0xB504) to run the internal self-test routine, which exercises the inertial sensor, measures the response, makes a pass/fail decision, reports the decision to the error flags in the DIAG\_STAT register, and then restores normal operation. MSC\_CTRL[10] resets itself to 0 after completing the routine. The MSC\_CTRL[9:8] bits provide manual control of the self-test function for investigation of potential failures. Table 28 outlines an example test flow for using this option to verify the gyroscope function.

#### Table 28. Manual Self-Test Example Sequence

|        | 1 1                                                                                       |

|--------|-------------------------------------------------------------------------------------------|

| DIN    | Description                                                                               |

| 0xB601 | SMPL_PRD[7:0] = 0x01, sample rate = 2429 SPS.                                             |

| 0xB904 | $SENS_AVG[15:8] = 0x04$ , range = $\pm 14000^{\circ}$ /sec.                               |

| 0xB802 | SENS_AVG[7:0] = 0x02, four-tap averaging filter.                                          |

|        | Delay = 50 ms.                                                                            |

| 0x0400 | Read GYRO_OUT.                                                                            |

| 0xB502 | MSC_CTRL[9:8] = 10, gyroscope negative self-test.                                         |

|        | Delay = 50 ms.                                                                            |

| 0x0400 | Read GYRO_OUT.                                                                            |

|        | Determines whether the bias in the gyroscope<br>output changed according to the self-test |

|        | response specified in Table 1.                                                            |

| 0xB501 | MSC_CTRL[9:8] = 01, gyroscope positive self-test.                                         |

|        | Delay = 50 ms.                                                                            |

| 0x0400 | Read GYRO_OUT.                                                                            |

|        | Determines whether the bias in the gyroscope                                              |

|        | output changed according to the self-test                                                 |

|        | response specified in Table 1.                                                            |

| 0xB500 | MSC_CTRL[15:8] = 0x00.                                                                    |

|        |                                                                                           |

Zero motion provides results that are more reliable. The settings in Table 28 are flexible and allow for optimization around speed and noise influence. For example, using fewer filtering taps decreases delay times but increases the potential for noise influence.

#### Memory Test

Setting MSC\_CTRL[11] = 1 (DIN = 0xB508) performs a checksum comparison between the flash memory and SRAM to help verify memory integrity. The pass/fail result is loaded into the DIAG\_STAT[6] register.

#### Status

The error flags provide indicator functions for common system level issues. All of the flags are cleared (set to 0) after each DIAG\_STAT register read cycle. If an error condition remains, the error flag returns to 1 during the next sample cycle. DIAG\_STAT[1:0] does not require a read of this register to return to 0. When the power supply voltage goes back into range, these two flags clear automatically.

#### Table 29. DIAG\_STAT Bits (Base Address = 0x3C)

|   | Table 29. DIAG_STAT bits (base Address = 0x3C) |                                                           |

|---|------------------------------------------------|-----------------------------------------------------------|

|   | Bits                                           | Description                                               |

|   | [15:10]                                        | Not used.                                                 |

|   | 9                                              | Alarm 2 status (1 = active, $0 =$ inactive).              |

|   | 8                                              | Alarm 1 status (1 = active, $0 =$ inactive).              |

|   | 7                                              | Not used.                                                 |

|   | 6                                              | Flash test, checksum flag (1 = fail, 0 = pass).           |

| Ì | 5                                              | Self-test diagnostic error flag (1 = fail, 0 = pass).     |

|   | 4                                              | Sensor overrange (1 = fail, 0 = pass).                    |

| 1 | 3                                              | SPI communication failure $(1 = fail, 0 = pass)$ .        |

|   | 2                                              | Flash update failure (1 = fail, 0 = pass).                |

|   | 1                                              | Power supply > 5.25 V.                                    |

|   |                                                | $1 = power supply > 5.25 V, 0 = power supply \le 5.25 V.$ |

|   | 0                                              | Power supply < 4.75 V.                                    |

| _ |                                                | $1 = power supply < 4.75 V, 0 = power supply \ge 4.75 V.$ |

### **Data Sheet**

### **ALARMS**

#### **Alarm Registers**

The alarm function provides monitoring for two independent conditions. The ALM\_CTRL register provides control inputs for data source selection, data filtering (prior to comparison), static comparison, dynamic rate-of-change comparison, and output indicator configurations. The ALM\_MAGx registers establish the trigger threshold and polarity configurations. Table 35 gives an example of how to configure a static alarm. The ALM\_SMPLx registers provide the numbers of samples to use in the dynamic rate-of-change configuration. The period equals the number in the ALM\_SMPLx register multiplied by the sample period time. See Table 36 for an example of how to configure the sensor for this type of function.

#### Table 30. ALM\_MAG1 Bits (Base Address = 0x20)

| Bits   | Description (Default = 0x0000)                                         |

|--------|------------------------------------------------------------------------|

| 15     | Comparison polarity $(1 = \text{greater than}, 0 = \text{less than}).$ |

| 14     | Not used.                                                              |

| [13:0] | Data bits that match the format of the trigger source selection.       |

#### Table 31. ALM\_MAG2 Bits (Base Address = 0x22)

| Bits   | Description (Default = 0x0000)                                   |

|--------|------------------------------------------------------------------|

| 15     | Comparison polarity (1 = greater than, 0 = less than).           |

| 14     | Not used.                                                        |

| [13:0] | Data bits that match the format of the trigger source selection. |

#### Table 32. ALM SMPL1 Bits (Base Address = 0x24)

| Bits   | Description (Default = 0x0000)                              |

|--------|-------------------------------------------------------------|

| [15:8] | Not used.                                                   |

| [7:0]  | Data bits: number of samples (both $0x00$ and $0x01 = 1$ ). |

|        |                                                             |

#### Table 33. ALM SMPL2 Bits (Base Address = 0x26)

| Bits   | Description (Default = 0x0000)                              |

|--------|-------------------------------------------------------------|

| [15:8] | Not used.                                                   |

| [7:0]  | Data bits: number of samples (both $0x00$ and $0x01 = 1$ ). |

| -      |                                                             |

| Table 34. ALM_CTRL Bits (Base Address = 0x28) |                                                             |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------|--|--|--|--|

| Bits                                          | Description (Default = 0x0000)                              |  |  |  |  |

| 15                                            | Dynamic rate-of-change enable for Alarm 2 (1 = rate         |  |  |  |  |

|                                               | of change, 0 = static level).                               |  |  |  |  |

| [14:12]                                       | Alarm 2 source selection.                                   |  |  |  |  |

|                                               | 000 = disable.                                              |  |  |  |  |

|                                               | 001 = power supply output.                                  |  |  |  |  |

|                                               | 010 = gyroscope output.                                     |  |  |  |  |

|                                               | 011 = not used.                                             |  |  |  |  |

|                                               | 100 = not used.                                             |  |  |  |  |

|                                               | 101 = auxiliary ADC input.                                  |  |  |  |  |

|                                               | 10 = temperature output.                                    |  |  |  |  |

|                                               | 111 = not used.                                             |  |  |  |  |

| 11                                            | Rate-of-change enable for Alarm 1 (1 = dynamic rate         |  |  |  |  |

|                                               | of change, 0 = static level).                               |  |  |  |  |

| [10:8]                                        | Alarm 1 source selection (same as for Alarm 2).             |  |  |  |  |

| [7:5]                                         | ot used.                                                    |  |  |  |  |

| 4                                             | Comparison data filter setting $(1 = filtered data, 0 =$    |  |  |  |  |

|                                               | unfiltered data).                                           |  |  |  |  |

| 3                                             | Not used.                                                   |  |  |  |  |

| 2                                             | Alarm output enable $(1 = enabled, 0 = disabled)$ .         |  |  |  |  |

| 1                                             | Alarm output polarity $(1 = active high, 0 = active low)$ . |  |  |  |  |

| 0                                             | Alarm output line select $(1 = DIO2, 0 = DIO1)$ .           |  |  |  |  |

| Table 35                                      | . Alarm Configuration Example 1                             |  |  |  |  |

| DIN                                           | Description                                                 |  |  |  |  |

| 0xA922,                                       | ALM_CTRL = 0x2217.                                          |  |  |  |  |

| 0xA817                                        | Alarm 1 input = GYRO_OUT.                                   |  |  |  |  |

|                                               | Alarm 2 input = GYRO_OUT.                                   |  |  |  |  |

|                                               | Static level comparison, filtered data.                     |  |  |  |  |

|                                               | DIO2 output indicator, positive polarity.                   |  |  |  |  |

| 0xA183,                                       | ALM MAG1 = 0x83E8.                                          |  |  |  |  |

| 0xA0E8                                        | Alarm 1 is true if GYRO_OUT > +4170°/sec.                   |  |  |  |  |

|                                               |                                                             |  |  |  |  |

ALM\_MAG2 = 0x3830.

Alarm 2 is true if GYRO\_OUT < -8340°/sec.

0xA338,

0xA230

#### Table 36. Alarm Configuration Example 2

| Table 50. Alarm Configuration Example 2 |                                                     |  |  |

|-----------------------------------------|-----------------------------------------------------|--|--|

| DIN                                     | Description                                         |  |  |

| 0xA9AA,                                 | $ALM_CTRL = 0xAA04.$                                |  |  |

| 0xA804                                  | Alarm 1 input = GYRO_OUT.                           |  |  |

|                                         | Alarm 2 input = GYRO_OUT.                           |  |  |

|                                         | Dynamic rate-of-change comparison, unfiltered data. |  |  |

|                                         | DIO1 output indicator, negative polarity.           |  |  |

| 0xB600                                  | SMPL_PRD = 0x0000. Sample rate = 2429 SPS.          |  |  |

| 0xA4FF                                  | ALM_SMPL1[7:0] = 0x00FF.                            |  |  |

|                                         | Alarm 1 dynamic rate-of-change period = 105 ms.     |  |  |

| 0xA6FF                                  | ALM_SMPL2[7:0] = 0x00FF.                            |  |  |

|                                         | Alarm 2 dynamic rate-of-change period = 105 ms.     |  |  |

| 0xA181,                                 | ALM_MAG1 = 0x8100.                                  |  |  |

| 0xA000                                  | Alarm 1 is true if GYRO_OUT changes more than       |  |  |

|                                         | 1067.5°/sec over a period of 105 ms.                |  |  |

| 0xA300,                                 | ALM_MAG2 = 0x000A.                                  |  |  |

| 0xA20A                                  | Alarm 2 is true if GYRO_OUT changes less than       |  |  |

|                                         | 41.7°/sec over a period of 105 ms.                  |  |  |

#### PRODUCT IDENTIFICATION

Table 37 provides a summary of the registers that identify the product: PROD\_ID, which identifies the product type; LOT\_ID1 and LOT\_ID2, the 32-bit lot identification code; and SERIAL\_NUM, which displays the 16-bit serial number. All four registers are two bytes in length.

#### Table 37. Identification Registers

| Tuble 577 Tublication Registers |         |                                 |  |

|---------------------------------|---------|---------------------------------|--|

| <b>Register Name</b>            | Address | Description                     |  |

| LOT_ID1                         | 0x52    | Lot Identification Code 1       |  |

| LOT_ID2                         | 0x54    | Lot Identification Code 2       |  |

| PROD_ID                         | 0x56    | Product identification = 0x3F8A |  |

|                                 |         | (0x3F8A = 16,266 decimal)       |  |

| SERIAL_NUM                      | 0x58    | Serial number                   |  |

|                                 |         |                                 |  |

# APPLICATIONS INFORMATION ASSEMBLY

When developing a process flow for installing ADIS16266 devices on printed circuit boards (PCBs), see the IPC/JEDEC J-STD-020C standard document for reflow temperature profile and processing information. The ADIS16266 can use the Sn-Pb eutectic process or the Pb-free eutectic process from this standard. See IPC/JEDEC J-STD-033 for moisture sensitivity level (MSL) handling requirements. The MSL rating for these devices is marked on the antistatic bags, which protect these devices from electrostatic discharge (ESD) during shipping and handling.

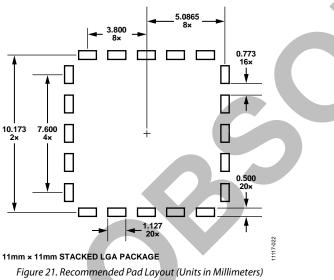

Prior to assembly, review the process flow for information about introducing shock levels that exceed the absolute maximum ratings for the ADIS16266. PCB separation and ultrasonic cleaning processes can introduce high levels of shock and damage the MEMS element. Bowing or flexing the PCB after solder reflow can also place large peeling stress on the pad structure and can damage the device. If this is unavoidable, consider using an underfill material to help distribute these forces across the bottom of the package. Figure 21 provides a PCB pad design example for this package style.

#### **BIAS OPTIMIZATION**

Use the following steps to fine tune the bias to an accuracy that approaches the in-run bias stability,  $0.129^{\circ}/\text{sec}$  (1  $\sigma$ ):

- 1. Apply 5 V and allow enough time to start up.

- 2. Set SENS\_AVG[10:8] = 001 (DIN = 0xB901).

- 3. Collect GYRO\_OUT data for 30 seconds at a sample rate of 2429 SPS.

- 4. Average data record.

- 5. Round to the nearest integer.

- 6. Multiply by -1.

- 7. Write the resulting number (from Step 6) to GYRO\_OFF.

- 8. Set  $GLOB\_CMD[3] = 1$  (DIN = 0xBE08).

- 9. Wait for >50 ms and resume operation.

Alternatively, setting GLOB\_CMD[0] = 1 (DIN = 0xBE01) provides a single sample, bias correction. The Allan variance curve (see Figure 6) provides a trade-off relationship between accuracy and averaging time. For example, an average time of 1 second produces an accuracy of approximately  $0.358^{\circ}$ /sec (1  $\sigma$ ).

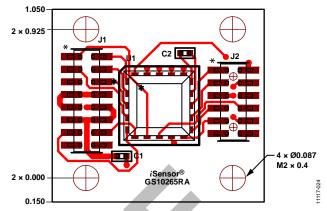

#### **INTERFACE PCB**

The ADIS16266/PCBZ includes one ADIS16266BCCZ IC on a 1.2 inch  $\times$  1.3 inch PCB. The interface PCB simplifies the IC connection of these devices to an existing processor system. The four mounting holes accommodate either M2 (2 mm) or 2-56 machine screws. These boards are made of IS410 material and are 0.063 inches thick. The second level assembly uses a SAC305compatible solder composition, which has a presolder reflow thickness of approximately 0.005 inches.