## LM3668

# 1A, High Efficiency Dual Mode Single Inductor Buck-Boost DC/DC Converter

### **General Description**

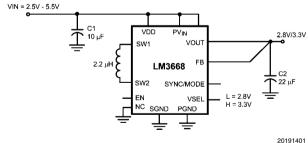

The LM3668 is a synchronous buck-boost DC-DC converter optimized for powering low voltage circuits from a Li-Ion battery and input voltage rails between 2.5V and 5.5V. It has the capability to support up to 1A output current over the output voltage range. The LM3668 regulates the output voltage over the complete input voltage range by automatically switching between buck or boost modes depending on the input voltage.

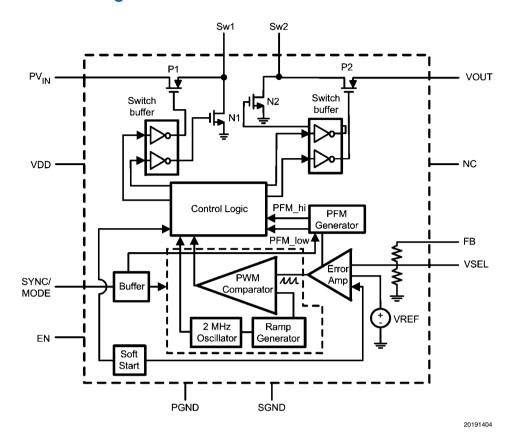

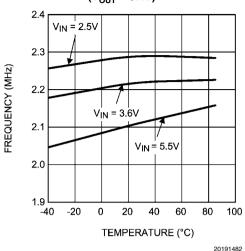

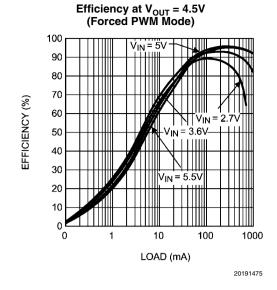

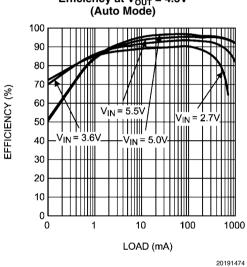

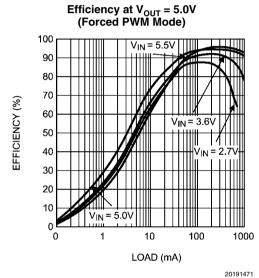

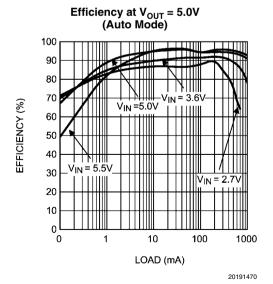

The LM3668 has 2 N-channel MOSFETS and 2 P-channel MOSFETS arranged in a topology that provides continuous operation through the buck and boost operating modes. There is a MODE pin that allows the user to choose between an intelligent automatic PFM-PWM mode operation and forced PWM operation. During PWM mode, a fixed-frequency 2.2MHz (typ.) is used. PWM mode drives load up to 1A. Hysteretic PFM mode extends the battery life through reduction of the quiescent current to 45 $\mu$ A (typ.) at light loads during system standby. Internal synchronous rectification provides high efficiency. In shutdown mode (Enable pin pulled low) the device turns off and reduces battery consumption to 0.01 $\mu$ A (typ.).

The LM3668 is available in a 12-pin LLP package. A high switching frequency of 2.2MHz (typ.) allows the use of tiny surface-mount components including a 2.2 $\mu$ H inductor, a 10 $\mu$ F input capacitor, and a 22 $\mu$ F output capacitor.

#### **Features**

- 45µA typical quiescent current

- For 2.8V/3.3V and 3.0/3.4V versions:

- 1A maximum load current for V<sub>IN</sub> = 2.8V to 5.5V

- 800mA maximum load current for V<sub>IN</sub> = 2.7V

- 600mA maximum load current for V<sub>IN</sub> = 2.5V

- For 4.5/5V

- 1A maximum load current for V<sub>IN</sub> = 3.9V to 5.5V

- 800mA maximum load current for V<sub>IN</sub> = 3.4V to 3.8V

- 700mA maximum load current for  $V_{IN} = 3.0V$  to 3.3V

- 600mA maximum load current for V<sub>IN</sub> = 2.7V to 2.9V

- 2.2MHz PWM fixed switching frequency (typ.)

- Automatic PFM-PWM Mode or Forced PWM Mode

- Wide Input Voltage Range: 2.5V to 5.5V

- Internal synchronous rectification for high efficiency

- Internal soft start: 600µs Maximum startup time after V<sub>IN</sub> settled

- 0.01µA typical shutdown current

- Current overload and Thermal shutdown protection

- Frequency Sync Pin: 1.6MHz to 2.7MHz

### **Applications**

- Handset Peripherals

- MP3 players

- Pre-Regulation for linear regulators

- PDAs

- Portable Hard Disk Drives

- WiMax Modems

## **Typical Applications**

**Typical Application Circuit**

1

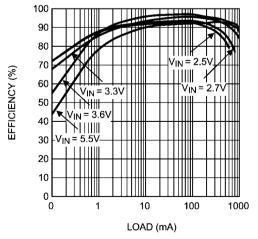

Efficiency at 3.3V Output

## **Functional Block Diagram**

FIGURE 1. Functional Block Diagram

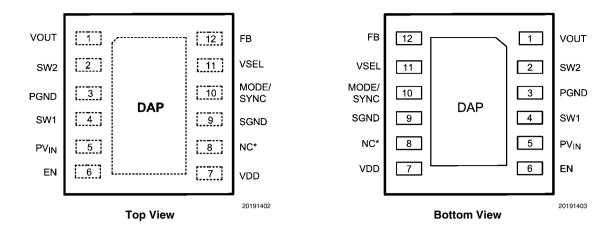

## **Connection Diagrams and Package Mark Information**

## **Pin Descriptions**

| Pin # | Pin Name         | Description                                                                                                                                                                   |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VOUT             | Connect to output capacitor.                                                                                                                                                  |

| 2     | SW2              | Switching Node connection to the internal PFET switch (P2) and NFET synchronous rectifier (N2).                                                                               |

| 3     | PGND             | Power Ground.                                                                                                                                                                 |

| 4     | SW1              | Switching Node connection to the internal PFET switch (P1) and NFET synchronous rectifier (N1).                                                                               |

| 5     | PV <sub>IN</sub> | Supply to the power switch, connect to the input capacitor.                                                                                                                   |

| 6     | EN               | Enable Input. Set this digital input high for normal operation. For shutdown, set low.                                                                                        |

| 7     | VDD              | Signal Supply input. If board layout is not optimum an optional 1µF ceramic capacitor is suggested as close to this pin as possible.                                          |

| 8     | NC               | No connect. Connect this pin to SGND on PCB layout.                                                                                                                           |

| 9     | SGND             | Analog and Control Ground.                                                                                                                                                    |

| 10    | MODE/SYNC        | Mode = LOW, Automatic Mode. Mode= HI, Forced PWM Mode SYNC = external clock synchronization from 1.6MHz to 2.7MHz (When SYNC function is used, device is forced in PWM mode). |

| 11    | VSEL             | Voltage selection pin; ( ie: 2.8V/3.3V option) Logic input low (or GND) = 2.8V and logic high = 3.3V (or $V_{IN}$ ) to set output Voltage.                                    |

| 12    | FB               | Feedback Analog Input. Connect to the output at the output filter.                                                                                                            |

| DAP   | DAP              | Die Attach Pad, connect the DAP to SGND on PCB layout to enhance thermal performance. It should not be used as a primary ground connection.                                   |

## **Ordering Information**

| Order Number     | Package | NSC Package<br>Marking | Supplied As               |  |

|------------------|---------|------------------------|---------------------------|--|

| LM3668SD - 2833  | LLP-12  | S017B                  | 1000 units, Tape and Reel |  |

| LM3668SDX - 2833 | LLP-12  | 30176                  | 4500 units, Tape and Reel |  |

| LM3668SD - 3034  | LLD 10  | C010D                  | 1000 units, Tape and Reel |  |

| LM3668SDX - 3034 | LLP-12  | S018B                  | 4500 units, Tape and Reel |  |

| LM3668SD - 4550  | LLD 10  | COLOR                  | 1000 units, Tape and Reel |  |

| LM3668SDX - 4550 | LLP-12  | S019B                  | 4500 units, Tape and Reel |  |

Note: As an example, if  $V_{OUT}$  option is 3.0V/3.4V, when  $V_{SEL}$  = Low, set  $V_{OUT}$  to 3V; when  $V_{SEL}$  = high, set  $V_{OUT}$  = 3.4V. This configuration applies to all voltage options.

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$PV_{IN,}V_{DD}$  Pin, SW1, SW2 &  $V_{OUT}$ : Voltage to SGND & PGND

-0.2V to +6.0V

FB. EN .MODE. SYNC pins:

(PGND & SGND-0.2V) to

$(PV_{IN} + 0.2)$

PGND to SGND Continuous Power Dissipation -0.2V to 0.2V Internally Limited

(Note 3)

Maximum Junction Temperature

$(T_{J-MAX})$

+125°C

Storage Temperature Range

Maximum Lead Temperature

(Soldering, 10 sec)

## **Operating Ratings**

Input Voltage Range 2.5V to 5.5V Recommended Load Current 0mA to 1A Junction Temperature ( $T_J$ ) Range  $-40^{\circ}$ C to  $+125^{\circ}$ C Ambient Temperature ( $T_A$ ) Range  $-40^{\circ}$ C to  $+85^{\circ}$ C

-65°C to +150°C

+260°C

(Note 3)

## **Thermal Properties**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ), 34°C/W Leadless Lead frame Package (*Note 5*)

**Electrical Characteristics** (*Note 6*, *Note 7*) Limits in standard typeface are for  $T_J = +25^{\circ}C$ . Limits in **boldface** type apply over the full operating ambient temperature range ( $-40^{\circ}C \le T_A \le +85^{\circ}C$ ). Unless otherwise noted, specifications apply to the LM3668.  $V_{IN} = 3.6V = EN$ ,  $V_{OLIT} = 3.3V$ . For  $V_{OLIT} = 4.5/5.0V$ ,  $V_{IN} = 4V$ .

| Symbol                      | Parameter                                   | Conditions                                                                         | Min | Тур  | Max  | Units |

|-----------------------------|---------------------------------------------|------------------------------------------------------------------------------------|-----|------|------|-------|

| $\overline{V_{FB}}$         | Feedback Voltage                            | (Note 7)                                                                           | -3  |      | 3    | %     |

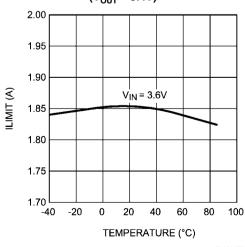

| I <sub>LIM</sub>            | Switch Peak Current Limit                   | Open loop(Note 2)                                                                  | 1.6 | 1.85 | 2.05 | Α     |

| I <sub>SHDN</sub>           | Shutdown Supply Current                     | EN =0V                                                                             |     | 0.01 | 1    | μΑ    |

| I <sub>Q_PFM</sub>          | DC Bias Current in PFM                      | No load, device is not switching (FB forced higher than programmed output voltage) |     | 45   | 60   | μΑ    |

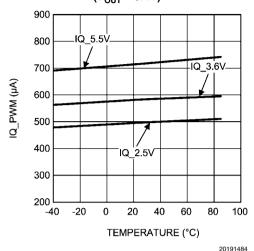

| I <sub>Q_PWM</sub>          | DC Bias Current in PWM                      | PWM Mode, No Switching                                                             |     | 600  | 750  | μΑ    |

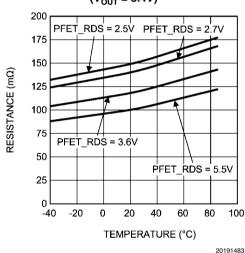

| R <sub>DSON(P)</sub>        | Pin-Pin Resistance for PFET                 | Switches P1 and P2                                                                 |     | 130  | 180  | mΩ    |

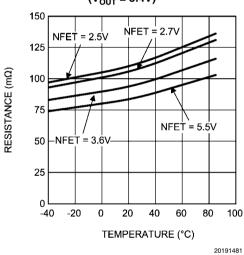

| R <sub>DSON(N)</sub>        | Pin-Pin Resistance for NFET                 | Switches N1 and N2                                                                 |     | 100  | 150  | mΩ    |

| Fosc                        | Internal Oscillator Frequency               | PWM Mode                                                                           | 1.9 | 2.2  | 2.5  | MHz   |

| F <sub>SYNC</sub>           | Sync Frequency Range                        | V <sub>IN</sub> = 3.6V                                                             | 1.6 |      | 2.7  | MHz   |

| V <sub>IH</sub>             | Logic High Input for EN, MODE/<br>SYNC pins |                                                                                    | 1.1 |      |      | V     |

| V <sub>IL</sub>             | Logic Low Input for EN, MODES/<br>SYNC pins |                                                                                    |     |      | 0.4  | V     |

| I <sub>EN, MODE, SYNC</sub> | EN, MODES/SYNC pins Input<br>Current        |                                                                                    |     | 0.3  | 1    | μΑ    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

**Note 2:** Electrical Characteristic table reflects open loop data (FB = 0V and current drawn from SW pin ramped up until cycle by cycle current limits is activated). Closed loop current limit is the peak inductor current measured in the application circuit by increasing output current until output voltage drops by 10%.

Note 3: In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 4: The Human body model is a 100pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin. MIL-STD-883 3015.7

Note 5: Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 101.6mm x 76.2mm x 1.6mm. Thickness of the copper layers are 2oz/1oz/1oz/2oz. The middle layer of the board is 60mm x 60mm. Ambient temperature in simulation is 22°C, still air.

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

Note 6: All voltage is with respect to SGND.

Note 7: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

Note 8: C<sub>IN</sub> and C<sub>OUT</sub>: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics. C<sub>OUT\_MIN</sub> should not exceed -40% of suggested value. The preferable choice would be a type and make MLCC that issues -30% over the operating temperature and voltage range.

#

# Supply Current vs. Temperature (Not switching) $(V_{OUT} = 3.4V)$

# NFET\_RDS (on) vs. Temperature (V<sub>OUT</sub> = 3.4V)

# ILIMIT vs. Temperature $(V_{OUT} = 3.4V)$

# Switching Frequency vs. Temperature $(V_{OUT} = 3.4V)$

# PFET\_RDS (on) vs. Temperature (V<sub>OUT</sub> = 3.4V)

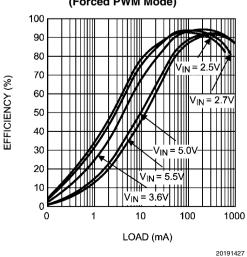

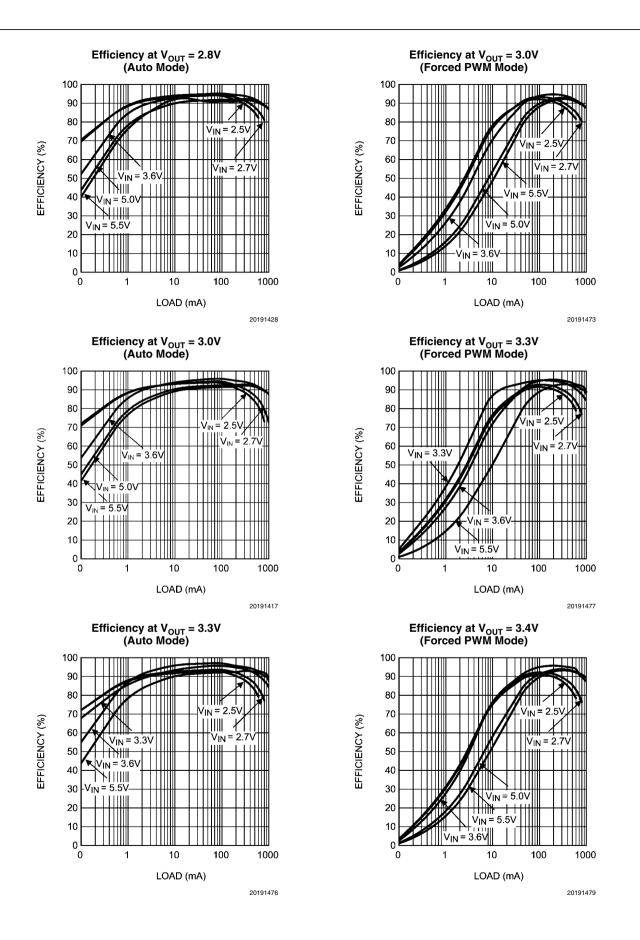

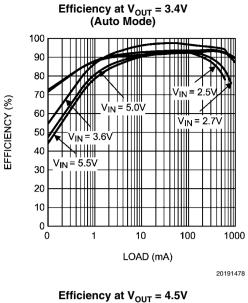

#### Efficiency at V<sub>OUT</sub> = 2.8V (Forced PWM Mode)

www.national.com

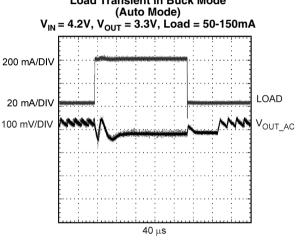

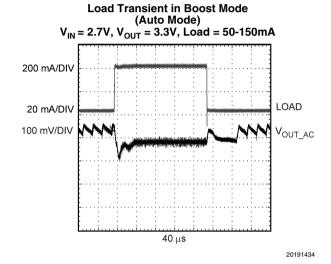

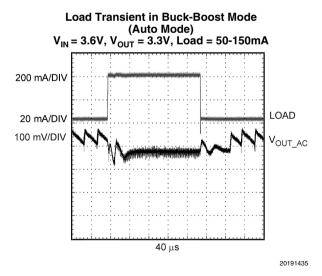

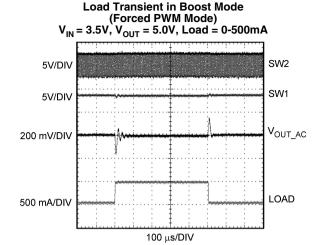

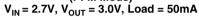

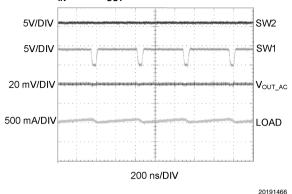

**Load Transient in Buck-Boost Mode**

20191436

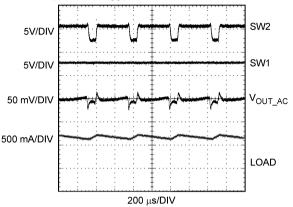

# Typical Switching Waveform in Boost Mode (PWM Mode)

$V_{IN} = 2.7V, V_{OUT} = 3.0V, Load = 500mA$

20191461

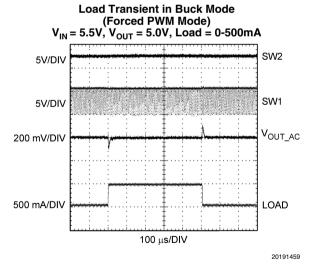

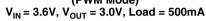

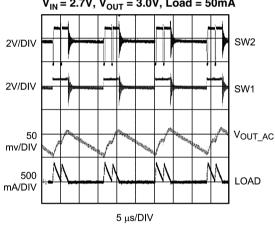

# Typical Switching Waveform in Buck Mode (PWM Mode)

20191460

20191462

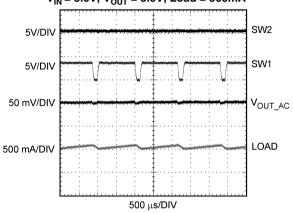

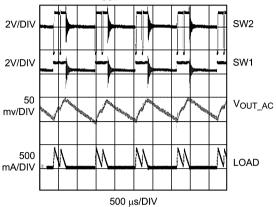

Typical Switching Waveformt in Boost Mode (PFM Mode)

20191463

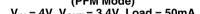

# Typical Switching Waveform in Buck Mode (PFM Mode)

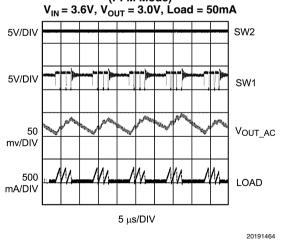

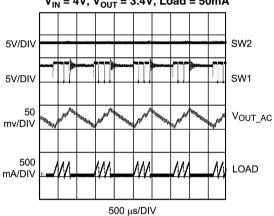

Typical Switching Waveform in Boost Mode (PWM Mode)

20191465

# Typical Switching Waveform in Buck Mode (PWM Mode) $V_{IN} = 4V, V_{OUT} = 3.4V, Load = 500mA$

# Typical Switching Waveform in Boost Mode (PFM Mode) $V_{\text{IN}} = 3V,\, V_{\text{OUT}} = 3.4V,\, \text{Load} = 50\text{mA}$

20191467

20191429

# Typical Switching Waveform in Buck Mode (PFM Mode) $V_{\text{IN}} = 4V,\,V_{\text{OUT}} = 3.4V,\,\text{Load} = 50\text{mA}$

20191468

# $(V_{OUT} = 3.4V, Load = 1mA)$ ΕN 2V/DIV $V_{OUT}$ 2V/DIV 500 mA/DIV

200 μs

Start up in PWM Mode

Start up in PWM Mode (V<sub>OUT</sub> = 3.4V, Load = 500mA) ΕN 2V/DIV  $V_{OUT}$ 2V/DIV 500 mA/DIV

200 μs

## **Circuit Description**

The LM3668, a high-efficiency Buck or Boost DC-DC converter, delivers a constant voltage from either a single Li-Ion or three cell NIMH/NiCd battery to portable devices such as mobile phones and PDAs. Using a voltage mode architecture with synchronous rectification, the LM3668 has the ability to deliver up to 1A depending on the input voltage, output voltage, ambient temperature and the chosen inductor.

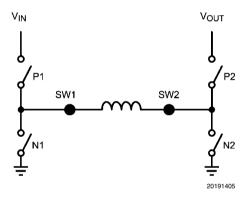

In addition, the device incorporates a seamless transition from buck-to-boost or boost-to-buck mode. The internal error amplifier continuously monitors the output to determine the transition from buck-to-boost or boost-to-buck operation. *Figure 2* shows the four switches network used for the buck and boost operation. Table 1 summarizes the state of the switches in different modes.

There are three modes of operation depending on the current required: PWM (Pulse Width Modulation), PFM (Pulse Frequency Modulation), and shutdown. The device operates in PWM mode at load currents of approximately 80mA or higher to improve efficiency. Lighter load current causes the device to automatically switch into PFM mode to reduce current consumption and extend battery life. Shutdown mode turns off the device, offering the lowest current consumption.

FIGURE 2. Simplified Diagram of Switches

**TABLE 1. State of Switches in Different Modes**

| Mode  | Always ON | Always<br>OFF | Switching  |

|-------|-----------|---------------|------------|

| Buck  | SW P2     | SW N2         | SW P1 & N1 |

| Boost | SW P1     | SW N1         | SW N2 & P2 |

#### **BUCK OPERATION**

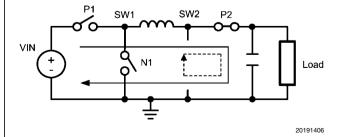

When the input voltage is greater than the output voltage, the device operates in buck mode where switch P2 is always ON and P1 & N1 control the output . Figure 3 shows the simplified circuit for buck mode operation.

FIGURE 3. Simplified Circuit for Buck Operation

#### **BOOST OPERATION**

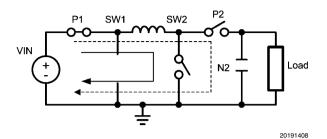

When the input voltage is smaller than the output voltage, the device enters boost mode operation where P1 is always ON, while switches N2 & P2 control the output. Figure 4 shows the simplified circuit for boost mode operation.

FIGURE 4. Simplified Circuit for Boost Operation

#### **PWM OPERATION**

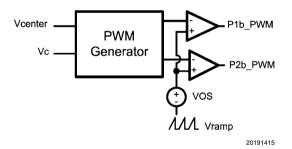

In PWM operation, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control power to the load. In Normal operation, the internal error amplifier provides an error signal, Vc, from the feedback voltage and Vref. The error amplifier signal, Vc, is compared with a voltage, Vcenter, and used to generate the PWM signals for both Buck & Boost modes. Signal Vcenter is a DC signal which sets the transition point of the buck and boost modes. Below are three regions of operation:

- Region I: If Vc is less than Vcenter, Buck mode.

- Region II: If Vc and Vcenter are equal, both PMOS switches (P1, P2) are on and both NMOS switches (N1, N2) are off. The power passes directly from input to output via P1 & P2

- Region III: If Vc is greater than Vcenter, Boost mode.

The Buck-Boost operation is avoided, to improve the efficiency across  $\rm V_{\rm IN}$  and load range.

FIGURE 5. PWM Generator Block Diagram

#### **INTERNAL SYNCHRONOUS RECTIFICATION**

While in PWM mode, the LM3668 uses an internal MOSFET as a synchronous rectifier to reduce rectifier forward voltage drop and associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relatively low compare to the voltage drop across an ordinary rectifier diode.

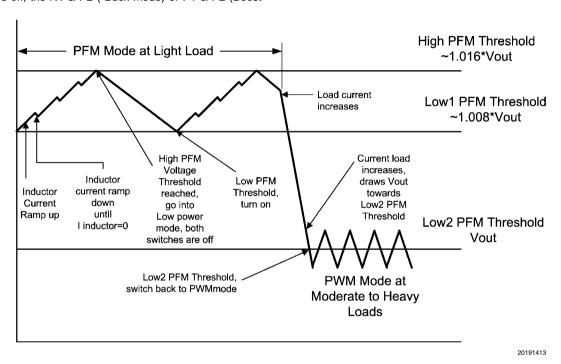

#### **PFM OPERATION**

At very light loads, the converter enters PFM mode and operates with reduced switching frequency and supply current to maintain high efficiency. The part automatically transitions into PFM mode when either of two following conditions occur for a duration of 128 or more clock cycles:

- A. The inductor current reaches zero.

- B. The peak inductor current drops below the  $I_{MODE}$  level, (Typically  $I_{MODF} < 45 mA + V_{IN}/80~\Omega$  ).

In PFM operation, the compensation circuit in the error amplifier is turned off. The error amplifier works as a hysteretic comparator. The PFM comparator senses the output voltage via the feedback pin and controls the switching of the output FETs such that the output voltage ramps between ~0.8% and ~1.6% of the nominal PWM output voltage (). If the output voltage is below the 'high' PFM comparator threshold, the P1 & P2 (Buck mode) or N2 & P1 (Boost mode) power switches are turned on. It remains on until the output voltage reaches the 'high' PFM threshold or the peak current exceeds the  $I_{\rm PFM}$  level set for PFM mode. The typical peak current in PFM mode is:  $I_{\rm PFM} = 220 \text{mA}$

Once the P1 (Buck mode) or N2 (Boost mode) power switch is turned off, the N1 & P2 (Buck mode) or P1 & P2 (Boost

mode) power switches are turned on until the inductor current ramps to zero. When the zero inductor current condition is detected, the N1( Buck mode) or P2 (Boost mode) power switches are turned off. If the output voltage is below the 'high' PFM comparator threshold, the P1 & P2 (Buck mode) or N2 & P1 (Boost mode) switches are again turned on and the cycle is repeated until the output reaches the desired level. Once the output reaches the 'high' PFM threshold, the N1 & P2 (Buck mode) or P1 & P2 (Boost mode) switches are turned on briefly to ramp the inductor current to zero, then both output switches are turned off and the part enters an extremely low power mode. Quiescent supply current during this 'sleep' mode is  $45\mu A$  (typ), which allows the part to achieve high efficiency under extremely light load conditions.

FIGURE 6. PFM to PWM Mode Transition

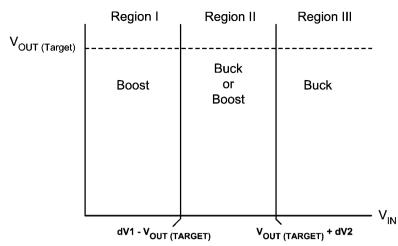

In addition to the auto mode transition, the LM3668 operates in PFM Buck or PFM Boost based on the following conditions. There is a small delta (~500mV) known as dv1(~200mV) & dv2(~300mV) when  $V_{OUT\_TARGET}$  is very close to  $V_{IN}$  where the LM3668 can be in either Buck or Boost mode. For example, when  $V_{OUT\_TARGET}=3.3V$  and  $V_{IN}$  is between 3.1V & 3.6V, the LM3668 can be in either mode depending on the  $V_{IN}$  vs  $V_{OUT\_TARGET}$ .

- Region I: If V<sub>IN</sub> < V<sub>OUT\_TARGET</sub> dv1, the regulator operates in Boost mode.

- Region II: If V<sub>OUT\_TARGET</sub> dv1 < V<sub>IN</sub> < V<sub>OUT\_TARGET</sub>+ dv2, the regulator operates in either Buck or Boost mode.

- Region III: If V<sub>IN</sub> > V<sub>OUT\_TARGET</sub> + dv2, the regulator operates in Buck mode.

FIGURE 7. V<sub>OUT</sub> vs V<sub>IN</sub> Transition

In the buck PFM operation, P2 is always turned on and N2 is always turned off , P1 and N1 power switches are switching. P1 and N1 are turned off to enter " sleep mode" when the output voltage reaches the "high" comparator threshold. In boost PFM operation, P2 and N2 are switching. P1 is turned on and N1 is turned off when the output voltage is below the "high" threshold. Unlike in buck mode, all four power switches are turned off to enter "sleep" mode when the output voltage reaches the "high" threshold in boost mode. In addition, the internal current sensing of the  $I_{\rm PFM}$  is used to determine the precise condition to switch over to buck or boost mode via the PFM generator.

#### **CURRENT LIMIT PROTECTION**

The LM3668 has current limit protection to prevent excessive stress on itself and external components during overload conditions. The internal current limit comparator will disable the power device at a typical switch peak current limit of 1.85A (typ.).

#### **UNDERVOLTAGE PROTECTION**

The LM3668 has an UVP comparator to turn the power device off in case the input voltage or battery voltage is too low . The typical UVP threshold is around 2V.

#### SHORT CIRCUIT PROTECTION

When the output of the LM3668 is shorted to GND, the current limit is reduced to about half of the typical current limit value until the short is removed.

#### **SHUTDOWN**

When the EN pin is pulled low, P1 and P2 are off; N1 and N2 are turned on to pull SW1 and SW2 to ground.

#### THERMAL SHUTDOWN

The LM3668 has an internal thermal shutdown function to protect the die from excessive temperatures. The thermal shutdown trip point is typically 150°C; normal operation resumes when the temperature drops below 125°C.

#### **STARTUP**

The LM3668 has a soft-start circuit that smooth the output voltage and ramp current during startup. During startup the bandgap reference is slowly ramped up and switch current limit is reduced to half the typical value. Soft start is activated only if EN goes from logic low to logic high after  $V_{\text{IN}}$  reaches

20191414

2.5V. The startup time thereby depends on the output capacitor and load current demanded at startup. It is not recommended to start up the device at full load while in soft-start.

### **Application Information**

#### SYNC/MODE PIN

If the SYNC/MODE pin is set high, the device is set to operate at PWM mode only. If SYNC/MODE pin is set low, the device is set to automatically transition from PFM to PWM or PWM to PFM depending on the load current. **Do not leave this pin floating**. The SYNC/MODE pin can also be driven by an external clock to set the desired switching frequency between 1.6MHz to 2.7MHz.

#### **V<sub>SEL</sub> PIN**

The LM3668 has built in logic for conveniently setting the output voltage, for example if  $\rm V_{\rm SEL}$  high, the output is set to 3.3V; with  $\rm V_{\rm SEL}$  low the output is set to 2.8V. It is not recommended to use this function for dynamically switching between 2.8V and 3.3V or switching at maximum load.

#### **MAXIMUM CURRENT**

The LM3668 is designed to operate up to 1A. For input voltages at 2.5V, the maximum operating current is 600mA and 800mA for 2.7V input voltage. In any mode it is recommended to avoid starting up the device at minimum input voltage and maximum load. Special attention must be taken to avoid operating near thermal shutdown when operating in boost mode at maximum load (1A). A simple calculation can be used to determine the power dissipation at the operating condition;  $P_{D\text{-MAX}} = (T_{J\text{-MAX}\text{-}OP} - T_{A\text{-MAX}})/\theta_{JA}.$  The LM3668 has thermal resistance  $\theta_{JA} = 34^{\circ}\text{C/W}$  ((Note 3) and (Note 6)), and maximum operating ambient of 85°C. As a result, the maximum power dissipation using the above formula is around 1176mW. Refer to dissipation table below for  $P_{D\text{-MAX}}$  value at different ambient temperatures.

#### **Dissipation Rating Table**

| $\theta_{JA}$                                        | T <sub>A</sub> ≤ 25°C | T <sub>A</sub> ≤ 60°C | T <sub>A</sub> ≤ 85°C |

|------------------------------------------------------|-----------------------|-----------------------|-----------------------|

| 34°C/W ( 4<br>layers board<br>per JEDEC<br>standard) | 2941mW                | 1912mW                | 1176mW                |

#### **INDUCTOR SELECTION**

There are two main considerations when choosing an inductor: the inductor should not saturate, and the inductor current ripple should be small enough to achieve the desired output voltage ripple. Different saturation current rating specifications are followed by different manufacturers so attention must be given to details. Saturation current ratings are typically specified at 25°C. However, ratings at the maximum ambient temperature of application should be requested from the manufacturer. Shielded inductors radiate less noise and should be preferred.

In the case of the LM3668, there are two modes (Buck & Boost) of operation that must be consider when selecting an inductor with appropriate saturation current. The saturation current should be greater than the sum of the maximum load current and the worst case average to peak inductor current. The first equation shows the buck mode operation for worst case conditions and the second equation for boost condition.

$$\begin{split} I_{SAT} &> I_{OUTMAX} + I_{RIPPLE} & \text{For Buck} \\ Where \ I_{RIPPLE} &= \frac{(V_{IN} - V_{OUT})}{(2 \times L \times f)} \times \frac{V_{OUT}}{V_{IN}} \\ I_{SAT} &> \frac{I_{OUTMAX}}{D'} + I_{RIPPLE} & \text{For Boost} \\ Where \ I_{RIPPLE} &= \frac{(V_{OUT} - V_{IN})}{(2 \times L \times f)} \times \frac{V_{IN}}{V_{OUT}} \\ Where \ D &= \frac{(V_{OUT} - V_{IN})}{(V_{OUT})} & \& \ D' = (1-D) \end{split}$$

- I<sub>RIPPLE</sub>: Peak inductor current

- I<sub>OUTMAX</sub>: Maximum load current

- V<sub>IN</sub>: Maximum input voltage in application

- L: Min inductor value including worst case tolerances (30% drop can be considered)

- f: Minimum switching frequency

- $\bullet \quad {\rm V_{OUT}}{:} \ {\rm Output} \ {\rm voltage}$

- D: Duty Cycle for CCM Operation

- V<sub>OUT</sub>: Output Voltage

- V<sub>IN</sub>: Input Voltage

#### **Example using above equations:**

- V<sub>IN</sub> = 2.8V to 4V

- V<sub>OUT</sub> = 3.3V

- I<sub>OUT</sub> = 500mA

- $L = 2.2 \mu H$

- F = 2MHz

- Buck: I<sub>SAT</sub> = 567mA

- Boost: I<sub>SAT</sub> = 638mA

As a result, the inductor should be selected according to the highest of the two  $I_{\text{SAT}}$  values.

A more conservative and recommended approach is to choose an inductor that has a saturation current rating greater than the maximum current limit of 2.05A.

A 2.2 $\mu$ H inductor with a saturation current rating of at least 2.05A is recommended for most applications. The inductor's resistance should be less than 100m $\Omega$  for good efficiency. For low-cost applications, an unshielded bobbin inductor could be

considered. For noise critical applications, a toroidal or shield-ed-bobbin inductor should be used. A good practice is to lay out the board with overlapping footprints of both types for design flexibility. This allows substitution of a low-noise shielded inductor, in the event that noise from low-cost bobbin model is unacceptable.

**TABLE 2. Suggest Inductors and Suppliers**

| Model     | Vendor    | Dimension    | D.C.R          | I <sub>SAT</sub> |

|-----------|-----------|--------------|----------------|------------------|

|           |           | s            | (max)          |                  |

|           |           | LxWxH        |                |                  |

|           |           | (mm)         |                |                  |

| LPS4012-  | Coilcraft | 4 x 4 x 1.2  | 100 m $\Omega$ | 2.1A             |

| 222L      |           |              |                |                  |

| LPS4018-  | Coilcraft | 4 x 4 x 1.8  | 70~mΩ          | 2.5A             |

| 222L      |           |              |                |                  |

| 1098AS-2  | TOKO      | 3 x 2.8x 1.2 | 67 mΩ          | 1.8A             |

| R0M (2µF) |           |              |                | ( lower          |

|           |           |              |                | current          |

|           |           |              |                | application      |

|           |           |              |                | s)               |

#### INPUT CAPACITOR SELECTION

A ceramic input capacitor of at least  $10\mu F$ , 6.3V is sufficient for most applications. Place the input capacitor as close as possible to the  $PV_{IN}$  pin of the device. A larger value may be used for improved input voltage filtering. Use X7R or X5R types; do not use Y5V. DC bias characteristics of ceramic capacitors must be considered when selecting case sizes like 0805 or 0603. The input filter capacitor supplies current to the PFET switch of the LM3668 in the first half of each cycle and reduces voltage ripple imposed on the input power source. A ceramic capacitor's low ESR provides the best noise filtering of the input voltage spikes due to this rapidly changing current. For applications where input voltage is 4V or higher, it is best to use a higher voltage rating capacitor to eliminate the DC bias affect over capacitance.

#### **OUTPUT CAPACITOR SELECTION**

A ceramic output capacitor of  $22\mu\text{F}$ , 6.3V (use 10V or higher rating for 4.5/5V output option) is sufficient for most applications. Multilayer ceramic capacitors such as X5R or X7R with low ESR is a good choice for this as well. These capacitors provide an ideal balance between small size, cost, reliability and performance. Do not use Y5V ceramic capacitors as they have poor dielectric performance over temperature and poor voltage characteristic for a given value. In other words, ensure the minimum  $C_{\text{OUT}}$  value does not exceed -40% of the above-suggested value over the entire range of operating temperature and bias conditions.

Extra attention is required if a smaller case size capacitor is used in the application. Smaller case size capacitors typically have less capacitance for a given bias voltage as compared to a larger case size capacitor with the same bias voltage. Please contact the capacitor manufacturer for detail information regarding capacitance verses case size. Table 1 lists several capacitor suppliers.

The output filter capacitor smooths out current flow from the inductor to the load, helps maintain a steady output voltage during transient load changes and reduces output voltage ripple. These capacitors must be selected with sufficient capacitance and sufficiently low ESR to perform these functions.

Note that the output voltage ripple is dependent on the inductor current ripple and the equivalent series resistance of the output capacitor ( $R_{\text{ESR}}$ ).

The  $R_{\rm ESR}$  is frequency dependent (as well as temperature dependent); make sure the value used for calculations is at the switching frequency of the part.

**TABLE 3. Suggested Capacitors and Suppliers**

| Model                                                                              | Туре                                                                              | Vendor       | Voltage Rating | Case Size<br>Inch (mm) |  |  |  |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------|----------------|------------------------|--|--|--|

| 10 μF for C <sub>IN</sub> (For 4.5/5V op                                           | 10 μF for C <sub>IN</sub> (For 4.5/5V option, use 10V or higher rating capacitor) |              |                |                        |  |  |  |

| GRM21BR60J106K                                                                     | Ceramic, X5R                                                                      | Murata       | 6.3V           | 0805 (2012)            |  |  |  |

| JMK212BJ106K                                                                       | Ceramic, X5R                                                                      | Taiyo-Yuden  | 6.3V           | 0805 (2012)            |  |  |  |

| C2012X5R0J106K                                                                     | Ceramic, X5R                                                                      | TDK          | 6.3V           | 0805 (2012)            |  |  |  |

| LMK212 BJ106MG (+/-20%)                                                            | Ceramic, X5R                                                                      | Taiyon-Yuden | 10V            | 0806(2012)             |  |  |  |

| LMK212 BJ106KG (+/-10%)                                                            | Ceramic, X5R                                                                      | Taiyon-Yuden | 10V            | 0805(2012)             |  |  |  |

| 22 μF for C <sub>OUT</sub> (For 4.5/5V option, use 10V or higher rating capacitor) |                                                                                   |              |                |                        |  |  |  |

| JMK212BJ226MG                                                                      | Ceramic, X5R                                                                      | Taiyo-Yuden  | 6.3V           | 0805(2012)             |  |  |  |

| LMK212BJ226MG                                                                      | Ceramic, X5R                                                                      | Taiyo-Yuden  | 10V            | 0805(2012)             |  |  |  |

#### **LAYOUT CONSIDERATIONS**

As for any high frequency switcher, it is important to place the external components as close as possible to the IC to maximize device performance. Below are some layout recommendations:

- 1) Place input filter and output filter capacitors close to the IC to minimize copper trace resistance which will directly effect the overall ripple voltage.

- 2) Route noise sensitive trace away from noisy power components. Separate power GND (Noisy GND) and Signal GND

(quiet GND) and star GND them at a single point on the PCB preferably close to the device GND pin.

3) Connect the ground pins and filter capacitors together via a ground plane to prevent switching current circulating through the ground plane. Additional layout consideration regarding the LLP package can be found in Application AN1187.

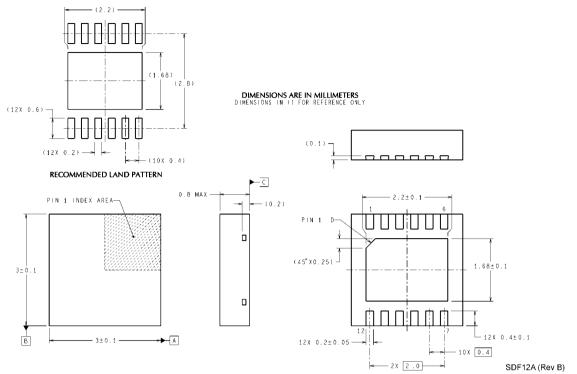

## Physical Dimensions inches (millimeters) unless otherwise noted

12-Pin LLP NS Package Number SDF12A

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com