## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

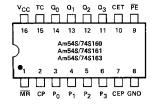

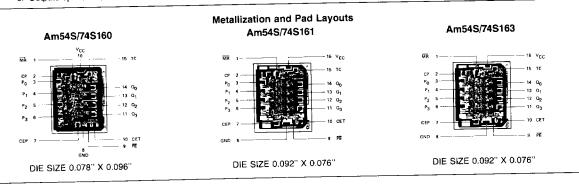

# Am54S/74S160 • Am54S/74S161 • Am54S/74S163

**BCD Decade/Four-Bit Binary Counters**

### **Distinctive Characteristics**

- Fully synchronous counting

- Fully synchronous parallel loading

- Edge-triggered clock action

- Advanced Schottky technology

- 100% MIL-STD-883 reliability assurance test

### **FUNCTIONAL DESCRIPTION**

The Am54S/74S160 is a fully synchronous 4-bit decimal counter. The Am54S/74S161 and Am54S/74S163 are fully synchronous 4-bit binary counters. With the parallel enable ( $\overline{PE}$ ) LOW, data on the P $_0$ -P $_3$  inputs is parallel loaded on the positive clock transition. When  $\overline{PE}$  is HIGH and both count enables CEP and CET are also HIGH, counting will occur on the LOW-to-HIGH clock transition.

The terminal count state (1001 for the Am54S/74S160 and 1111 for both the Am54S/74S161 and Am54S/74S163) is decoded and ANDed with CET in the terminal count (TC) output. If CET is HIGH and the counter is in its terminal count state, then TC is HIGH.

Both the Am54S/74S160 and Am54S/74S161 have an asynchronous master reset  $(\overline{MR})$ . A LOW on the  $\overline{MR}$  input forces the Q outputs LOW independent of all other inputs.

The Am54S/74S163 has a synchronous master reset ( $\overline{\text{MR}}$ ). A LOW on the  $\overline{\text{MR}}$  input forces the Q outputs LOW after the next clock pulse independent of all other inputs. The only requirements on the  $\overline{\text{PE}}$ , CEP, CET and P<sub>0</sub>-P<sub>3</sub> inputs is that they meet the set-up time requirements before the clock LOW-to-HIGH transition.

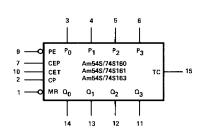

#### LOGIC SYMBOL

$V_{CC} = Pin 16$ GND = Pin 8

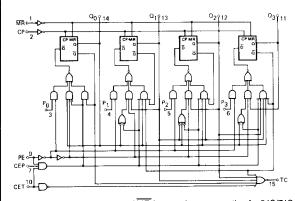

#### Am54S/74S160

#### LOGIC DIAGRAMS

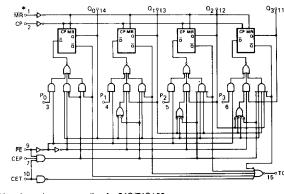

#### Am54S/74S161/S163

\*MR is asynchronous on the Am54S/74S161 and synchronous on the Am54S/74S163

## ORDERING INFORMATION

| Package<br>Type   | Temperature<br>Range | Am54S/<br>74S160<br>Order<br>Number | Am54S/<br>74S161<br>Order<br>Number | Am54S/<br>74S163<br>Order<br>Number |

|-------------------|----------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Molded DIP        | 0 to +75°C           | SN74S160N                           | SN74S161N                           | SN74S163N                           |

| Hermetic DIP      | 0 to +75°C           | SN74S160J                           | SN74S161J                           | SN74S163J                           |

| Dice              | 0 to +75°C           | SN74S160X                           | SN74S161X                           | SN74S163X                           |

| Hermetic DIP      | -55 to +125°C        | SN54S160J                           | SN54S161J                           | SN54S163J                           |

| Hermetic Flat Pak | -55 to +125°C        | SN54S160W                           | SN54S161W                           | SN54S163W                           |

| Dice              | -55 to +125°C        | SN54S160X                           | SN54S161X                           | SN54S163X                           |

## CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

| AXIMOM RATINGS (Above which the desire has a                  |                                |

|---------------------------------------------------------------|--------------------------------|

| T                                                             | _65°C to +150°C                |

| orage Temperature                                             | -55°C to +125°C                |

| mperature (Ambient) Under Bias                                |                                |

| pply Voltage to Ground Potential (Pin 16 to Pin 8) Continuous | -0.5V to +7V                   |

| 2 Voltage Applied to Outputs for HIGH Output State            | -0.5V to +V <sub>CC</sub> max. |

|                                                               | -0.5V to +5.5V                 |

| Comput Voltage                                                | 30mA                           |

| COutput Current, Into Outputs                                 |                                |

| C Input Current                                               | -30mA to +5.0mA                |

# ELECTRICAL CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (Unless Otherwise Noted)

$T_A = 0 \text{ to } +75^{\circ}\text{C}$ 4m74S160X, Am74S161X, Am74S163  $T_A = -55 \text{ to } + 125^{\circ}\text{C}$ Am54S160X, Am54S161X, Am54S163

$V_{CC} = 5.0V \pm 5\% \text{ (COM'L)}$  $V_{CC}^{-2} = 5.0V \pm 10\% (MIL)$

MIN = 4.75VM1N = 4.5V

MAX = 5.25VMAX = 5.5V

| arameters       | Description                                   | Test Conditions                                                   | (Note 1)                      |      | Min          | Typ<br>(Note 2) | Max  | Units |

|-----------------|-----------------------------------------------|-------------------------------------------------------------------|-------------------------------|------|--------------|-----------------|------|-------|

|                 | <u> </u>                                      | $V_{CC} = MIN, I_{OH} = -1mA$                                     | MIL                           |      | 2.5          | 3.4             |      | Volts |

| V <sub>OH</sub> | Output HIGH Voltage                           | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> COM'L        |                               | ∕l'L | 2.7          | 3.4             |      |       |

| V <sub>OL</sub> | Output LOW Voltage                            | $V_{CC} = MIN$ , $I_{OL} = 20mA$<br>$V_{IN} = V_{IH}$ or $V_{IL}$ |                               |      |              | 0.35            | 0.5  | Volts |

| V <sub>IH</sub> | Input HIGH Level                              | Guaranteed input logical HI voltage for all inputs                | GH                            |      | 2.0          |                 |      | Volts |

| V <sub>IL</sub> | Input LOW Level                               | Guaranteed input logical LOW voltage for all inputs               |                               |      |              |                 | 0.8  | Volts |

| V <sub>I</sub>  | Input Clamp Voltage                           | $V_{CC}$ = MIN, $I_{IN}$ = $-18$ mA                               |                               |      |              |                 | -1.2 | Volts |

|                 |                                               |                                                                   | P; MR; CE                     | Р    |              |                 | -2.0 |       |

| i <sub>n_</sub> |                                               | $V_{IN} = 0.5V$                                                   | CET                           |      |              |                 | -3.0 | mA    |

| (Note 3)        | Input LOW Current                             |                                                                   | PE                            |      |              |                 | -4.0 |       |

|                 |                                               |                                                                   | СР                            |      |              |                 | -5.0 |       |

|                 |                                               |                                                                   | P; MR; CE                     | Р    |              |                 | 50   |       |

| l <sub>iH</sub> |                                               | $V_{CC} = MAX,$                                                   | CET                           |      |              |                 | 75   | μΑ    |

| (Note 3)        | Input HIGH Current                            | $V_{IN} = 2.7V$                                                   | PE                            |      |              |                 | 100  |       |

|                 |                                               |                                                                   | СР                            |      |              |                 | 125  |       |

| <u> </u>        | Input HIGH Current                            | $V_{CC} = MAX, V_{IN} = 5.5V$                                     | = MAX, V <sub>IN</sub> = 5.5V |      |              |                 | 1.0  | mA    |

| l <sub>SC</sub> | Output Short Circuit Current (Note 4)         | V <sub>CC</sub> = MAX                                             |                               |      | - <b>4</b> 0 | -65             | -100 | mA    |

|                 | Power Supply Current<br>Am54S/74S160/161 only | V <sub>CC</sub> = MAX (Note 5)                                    |                               |      |              | 82              | 127  | mA    |

| lcc             | Am54S/74S163 only                             | V <sub>CC</sub> = MAX (Note 6)                                    |                               |      |              | 96              | 150  | mA    |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical limits are at  $V_{CC} = 5.0V$ , 25°C ambient and maximum loading.

- 3. Actual input currents = Unit Load Current x Input Load Factor (See Loading Rules).

- 4. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

- 5. Outputs open;  $\overline{MR} = 0V$ ; all other inputs HIGH.

- 6. Outputs open;  $\overline{MR}$ , CP, CET = HIGH; all other inputs LOW.

### **DEFINITION OF FUNCTIONAL TERMS**

PE Parallel Enable. When PE is LOW, the parallel inputs, P<sub>0</sub> through P<sub>3</sub>, are enabled. When PE is

HIGH, the count function is possible.

CEP Count Enable Parallel. CEP is one of the count enable inputs that must be HIGH for the counter

to count.

CET Count Enable Trickle. CET is one of the count enable inputs that must be HIGH for the counter

to count. In addition, CET is included in the TC output gate and must be HIGH for TC to be

HIGH.

Clock Pulse. Causes the required output change on the LOW-to-HIGH transition (Edge-

triggered).

Master Reset (Am54S/74S160/S161). When the asynchronous master reset is LOW, the  $Q_0$  through  $Q_3$  outputs will be LOW regardless of

the other inputs.

MR Master Reset (Am54S/74S163). When the synchronous master reset is LOW the Q<sub>0</sub> through Q<sub>3</sub> outputs will be LOW following the next clock

pulse regardless of the other inputs.

P<sub>0</sub>, P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub> The parallel data inputs for the four internal flipflops.

Q<sub>0</sub>, Q<sub>1</sub>, Q<sub>2</sub>, Q<sub>3</sub> The four parallel outputs from the counter.

TC

CP

MR

Terminal Count. The terminal count output will be HIGH for CET HIGH and binary nine on the Am54S/74S160 or CET HIGH and binary 15 on the Am54S/74S161.

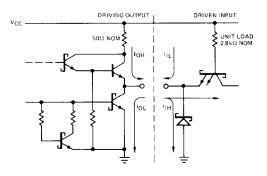

## **LOADING RULES (In Unit Loads)**

|                       |           |                    | Fan            | -out          |

|-----------------------|-----------|--------------------|----------------|---------------|

| Input/Output          | Pin No.'s | Input<br>Unit Load | Output<br>HIGH | Output<br>LOW |

| MR                    | 1         | 1                  | -              | _             |

| СР                    | 2         | 2.5                | -              | _             |

| PO                    | 3         | 1                  | _              | -             |

| P <sub>1</sub>        | 4         | 1                  | _              | _             |

| P <sub>2</sub>        | 5         | 1                  | _              | _             |

| P <sub>3</sub>        | 6         | 1                  | _              | _             |

| CEP                   | 7         | 1                  | _              |               |

| GND                   | 8         | _                  |                |               |

| PE                    | 9         | 2                  | _              | -             |

| CET                   | 10        | 1.5                | _              | _             |

| <b>Q</b> <sub>3</sub> | 11        | _                  | 20             | 10            |

| <b>a</b> <sub>2</sub> | 12        |                    | 20             | 10            |

| Q <sub>1</sub>        | 13        |                    | 20             | 10            |

| <b>a</b> <sub>0</sub> | 14        | _                  | 20             | 10            |

| тс                    | 15        | -                  | 20             | 10            |

| v <sub>cc</sub>       | 16        | -                  | _              | -             |

|                       |           |                    |                |               |

A Schottky TTL Unit Load is defined as  $50\mu A$  measured at 2.7V HIGH and -2.0 mA measured at 0.5V LOW.

### **FUNCTION TABLE**

| DEVICE TYPE            | INPUTS |    |    |     |     |                |                | OUTPUTS        |                |    |                |                |                |

|------------------------|--------|----|----|-----|-----|----------------|----------------|----------------|----------------|----|----------------|----------------|----------------|

|                        | СР     | MR | PE | CEP | ÇET | Po             | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> | Qo | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> |

| Am54S/74S160/S161      | Х      | L  | х  | х   | x   | х              | х              | х              | х              | L  | L              | L              | L              |

| Am54S/74S163           | 1      | L  | Х  | х   | ×   | Х              | х              | х              | ×              | L  | L              | L              | L              |

| Am54S/74S160/S161/S163 | t      | Н  | L  | х   | х   | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | Do | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> |

|                        | 1      | н  | н  | L   | L   | х              | х              | x              | х              | NC | NC             | NC             | NC             |

|                        | 1      | н  | н  | L   | н   | Х              | х              | х              | х              | NC | NC             | NC             | NC             |

|                        | 1      | Н  | Н  | Н   | L   | х              | х              | Х              | x              | NÇ | NC             | NC.            | NC             |

|                        | t      | н  | н  | Н   | н   | Х              | X              | х              | ×              |    | co             | UNT            |                |

H = HIGH

X = Don't Care

L = LOW

NC = No Change

D<sub>i</sub> may be either HIGH or LOW ↑ LOW-to-HIGH Transition

## **TERMINAL COUNT (TC) TRUTH TABLE**

|     | S160           |    | А  | тс |     |       |    |    |    |   |

|-----|----------------|----|----|----|-----|-------|----|----|----|---|

| CET | $\mathbf{q}_0$ | 01 | 02 | 03 | CET | $o_0$ | Ω1 | 02 | Ο3 |   |

| Н   | н              | L  | L  | н  | н   | н     | н  | Н  | н  | H |

| L   | х              | ×  | ×  | ×  | L   | ×     | ×  | ×  | ×  | Ł |

| x   | L              | ×  | ×  | ×  | ×   | L     | ×  | ×  | х  | L |

| ×   | x              | н  | ×  | x  | ×   | х     | L  | ×  | х  | L |

| ×   | х              | x  | н  | x  | ×   | х     | ×  | L  | х  | L |

| ×   | х              | х  | ×  | L  | ×   | ×     | ×  | ×  | L  | L |

H = HIGH L = LOW X = Don't Care

# SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

## SWITCHING CHARACTERISTICS (T<sub>A</sub> = +25°)

| arameters        | Description                                                        | Test Conditions   | Min | Тур | Max | Units     |

|------------------|--------------------------------------------------------------------|-------------------|-----|-----|-----|-----------|

| f <sub>MAX</sub> | Count Frequency                                                    |                   | 70  | 100 |     | MHz       |

| t <sub>PLH</sub> |                                                                    |                   |     | 6   | 9   | l<br>⊣ ns |

| tPHL             | Clock to Q                                                         |                   |     | 8.5 | 13  |           |

| t <sub>PLH</sub> | 0                                                                  |                   |     | 12  | 18  | ns ns     |

| tPHL             | Clock to TC                                                        |                   |     | 8   | 12  |           |

| t <sub>PLH</sub> |                                                                    |                   |     | 6.5 | 10  | ns        |

| tPHL             | CET to TC                                                          |                   |     | 6.5 | 10  |           |

| t <sub>PHL</sub> | MR to Q (Am54S/74S160/161 only)                                    |                   |     | 14  | 20  | ns        |

| t <sub>s</sub>   | Recovery Time for MR (inactive) Am54S/74S160 and Am54S/74S161 only |                   |     |     |     | ns        |

| t <sub>pw</sub>  | Master Reset Pulse Width                                           | $R_L = 280\Omega$ | 13  |     |     | ns        |

| -                | Clock Pulse Width HIGH                                             |                   | 6   |     |     | ns        |

| t <sub>pw</sub>  | Clock Pulse Width LOW                                              |                   | 10  |     |     |           |

| t <sub>s</sub>   |                                                                    |                   | 8   |     |     | ns        |

| t <sub>h</sub>   | Data to Clock                                                      |                   | 0   |     |     |           |

| ts               | = 0.1                                                              |                   | 16  |     |     | - ns      |

| th               | PE to Clock                                                        |                   | 0   |     |     |           |

| t <sub>s</sub>   |                                                                    | 7                 | 12  |     |     | ns        |

| th               | CEP or CET to Clock                                                |                   | 0   |     |     |           |

| t <sub>s</sub>   | MR to Clock                                                        |                   | 14  |     |     | ns        |

| th               | Am54S/74S163 only                                                  |                   | 0   |     |     | ,13       |