July 2014

# FL7733 Primary-Side-Regulated LED Driver with Power Factor Correction

### Features

### **High Performance**

- Cost-Effective Solution without Requiring Input Bulk Capacitor and Secondary Feedback Circuitry

- Power Factor Correction

- THD <10% Over Universal Line Range</p>

- Constant Current Tolerance:

- < ±1% Over Universal Line Voltage Variation

- < ±1% by 50% 100% Load Voltage Variation

- < ±1% by ±20% Magnetizing Inductance Variation

- High-Voltage Startup with V<sub>DD</sub> Regulation

- Adaptive Feedback Loop Control for Startup without Overshoot

### **High Reliability**

- LED Short / Open Protection

- Output Diode Short Protection

- Sensing Resistor Short / Open Protection

- V<sub>DD</sub> Over-Voltage Protection (OVP)

- V<sub>DD</sub> Under-Voltage Lockout (UVLO)

- Over-Temperature Protection (OTP)

- All Protections are Auto Restart (AR)

- Cycle-by-Cycle Current Limit

- Application Input Voltage Range: 80 V<sub>AC</sub> 308 V<sub>AC</sub>

# Applications

LED Lighting System

### Description

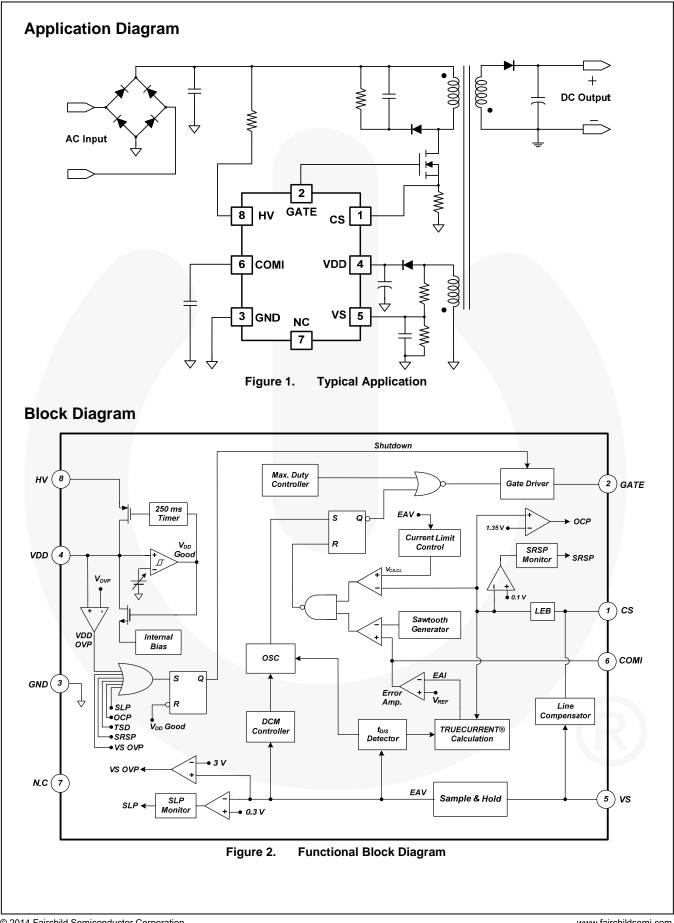

This highly integrated PWM controller with advanced Primary-Side Regulation (PSR) technique provides features to enhance the performance of low-to-mid-power LED lighting converter. The FL7733 LED driver is designed with minimum system components while LED current is accurately controlled by Fairchild's TRUECURRENT<sup>®</sup> technique and improved feedback loop control. Constant Current (CC) tolerance less than  $\pm 1\%$  over the universal line voltage range meets the requirement of highly reliable LED brightness management.

By minimizing turn-on time fluctuation, high power factor, and low THD; <10% THD over the universal line range can be obtained. An integrated high-voltage startup circuit implements fast startup and high system efficiency. During startup, adaptive feedback loop control anticipates the steady-state condition and sets initial feedback condition close to the steady state to ensure no overshoot or undershoot of LED current.

The FL7733 provides powerful protections, such as LED short / open, output diode short, sensing resistor short / open, and over-temperature for high system reliability.

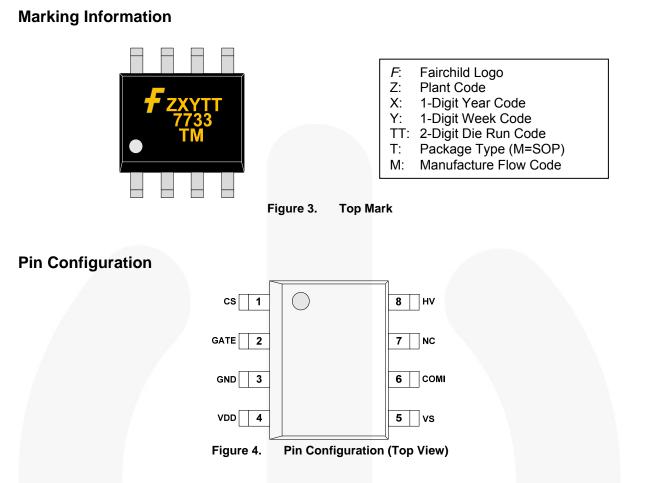

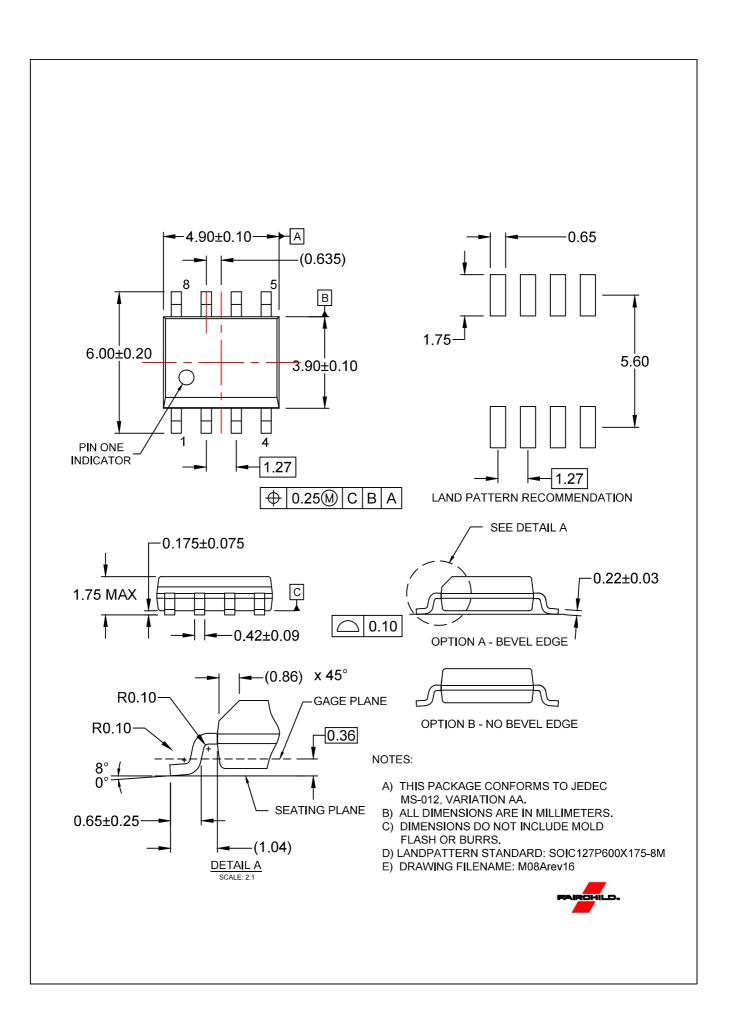

The FL7733 controller is available in an 8-pin Small-Outline Package (SOP).

# **Related Resources**

<u>AN-5076 — Design High Power Factor Flyback Converter</u> <u>using FL7733 for LED Driver with Ultra-Wide Output</u> <u>Voltage</u>

AN-FEBFL7733\_L50U008A — User Guide for FEBFL7733\_L50U008A\_Evaluation\_Board\_of\_8.4 W\_LED Driver (PFC PSR Flyback)

AN-FEBFL7733 L52U050A — User Guide for FEBFL7733 L52U050A Evaluation Board of 50 W LED Driver (PFC PSR Flyback)

| Ordering Information |                                         |                 |                                       |                |  |

|----------------------|-----------------------------------------|-----------------|---------------------------------------|----------------|--|

|                      | Part Number Operating Temperature Range |                 | Package                               | Packing Method |  |

|                      | FL7733MX                                | -40°C to +125°C | 8-Lead, Small Outline Package (SOP-8) | Tape & Reel    |  |

# **Pin Descriptions**

| Pin #                                                                                                                                     | Name                                                                                                             | Description                                                                                                                                                                                            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                                                                                                                         | CS                                                                                                               | <b>Current Sense</b> . This pin connects a current-sense resistor to detect the MOSFET current for constant output current regulation.                                                                 |  |

| 2                                                                                                                                         | 2 GATE <b>PWM Signal Output</b> . This pin uses the internal totem-pole output driver to drive the power MOSFET. |                                                                                                                                                                                                        |  |

| 3                                                                                                                                         | GND                                                                                                              | Ground                                                                                                                                                                                                 |  |

| 4                                                                                                                                         | VDD                                                                                                              | Power Supply. IC operating current and MOSFET driving current are supplied using this pin.                                                                                                             |  |

| 5                                                                                                                                         | VS                                                                                                               | <b>Voltage Sense</b> . This pin detects the output voltage and discharge time information for CC regulation. This pin is connected to the auxiliary winding of the transformer via a resistor divider. |  |

| 6 COMI Constant Current Loop Compensation. This pin is connected to a capacitor between C and GND for compensating the current loop gain. |                                                                                                                  | <b>Constant Current Loop Compensation</b> . This pin is connected to a capacitor between COMI and GND for compensating the current loop gain.                                                          |  |

| 7                                                                                                                                         | NC                                                                                                               | No Connect                                                                                                                                                                                             |  |

| 8                                                                                                                                         | HV                                                                                                               | High Voltage. This pin is connected to the rectified input voltage via a resistor.                                                                                                                     |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameter                                 |      | Max. | Unit |

|-------------------|-------------------------------------------|------|------|------|

| HV                | HV Pin Voltage                            |      | 700  | V    |

| V <sub>VDD</sub>  | DC Supply Voltage <sup>(1,2)</sup>        |      | 30   | V    |

| $V_{VS}$          | VS Pin Input Voltage                      | -0.3 | 6.0  | V    |

| V <sub>CS</sub>   | CS Pin Input Voltage                      | -0.3 | 6.0  | V    |

| V <sub>COMI</sub> | COMI Pin Input Voltage                    | -0.3 | 6.0  | V    |

| $V_{\text{GATE}}$ | GATE Pin Input Voltage                    | -0.3 | 30.0 | V    |

| PD                | Power Dissipation (T <sub>A</sub> < 50°C) |      | 633  | mW   |

| TJ                | Maximum Junction Temperature              |      | 150  | °C   |

| T <sub>STG</sub>  | Storage Temperature Range                 | -55  | 150  | °C   |

| TL                | Lead Temperature (Soldering) 10 Seconds   |      | 260  | °C   |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

2. All voltage values, except differential voltages, are given with respect to GND pin.

# Thermal Impedance

T<sub>A</sub>=25°C, unless otherwise specified

| Symbol                                             | Parameter                                             | Value | Unit |  |

|----------------------------------------------------|-------------------------------------------------------|-------|------|--|

| θ <sub>JA</sub>                                    | θ <sub>JA</sub> Junction-to-Ambient Thermal Impedance |       | °C/W |  |

| θ <sub>JC</sub> Junction-to-Case Thermal Impedance |                                                       | 39    | °C/W |  |

Note:

3. Referenced the JEDEC recommended environment, JESD51-2, and test board, JESD51-3, 1S1P with minimum land pattern.

# **ESD** Capability

| Symbol | mbol Parameter                                |   | Unit |

|--------|-----------------------------------------------|---|------|

| FOD    | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 | 4 |      |

| ESD    | Charged Device Model, JESD22-C101             | 2 | kV   |

### Note:

4. Meets JEDEC standards JESD22-A114 and JESD 22-C101.

# **Electrical Characteristics**

$V_{DD}$ =15 V,  $T_{J}$ =-40 to +125°C, unless otherwise specified. Currents are defined as positive into the device and negative out of device.

| Symbol                    | Parameter                                         | Conditions                                                                                      | Min. | Тур. | Max. | Unit |

|---------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DD-ON</sub>        | Turn-On Threshold Voltage                         |                                                                                                 | 14.5 | 16.0 | 17.5 | V    |

| $V_{\text{DD-OFF}}$       | Turn-Off Threshold Voltage                        |                                                                                                 | 6.75 | 7.75 | 8.75 | V    |

| I <sub>DD-OP</sub>        | Operating Current                                 | C <sub>L</sub> =1 nF, f=f <sub>MAX-CC</sub>                                                     | 3    | 4    | 5    | mA   |

| I <sub>DD-ST</sub>        | Startup Current                                   | V <sub>DD</sub> =V <sub>DD-ON</sub> -1.6 V                                                      |      | 30   | 50   | μA   |

| $V_{\text{VDD-OVP}}$      | V <sub>DD</sub> Over-Voltage Protection Level     |                                                                                                 | 23   | 24   | 25   | V    |

| GATE SECTIC               | N I I I I I I I I I I I I I I I I I I I           |                                                                                                 |      |      | •    | •    |

| V <sub>OL</sub>           | Output Voltage Low                                | $T_A=25^{\circ}C, V_{DD}=20 V,$<br>$I_{DD_GATE}=1 mA$                                           |      |      | 1.5  | V    |

| V <sub>он</sub>           | Output Voltage High                               | $T_A=25^{\circ}C$ , $V_{DD}=10 V$ ,<br>$I_{DD}=1 mA$                                            | 5    |      |      | V    |

| ISOURCE                   | Peak Sourcing Current <sup>(5)</sup>              | V <sub>DD</sub> =10 ~ 20 V                                                                      |      | -60  |      | mA   |

| I <sub>SINK</sub>         | Peak Sinking Current <sup>(5)</sup>               | V <sub>DD</sub> =10 ~ 20 V                                                                      |      | 180  |      | mA   |

| t <sub>R</sub>            | Rising Time                                       | $T_A=25^{\circ}C, V_{DD}=15 V,$<br>$C_{LOAD}=1 nF$                                              | 100  | 150  | 200  | ns   |

| t <sub>F</sub>            | Falling Time                                      | $T_A=25^{\circ}C$ , $V_{DD}=15 V$ , $C_{LOAD}=1 nF$                                             | 20   | 60   | 100  | ns   |

| V <sub>CLAMP</sub>        | Output Clamp Voltage                              | V <sub>DD</sub> =20 V, V <sub>CS</sub> =0 V,<br>V <sub>VS</sub> =0 V, V <sub>COM</sub> =0 V     | 12   | 15   | 18   | v    |

| HV STARTUP                | SECTION                                           |                                                                                                 |      |      | •    |      |

| I <sub>HV</sub>           | Supply Current From HV Pin                        | $ \begin{array}{c} T_{A} = 25^{\circ}C, \ V_{IN} = 90 \ V_{AC}, \\ V_{DD} = 0 \ V \end{array} $ |      |      | 9    | mA   |

| I <sub>HV-LC</sub>        | Leakage Current after Startup                     |                                                                                                 |      | 1    | 10   | μA   |

| t <sub>R-JFET</sub>       | JFET Regulation Time after Startup <sup>(5)</sup> | T <sub>A</sub> =25°C                                                                            | 190  | 250  | 310  | ms   |

| V <sub>JFET-HL</sub>      | JFET Regulation High Limit Voltage                |                                                                                                 | 17.5 | 19.0 | 20.5 | V    |

| V <sub>JFET-LL</sub>      | JFET Regulation Low Limit Voltage                 |                                                                                                 | 11.5 | 13.0 | 14.5 | V    |

| CURRENT-ER                | ROR-AMPLIFIER SECTION                             |                                                                                                 |      |      |      |      |

| 9м                        | Transconductance <sup>(5)</sup>                   | T <sub>A</sub> =25°C                                                                            | 11   | 17   | 23   | µmho |

| I <sub>COMI-SINK</sub>    | COMI Sink Current                                 | $\begin{array}{l} T_{A} = 25^{\circ}C, \ V_{EAI} = 2.55 \ V, \\ V_{COMI} = 5 \ V \end{array}$   | 12   | 18   | 24   | μA   |

| ICOMI-SOURCE              | COMI Source Current                               | Т <sub>A</sub> =25°С, V <sub>EAI</sub> =0.45 V,<br>V <sub>COMI</sub> =0 V                       | 12   | 18   | 24   | μΑ   |

| V <sub>COMI-HGH</sub>     | COMI High Voltage                                 | V <sub>EAI</sub> =0 V                                                                           | 4.7  |      |      | V    |

| V <sub>COMI-LOW</sub>     | COMI Low Voltage                                  | V <sub>EAI</sub> =5 V                                                                           |      |      | 0.1  | V    |

| V <sub>COMI_INT.CLP</sub> | Initial COMI Clamping Voltage <sup>(5)</sup>      |                                                                                                 |      | 1.2  |      | V    |

| t <sub>COMI_INT.CLP</sub> | Time for Initial COMI Clamping <sup>(5)</sup>     |                                                                                                 |      | 15   |      | ms   |

Continued on the following page...

# FL7733 — Primary-Side-Regulated LED Driver with Power Factor Correction

# Electrical Characteristics (Continued)

$V_{DD}$ =15 V,  $T_{J}$ =-40 to +125°C, unless otherwise specified. Currents are defined as positive into the device and negative out of device.

| Symbol Parameter Conditions       |                                                                                 | Min.                                                             | Тур.  | Max.  | Uni   |     |

|-----------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|-------|-------|-------|-----|

| VOLTAGE-SEI                       | NSE SECTION                                                                     |                                                                  |       |       |       |     |

| V <sub>VS-MAX-CC</sub>            | V <sub>S</sub> for Maximum Frequency in CC                                      | f=f <sub>MAX-CC</sub> -2 kHz                                     | 2.25  | 2.35  | 2.45  | V   |

| V <sub>VS-MIN-CC</sub>            | V <sub>S</sub> for Minimum Frequency in CC                                      | f=f <sub>MIN-CC</sub> +2 kHz                                     | 0.55  | 0.85  | 1.15  | V   |

| t <sub>DIS-BNK</sub>              | t <sub>DIS</sub> Blanking Time of V <sub>S</sub> <sup>(5)</sup>                 |                                                                  | 0.85  | 1.15  | 1.45  | μs  |

| I <sub>VS-BNK</sub>               | V <sub>S</sub> Current for VS Blanking                                          |                                                                  | -75   | -90   | -105  | μA  |

| V <sub>VS-OVP</sub>               | V <sub>S</sub> Level for Output Over-Voltage<br>Protection                      |                                                                  | 2.95  | 3.00  | 3.15  | V   |

| Vvs-low-cl-en                     | $V_{\text{S}}$ Threshold Voltage to Enable Low Current Limit^{(5)}              |                                                                  | 0.25  | 0.30  | 0.35  | V   |

| V <sub>VS-HIGH-CL-DIS</sub>       | V <sub>S</sub> Threshold Voltage to Disable<br>Low Current Limit <sup>(5)</sup> |                                                                  | 0.54  | 0.60  | 0.66  | V   |

| Vvs-slp-th                        | V <sub>S</sub> Threshold Voltage for Output<br>Short-LED Protection             |                                                                  | 0.25  | 0.30  | 0.35  | V   |

| t <sub>SLP-BNK</sub>              | V <sub>S</sub> Detection Disable Time after Startup <sup>(5)</sup>              | T <sub>A</sub> =25°C                                             |       | 15    |       | ms  |

| CURRENT-SE                        | NSE SECTION                                                                     |                                                                  |       |       |       |     |

| V <sub>RV</sub>                   | Reference Voltage                                                               | T <sub>A</sub> =25°C                                             | 1.485 | 1.500 | 1.515 | V   |

| t <sub>LEB</sub>                  | Leading-Edge Blanking Time <sup>(5)</sup>                                       |                                                                  |       | 300   |       | ns  |

| t <sub>MIN</sub>                  | Minimum On Time in CC <sup>(5)</sup>                                            | V <sub>COMI</sub> =0 V                                           |       | 500   |       | ns  |

| t <sub>PD</sub>                   | Propagation Delay to GATE Output                                                |                                                                  | 50    | 100   | 150   | ns  |

| V <sub>CS-HIGH-CL</sub>           | High Current Limit Threshold                                                    |                                                                  | 0.9   | 1.0   | 1.1   | V   |

| V <sub>CS-LOW-CL</sub>            | Low Current Limit Threshold                                                     |                                                                  | 0.16  | 0.20  | 0.24  | V   |

| t <sub>LOW-CM</sub>               | Low Current Mode Operation Time at Startup <sup>(5)</sup>                       |                                                                  |       | 20    |       | ms  |

| V <sub>CS-SRSP</sub>              | V <sub>CS</sub> Threshold Voltage for Sensing Resistor Short Protection         |                                                                  |       |       | 0.1   | V   |

| V <sub>CS-OCP</sub>               | V <sub>CS</sub> Threshold Voltage for Over-<br>Current Protection               | T <sub>A</sub> =25°C                                             | 1.20  | 1.35  | 1.50  | V   |

| V <sub>CS</sub> / I <sub>VS</sub> | Relation of Line Compensation Voltage and $V_S$ Current <sup>(5)</sup>          |                                                                  |       | 21.5  |       | V/A |

| OSCILLATOR                        | SECTION                                                                         |                                                                  |       |       | - 6   |     |

| f <sub>MAX-CC</sub>               | Maximum Frequency in CC                                                         | T <sub>A</sub> =25°C, V <sub>DD</sub> =10 V, 20 V                | 60    | 65    | 70    | kHz |

| f <sub>MIN-CC</sub>               | Minimum Frequency in CC                                                         | $T_A$ =25°C, $V_{DD}$ =10 V, 20 V                                | 21.0  | 23.5  | 26.0  | kHz |

| t <sub>ON-MAX</sub>               | Maximum Turn-On Time                                                            | Maximum Turn-On Time T <sub>A</sub> =25°C, f=f <sub>MAX-CC</sub> |       | 13.0  | 15.6  | μs  |

| OVER-TEMPE                        | RATURE-PROTECTION SECTION                                                       |                                                                  |       |       |       |     |

| T <sub>OTP</sub>                  | Threshold Temperature for OTP <sup>(5)</sup>                                    |                                                                  |       | 150   |       | °C  |

| T <sub>OTP-HYS</sub>              | Restart Junction Temperature<br>Hysteresis <sup>(5)</sup>                       |                                                                  |       | 10    |       | °C  |

5. These parameters, although guaranteed by design, are not production tested.

### **Functional Description**

FL7733 is AC-DC PWM controller for LED lighting applications. TRUECURRENT<sup>®</sup> techniques regulate accurate constant LED current; independent of input voltage, output voltage, and magnetizing inductance variations. The DCM control in the oscillator reduces conduction loss and maintains DCM operation over a wide range of output voltage, which implements high power factor correction in a single-stage flyback or buck-boost topology. A variety of protections, such as LED short / open protection, sensing resistor short / open protection, over-temperature protection, and cycle-by-cycle current limitation stabilize system operation and protect external components.

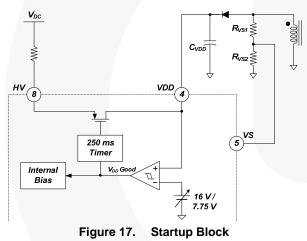

### Startup

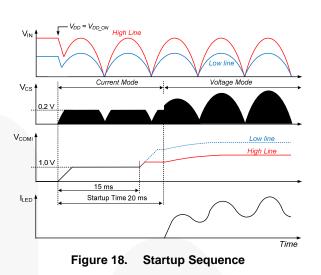

At startup, an internal high-voltage JFET supplies startup current and V<sub>DD</sub> capacitor charging current, as shown in Figure 17. When V<sub>DD</sub> reaches 16 V, switching begins and the internal high-voltage JFET continues to supply V<sub>DD</sub> operating current for an initial 250 ms to maintain V<sub>DD</sub> voltage higher than V<sub>DD-OFF</sub>. As the output voltage increases, the auxiliary winding becomes the dominant V<sub>DD</sub> supply current source.

Switching is controlled by current-mode for 20 ms after  $V_{DD-ON}$ . During current-mode switching with the flyback or buck-boost topology, output current is only determined by output voltage. Therefore, the output voltage increases with constant slope, regardless of line voltage variation. Short-LED Protection (SLP) is enabled after the 15 ms SLP blanking time so that the output voltage is higher than SLP threshold voltage and successful startup is guaranteed without SLP in normal condition.

During current-mode switching, COMI voltage, which determines turn-on time in voltage mode, is adjusted close to the steady state level by sensing peak line voltage. The COMI capacitor is charged to 1.2 V for 15 ms and adjusted to a modulated level inversely proportional to  $V_{\rm IN}$  peak value for 5 ms. Turn-on time right after 20 ms startup time can be controlled close to steady state on time so that voltage mode is smoothly entered without LED current overshoot or undershoot.

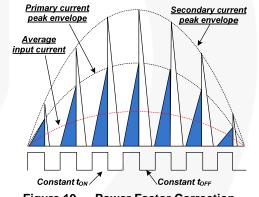

### **PFC and THD**

In the flyback or the buck-boost topology, constant turnon time and constant frequency in Discontinuous Conduction Mode (DCM) operation can achieve high PF and low THD, as shown in Figure 19. Constant turn-on time is maintained by the internal error amplifier and a large external COMI capacitor (typically over 1  $\mu$ F) at COMI pin. Constant frequency and DCM operation are managed by DCM control.

Figure 19. Power Factor Correction

### **Constant-Current Regulation**

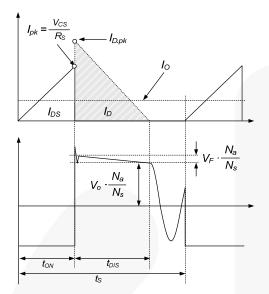

The output current can be estimated using the peak drain current and inductor current discharge time because output current is the same as the average of the diode current in steady state. The peak value of the drain current is determined by the CS peak voltage detector. The inductor current discharge time ( $t_{DIS}$ ) is sensed by a  $t_{DIS}$  detector. With peak drain current, inductor current discharging time and operating switching period information, the TRUECURRENT® calculation block estimates output current as follows:

$$I_{o} = \frac{1}{2} \cdot \frac{t_{DIS}}{t_{s}} \cdot V_{CS} \cdot n_{PS} \cdot \frac{1}{R_{s}}$$

$$\frac{t_{DIS}}{t_{s}} \cdot V_{CS} = 0.25$$

$$I_{o} = 0.125 \cdot \frac{n_{PS}}{R_{s}}$$

(1)

where,  $n_{PS}$  is the primary-to-secondary turn ratio and  $R_S$  is a sensing resistor connected between the source terminal of the MOSFET and ground.

Figure 20. Key Waveforms for Primary-Side Regulation

The output of the current calculation is compared with an internal precise voltage reference to generate an error voltage ( $V_{COMI}$ ), which determines the MOSFET's turn-on time in voltage-mode control. With Fairchild's innovative TRUECURRENT® technique, constant-current output can be precisely controlled.

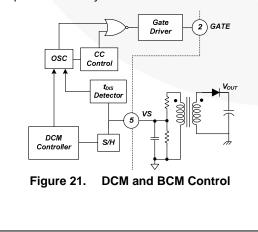

### DCM Control

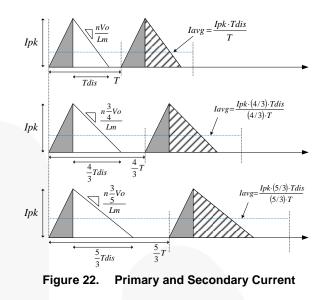

As mentioned above, DCM should be guaranteed for high power factor in flyback topology. To maintain DCM across a wide range of output voltage, the switching frequency is linearly adjusted by the output voltage in linear frequency control. Output voltage is detected by the auxiliary winding and the resistive divider connected to the VS pin, as shown in Figure 21. When the output voltage decreases, secondary diode conduction time is increased and the DCM control lengthens the switching period, which retains DCM operation over the wide output voltage range, as shown in Figure 22. The frequency control lowers the primary rms current with better power efficiency in full-load condition.

### **BCM** Control

The end of secondary diode conduction time could possibly be behind the end of a switching period set by DCM control. In this case, the next switching cycle starts at the end of secondary diode conduction time since FL7733 doesn't allow CCM. Consequently, the operation mode changes from DCM to BCM.

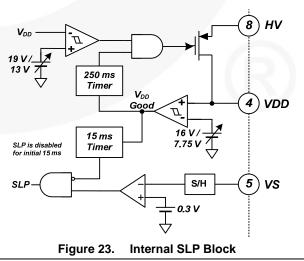

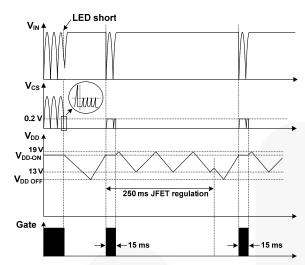

### Short-LED Protection (SLP)

In case of a short-LED condition, the secondary diode is stressed by high current. When  $V_S$  voltage is lower than 0.3 V due to a short-LED condition, the cycle-by-cycle current limit level changes to 0.2 V from 1.0 V and SLP is triggered if the  $V_S$  voltage is less than 0.3 V for four (4) consecutive switching cycles. Figure 23 and Figure 24 show the SLP block and operational waveforms during LED-short condition. To set enough auto-restart time for system safety under protection conditions,  $V_{DD}$  is maintained between 13 V and 19 V, which is higher than UVLO, for 250 ms after  $V_{DD-ON}$ . SLP is disabled for an initial 15 ms to ensure successful startup in normal LED condition.

Figure 24. Waveforms in Short-LED Condition

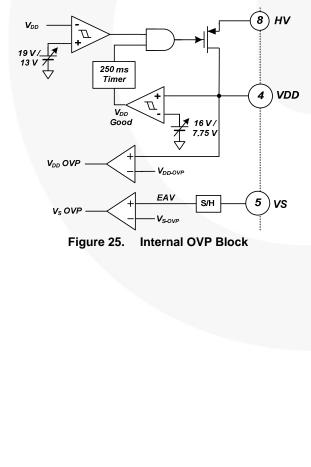

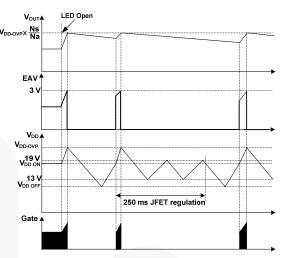

### **Open-LED Protection**

FL7733 protects external components, such as output diodes and output capacitors, during open-LED condition. During switch turn-off, the auxiliary winding voltage is applied as the reflected output voltage. Because the  $V_{DD}$  and  $V_S$  voltages have output voltage information through the auxiliary winding, the internal voltage comparators in the VDD and VS pins can trigger output Over-Voltage Protection (OVP), as shown in Figure 25 and Figure 26.

Figure 26. Waveforms in LED Open Condition

### Sensing Resistor Short Protection (SRSP)

In a sensing resistor short condition, the V<sub>CS</sub> level is almost zero and pulse-by-pulse current limit or OCP is not effective. The FL7733 is designed to provide sensing resistor short protection for both current and voltage mode operation. If the V<sub>CS</sub> level is less than 0.1 V in the first switching cycle, the GATE output is stopped by current-mode SRSP. After 20 ms startup time, the GATE is shut down by the voltage-mode SRSP if V<sub>CS</sub> level is less than 0.1 V at over 60% level of peak V<sub>IN</sub>.

### **Under-Voltage Lockout (UVLO)**

The V<sub>DD</sub> turn-on and turn-off thresholds are fixed internally at 16 V and 7.75 V, respectively. During startup, the V<sub>DD</sub> capacitor must be charged to 16 V through the high-voltage JFET to enable the FL7733. The V<sub>DD</sub> capacitor continues to supply V<sub>DD</sub> until auxiliary power is delivered from the auxiliary winding of the main transformer. V<sub>DD</sub> should remain higher than 7.75 V during this startup process. Therefore, the V<sub>DD</sub> capacitor must be adequate to keep V<sub>DD</sub> over the UVLO threshold until the auxiliary winding voltage is above 7.75 V.

# **Over-Current Protection (OCP)**

When an output diode or secondary winding are shorted, switch current with extremely high di/dt can flow through the MOSFET even by minimum turn-on time. The FL7733 is designed to protect the system against this excessive current. When the CS voltage across the sensing resistor is higher than 1.35 V, the OCP comparator output shuts down GATE switching.

In a sensing resistor open condition, the sensing resistor voltage can't be detected and output current is not regulated properly. If the sensing resistor is damaged open-circuit, the parasitic capacitor in the CS pin is charged by internal CS current sources. Therefore, the  $V_{CS}$  level is built up to the OCP threshold voltage and then switching is shut down immediately.

### **Over-Temperature Protection (OTP)**

The temperature-sensing circuit shuts down PWM output if the junction temperature exceeds 150°C. The hysteresis temperature after OTP triggering is 10°C.

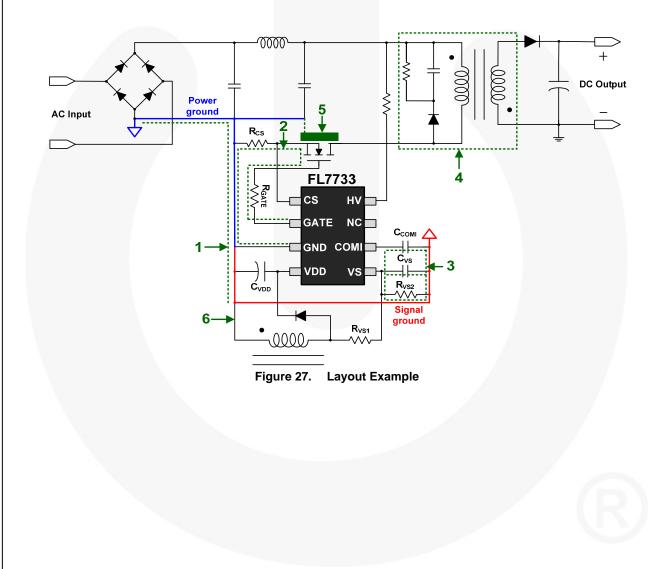

## **PCB Layout Guidance**

PCB layout for a power converter is as important as circuit design because PCB layout with high parasitic inductance or resistance can lead to severe switching noise with system instability. PCB should be designed to minimize switching noise into control signals.

- 1. The signal ground and power ground should be separated and connected only at one position (GND pin) to avoid ground loop noise. The power ground path from the bridge diode to the sensing resistors should be short and wide.

- 2. Gate-driving current path (GATE  $R_{GATE}$  MOSFET  $R_{CS}$  GND) must be as short as possible.

- Control pin components; such as C<sub>COMI</sub>, C<sub>VS</sub>, and R<sub>VS2</sub>; should be placed close to the assigned pin and signal ground.

- High-voltage traces related to the drain of MOSFET and RCD snubber should be kept far way from control circuits to avoid unnecessary interference.

- 5. If a heat sink is used for the MOSFET, connect this heat sink to power ground.

- 6. The auxiliary winding ground should be connected closer to the GND pin than the control pin components' ground.

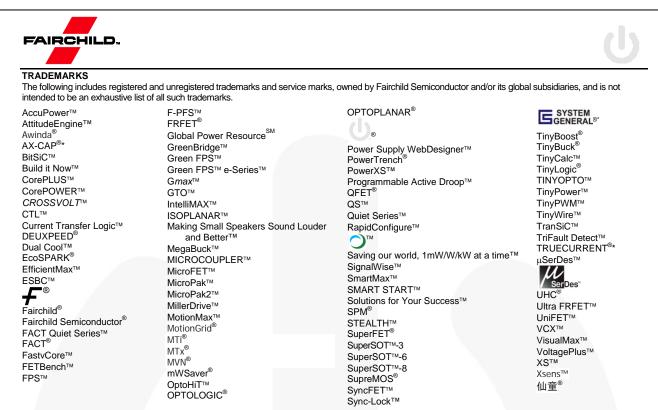

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR WEBSITE AT <u>HTTP://WWW.FAIRCHILDSEMI.COM</u>, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

### AUTHORIZED USE

Unless otherwise specified in this data sheet, this product is a standard commercial product and is not intended for use in applications that require extraordinary levels of quality and reliability. This product may not be used in the following applications, unless specifically approved in writing by a Fairchild officer: (1) automotive or other transportation, (2) military/aerospace, (3) any safety critical application – including life critical medical equipment – where the failure of the Fairchild product reasonably would be expected to result in personal injury, death or property damage. Customer's use of this product is subject to agreement of this Authorized Use policy. In the event of an unauthorized use of Fairchild's product, Fairchild accepts no liability in the event of product failure. In other respects, this product shall be subject to Fairchild's Worldwide Terms and Conditions of Sale, unless a separate agreement has been signed by both Parties.

### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Terms of Use

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

### **PRODUCT STATUS DEFINITIONS**

| Definition of Terms          | Definition of Terms |                                                                                                                                                                                                     |  |  |  |  |

|------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Datasheet Identification     | Product Status      | Definition                                                                                                                                                                                          |  |  |  |  |

| Preliminary First Production |                     | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |  |  |

|                              |                     | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |  |

|                              |                     | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |  |  |

| Obsolete                     | Not In Production   | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                 |  |  |  |  |

Rev. 177