# **TUSB5152**

**USB to 2-Serial + 1-Parallel Controller With Configurable Optional Hub**

# Data Manual

Designing with this device may require extensive support. Before incorporating this device into a design, customers should contact TI or an Authorized TI Distributor.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated

# **Contents**

| Section |        |             | Title                                               |      |  |  |  |

|---------|--------|-------------|-----------------------------------------------------|------|--|--|--|

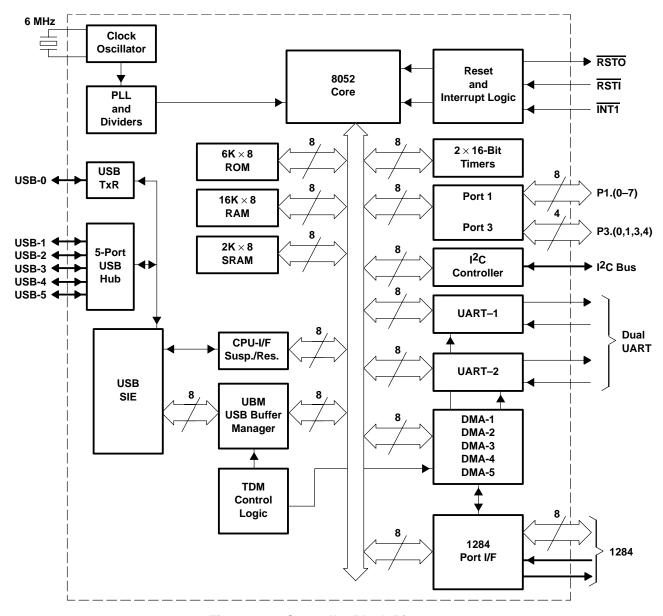

| 1       | Contr  | oller Des   | cription                                            | 1–1  |  |  |  |

| 2       | Main I | Features    |                                                     | 2–1  |  |  |  |

|         | 2.1    | General     | Features                                            | 2–1  |  |  |  |

|         | 2.2    | Enhance     | ed UART Features                                    | 2–1  |  |  |  |

|         | 2.3    |             | 84 Port                                             |      |  |  |  |

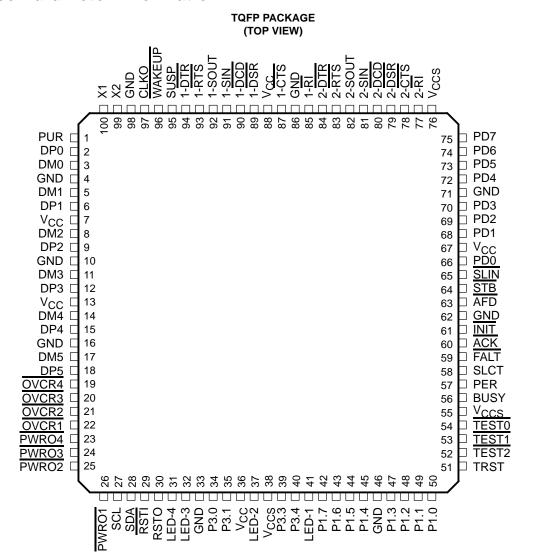

| 3       | Devic  | e Parame    | eter Information                                    | 3–1  |  |  |  |

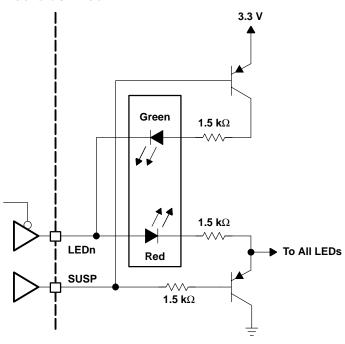

|         | 3.1    | Hub-Por     | ts LED Status Definition                            | 3–4  |  |  |  |

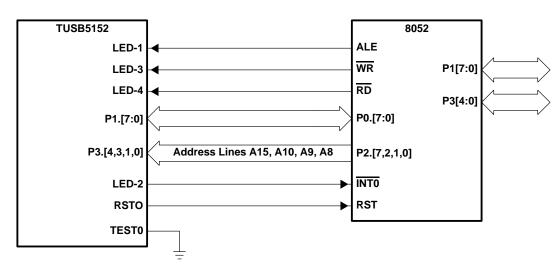

|         | 3.2    | Connect     | ing an External Microcontroller for Development     | 3–5  |  |  |  |

|         | 3.3    | Setting the | he TRST and TEST[2:0] Pins for Various Applications | 3–6  |  |  |  |

|         | 3.4    | Pin State   | e in Suspend Mode                                   | 3–6  |  |  |  |

|         | 3.5    |             | ming                                                |      |  |  |  |

| 4       | MCU    | Memory N    | Map (Internal Operation)                            | 4–1  |  |  |  |

|         | 4.1    | Miscellar   | neous Registers                                     | 4–2  |  |  |  |

|         |        | 4.1.1       | ROMS: ROM Shadow Configuration Register             | 4–2  |  |  |  |

|         |        | 4.1.2       | Boot Operation (MCU Firmware Loading)               | 4–2  |  |  |  |

|         |        | 4.1.3       | GLOBCTL: Global Control Register                    | 4–3  |  |  |  |

|         | 4.2    |             | ⊦ I/O RAM Map                                       |      |  |  |  |

|         | 4.3    | Endpoint    | t Descriptor Block (EDB-1 to EDB-7)                 | 4–6  |  |  |  |

|         |        | 4.3.1       | OEPCNF_n: Output Endpoint Configuration             | 4–7  |  |  |  |

|         |        | 4.3.2       | OEPBBAX_n: Output Endpoint X-Buffer Base-Address    | 4–7  |  |  |  |

|         |        | 4.3.3       | OEPBCTX_n: Output Endpoint X-Byte Count             | 4–8  |  |  |  |

|         |        | 4.3.4       | OEPBBAY_n: Output Endpoint Y-Buffer Base-Address    | 4–8  |  |  |  |

|         |        | 4.3.5       | OEPBCTY_n: Output Endpoint Y-Byte Count             | 4–8  |  |  |  |

|         |        | 4.3.6       | OEPSIZXY_n: Output Endpoint X/Y-Buffer Size         | 4–9  |  |  |  |

|         |        | 4.3.7       | IEPCNF_n: Input Endpoint Configuration              | 4–9  |  |  |  |

|         |        | 4.3.8       | IEPBBAX_n: Input Endpoint X-Buffer Base-Address     | 4–9  |  |  |  |

|         |        | 4.3.9       | IEPBCTX_n: Input Endpoint X-Byte Count              | 4–10 |  |  |  |

|         |        | 4.3.10      | IEPBBAY_n: Input Endpoint Y-Buffer Base-Address     | 4–10 |  |  |  |

|         |        | 4.3.11      | IEPBCTY_n: Input Endpoint Y-Byte Count              | 4–10 |  |  |  |

|         |        | 4.3.12      | IEPSIZXY_n: Input Endpoint X/Y-Buffer Size          | 4–11 |  |  |  |

|         | 4.4    | Endpoint    | t-0 Descriptor Registers                            | 4–11 |  |  |  |

|         |        | 4.4.1       | IEPCNFG_0: Input Endpoint-0 Configuration Register  | 4–11 |  |  |  |

|         |        | 4.4.2       | IEPBCNT_0: Input Endpoint-0 Byte Count Register     | 4–12 |  |  |  |

|         |        | 4.4.3       | OEPCNFG_0: Output Endpoint-0 Configuration          |      |  |  |  |

|         |        |             | Register                                            |      |  |  |  |

|         |        | 4.4.4       | OEPBCNT_0: Output Endpoint X-Byte Count Register    |      |  |  |  |

| 5       | HISR F | Panietare   |                                                     | 5_1  |  |  |  |

| 5.3 OEPCNFG_0: Output Endpoint-0 Configura 5.4 OEPBCNT_0: Output Endpoint-0 Byte Cou 5.5 USBMSK: USB Interrupt Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ess Register 5                                      | 5–1        |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------|--|--|--|--|--|

| 5.4 OEPBCNT_0: Output Endpoint-0 Byte Cou 5.5 USBMSK: USB Interrupt Mask Register 5.6 USBCTL: USB Control Register 5.7 HUBCNF1: Hub-Configuration-1 Register . 5.8 HUBCNF2: Hub-Configuration-2 Register . 5.9 HUBPOTG: Hub Power-On to Power-Good 5.10 HUBPIDL: Hub-PID Register (Low-Byte) . 5.11 HUBPIDH: Hub-PID Register (High-Byte) . 5.12 HUBVIDL: Hub-VID Register (High-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interc 5.15 Pullup Resistor Connect/Disconnect 6.1 DMA Controller 6.1.1 DMACDR[2:1]: DMA Channel De 6.1.2 DMACSR[2:1]: DMA Control and 6.1.3 DMACDR[4:3]: DMA Control and 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.1.6 DMACSR[5]: DMA-5 Control and 6.1.7 DMACDR[5]: DMA-5 Control and 6.1.8 DMACDR[5]: DMA-5 Control and 6.1.9 DMACSR[5]: DMA-5 Control and 6.10 DMACSR[5]: DMA-5 Control and 6.11 DMACDR[5]: DMA-5 Control and 6.12 Bulk Data I/O Using the EDB 7.1.1 RDR[2:1]: Transmitter Data Registe 7.1.2 TDR[2:1]: UART Flow Control Registers 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control Registers 7.1.5 MCR[2:1]: Modem-Control Registers 7.1.6 LSR[2:1]: Modem-Status Register 7.1.7 MSR[2:1]: Divisor Low-Byte Registe 7.1.8 DLL[2:1]: Divisor Low-Byte Registe 7.1.9 DLH[2:1]: Divisor High-Byte Regist 7.1.10 XON[2:1]: Xoff Registers 7.1.11 XOFF[2:1]: WART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control) | USBSTA: USB Status Register                         |            |  |  |  |  |  |

| 5.5 USBMSK: USB Interrupt Mask Register 5.6 USBCTL: USB Control Register 5.7 HUBCNF1: Hub-Configuration-1 Register . 5.8 HUBCNF2: Hub-Configuration-2 Register . 5.9 HUBPOTG: Hub Power-On to Power-Good 5.10 HUBPIDL: Hub-PID Register (Low-Byte) . 5.11 HUBPIDH: Hub-VID Register (High-Byte) . 5.12 HUBVIDL: Hub-VID Register (High-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interced 5.15 Pullup Resistor Connect/Disconnect 6.1 DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OEPCNFG_0: Output Endpoint-0 Configuration Register |            |  |  |  |  |  |

| 5.5 USBMSK: USB Interrupt Mask Register 5.6 USBCTL: USB Control Register 5.7 HUBCNF1: Hub-Configuration-1 Register . 5.8 HUBCNF2: Hub-Configuration-2 Register . 5.9 HUBPOTG: Hub Power-On to Power-Good 5.10 HUBPIDL: Hub-PID Register (Low-Byte) . 5.11 HUBPIDH: Hub-VID Register (High-Byte) . 5.12 HUBVIDL: Hub-VID Register (High-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interced 5.15 Pullup Resistor Connect/Disconnect 6.1 DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ipoint-0 Byte Count Register 5                      | 5–2        |  |  |  |  |  |

| 5.6 USBCTL: USB Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     | 5–3        |  |  |  |  |  |

| 5.7 HUBCNF1: Hub-Configuration-1 Register . 5.8 HUBCNF2: Hub-Configuration-2 Register . 5.9 HUBPOTG: Hub Power-On to Power-Good . 5.10 HUBPIDL: Hub-PID Register (Low-Byte) . 5.11 HUBPIDH: Hub-PID Register (High-Byte) . 5.12 HUBVIDL: Hub-VID Register (Low-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interests . 5.15 Pullup Resistor Connect/Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L: USB Control Register                             |            |  |  |  |  |  |

| 5.8 HUBCNF2: Hub-Configuration-2 Register . 5.9 HUBPOTG: Hub Power-On to Power-Good 5.10 HUBPIDL: Hub-PID Register (Low-Byte) . 5.11 HUBPIDH: Hub-PID Register (High-Byte) . 5.12 HUBVIDL: Hub-VID Register (Low-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interce 5.15 Pullup Resistor Connect/Disconnect 6 DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | F1: Hub-Configuration-1 Register                    |            |  |  |  |  |  |

| 5.9 HUBPOTG: Hub Power-On to Power-Good 5.10 HUBPIDL: Hub-PID Register (Low-Byte) 5.11 HUBPIDH: Hub-PID Register (High-Byte) 5.12 HUBVIDL: Hub-VID Register (Low-Byte) 5.13 HUBVIDH: Hub-VID Register (High-Byte) 5.14 Function Reset and Power-Up Reset Interce 5.15 Pullup Resistor Connect/Disconnect 6 DMA Controller 6.1.1 DMACDR[2:1]: DMA Channel De 6.1.2 DMACSR[2:1]: DMA Control and 6.1.3 DMACDR[4:3]: DMA Control and 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB 7 UARTS 7.1 UART Registers 7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: UART Flow Control R 7.1.6 LSR[2:1]: Modem-Control Register 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regist 7.1.9 DLH[2:1]: Divisor High-Byte Regist 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                       | <u> </u>                                            | 5–6        |  |  |  |  |  |

| 5.10 HUBPIDL: Hub-PID Register (Low-Byte) 5.11 HUBPIDH: Hub-PID Register (High-Byte) 5.12 HUBVIDL: Hub-VID Register (Low-Byte) 5.13 HUBVIDH: Hub-VID Register (High-Byte) 5.14 Function Reset and Power-Up Reset Interce 5.15 Pullup Resistor Connect/Disconnect 6.15 Pullup Resistor Connect/Disconnect 6.1 DMA Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                                   | 5–6        |  |  |  |  |  |

| 5.11 HUBPIDH: Hub-PID Register (High-Byte) . 5.12 HUBVIDL: Hub-VID Register (Low-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interce 5.15 Pullup Resistor Connect/Disconnect 6.15 Pullup Resistor Connect/Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     | 5–6        |  |  |  |  |  |

| 5.12 HUBVIDL: Hub-VID Register (Low-Byte) . 5.13 HUBVIDH: Hub-VID Register (High-Byte) . 5.14 Function Reset and Power-Up Reset Interce 5.15 Pullup Resistor Connect/Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ` · · · · · · · · · · · · · · · · · · ·             | 5–6        |  |  |  |  |  |

| 5.13 HUBVIDH: Hub-VID Register (High-Byte) 5.14 Function Reset and Power-Up Reset Interce 5.15 Pullup Resistor Connect/Disconnect 6.1 DMA Controller 6.1 DMA Controller Registers 6.1.1 DMACDR[2:1]: DMA Channel De 6.1.2 DMACSR[2:1]: DMA Control and 6.1.3 DMACDR[4:3]: DMA Channel De 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB 7.1 UARTS 7.1 UART Registers 7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Transmitter Data Registe 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Registers 7.1.6 LSR[2:1]: Modem-Status Register 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regist 7.1.9 DLH[2:1]: Divisor High-Byte Regist 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-CTS (Transmitter Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · ·                                               | 5–7        |  |  |  |  |  |

| 5.14 Function Reset and Power-Up Reset Intered 5.15 Pullup Resistor Connect/Disconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ` · · · · · · · · · · · · · · · · · · ·             | 5–7        |  |  |  |  |  |

| 5.15 Pullup Resistor Connect/Disconnect  6.1 DMA Controller  6.1.1 DMACDR[2:1]: DMA Channel De  6.1.2 DMACSR[2:1]: DMA Control and  6.1.3 DMACDR[4:3]: DMA Channel De  6.1.4 DMACSR[4:3]: DMA Control and  6.1.5 DMACDR[5]: DMA-5 Channel De  6.1.6 DMACSR[5]: DMA-5 Control and  6.2 Bulk Data I/O Using the EDB  7.1.1 RDR[2:1]: Receiver Data Registe  7.1.2 TDR[2:1]: Transmitter Data Registe  7.1.3 LCR[2:1]: Line Control Registers  7.1.4 FCRL[2:1]: UART Flow Control R  7.1.5 MCR[2:1]: Modem-Control Register  7.1.6 LSR[2:1]: Modem-Status Register  7.1.7 MSR[2:1]: Modem-Status Register  7.1.8 DLL[2:1]: Divisor Low-Byte Regist  7.1.9 DLH[2:1]: Divisor High-Byte Regist  7.1.10 XON[2:1]: Xoff Registers  7.1.11 XOFF[2:1]: Xoff Registers  7.1.12 MASK[2:1]: UART Interrupt-Mask  7.2 UART Data Transfer  7.2.1 Receiver Data Flow  7.2.2 Hardware Flow Control  7.2.3 Auto-CTS (Transmitter Control)  7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     | 5–7        |  |  |  |  |  |

| 6.1 DMA Controller Registers 6.1.1 DMACDR[2:1]: DMA Channel De 6.1.2 DMACSR[2:1]: DMA Channel De 6.1.3 DMACDR[4:3]: DMA Channel De 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB  7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Transmitter Data Regist 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Register 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regist 7.1.9 DLH[2:1]: Divisor High-Byte Regist 7.1.10 XON[2:1]: Xoff Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                   | 5–8        |  |  |  |  |  |

| 6.1 DMA Controller Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     | <u>3–1</u> |  |  |  |  |  |

| 6.1.1 DMACDR[2:1]: DMA Channel De 6.1.2 DMACSR[2:1]: DMA Control and 6.1.3 DMACDR[4:3]: DMA Channel De 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB  7.1 UARTS  7.1 UART Registers  7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Transmitter Data Registe 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Regist 7.1.6 LSR[2:1]: Modem-Status Registers 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Regist 7.1.9 DLH[2:1]: Divisor High-Byte Regist 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: VART Interrupt-Mask 7.2 UART Data Transfer  7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     | 5–1        |  |  |  |  |  |

| 6.1.2 DMACSR[2:1]: DMA Control and 6.1.3 DMACDR[4:3]: DMA Channel De 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB  7.1 UARTS  7.1 UART Registers  7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Transmitter Data Registe 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Regist 7.1.6 LSR[2:1]: Modem-Control Regist 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Regist 7.1.9 DLH[2:1]: Divisor High-Byte Regist 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: VART Interrupt-Mask 7.2 UART Data Transfer  7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | 5–2        |  |  |  |  |  |

| 6.1.3 DMACDR[4:3]: DMA Channel De 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB  7.1 UARTS  7.1 UART Registers  7.1.1 RDR[2:1]: Receiver Data Register 7.1.2 TDR[2:1]: Transmitter Data Register 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control Registers 7.1.5 MCR[2:1]: Modem-Control Registers 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Registers 7.1.9 DLH[2:1]: Divisor High-Byte Registers 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     | 3–3        |  |  |  |  |  |

| 6.1.4 DMACSR[4:3]: DMA Control and 6.1.5 DMACDR[5]: DMA-5 Channel De 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB  7 UARTS  7.1 UART Registers  7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Transmitter Data Registe 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Register 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Register 7.1.9 DLH[2:1]: Divisor High-Byte Register 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | S S                                                 | 6–4        |  |  |  |  |  |

| 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB  7 UARTS  7.1 UART Registers  7.1.1 RDR[2:1]: Receiver Data Register  7.1.2 TDR[2:1]: Transmitter Data Register  7.1.3 LCR[2:1]: Line Control Registers  7.1.4 FCRL[2:1]: UART Flow Control Registers  7.1.5 MCR[2:1]: Modem-Control Registers  7.1.6 LSR[2:1]: Line-Status Registers  7.1.7 MSR[2:1]: Modem-Status Registers  7.1.8 DLL[2:1]: Divisor Low-Byte Registers  7.1.9 DLH[2:1]: Divisor High-Byte Registers  7.1.10 XON[2:1]: Xon Registers  7.1.11 XOFF[2:1]: Xoff Registers  7.1.12 MASK[2:1]: UART Interrupt-Mask  7.2 UART Data Transfer  7.2.1 Receiver Data Flow  7.2.2 Hardware Flow Control  7.2.3 Auto-RTS (Receiver Control)  7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u> </u>                                            | 3–5        |  |  |  |  |  |

| 6.1.6 DMACSR[5]: DMA-5 Control and 6.2 Bulk Data I/O Using the EDB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MA-5 Channel Definition Register 6                  | 6–6        |  |  |  |  |  |

| 7 UARTS  7.1 UART Registers  7.1.1 RDR[2:1]: Receiver Data Registe  7.1.2 TDR[2:1]: Transmitter Data Registe  7.1.3 LCR[2:1]: Line Control Registers  7.1.4 FCRL[2:1]: UART Flow Control R  7.1.5 MCR[2:1]: Modem-Control Registers  7.1.6 LSR[2:1]: Line-Status Registers  7.1.7 MSR[2:1]: Modem-Status Registers  7.1.8 DLL[2:1]: Divisor Low-Byte Registers  7.1.9 DLH[2:1]: Divisor High-Byte Registers  7.1.10 XON[2:1]: Xon Registers  7.1.11 XOFF[2:1]: UART Interrupt-Mask  7.2 UART Data Transfer  7.2.1 Receiver Data Flow  7.2.2 Hardware Flow Control  7.2.3 Auto-RTS (Receiver Control)  7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>y</del>                                        | 6–7        |  |  |  |  |  |

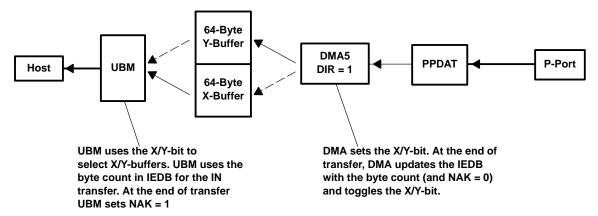

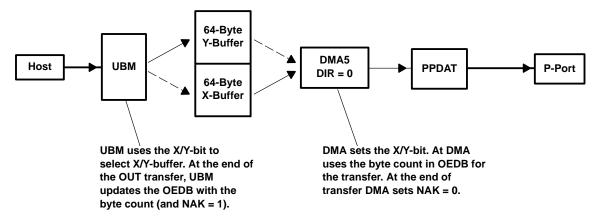

| 7.1 UART Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | 6–7        |  |  |  |  |  |

| 7.1.1 RDR[2:1]: Receiver Data Registe 7.1.2 TDR[2:1]: Transmitter Data Registe 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Registers 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Registers 7.1.9 DLH[2:1]: Divisor High-Byte Registers 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     | 7–1        |  |  |  |  |  |

| 7.1.2 TDR[2:1]: Transmitter Data Regis 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Regist 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     | 7–1        |  |  |  |  |  |

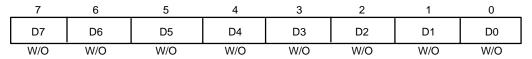

| 7.1.2 TDR[2:1]: Transmitter Data Regis 7.1.3 LCR[2:1]: Line Control Registers 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Regist 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Registers 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | iver Data Registers 7                               | 7–1        |  |  |  |  |  |

| 7.1.4 FCRL[2:1]: UART Flow Control R 7.1.5 MCR[2:1]: Modem-Control Regist 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mitter Data Registers                               | 7–1        |  |  |  |  |  |

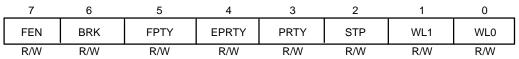

| 7.1.5 MCR[2:1]: Modem-Control Regist 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Control Registers                                   | 7–2        |  |  |  |  |  |

| 7.1.6 LSR[2:1]: Line-Status Registers 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RT Flow Control Registers 7                         | 7–3        |  |  |  |  |  |

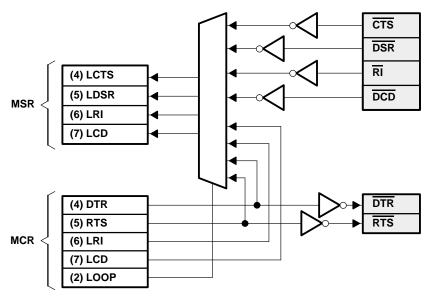

| 7.1.7 MSR[2:1]: Modem-Status Register 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow 7.2.2 Hardware Flow Control 7.2.3 Auto-RTS (Receiver Control) 7.2.4 Auto-CTS (Transmitter Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | em-Control Registers 7                              | 7–5        |  |  |  |  |  |

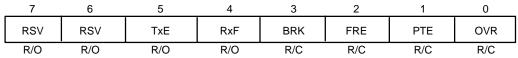

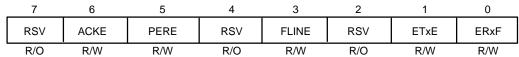

| 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Status Registers 7                                  | 7–6        |  |  |  |  |  |

| 7.1.8 DLL[2:1]: Divisor Low-Byte Regis 7.1.9 DLH[2:1]: Divisor High-Byte Regis 7.1.10 XON[2:1]: Xon Registers 7.1.11 XOFF[2:1]: Xoff Registers 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer 7.2.1 Receiver Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | em-Status Registers 7                               | 7–7        |  |  |  |  |  |

| 7.1.10 XON[2:1]: Xon Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     | 7–7        |  |  |  |  |  |

| 7.1.11 XOFF[2:1]: Xoff Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | or High-Byte Registers 7                            | 7–8        |  |  |  |  |  |

| 7.1.12 MASK[2:1]: UART Interrupt-Mask 7.2 UART Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Registers                                           | 7–9        |  |  |  |  |  |

| 7.2 UART Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Registers 7                                         | 7–9        |  |  |  |  |  |

| <ul> <li>7.2.1 Receiver Data Flow</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RT Interrupt-Mask Registers 7                       | 7–9        |  |  |  |  |  |

| <ul> <li>7.2.2 Hardware Flow Control</li> <li>7.2.3 Auto-RTS (Receiver Control)</li> <li>7.2.4 Auto-CTS (Transmitter Control) .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     | 7–9        |  |  |  |  |  |

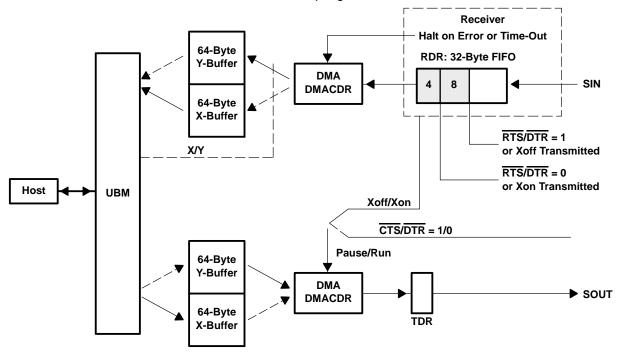

| <ul> <li>7.2.3 Auto-RTS (Receiver Control)</li> <li>7.2.4 Auto-CTS (Transmitter Control) .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Flow                                                | -10        |  |  |  |  |  |

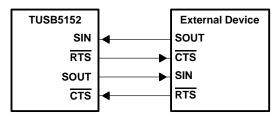

| 7.2.4 Auto-CTS (Transmitter Control) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Control                                             | -10        |  |  |  |  |  |

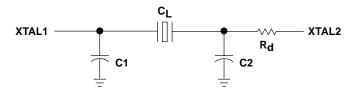

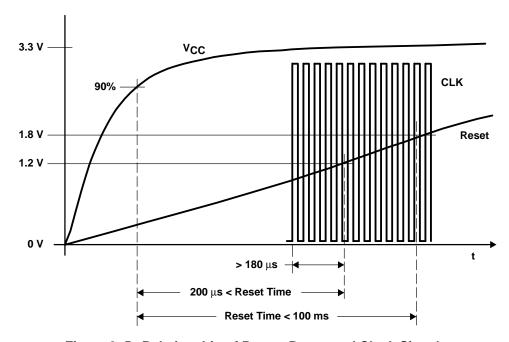

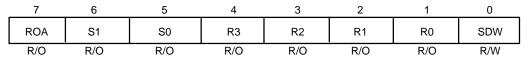

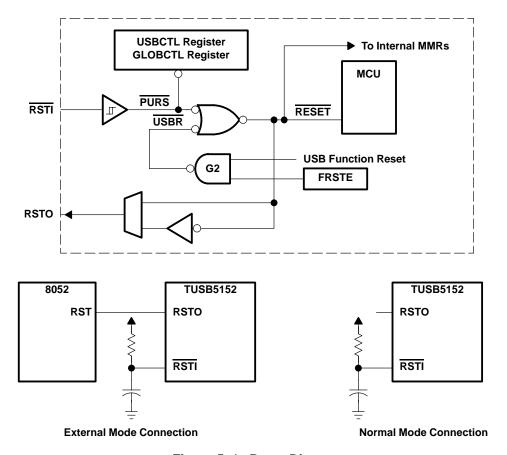

| 7.2.4 Auto-CTS (Transmitter Control) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | eiver Control) 7-                                   | -10        |  |  |  |  |  |