# **ICs for Communications**

ISDN Communication Controller · ICC PEB 2070 PEF 2070

SIEMS02119

User's Manual

# ICs for Communications

ISDN Communication Controller ICC PEB 2070 PEF 2070

User's Manual 01.94

| PEB 2070<br>Revision I | ; PEF 2070<br>History:                 | 01.94 |  |

|------------------------|----------------------------------------|-------|--|

| Previous F             | Releases:                              | 06.92 |  |

| Page                   | Subjects (changes since last revision) |       |  |

|                        | Update                                 |       |  |

#### **Data Classification**

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### Characteristics

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

#### **Operating Range**

In the operating range the functions given in the circuit description are fulfilled.

For detailed technical information about "Processing Guidelines" and "Quality Assurance" for ICs, see our "Product Overview".

#### Edition 01.94

This edition was realized using the software system FrameMaker®.

# Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, D-81541 München

© Siemens AG 1994. All Rights Reserved.

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery, and prices please contact the Offices of Semiconductor Group in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the type in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you - get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

| Conten   | ts                                        | Page |

|----------|-------------------------------------------|------|

| Introdu  | ction                                     | 7    |

| 1        | Features                                  | 9    |

| 1.1      | Pin Definitions and Functions             |      |

| 1.2      | Logic Symbol                              |      |

| 1.3      | Functional Block Diagram                  |      |

| 1.4      | System Integration                        |      |

| 1.4.1    | ISDN Applications                         |      |

| 1.4.2    | Other Applications                        |      |

| 1.4.3    | Microprocessor Environment                |      |

| 2        | Functional Description                    | 23   |

| _<br>2.1 | General Functions and Device Architecture | 23   |

| 2.2      | Serial Interface Modes                    |      |

| 2.2.1    | IOM®-1 Mode (IMS = 0, DIM2 = 0)           |      |

| 2.2.2    | IOM®-2 Mode (IMS = 1)                     |      |

| 2.2.3    | HDLC Controller Mode (IMS = 0, DIM2 = 1)  | 28   |

| 2.3      | Interfaces                                |      |

| 2.3.1    | μP Interface                              |      |

| 2.3.2    | ISDN Oriented Modular (IOM®) Interface    | 30   |

| 2.3.3    | SSI (Serial Port A)                       |      |

| 2.3.4    | SLD                                       | 39   |

| 2.4      | Individual Functions                      |      |

| 2.4.1    | Layer-2 Functions for HDLC                | 40   |

| 2.4.1.1  | Message Transfer Modes                    |      |

| 2.4.1.2  | Protocol Operations (auto mode)           | 42   |

| 2.4.1.3  | Reception of Frames                       |      |

| 2.4.1.4  | Transmission of Frames                    | 49   |

| 2.4.2    | B-Channel Switching (IOM®_1)              | 52   |

| 2.4.3    | Access to B/IC Channels                   |      |

| 2.4.4    | C/I Channel Handling                      | 59   |

| 2.4.5    | MONITOR Channel Handling                  |      |

| 2.4.6    | Terminal Specific Functions               | 64   |

| 2.4.7    | Test Functions                            | 65   |

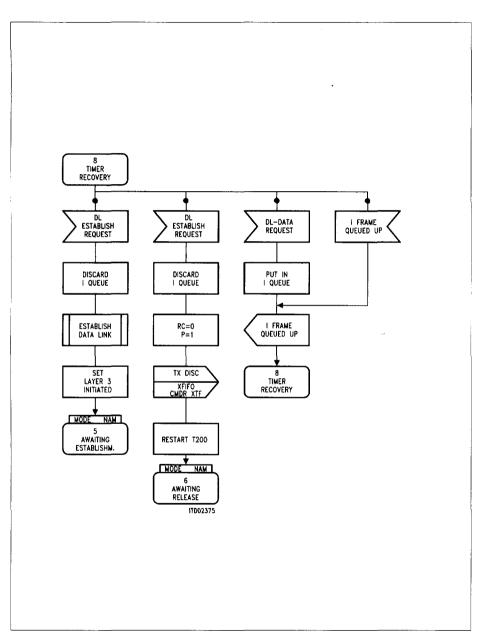

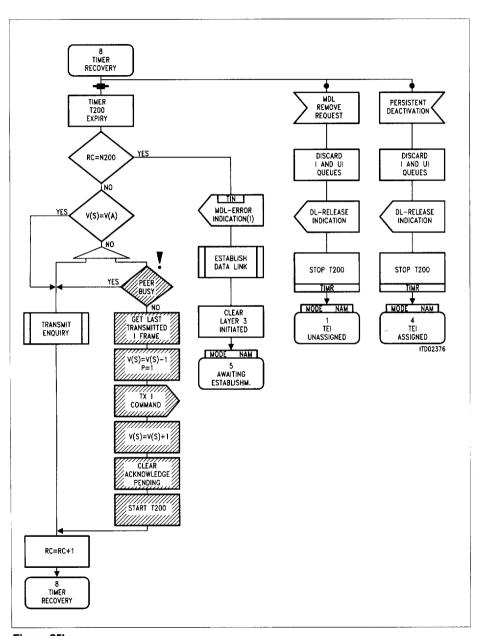

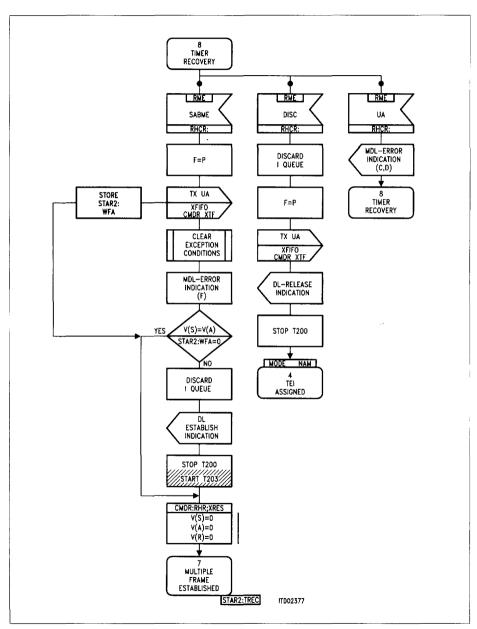

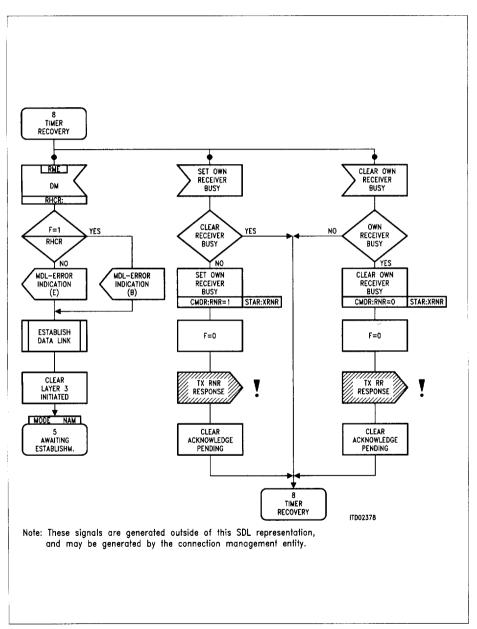

| 2.4.8    | Documentation of the Auto Mode            | 66   |

| 3        | Operational Description                   | 93   |

| 3.1      | Microprocessor Interface Operation        |      |

| 3.2      | Reset.                                    | 93   |

| 3.3      | Initialization                            |      |

| 3.4      | IOM® Interface Connections                | 97   |

$\mathsf{IOM}^{@}$ ,  $\mathsf{IOM}^{@}$ -1,  $\mathsf{IOM}^{@}$ -2,  $\mathsf{ARCOFI}^{@}$ ,  $\mathsf{ISAC}^{@}$ -P,  $\mathsf{ISAC}^{@}$ -S,  $\mathsf{ITAC}^{@}$ ,  $\mathsf{EPIC}^{@}$ ,  $\mathsf{SICOFI}^{@}$  are registered trademarks of Siemens AG.

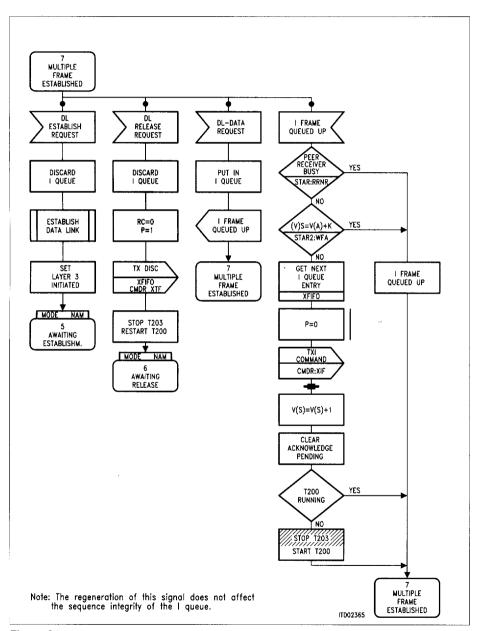

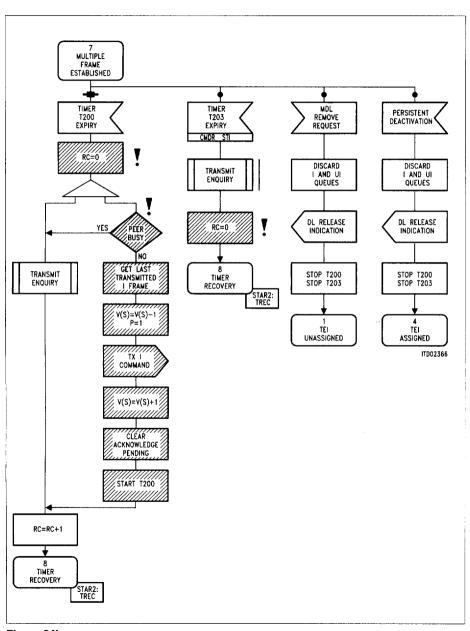

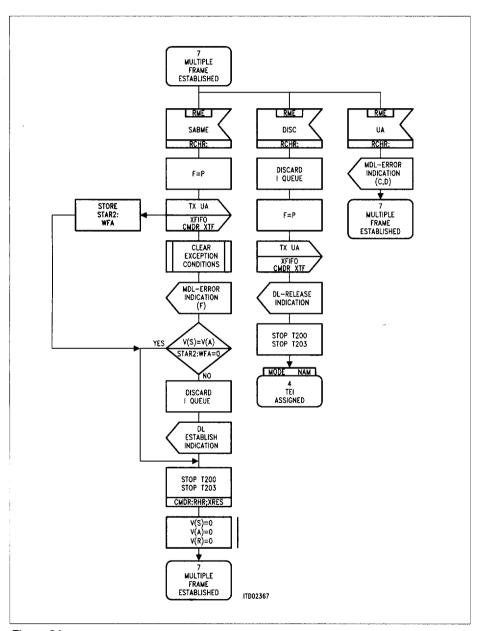

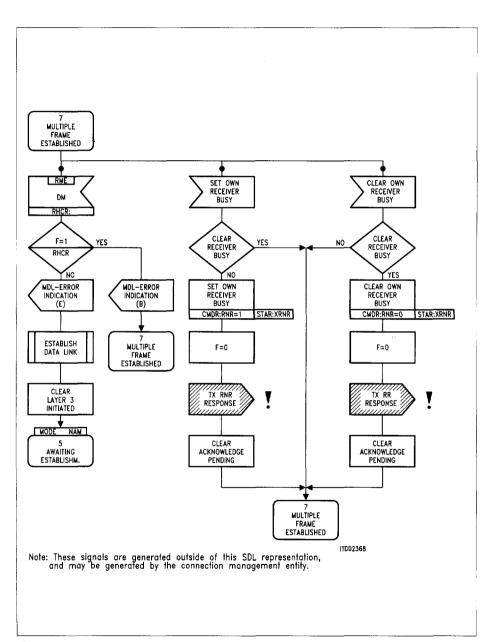

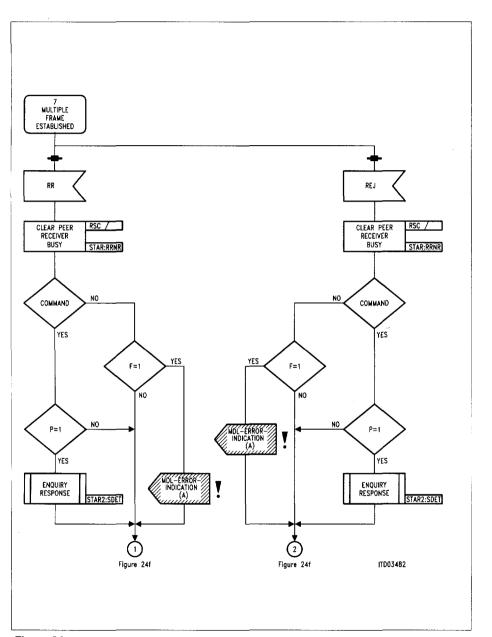

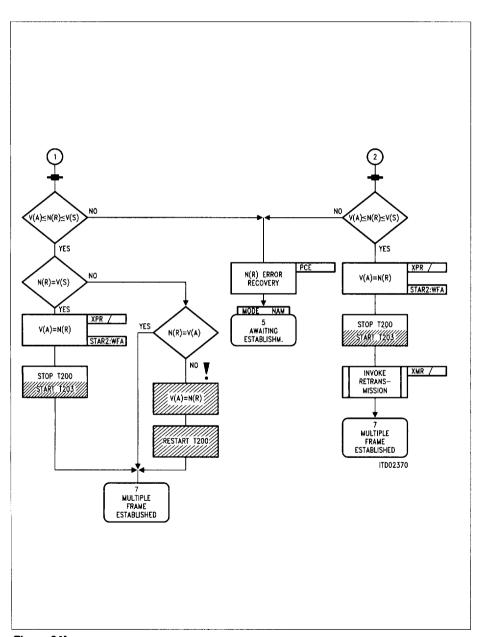

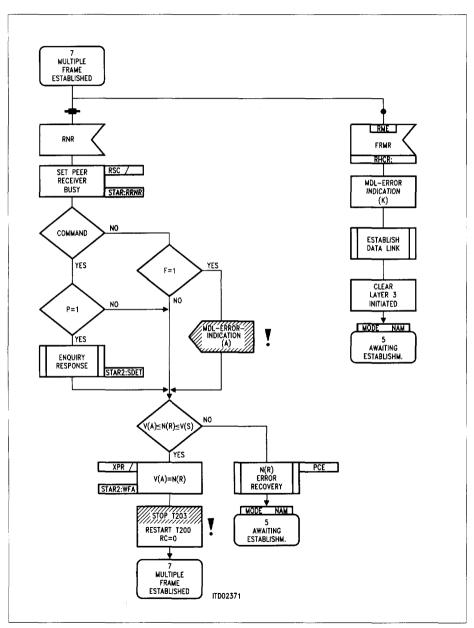

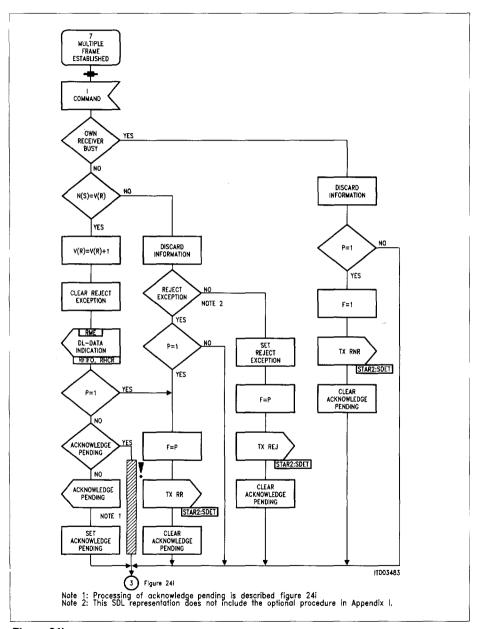

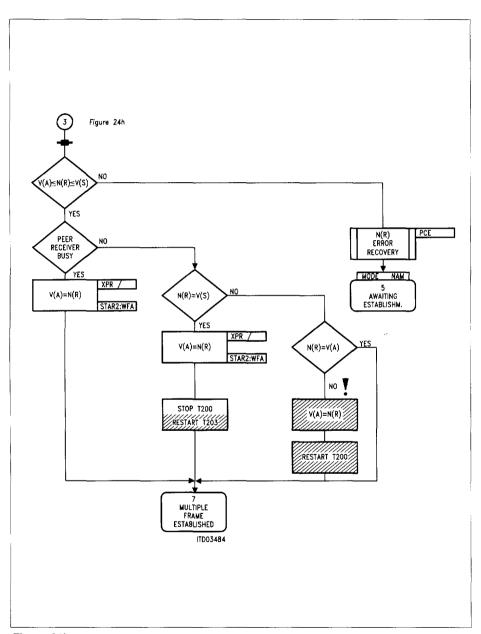

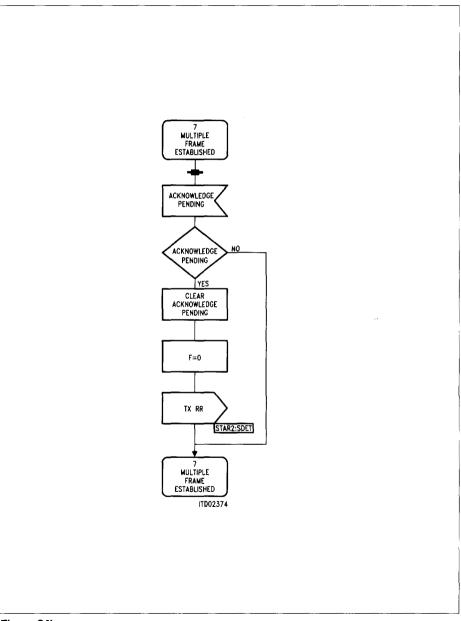

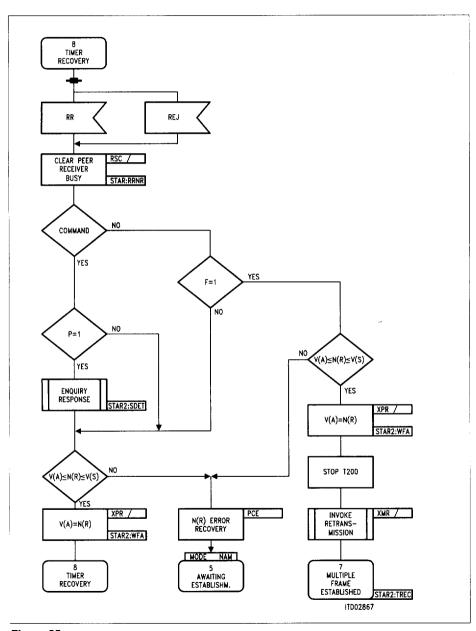

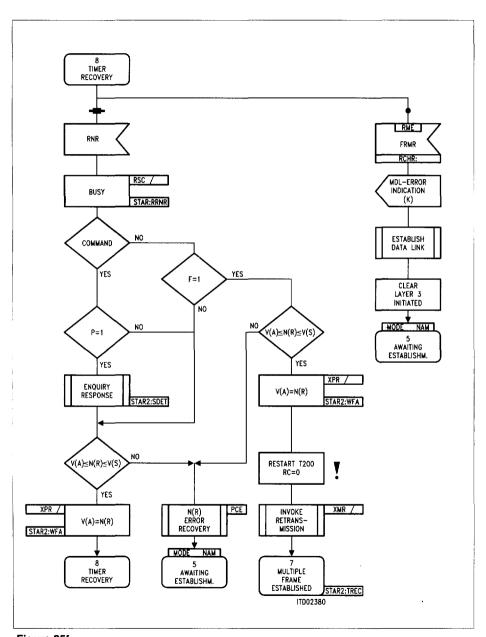

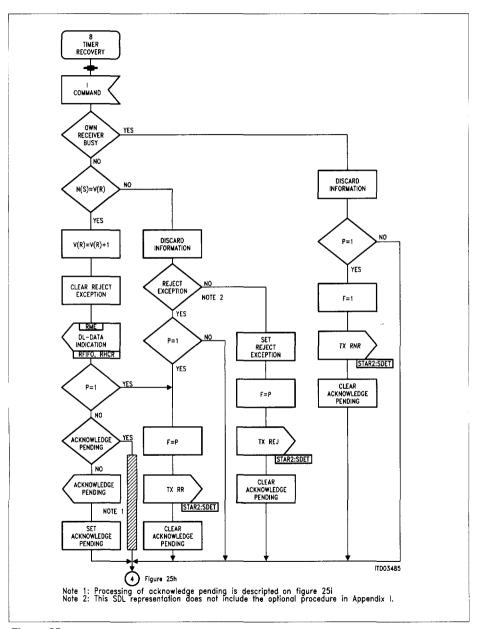

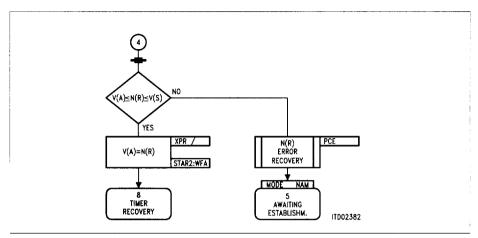

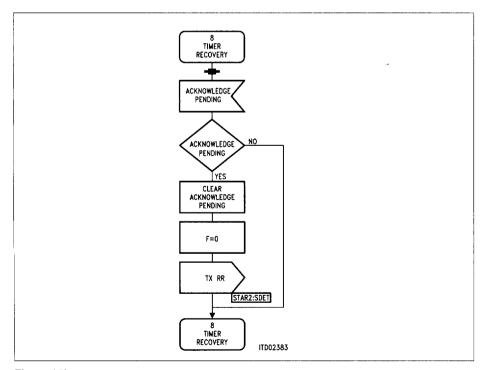

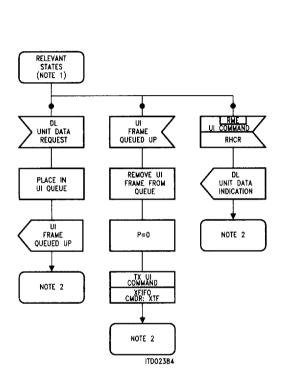

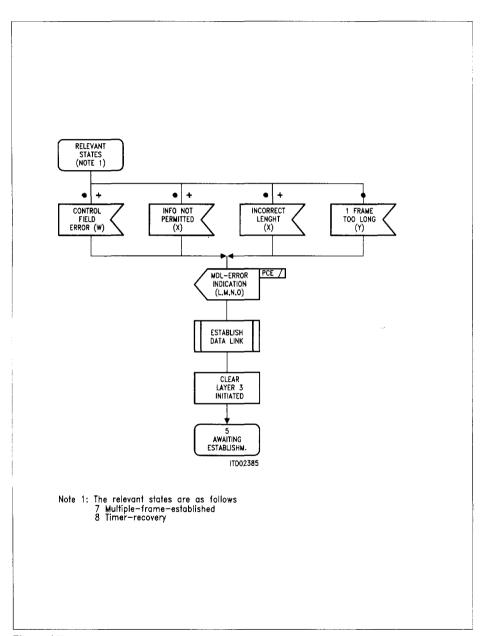

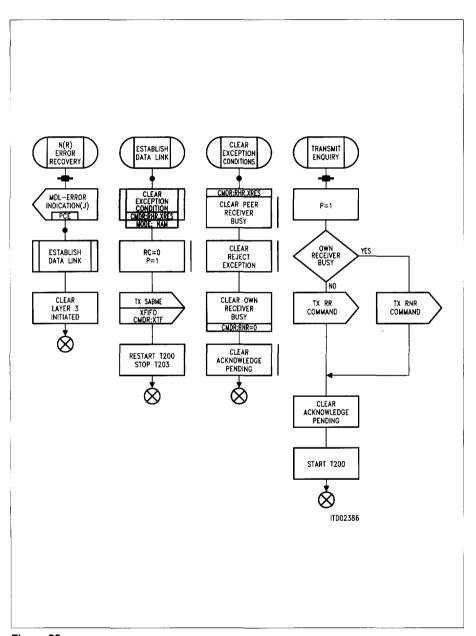

Figure 24a until figure 26d are CCITT recommendations for comparison.

| Conten                                      | ts (cont'd)                                                                               | Page                    |

|---------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|

| 3.5<br>3.5.1<br>3.5.2<br>3.5.2.1<br>3.5.2.2 | Processing Interrupt Structure Data Transfer HDLC Frame Reception HDLC Frame Transmission | . 102<br>. 105<br>. 109 |

| 4                                           | Detailed Register Description                                                             | . 114                   |

| 4.1                                         | HDLC Operation and Status Registers                                                       | . 119                   |

| 4.1.1                                       | Receive FIFO                                                                              |                         |

| 4.1.2                                       | Transmit FIFO                                                                             |                         |

| 4.1.3                                       | Interrupt Status Register                                                                 |                         |

| 4.1.4                                       | Mask Register                                                                             |                         |

| 4.1.5                                       | Status Register                                                                           |                         |

| 4.1.6                                       | Command Register                                                                          |                         |

| 4.1.7                                       | Mode Register                                                                             |                         |

| 4.1.8                                       | Time Register                                                                             |                         |

| 4.1.9                                       | Extended Interrupt Register                                                               |                         |

| 4.1.10                                      | Transmit Address 1                                                                        |                         |

| 4.1.11<br>4.1.12                            | Receive Frame Byte Count Low                                                              |                         |

| 4.1.12                                      | Transmit Address 2                                                                        |                         |

| 4.1.13                                      | SAPI1 Register                                                                            |                         |

| 4.1.14                                      | Received Status Register                                                                  |                         |

| 4.1.16                                      | SAP12 Register                                                                            |                         |

| 4.1.17                                      | TEI1 Register 1                                                                           |                         |

| 4.1.18                                      | Receive HDLC Control Register                                                             |                         |

| 4.1.19                                      | TEI2 Register                                                                             |                         |

| 4.1.20                                      | Receive Frame Byte Count High                                                             |                         |

| 4.2                                         | Special Purpose Registers: IOM-1Mode                                                      |                         |

| 4.2.1                                       | Serial Port Control Register                                                              |                         |

| 4.2.2                                       | Command/Indication Receive Register                                                       |                         |

| 4.2.3                                       | Command/Indication Transmit Register                                                      |                         |

| 4.2.4                                       | MONITOR Receive Register                                                                  |                         |

| 4.2.5                                       | MONITOR Transmit Register                                                                 | . 141                   |

| 4.2.6                                       | SIP Signaling Code Receive                                                                | . 141                   |

| 4.2.7                                       | SIP Signaling Code Transmit                                                               | . 141                   |

| 4.2.8                                       | SIP Feature Control Read                                                                  |                         |

| 4.2.9                                       | SIP Feature Control Write                                                                 |                         |

| 4.2.10                                      | Channel Register 1                                                                        |                         |

| 4.2.11                                      | Channel Register 2                                                                        | . 142                   |

| 4.2.12                                      | B1 Channel Register                                                                       | . 143                   |

| 4.2.13                                      | Synchronous Transfer Control Register                                                     |                         |

| 4.2.14                                      | B2 Channel Register                                                                       |                         |

| 4.2.15                                      | Additional Feature Register 1                                                             |                         |

| 4.2.16                                      | Additional Feature Register 2                                                             | . 145                   |

| 4.3                                         | Special Purpose Registers: IOM-2 Mode                                                     |                         |

| 4.3.1                                       | Serial Port Control Register                                                              | . 146                   |

### **General Information**

### **SIEMENS**

| Conter | its (cont'd)                          | Page |

|--------|---------------------------------------|------|

| 4.3.2  | Command/Indication Receive 0          | 148  |

| 4.3.3  | Command/Indication Transmit 0         | 148  |

| 4.3.4  | MONITOR Receive Channel 0             |      |

| 4.3.5  | MONITOR Transmit Channel 0            |      |

| 4.3.6  | Command/Indication Receive 1          | 150  |

| 4.3.7  | Command/Indication Transmit 1         |      |

| 4.3.8  | MONITOR Receive Channel 1             | 151  |

| 4.3.9  | MONITOR Transmit Channel 1            | 151  |

| 4.3.10 | Channel Register 1                    | 151  |

| 4.3.11 | Channel Register 2                    | 151  |

| 4.3.12 | B1 Channel Register                   | 152  |

| 4.3.13 | Synchronous Transfer Control Register | 152  |

| 4.3.14 | B2 Channel Register                   | 153  |

| 4.3.15 | Additional Feature Register 1         | 154  |

| 4.3.16 | Additional Feature Register 2         | 155  |

| 4.3.17 | MONITOR Status Register               | 156  |

| 4.3.18 | MONITOR Control Register              | 157  |

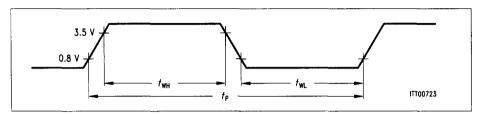

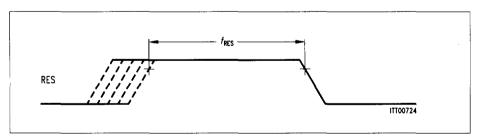

| 5      | Electrical Characteristics            | 158  |

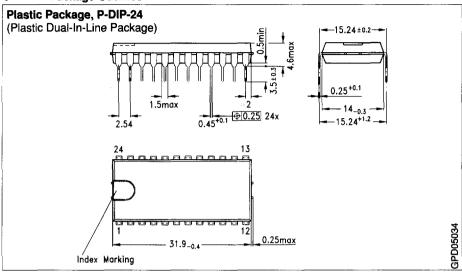

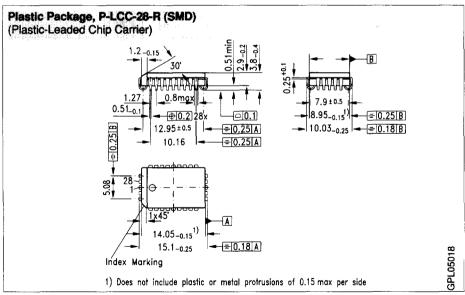

| 6      | Package Outlines                      | 170  |

| 7      | Information om Literature             | 171  |

#### Introduction

The transmission and protocol functions in an ISDN basis access can be all be implemented using the CMOS circuits of the ISDN Oriented Modular (IOM®) chip set. While three chips, the S Bus interface Circuit SBC (PEB 2080), the ISDN Echo Cancellation circuit IEC (PEB 2090) and the ISDN Burst Controller IBC (PEB 2095) perform the transmission functions in different applications (S and U interface), the ISDN Communication Controller ICC (PEB 2070) acts as the D-channel-link-access protocol controller.

The IOM® architecture makes possible a wide range of configurations for the Basic Access, using the basic devices. These configurations essentially differ in the implementation of the layer-1 OSI functions, while the layer-2 functions are provided by the ICC for all configurations.

In addition to that, the PEB 2070 provides the interface to B-channel sources in the terminal and to a peripheral board controller (PEB 2050, 51, 52 etc.) at the exchange.

The HDLC packets of the ISDN D channel are handled by the ICC which transfers them to the associated microcontroller. The ICC has on-chip buffer memories (64 bytes per direction) for the temporary storage of data packets. Because of the overlapping I/O operations the maximum length of the D-channel packets is not limited. In one of its operating modes the device offers high level support of layer-2 functions of the LAPD protocol.

Aside from ISDN applications, the ICC can be used as a general purpose communication controller in all applications calling for LAPD, LAPB or other HDLC/SDLC based protocols.

# ISDN Communication Controller (ICC)

- 1 Features

- Support of LAPD protocol

- Different types of operating modes for increased flexibility

- FIFO buffer (2 x 64 bytes) for efficient transfer of data packets

• Serial interfaces: IOM®-1, SLD, SSI

IOM®-2

- General purpose HDLC communication interface

- Implementation of IOM-1/IOM-2 MONITOR and C/I channel protocol to control layer 1 and peripheral devices

- D-channel access with contention resolution mechanism

- μP access to B channel and intercommunication channels

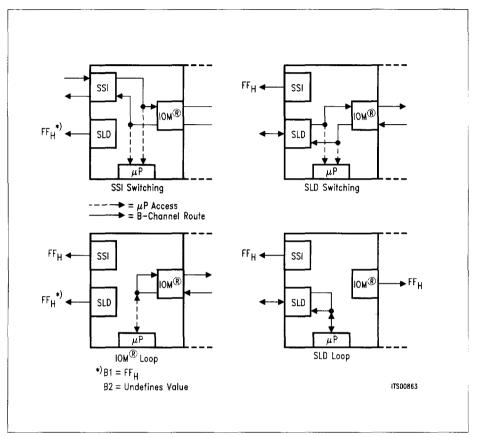

- B-channels switching

- Watchdog timer

- Test loops

- Advanced CMOS technology

Low power consumption:

active: 17 mW (IOM-2)

: 8 mW (IOM-1)

standby : 3 mW

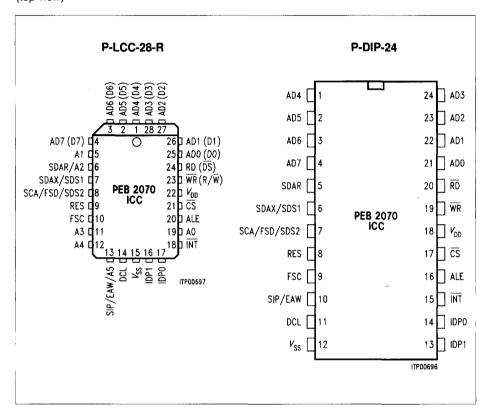

| Туре       | Ordering Code | Package          |

|------------|---------------|------------------|

| PEB 2070-N | Q67100-H6213  | P-LCC-28-R (SMD) |

| PEB 2070-P | Q67100-H6212  | P-DIP-24         |

| PEF 2070-N | H67100-H6246  | P-LCC-28-R (SMD) |

### Pin Configuration

(top view)

### 1.1 Pin Definitions and Functions

| Pin No.<br>P-DIP                    | Pin No.<br>P-LCC                         | Symbol                                                                       | Input (I)<br>Output (O)                       | Function                                                                                                                                                                                                                                   |

|-------------------------------------|------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21<br>22<br>23<br>24<br>1<br>2<br>3 | 25<br>26<br>27<br>28<br>1<br>2<br>3<br>4 | AD0/D0<br>AD1/D1<br>AD2/D2<br>AD3/D3<br>AD4/D4<br>AD5/D5<br>AD6/D6<br>AD7/D7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Multiplexed Bus Mode: Address/Data bus. Transfers addresses from the $\mu P$ system to the ICC and data between the $\mu P$ system and the ICC. Non Multiplexed Bus Mode: Data bus. Transfers data between the $\mu P$ system and the ICC. |

| 17                                  | 21                                       | CS                                                                           | 1                                             | Chip Select. A "Low" on this line selects the ICC for read/write operation.                                                                                                                                                                |

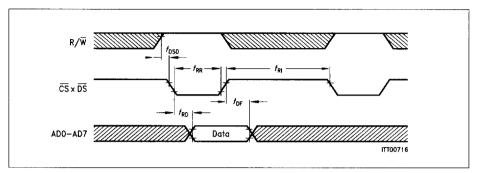

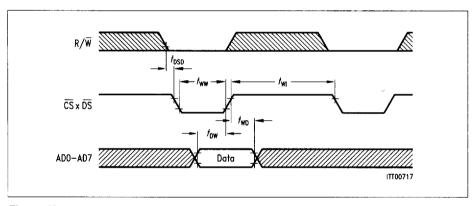

| 19                                  | 23                                       | R/W                                                                          | 1                                             | Read/Write. When "High", identifies a valid μP access as a read operation. When "Low", identifies a valid μP access as a write operation (Motorola bus mode).  Write. This signal indicates a write operation (Siemens/Intel bus mode).    |

| 20                                  | 24                                       | DS<br>RD                                                                     | 1                                             | Data Strobe. The rising edge marks the end of a valid read or write operation (Motorola bus mode).  Read. This signal indicates a read operation (Siemens/Intel bus mode).                                                                 |

| 15                                  | 18                                       | INT                                                                          | OD                                            | Interrupt Request. The signal is activated when the ICC request an interrupt. It is an open drain output.                                                                                                                                  |

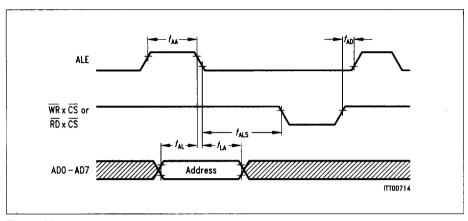

| 16                                  | 20                                       | ALE                                                                          | ı                                             | Address Latch Enable. A high on this line indicates an address on the external address bus (Multiplexed bus typ only).                                                                                                                     |

### Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP | Pin No.<br>P-LCC | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                         |

|------------------|------------------|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                | 8                | SCA    | 0                       | Serial Clock Port A, IOM-1 timing mode. A 128-kHz data clock signal for serial portA (SSI).                                                                                                                                                                      |

| 7                | 8                | FSD    | 0                       | Frame Sync Delayed, IOM-1 timing mode 1. An 8-kHz synchronization signal, delayed by 1/8 of a frame, for IOM-1 is supplied. In this mode a minimal round-trip delay for B1 and B2 channels is guaranteed.                                                        |

| 7                | 8                | SDS2   | 0                       | Serial Data Strobe 2, IOM-2 mode. A programmable strobe signal, selecting either one or two B or IC channels on IOM-2 interface, is supplied via this line.  After reset, SCA/FSD/SDS2 takes on the function of SDS2 until a write access to SPCR is made.       |

| . 8              | 9                | RES    | VO                      | Reset. A "High" on this input forces the ICC into reset state. The minimum pulse length is four clock periods. If the terminal specific functions are enabled, the ICC may also supply a reset signal.                                                           |

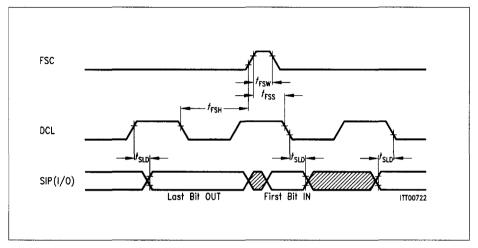

| 9                | 10               | FSC    | I                       | Frame Sync. Input synchronization signal. IOM-2 mode: Indicates the beginning of IOM frame. IOM-2 mode: Indicates the beginning of IOM and, if TSF = 0, frame (timing mode 0). Indicates the beginning of SLD frame (timing mode 1). HDLC-mode: Strobe signal of |

|                  | ,                |        |                         | programmable polarity.                                                                                                                                                                                                                                           |

### Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP | Pin No.<br>P-LCC | Symbol     | input (i)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                          |

|------------------|------------------|------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11               | 14               | DCL        | I                       | Data Clock. IOM modes: Clock of the frequency equal to twice the data on the IOM interface. HDLC mode: Clock of frequency equal to the data on serial port B.                                                                                                                                                     |

|                  | 19               | A0         | 1                       | Address bit 0 (Non-multiplexed bus type).                                                                                                                                                                                                                                                                         |

|                  | 5                | A1         | I                       | Address bit 1 (Non-multiplexed bus type).                                                                                                                                                                                                                                                                         |

| 6                | 6                | A2<br>SDAR | 1                       | Address bit 2 (Non-multiplexed bus type) Serial Data Port Receive. Serial data is received on this pin at standard TTL or CMOS level. An integrated pull-up circuit enables connection of an open-drain/ open collector driver without an external pull-up resistor. SDAR is used only if IOM-1 mode is selected. |

|                  | 11               | A3         | 1                       | Address bit 3 (Non-multiplexed bus type).                                                                                                                                                                                                                                                                         |

|                  | 12               | A4         | 1                       | Address bit 4 (Non-multiplexed bus type).                                                                                                                                                                                                                                                                         |

|                  | 13               | A5         | I                       | Address bit 5 (Non-multiplexed bus type).                                                                                                                                                                                                                                                                         |

| 10               | 13               | SIP        | I/O                     | SLD Interface Port, IOM-1 mode. This line transmits and receives serial data at standard TTL or CMOS levels.  External Awake (terminal specific function). If a falling edge on this input is detected, the ICC generates an interrupt and, if enabled, a reset pulse.                                            |

### Pin Definitions and Functions (cont'd)

| Pin No.<br>P-DIP | Pin No.<br>P-LCC | Symbol          | Input (i)<br>Output (O) | Function                                                                                                                                                                                                                                                |

|------------------|------------------|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6                | 7                | SDAX            | 0                       | Serial Data Port A transmit, IOM-1 mode. Transmit data is shifted out via this pin at standard TTL or CMOS levels.                                                                                                                                      |

| 6                | 7                | SDS1            | 0                       | Serial Data Strobe 1, IOM-2 mode. A programmable strobe signal, selecting either one or two B or IC channels on IOM-2 interface, is supplied via this line.  After reset, SDAX/SDS1 takes on the function of SDS1 until a write access to SPCR is made. |

| 12               | 15               | Vss             | -                       | Ground (0 V)                                                                                                                                                                                                                                            |

| 18               | 22               | V <sub>DD</sub> | _                       | Power supply (5 V ± 5%)                                                                                                                                                                                                                                 |

| 14               | 17               | IDP0            | 1/0                     | IOM Data Port 0                                                                                                                                                                                                                                         |

| 13               | 16               | IDP1            | 1/0                     | IOM Data Port 1                                                                                                                                                                                                                                         |

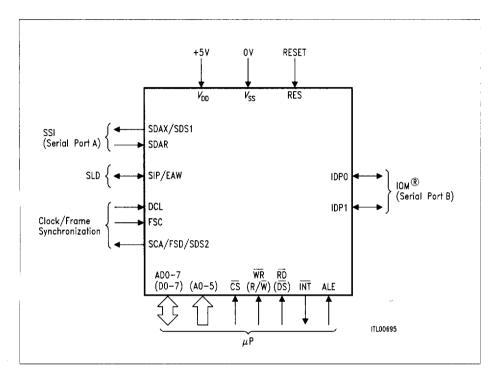

### 1.2 Logic Symbol

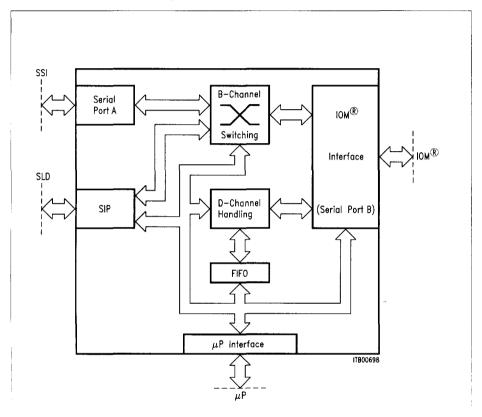

### 1.3 Functional Block Diagram

### 1.4 System Integration

#### 1.4.1 ISDN Applications

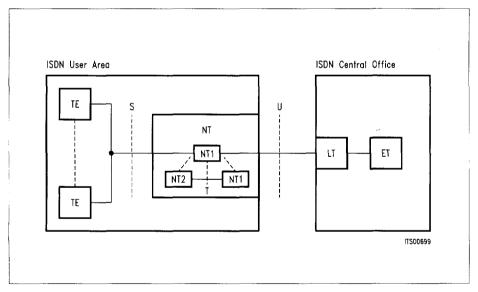

The reference model for the ISDN basic access according to CCITT I series recommendations consists of

- an exchange and trunk line termination in the central office (ET, LT)

- a remote network termination in the user area (NT)

- a two-wire loop (U interface) between NT and LT

- a four-wire link (S interface) which connects subscriber terminals and the NT in the user area as depicted in figure 1.

Figure 1

ISDN Subscriber Basic Access Architecture

The NT equipment serves as a converter between the U interface at the exchange and the S interface at the subscriber premises. The NT may consist of either an NT1 only or an NT1 together with an NT2 connected via the T interface which is physically identical to the S interface. The NT1 is a direct transformation between layer 1 of S and layer 1 of U. NT2 may include higher level functions like multiplexing and switching as in a PABX.

In terms of channels the ISDN access consists of:

- a number of 64 kbit/s bearer channels (n x B)

- e.g. n = 2 for basic rate ISDN access n = 30 or 23 for primary rate ISDN access;

- and a signaling channel (D), either 16 (basic rate) or 64 (primary rate) kbit/s (figure 2).

Figure 2 ISDN Basic Access Channel Structure

The B channels are used for end-to-end circuit switched digital connections between communicating stations.

The D channel is used to carry signaling and data via protocols defined by the CCITT. These protocols cover the network services layers of the open system interconnection model (Layers 1-3). At layer 2, the data link layer, an HDLC type protocol is employed, the link access procedure on the D channel LAPD (CCITT Rec. Q. 920/1).

The ISDN Communication Controller PEB 2070 can be used in all ISDN applications involving establishment and maintenance of the data link connection in either the D channel or B channel. It also provides the interface to layer-1 functions controlled via the IOM which links the ICC to any transceiver or peripheral device. Depending on the interface mode, the ICC supports three serial interfaces and offers switching functions and  $_\mu P$  access to voice/ data channels.

The applications comprise:

- Use as a signaling controller for the D channel

- Access to the D channel for data transmission

- Source/ sink for secured B-channel data

and the target equipment include:

- ISDN terminal

- ISDN PABX (NT2) and Central Office (ET) line card

- ISDN packet switches

- "Intelligent" NT1.

#### **Terminal Applications**

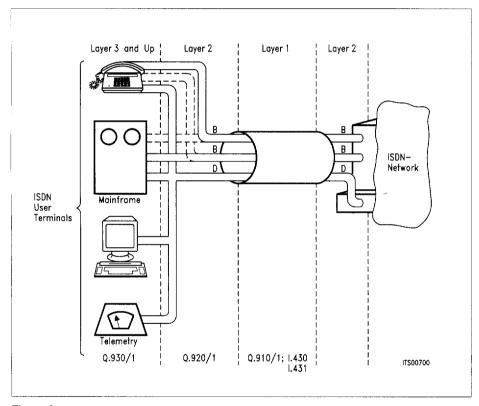

The concept of the ISDN basic access is based on two circuit-switched 64 kbit/s B channels and a message oriented 64 kbit/s D channel for packetized data, signaling and telemetry information.

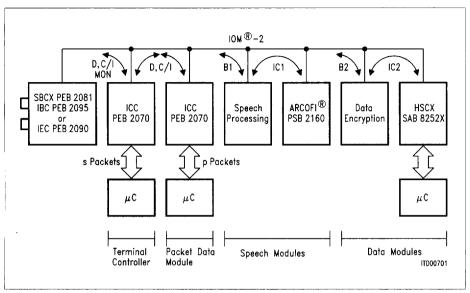

**Figure 3** shows an example of an integrated **multifunctional ISDN** terminal using the ICC. The transceiver provides the layer-1 connection to the transmission line, either an S or U interface, and is connected to the ICC and other, peripheral modules via the IOM-2 interface.

The D channel, containing signaling data and packet switched data, is processed by the ICC LAPD controller and routed via a parallel  $\mu P$  interface to the terminal processor. The high level support of the LAPD protocol which is implemented by the ICC allows the use of a low cost processor in cost sensitive applications.

The IOM-2 interface is used to connect diverse voice/data application modules:

- sources/ sinks for the D channel

- sources/ sinks for the B1 and B2 channels.

Figure 3 Example of ISDN Voice/Data Terminal

Different D-channel services (for different SAPI's) can be simply implemented by connecting an additional ICC in parallel to the first one, for instance for transmitting p-packets in the D channel.

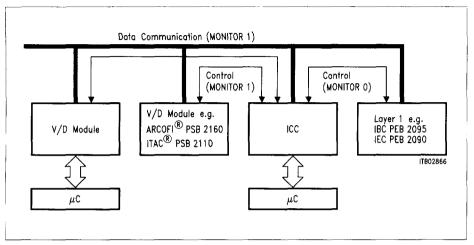

Up to eight ICCs may thus be connected to the D and C/I (Command/Indication) channels via the TIC bus. The ICCs handle contention autonomously.

Data transfer between the terminal controller and the different modules are done with the help of the IOM-2 MONITOR channel protocol. Each voice/data module can be accessed by an individual address. The same protocol enables the control of terminal modules that do not have an associated microcontroller (such as the Audio Ringing Codec Filter ARCOFI®: PSB 2160) and the programming of intercommunication inside the terminal. Two intercommunication channels IC1 and IC2 allow a 2 x 64 kbit/s transfer rate between voice/data modules.

In the example above (figure 3), one ICC is used for data packets in the D channel. A voice processor is connected to a programmable digital signal processing codec filter via IC1 and a data encryption module to a data device via IC2. B1 is used for voice communication, B2 for data communication.

The ICC ensures full upward compatibility with IOM-1 devices. It provides the additional strobe, clock and data lines for connecting standard combos or data devices via IOM, or serial SLD and SSI interfaces. The strobe signals and the switching of B channels is programmable.

### **Line Card Application**

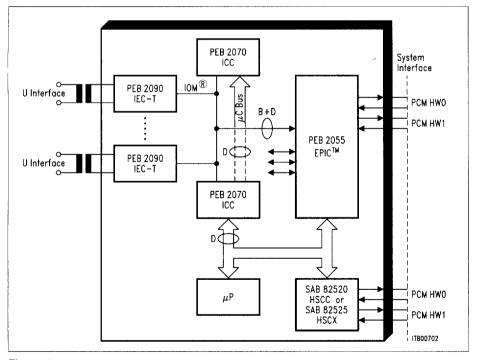

An example of the use of the ICC on an ISDN LT + ET line card (decentralized architecture) is shown in figure 4.

The transceivers (ISDN Cancellation Circuit IEC: PEB 2090) are connected to an Extended PCM Interface Controller (EPIC® PEB 2055) via an IOM interface.

This interface carries the control and data for up to eight subscribers using time division multiplexing. The ICCs are connected in parallel on IOM, one ICC per subscriber.

The EPIC performs dynamic B- and D-channel assignment on the PCM highways. Since this component supports four IOM interfaces, up to 32 subscribers may be accommodated.

#### 1.4.2 Other Applications

If programmed in non-ISDN mode, the ICC serial port B operates as an HDLC communication link without IOM frame structure. This allows the use of the ICC has a general purpose communication controller. The valid HDLC data is marked by a strobe signal on serial port B. Examples of the use of the ICC are: X.25 packet controllers, terminal adaptors, and packet transmission e.g. in primary rate/ DMI systems.

Figure 4 ISDN Line Card Implementation

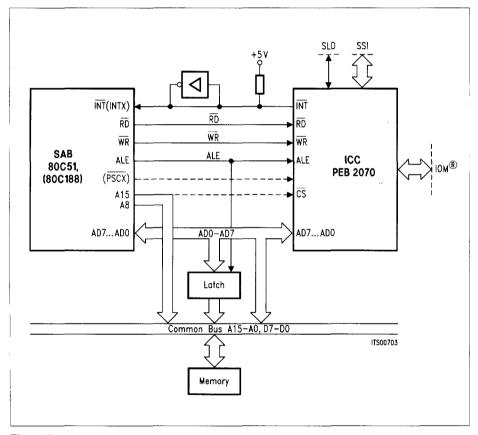

### 1.4.3 Microprocessor Environment

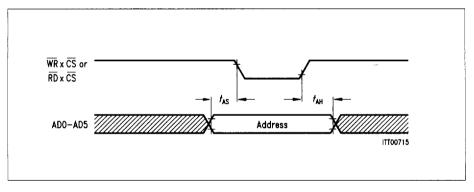

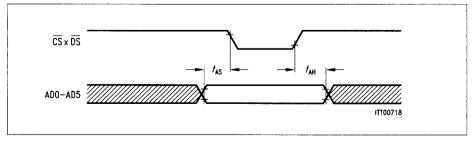

The ICC is especially suitable for cost-sensitive applications with single-chip microcontrollers (e.g. SAB 8048 / 8031 / 8051). However, due to its programmable micro interface and non-critical bus timing, if fits perfectly into almost any 8-bit microprocessor system environment. The microcontroller interface can be selected to be either of the Motorola type (with control signals  $\overline{CS}$ ,  $R/\overline{W}$ ,  $\overline{DS}$ ) of the Siemens/Intel non-multiplexed bus type (with control signals  $\overline{CS}$ ,  $\overline{WR}$ ,  $\overline{RD}$ ) or of the Siemens/Intel multiplexed address/data bus type ( $\overline{CS}$ ,  $\overline{WR}$ ,  $\overline{RD}$ , ALE).

Figure 5

Example of ICC Microcontroller Environment

### 2 Functional Description

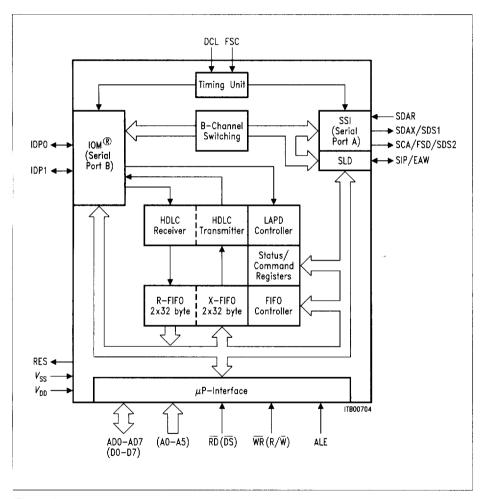

#### 2.1 General Functions and Device Architecture

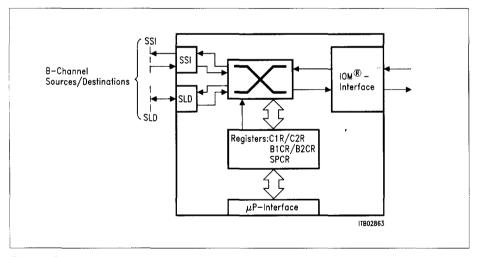

Figure 6

Architecture of the ICC

The functional block diagram in figure 6 shows the ICC to consist of:

- serial interface logic for the IOM and the SLD and SSI interfaces, with B-channel switching capabilities

- logic necessary to handle the D-channel messages (layer 2)

The latter consists of an HDLC receiver and an HDLC transmitter together with 64-byte deep FIFO's for efficient transfer of the messages to/ from the user's CPU.

In a special HDLC controller operating mode, the auto mode, the ICC processes protocol handshakes (I and S frames) of the LAPD (Link Access Procedure on the D channel) autonomously.

Control and MONITOR functions as well as data transfers between the user's CPU and the D and B channel are performed by the 8-bit parallel  $\mu P$  interface logic.

The IOM interface allows interaction between layer-1 and layer-2 functions. It implements D-channel collision resolution for connecting other layer-2 devices to the IOM interface, and the C/I and MONITOR channel protocols (IOM-1/IOM-2) to control peripheral devices. This function is called TIC-Bus-Access-Procedure.

The timing unit is responsible for the system clock and frame synchronization.

#### 2.2 Serial Interface Modes

The PEB 2070 can be used in different modes of operation:

- IOM-1 Mode

- IOM-2 Mode

- HDLC Controller Mode.

These modes are selected via bit IMS (Interface Mode Select) in ADF2 register and bits DIM2-0 (Digital Interface Mode) in MODE register. **See table 1**.

Table 1 Interface Modes

| IMS | DIM2 | Mode       |

|-----|------|------------|

| 0   | 0    | IOM-1 Mode |

| Ū   | 1    | HDLC Mode  |

| 1   | х    | IOM-2 Mode |

### 2.2.1 $IOM^{\circ}-1 Mode (IMS = 0, DIM2 = 0)$

Serial port B is used as the IOM-1 interface, which connects the ICC to layer-1 component.

The HDLC controller is always connected to the D channel of the IOM-1 interface.

Two additional serial interfaces are available in this mode, the Synchronous Serial Interface SSI (Serial Port A) and the Subscriber Line Datalink (SLD) interface.

The SSI is used especially in ISDN terminal applications for the connection of B-channel sources/sinks. It is available if timing mode 0 (Bit SPM = 0, SPCR register) is programmed.

#### The SLD is used:

- in ISDN terminal applications for the connection of SLD compatible B-channel devices

- in line card applications for the connection of a peripheral line board controller (e.g. PEB 2050).

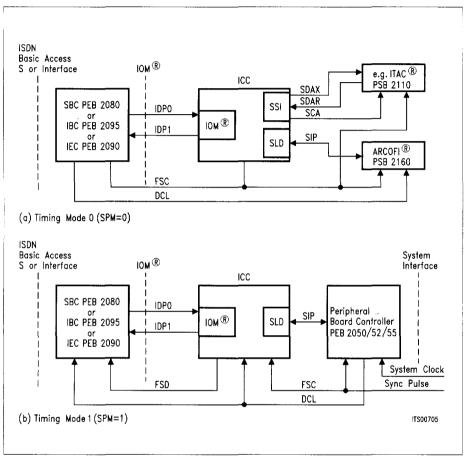

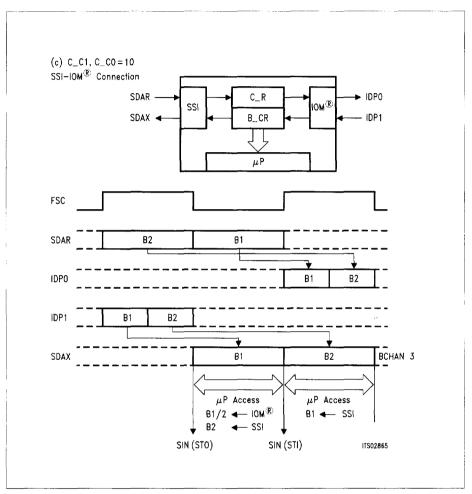

The connections of the serial interfaces in both terminal and exchange applications are shown in **figure 7**.

The SSI interface is only available in timing mode 0 (SPM = 0). Timing mode 1 (SPM = 1) is only applicable in exchange applications **figure 7b** and is used to minimize the B channel round-trip delay time for the SLD interface. Refer to **section 2.3.2**.

Figure 7 ICC Interfaces in IOM®-1 Mode

The characteristics of the IOM interface are determined by bits DIM1, 0 as shown in table 2.

Table 2 IOM®-1 Interface Mode Characteristics

| DIM1 | DIM0 | Characteristics                                                                                                                          |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | MONITOR channel upstream is used for TIC bus access.                                                                                     |

| 0    | 1    | MONITOR channel upstream is used for TIC bus access. Bit 3 of MONITOR channel downstream is evaluated to control D-channel transmission. |

| 1    | 0    | MONITOR channel is used for TIC bus access and for data transfer.                                                                        |

| 1    | 1    | MONITOR channel is used for TIC bus access, for data transfer and for D-channel access control.                                          |

### 2.2.2 IOM®-2 Mode (IMS = 1)

Serial port B is operated as an IOM-2 interface for the connection of layer-1 devices, and as a general purpose backplane bus in terminal equipment. The auxiliary serial SSI and SLD interfaces are not available in this case.

The functions carried out by the IOM are determined by bits SPCR:SPM (terminal mode/non-terminal mode) and DIM2-0, as shown in **table 3**.

Table 3 IOM®-2 Interface Mode Characteristics

| DIM2   | DIM1           | DIMO | Characteristics                                                                                                                                                    |

|--------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDLC i | n D channel:   |      | Last octet of IOM channel 2 is used for TIC bus access.                                                                                                            |

| 0      | 0              | 0    | Applicable in terminal mode (SPM = 0).                                                                                                                             |

| 0      | 0              | 1    | Last octet of IOM channel 2 is used for TIC bus access, bit 5 of last octet is evaluated to control D-channel transmission. Applicable in terminal mode (SPM = 0). |

| 0      | 1              | 0    | No TIC bus access and no S bus D-channel access control. Applicable in terminal and non-terminal mode.                                                             |

| 0      | 1              | 1    | Bit 5 of last octet is evaluated to control D-channel transmission. Applicable in terminal mode (SPM = 0).                                                         |

| HDLC i | n B or IC chan | nel: | No transmission/reception in D channel.                                                                                                                            |

| 1      | 1              | 0    | HDLC channel selected by ADF2:D1C2-0.                                                                                                                              |

Note: In IOM-2 terminal mode (SPM = 0, 12-byte IOM-2 frame), all DIM2 - 0 combinations are meaningful. When IOM-2 non-terminal mode is programmed (SPM = 1), the only meaningful combination is "10".

#### 2.2.3 HDLC Controller Mode (IMS = 0, DIM2 = 1)

In this case serial port B has no fixed frame structure, but is used as a serial HDLC port. The valid HDLC data is market by a strobe signal input via pin FSC. The data rate is determined by the clock input DLC (maximum 4096 Mbit/s). The characteristic of the serial port B are determined by bits DIM1, 0 as shown in **table 4**.

Table 4

HDLC Mode Characteristics

| DIM1 | DIMO | Characteristics        |

|------|------|------------------------|

| 0    | 0    | reserved               |

| 0    | 1    | FSC strobe active low  |

| 1    | 0    | FSC strobe active high |

| 1    | 1    | FSC strobe ignored     |

#### 2.3 Interfaces

The ICC serves three different user-oriented interface types:

- parallel processor interface to higher layer functions

- IOM interface: between layer 1 and 2, and as a universal backplane for terminals

- SSI and SLD interfaces for B-channel sources and destinations (in IOM-1 mode only).

#### 2.3.1 μP Interface

The ICC is programmed via an 8-bit parallel microcontroller interface. Easy and fast microprocessor access is provided by 8-bit address decoding on chip. The interface consists of 13 (18) lines and is directly compatible with multiplexed and non-multiplexed microcontroller interfaces (Siemens/Intel or Motorola type buses). The microprocessor interface signals are summarized in **table 5**.

Table 5 Interface of the ICC

| Pin No.<br>P-DIP | Pin No.<br>P-LCC | Symbol           | Input (I)<br>Output (O) | Function                                                                                                                                                |

|------------------|------------------|------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21<br>22         | 25<br>26         | AD0/D0           | I/O<br>I/O              | Multiplexed Bus Mode: Address/                                                                                                                          |

| 23               | 27               | AD1/D1<br>AD2/D2 | 1/0                     | Data bus. Transfers addresses from the µP system to the ICC and data                                                                                    |

| 24               | 28               | AD3/D3           | 1/0                     | between the µP system and the ICC.                                                                                                                      |

| 1                | 1                | AD4/D4           | 1/0                     | Detween the prosystem and the 100.                                                                                                                      |

| 2                | 2                | AD5/D5           | 1/0                     | Non Multiplexed Bus Mode: Data                                                                                                                          |

| 2<br>3           | 3                | AD6/D6           | 1/0                     | bus. Transfers data between the μP                                                                                                                      |

| 4                | 4                | AD7/D7           | I/O                     | system and the ICC.                                                                                                                                     |

| 17               | 21               | CS               | 1                       | Chip Select. A 0 "low" on this line selects the ICC for read/write operation.                                                                           |

| _                | 23               | R/W              | I                       | Read/Write. At 1 "high", identifies a valid μP access as a read operation. At 0, identifies a valid μP access as a write operation (Motorola bus mode). |

| 19               | 23               | WR               |                         | Write. This signal indicates a write operation (Siemens/Intel bus mode).                                                                                |

| _                | 24               | DS               | I                       | Data Strobe. The rising edge marks the end of a valid read or write                                                                                     |

| 20 .             | 24               | RD               |                         | operation (Motorola bus mode). <b>Read.</b> This signal indicates a read operation (Siemens/Intel bus mode).                                            |

### Interface of the ICC (cont'd)

| Pin No.<br>P-DIP | Pin No.<br>P-LCC | Symbol | Input (I)<br>Output (O) | Interrupt Request. The signal is activated when the ICC requests an interrupt. It is an open drain output.          |  |  |  |

|------------------|------------------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15               | 18               | ĪNT    | OD                      |                                                                                                                     |  |  |  |

| 16               | 20               | ALE    | 1                       | Address Latch Enable. A high on the line indicates an address on the external address bus (Multiplexed butyp only). |  |  |  |

|                  | 19               | A0     | I                       | Address bit 0 (Non-multiplexed bus type).                                                                           |  |  |  |

|                  | 5                | A1     | I                       | Address bit 1 (Non-multiplexed bus type).                                                                           |  |  |  |

|                  | 6                | A2     | I                       | Address bit 2 (Non-multiplexed bus type).                                                                           |  |  |  |

|                  | 11               | A3     | I                       | Address bit 3 (Non-multiplexed bus type).                                                                           |  |  |  |

|                  | 12               | A4     | I                       | Address bit 4 (Non-multiplexed bus type).                                                                           |  |  |  |

|                  | 13               | A5     | 1                       | Address bit 5 (Non-multiplexed bus type).                                                                           |  |  |  |

### 2.3.2 ISDN Oriented Modular (IOM®) Interface

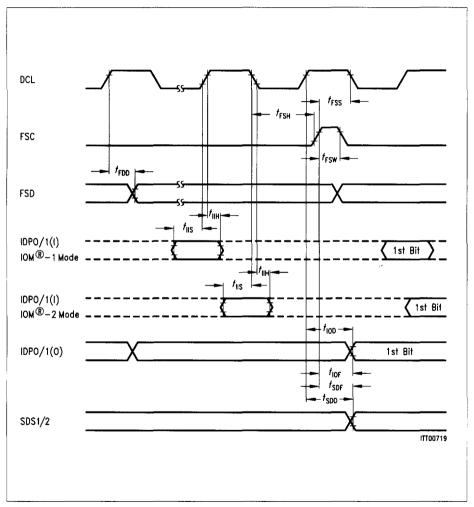

#### IOM®-1

This interface consists of one data line per direction (IOM Data Ports 0 and 1: IDP0,1). Three additional signals define the data clock (DCL) and the frame synchronization (FSC/FSD) at this interface. The data clock has a frequency of 512 kHz (twice the data rate) and the frame sync clock has a repetition rate of 8 kHz.

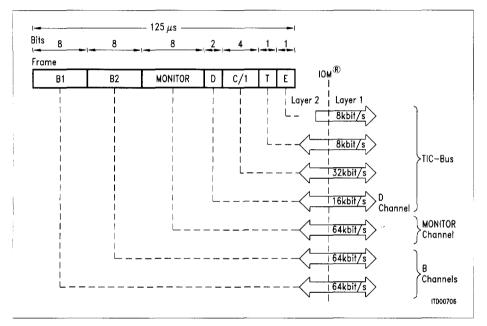

Via this interface four octets are transmitted per 125 μs frame (figure 8):

- The first two octets constitute the two 64 kbit/s B channels.

- The third octet is the MONITOR channel. It is used for the exchange of data using the IOM-1 MONITOR channel protocol which involves the E bit as a validation bit. In addition, it carries a bit which enables/inhibits the transmission of HDLC frames (IDP0) and it serves to arbitrate the access to the last octet. (IDP1).

The fourth octet is called the Telecom IC (TIC) bus because of the offered busing capability. It is constituted of the 16 kbit/s D channel (2 bits), a four-bit Command/Indication channel and the T and E bits. The C/I channel serves to control and MONITOR layer-1 functions (e.g. activation/deactivation of a transmission line...). The T bit is a transparent 8-kbit/s channel which can be accessed from the ICC, and the E bit is used in MONITOR byte transfer.

Figure 8 IOM®-1 Frame Structure

#### TIC Bus and Arbitration via MONITOR Channel

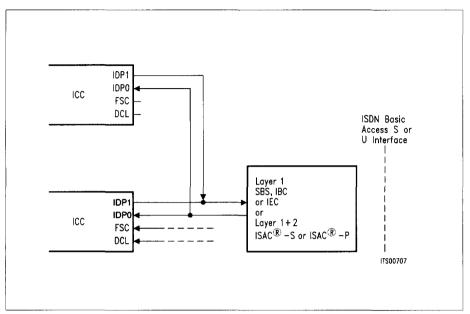

The arbitration mechanism implemented in the MONITOR channel allows the access of more than one (up to eight) ICC to the last octet of IOM (TIC). This capability is useful for the modular implementation of different ISDN services (different Service Access Points) e.g. in ISDN voice/data terminals. The IDP1 pins are connected together in a wired-or configuration, as shown in figure 9.

Figure 9 IOM® Bus (TIC Bus) Configuration

The arbitration mechanism is described in the following.

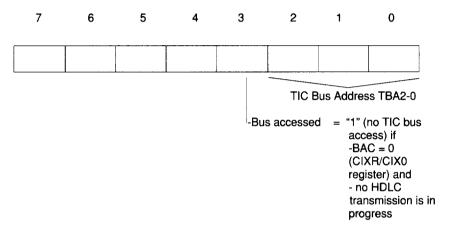

An access request to the TIC bus may either be generated by software ( $\mu P$  access to the C/I channel) or by the ICC itself (transmission of an HDLC frame). A software access request to the bus is effected by setting the BAC bit (CIXR/CIX0 register) to "1".

In the case of an access request, the ICC checks the bus accessed-bit (bit 3 of IDP1 MONITOR octet) for the status "bus free", which is indicated by a logical "1". If the bus is free, the ICC transmits its individual TIC bus address programmed in STCR register. The TIC bus is occupied by the device which is able to send its address error-free. If more than one device attempt to seize the bus simultaneously, the one with the lowest address value wins.

#### **MONITOR Channel Structure on IDP1**

When the TIC bus is seized by the ICC, the bus is identified to other devices as occupied via the IDP1 MONITOR channel bus accessed bit state "0" until the access request is withdrawn. After a successful bus access, the ICC is automatically set into a lower priority class, that is, a new bus access cannot be performed until the status "bus free" is indicated in two successive frames.

If none of the devices connected to the IOM interface request access to the D and C/l channels, the TIC bus address 7 will be present. The device with this address will therefore have access, by default, to the D and C/l channels.

Note: Bit BAC (CIXR/CIX0 register) should be reset by the  $\mu$ P when access to the C/I channel is no more requested, to grant other devices access to these channels.

#### **MONITOR Channel**

The MONITOR channel protocol for data transfer is described in section 2.4.5.

When the ICC is used in connection with an S interface layer-1 transceiver, an indication must be given to the ICC whether the D channel is available for transmission (TE applications with short passive or extended bus configuration).

This indication is assumed to be given in bit 3 "Stop/Go" (S/G) of the MONITOR input channel on IDP0. When a HDLC frame is to be transmitted in the D channel, the ICC automatically starts, proceeds with, or stops frame transmission according to the S/G bit value:

S/G = 1 : stopS/G = 0 : go

#### **MONITOR Channel Structure IDP0**

| 7 | 6 | 5 | 4 | 3   | 2 | 1 | . 0 |

|---|---|---|---|-----|---|---|-----|

| 1 | 1 | 1 | 1 | S/G | 1 | 1 | 1   |

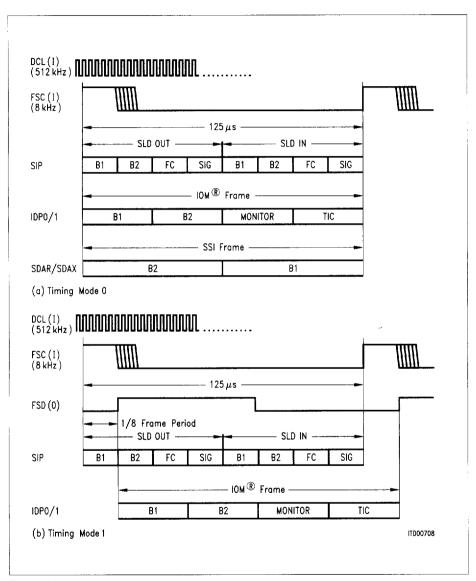

### IOM®-1 Timing

In IOM-1 mode, the ICC may be operated either in timing mode 0 or timing mode 1. The selection is via bit SPM in SPCR register.

Timing mode 0 (**SPM = 0**) is used in terminal applications. Timing mode 1 (**SPM = 1**) is only meaningful in exchange applications when the SLD is used. Programming timing mode 1 minimizes the B-channel round-trip delay time on the SLD interface.

In timing mode 0 the IOM frame begin is marked by a rising edge on the FSC input. It simultaneously marks the beginning of the SLD frame.

In timing mode 1 the IOM frame begins is marked by a rising edge on FSD output. The FSD output is delayed by the ICC by 1/8 th of a frame with respect to FSC (figure 10).

Figure 10 Interface Timing in IOM®-1 Mode

**Note:** The up-arrows show the position, where register contents are transferred to the sender, the down-arrows show the position, where the receiver transfers data to the registers.

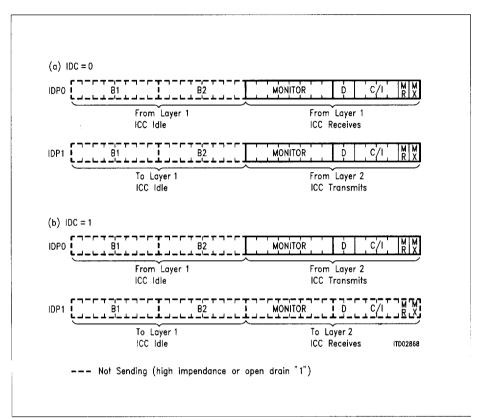

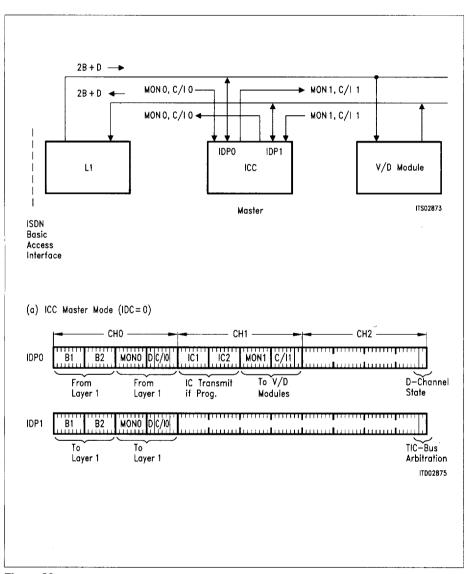

#### IOM®-2

The IOM-2 is a generalization and enhancement of the IOM-1. While the basic frame structure is very similar, IOM-2 offers further capacity for the transfer of maintenance information. In terminal applications, the IOM-2 constitutes a powerful backplane bus offering intercommunication and sophisticated control capabilities for peripheral modules.

The channel structure of the IOM-2 is depicted below.

#### Channel Structure of the IOM®-2

| B1 | B2 | MONITOR | D | C/I | MR |

|----|----|---------|---|-----|----|

|    |    |         |   |     |    |

#### MX

- The first two octets constitute the two 64 kbit/s B channels.

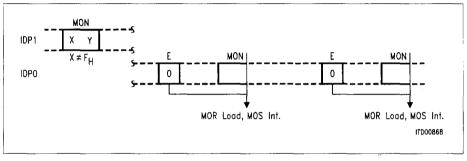

- The third octet is the MONITOR channel. It is used for the exchange of data between the ICC and the other attached device(s) using the IOM-2 MONITOR channel protocol.

- The fourth octet (control channel) contains

- two bits for the 16 kbit/s D channel

- a four-bit Command/Indication channel

- two bits MR and MX for supporting the MONITOR channel protocol.

In the case of an IOM-2 interface the frame structure depends on whether TE- or non-TE mode is selected, via bit SPM in SPCR register.

### Non-TE Timing Mode (SPM = 1)

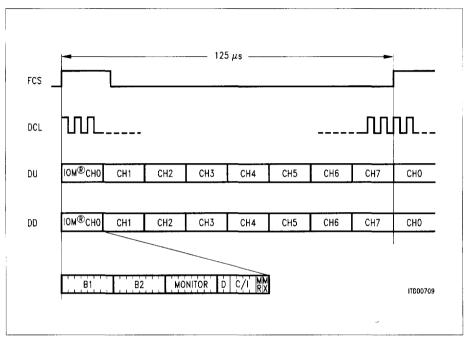

In this case the frame is a multiplex of eight IOM-2 channels (figure 11), each channel has the same structure.

Thus the data rate per subscriber connection (corresponding to one channel) is 256 kbit/s, whereas the bit rate is 2048 kbit/s. The IOM-2 interface signals are:

IDP0.1 : 2048 kbit/s

DCL : 4096 kHz input

FSC: 8 kHz input

Figure 11

Multiplexed Frame Structure of the IOM®-2 Interface in Non-TE Timing Mode

The ICC is assigned to one of the eight channels (0 to 7) via register programming.

This mode is used in ISDN exchange/line card applications.

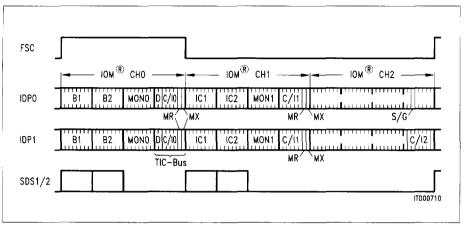

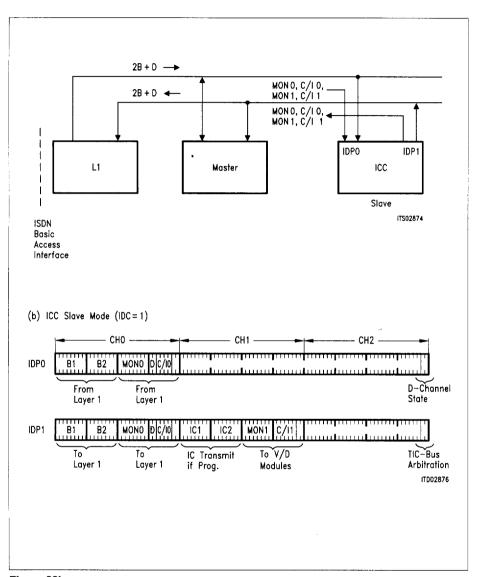

### TE Timing Mode (SPM = 0)

The frame is composed of three channels (figure 11):

- Channel 0 contains 144 kbit/s (for 2B + D) plus MONITOR and command/indication channels for layer-1 devices.

- Channel 1 contains two 64-kbit/s intercommunication channels plus MONITOR and command/indication channels for other IOM-2 devices.

- Channel 2 is used for enabling/inhibiting the transmission of HDLC frames. This bit is typically generated by an S-bus transceiver (stop/go: bit 5, or 3rd MSB of the last octet on IDP0). On IDP1, bits 2 to 5 of the last octet are used for TIC bus access arbitration.

As in the IOM-1 case (**figure 9**), up to eight ICCs can access the TIC bus (D and C/I channels). The bus arbitration mechanism is identical to that described previously, except that it involves bits 2 to 5 in channel 2.

Figure 12 Definition of the IOM®-2 Channels in Terminal Timing Mode

The IOM-2 signals are:

IDP0.1

768 kbit/s

FSC 8 kHz input.

1536 kHz input

In addition, to support standard combos/data devices the following signals are generated as

outputs:

DCL

SDS1/2 : 8 kHz programmable data strobe signals for selecting one or both B/IC

channel(s).

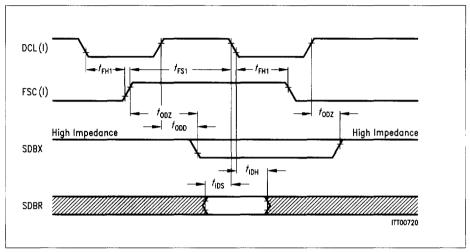

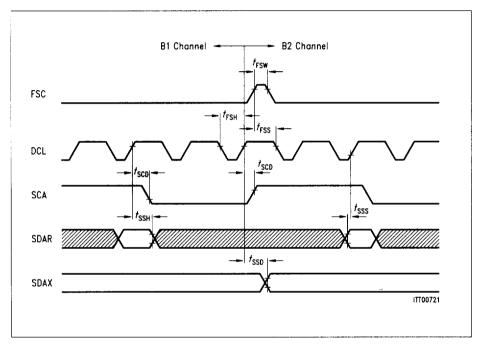

#### 2.3.3 SSI (Serial Port A)

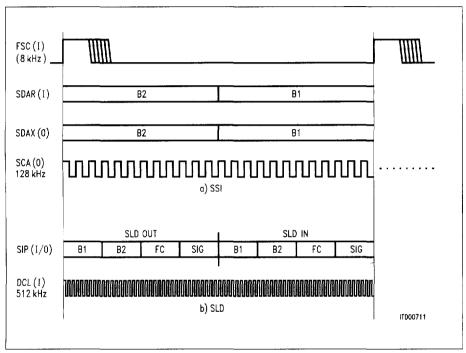

The SSI (Serial Synchronous Interface) is available in IOM-1 interface mode. Timing mode 0 (SPM = 0) has to be programmed.

The serial port SSI has a data rate of 128 kbit/s. It offers a full duplex link for B channels in ISDN voice/data terminals. Examples: serial synchronous transceiver devices (USART's. HSCX SAB 82525, ITAC PSB 2110, ...), and CODEC filters.

The port consists of one data line in each direction (SDAX and SDAR) and the 128-kHz clock output (SCA). The beginning of B2 is marked by a rising edge on FSC, see figure 12.

The μC system has access to B-channel data via the ICC registers BCR1/2 and BCX1/2.

The uC access must be synchronized to the serial transmission by means of the Synchronous Transfer Interrupt (STCR see chapter 4).

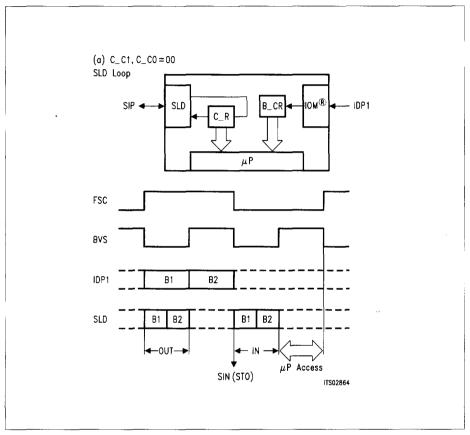

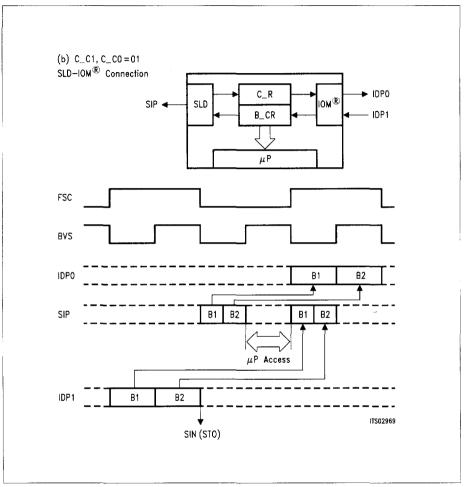

#### 2.3.4 SLD

The SLD is available in IOM-1 interface mode.

Figure 13 SSI (a) and SLD (b) Interface Lines

The standard SLD interface is a three-wire interface with a 512-kHz clock input (DCL), an 8-kHz frame direction signal input (FSC), and a serial ping-pong data lead (SIP) with an effective full duplex data rate of 256 kbit/s.

The frame is composed of four octets per direction. Octets 1 and 2 contain the two B channels, octet 3 is a feature control byte, and octet 4 is a signaling byte (figure 13).

The SLD interface can be used in:

Terminal applications as a full duplex time-multiplexed (ping-pong) connection to B-channel sources/destinations. CODEC filters, such as the SICOFI® (PEB 2060) or the ARCOFI® (PSB 2160) as well as other SLD compatible voice/data modules may be connected directly to the ICC as depicted in figure 13a. Terminal specific functions have to be deselected (TSF = 0), so that pin SIP/EAW takes on its proper function as SLD data line. Moreover, in TE applications timing mode 0 has to be programmed.

Digital exchange applications as a full duplex time-multiplexed connection to convey the B channels between the layer-1 devices and a Peripheral Board Controller (e.g. PBC PEB 2050 or PIC PEB 2052), which performs time-slot assignment on the PCM highways, forming a system interface to a switching network (figure 13b).

Timing mode 1 (SPM = 1) can be programmed in order to minimize the B-channel round-trip delay.

The  $\mu$ C system has access to B-channel data, the feature control byte and the signaling byte via the ICC registers:

- CFCR and SFCX  $\longrightarrow$  FC

- SSCR and SSCX → SIG

The  $\mu P$  access to C1R, C2R, SFCR, SFCX, SSCR and SSCX must be synchronized to the serial transmission by means of the Synchronous Transfer Interrupt (STCR) and the BVS-bit (STAR).

#### 2.4 Individual Functions

### 2.4.1 Layer-2 Functions for HDLC

The HDLC controller in the ICC is responsible for the data link layer using HDLC/SDLC based protocols.

The ICC can be made to support that data link layer to a degree that best suits system requirements. When programmed in auto mode, it handles elements of procedure of an acknowledged, balanced class of HDLC protocol autonomously (window size equal to "1"). Multiple links may be handled simultaneously due to the address recognition capabilities, as explained in **section 2.4.1.1**.

The ICC supports point-to-point protocols such as LAPB (Link Access Procedure Balanced) used in X.25 networking.

For ISDN, one particularly important protocol is the Link Access Procedure for the D channel (LAPD).

LAPD, layer 2 of the ISDN D-channel protocol (CCITT I.441) includes functions for:

- Provision of one or more data link connections on a D channel (multiple LAP).

Discrimination between the data link connections is performed by means of a data link connection identifier (DLCI = SAPI + TEI)

- HDLC-framing

- Application of a balanced class of procedure in point-multipoint configuration.

The simplified block diagram in **figure 6** shows the functional blocks of the ICC which support the LAPD protocol.

The HDLC transceiver in the ICC performs the framing functions used in HDLC/SDLC based communication: flag generation/recognition, bit stuffing, CRC check and address recognition.

The FIFO structure with two 64-byte pools for transmit and receive directions and an intelligent FIFO controller permit flexible transfer of protocol data units to and from the  $\mu$ C system.

### 2.4.1.1 Message Transfer Modes

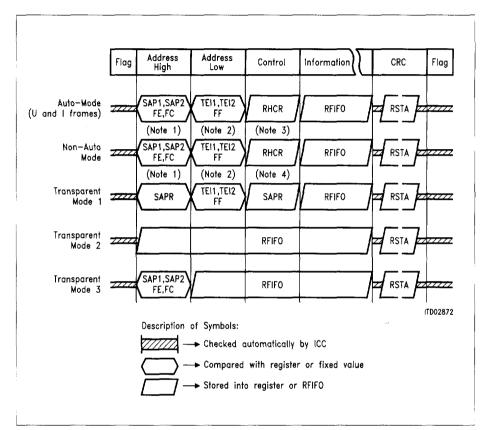

The HDLC controller can be programmed to operate in various modes, which are different in the treatment of the HDLC frame in receive direction. Thus, the receive data flow and the address recognition features can be programmed in a flexible way, to satisfy different system requirements.

In the auto mode the ICC handles elements of procedure of the LAPD (S and I frames) according to CCITT I.441 fully autonomously.

For the address recognition the ICC contains four programmable registers for individual SAPI and TEI values SAP1-2 and TEI1-2, plus two fixed values for "group" SAPI and TEI, SAPG and TEIG.

There are 5 different operating modes which can be set via the MODE register:

Auto mode (MDS2, MDS1 = 00)

Characteristics:

- Full address recognition (1 or 2 bytes).

- Normal (mod 8) or extended (mod 128) control field format

- Automatic processing of numbered frames of an HDLC procedure (see 2.4.1.2).

If a 2-byte address field is selected, the high address byte is compared with the fixed value FEH or FCH (group address) as well as with two individually programmable values in SAP1 and SAP2 registers. According to the ISDN LAPD protocol, bit 1 of the high byte address will be interpreted as COMMAND/RESPONSE bit (C/R) dependent on the setting of the CRI bit in SAP1, and will be excluded from the address comparison.

Similarly, the low address byte is compared with the fixed value FFH (group TEI) and two compare values programmed in special registers (TEI1, TEI2). A valid address will be recognized in case the high and low byte of the address field match one of the compare values. The ICC can be called (addressed) with the following address combinations:

- SAP1/TFI1

- SAP1/FFH

- SAP2/TEI2

- SAP2/FFH

- FEH(FCH)/TEI1

- FEH(FCH)/TEI2

- FEH(FCH)/FFH

Only the logical connection identified through the address combination SAP1, TEI1 will be processed in the auto mode, all others are handled as in the non-auto mode. The logical connection handled in the auto mode must have a window size 1 between transmitted and acknowledged frames. HDLC frames with address fields that do not match with any of the address combinations, are ignored by the ICC.

In case of a 1-byte address, TEI1 and TEI2 will be used as compare registers. According to the X.25 LAPB protocol, the value in TEI1 will be interpreted as COMMAND and the value in TEI2 as RESPONSE.

The control field is stored in RHCR register and the I field in RFIFO. Additional information is available in RSTA.

Non-Auto Mode (MDS2, MDS1 = 01)

Characteristics: Full address recognition (1 or 2 bytes)

Arbitrary window sizes

All frames with valid addresses (address recognition identical to auto mode) are accepted and the bytes following the address are transferred to the  $\mu P$  via RHCR and RFIFO. Additional information is available in RSTA.

Transparent Mode 1 (MDS2, MDS1, MDS0 = 101).

Characteristics: TEI recognition

A comparison is performed only on the second byte after the opening flag, with TEI1, TEI2 and group TEI (FFH). In case of a match, the first address byte is stored in SAPR, the (first byte of the) control field RHCR, and the rest of the frame in the RFIFO. Additional information is available in RSTA

Transparent Mode 2 (MDS2, MDS1, MDS0 = 110).

Characteristics: non address recognition.

Every received frame is stored in RFIFO (first byte after opening flag to CRC field). Additional information can be read from RSTA.

Transparent Mode 3 (MDS2, MDS1, MDS0 = 111)

Characteristics: SAPI recognition

A comparison is performed on the first byte after the opening flag with SAP1, SAP2 and group SAPI (FE/FCH). In the case of a match, all the following bytes are stored in RFIFO. Additional information can be read from RSTA.

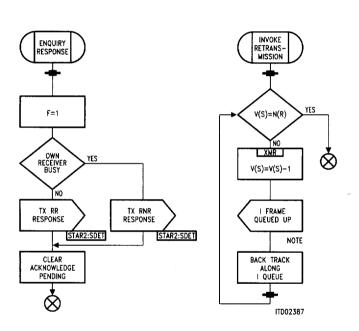

#### 2.4.1.2 Protocol Operations (auto mode)

In addition to address recognition all S and I frames are processed in hardware in the auto mode. The following functions are performed:

- update of transmit and receive counter

- evaluation of transmit and receive counter

- processing of S commands

- flow control with RR/RNR

- response generation

- recognition of protocol errors

- transmission of S commands, if an acknowledgment is not received

- continuous status guery of remote station after RNR has been received

- programmable timer/repeater functions.

The processing of frames in auto mode is described in detail in section 2.4.8.

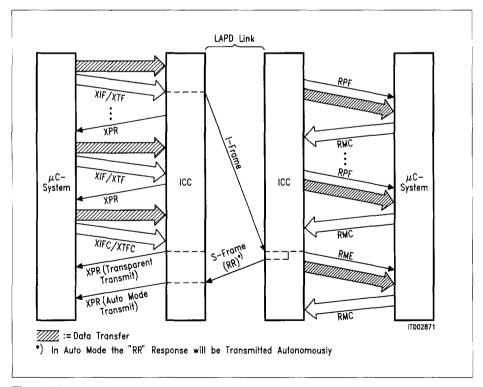

### 2.4.1.3 Reception of Frames

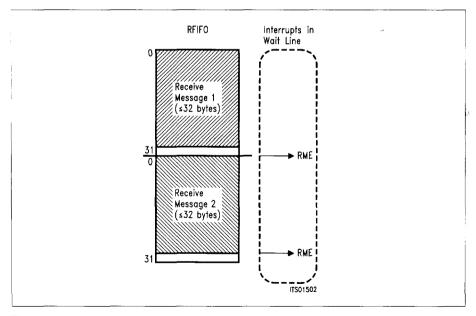

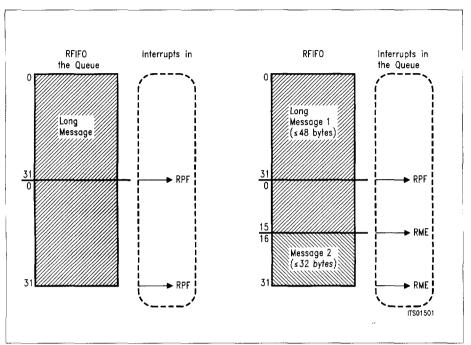

A 2x32-byte FIFO buffer (receive pools) is provided in the receive direction.

The control of the data transfer between the CPU and the ICC is handled via interrupts.

There are two different interrupt indications concerned with the reception of data:

- RPF (Receive Pool Full) interrupt, indicating that a 32-byte block of data can be read from the RFIFO and the received message is not yet complete.

- RME (Receive Message End) interrupt, indicating that the reception of one message is completed, i.e. either

- one message ≤ 32 bytes, or

- the last part of a message ≥ 32 bytes

is stored in the RFIFO.

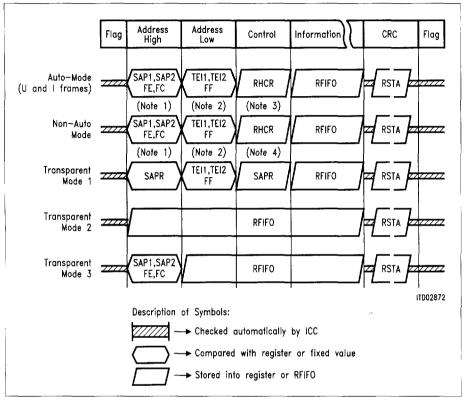

Depending on the message transfer mode the address and control fields of received frames are processed and stored in the receive FIFO or in special registers as depicted in figure 14.

The organization of the RFIFO is such that, in the case of short ( $\leq$  32 bytes), successive messages, up to two messages with all additional information can be stored. The contents of the RFIFO would be, for example, as shown in **figure 15**.

Figure 14

Contents of RFIFO (short message)

Figure 15 Receive Data Flow

- Note 1 Only if a 2-byte address field is defined (MDS0 = 1 in MODE register).

- Note 2 Comparison with Group TEI (FF<sub>H</sub>) is only made if a 2-byte address field is defined (MDS0 = 1 in MODE register).

- Note 3 In the case of an extended, modulo 128 control field format (MCS = 1 in SAP2 register) the control field is stored in RHCR in compressed form (I frames).

- Note 4 In the case of extended control field, only the first byte is stored in RHCR, the second in RFIFO.

When 32 bytes of a message longer than that are stored in RFIFO, the CPU is prompted to read out the data by an RPF interrupt. The CPU must handle this interrupt before more than 32 additional bytes are received, which would cause a "data overflow" (figure 16). This corresponds to a maximum CPU reaction time of 16 ms (data rate 16 kbit/s).

After a remaining block of less than or equal to 16 bytes has been stored, it is possible to store the first 16 bytes of a new message (see figure 16b).

The internal memory is now full. The arrival of additional bytes will result in "data overflow" and a third new message in "frame overflow".

The generated interrupts are inserted together with all additional information into a wait line to be individually passed to the CPU.

After an RPF or RME interrupt has been processed, i.e. the received data has been read from the RFIFO, this must be explicitly acknowledged by the CPU issuing a RMC (Receive Message Complete) command.

The ICC can then release the associated FIFO pool for new data. If there is an additional interrupt in the wait line it will be generated after the RMC acknowledgment.

Figure 16 Contents of RIFIFO (long message)

Information about the received frame is available for the  $\mu P$  when the RME interrupt is generated, as shown in **table 6**.

Table 6

Receive Information at RME Interrupt

| Information                                                   | Register     | Bit           | Mode                                                                                         |  |

|---------------------------------------------------------------|--------------|---------------|----------------------------------------------------------------------------------------------|--|

| First byte after<br>flag (SAPI of<br>LAPD address<br>field)   | SAPR         | _             | Transparent mode 1                                                                           |  |

| Control field                                                 | RHCR         | -             | Auto mode, I (modulo 8) and U frames                                                         |  |

| Compressed control field                                      | RHCR         | -             | Auto mode, I frames (modulo 128)                                                             |  |

| 2 <sup>nd</sup> byte after                                    | RHCR         | -             | Non-auto mode, 1-byte address field                                                          |  |

| 3 <sup>rd</sup> byte after                                    | RHCR         | _             | Non-auto mode, 2-byte address field<br>Transparent mode 1                                    |  |

| Type of frame<br>(Command/<br>Response)                       | STAR         | C/R           | Auto mode, 2-byte address field<br>Non-auto mode, 2-byte address field<br>Transparent mode 3 |  |

| Recognition of<br>SAPI                                        | STAR         | SA1-0         | Auto mode, 2-byte address field<br>Non-auto mode, 2-byte address field<br>Transparent mode 3 |  |

| Recognition of TEI                                            | STAR         | TA            | All expect Transparent mode 2,3                                                              |  |

| Result of CRC check (correct/ incorrect)                      | STAR         | CRC           | ALL                                                                                          |  |

| Data available in RFIFO (yes/no)                              | STAR         | RDA           | ALL                                                                                          |  |

| Abort condition detected (yes/no)                             | STAR         | RAB           | ALL                                                                                          |  |

| Data overflow<br>during recep-<br>tion of a frame<br>(yes/no) | STAR         | RDO           | ALL                                                                                          |  |

| Number of<br>bytes recei-<br>ved in RFIFO                     | RBCL         | RBC4-0        | ALL                                                                                          |  |

| Message<br>length                                             | RBCL<br>RBCH | RBC11-<br>50V | ALL                                                                                          |  |

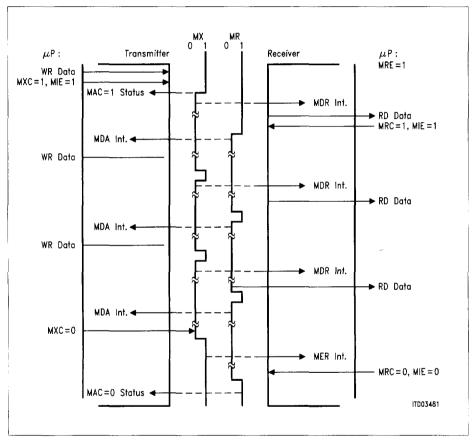

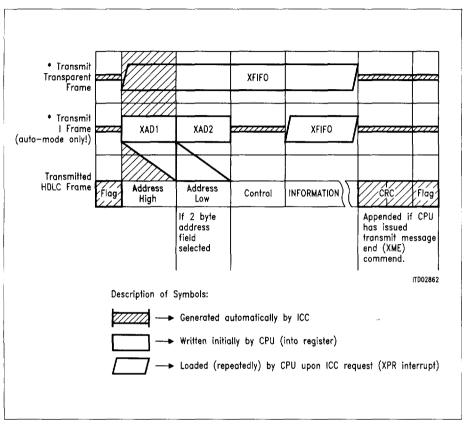

#### 2.4.1.4 Transmission of Frames

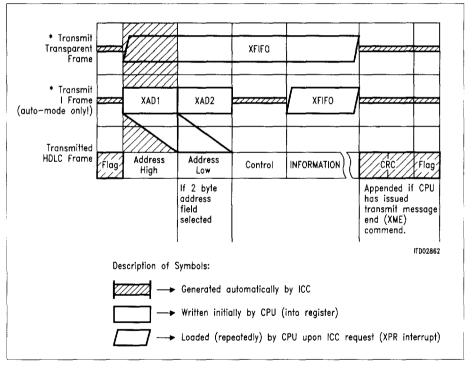

A 2x32 byte FIFO buffer (transmit pools) is provided in the transmit direction.

If the transmit pool is ready (which is true after an XPR interrupt or if the XFW bit in STAR is set), the CPU can write a data block of up to 32 bytes to the transmit FIFO. After this, data transmission can be initiated by command.

Two different frame types can be transmitted:

- Transparent frames (command: XTF), or

- I frames (command: XIF)

as shown in figure 17.

Figure 17 Transmit Data Flow

For transparent frames, the whole frame including address and control field must be written to the XFIFO.

The transmission of **I frames** is possible only if the ICC is operating in the auto mode. The address and control field is autonomously generated by the ICC and appended to the frame, only the data in the information field must be written to the XFIFO.

If a 2-byte address field has been selected, the ICC takes the contents of the XAD 1 register to build the high byte of the address field, and the contents of the XAD 2 register to build the low byte of the address field.

Additionally the C/R bit (bit 1 of the high byte address, as defined by LAPD protocol) is set to "1" or "0" dependent on whether the frame is a command or a response.

In the case of a 1-byte address, the ICC takes either the XAD 1 or XAD 2 register to differentiate between command or response frame (as defined by X.25 LAP B).

The control field is also generated by the ICC including the receive and send sequence number and the poll/final (P/F) bit. For this purpose, the ICC internally manages send and receive sequence number counters.

In the auto mode, S frames are sent autonomously by the ICC. The transmission of U frames, however, must be done by the CPU. U frames must be sent as transparent frames (XTF), i.e. address and control field must be defined by the CPU.

Once the data transmission has been initiated by command (XTF or XIF), the data transfer between CPU and ICC is controlled by interrupts.

The ICC repeatedly requests another data packet or block by means of an XPR interrupt, every time no more than 32 bytes are stored in the XFIFO.

The processor can then write further data to the XFIFO and enable the continuation of frame transmission by issuing an XIF/XTF command.

If the data block which has been written last to the XFIFO completes the current frame, this must be indicated additionally by setting the XME (Transmit Message End) command bit. The ICC then terminates the frame properly by appending the CRC and closing flag.

If the CPU fails to respond to an XPR interrupt within the given reaction time, a data underrun condition occurs (XFIFO holds no further valid data). In this case, the ICC automatically aborts the current frame by sending seven consecutive "ones" (ABORT sequence).

The CPU is informed about this via an XDU (Transmit Data Underrun) interrupt.

It is also possible to abort a message by software by issuing an XRES (Transmitter RESet) command, which causes an XPR interrupt.

After an end of message indication from the CPU (XME command), the termination of the transmission operation is indicated differently, depending on the selected message transfer mode and the transmitted frame type.

If the ICC is operating in the auto mode, the window size (= number of outstanding unacknowledged frames) is limited to 1; therefore an acknowledgment is expected for every I frame sent with an XIF command. The acknowledgment may be provided either by a received S or I frame with corresponding receive sequence number (see figure 14).

If no acknowledgment is received within a certain time (programmable), the ICC requests an acknowledgment by sending an S frame with the poll bit set (P = 1) (RR or RNR). If no response is received again, this process is repeated in total CNT times (retry count, programmable via TIMR register).

The termination of the transmission operation may be indicated either with:

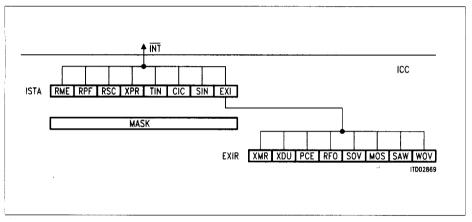

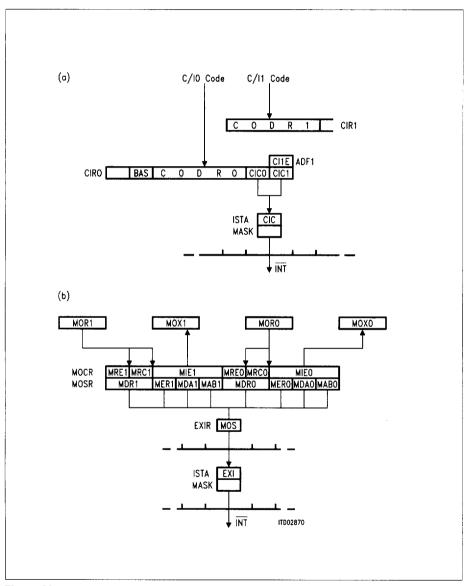

- XPR interrupt, if a positive acknowledgment has been received,