# FAN5400/FAN5401/FAN5402/FAN5403/FAN5404/FAN5405 USB-Compliant Single-Cell Li-Ion Switching Charger with USB-OTG Boost Regulator

### **Features**

- Fully Integrated, High-Efficiency Charger for Single-Cell Li-Ion and Li-Polymer Battery Packs

- Faster Charging than Linear

- Charge Voltage Accuracy: ±0.5% at 25°C

±1% from 0 to 125°C

- ±5% Input Current Regulation Accuracy

- ±5% Charge Current Regulation Accuracy

- 20 V Absolute Maximum Input Voltage

- 6 V Maximum Input Operating Voltage

- 1.25 A Maximum Charge Rate

- Programmable through High-Speed I<sup>2</sup>C Interface (3.4 Mb/s) with Fast Mode Plus Compatibility

- Input Current

- Fast-Charge / Termination Current

- Charger Voltage

- Termination Enable

- 3 MHz Synchronous Buck PWM Controller with Wide Duty Cycle Range

- Small Footprint 1 μH External Inductor

- Safety Timer with Reset Control

- 1.8 V Regulated Output from VBUS for Auxiliary Circuits

- Weak Input Sources Accommodated by Reducing Charging Current to Maintain Minimum VBUS Voltage

- Low Reverse Leakage to Prevent Battery Drain to VBUS

- 5 V, 300 mA Boost Mode for USB OTG for 2.5 to 4.5 V Battery Input

# **Applications**

- Cell Phones, Smart Phones, PDAs

- Tablet, Portable Media Players

- Gaming Device, Digital Cameras

All trademarks are the property of their respective owners.

# **Description**

The FAN5400 family (FAN540x) combines a highly integrated switch-mode charger, to minimize single-cell Lithium-ion (Li-ion) charging time from a USB power source, and a boost regulator to power a USB peripheral from the battery.

The charging parameters and operating modes are programmable through an I<sup>2</sup>C Interface that operates up to 3.4 Mbps. The charger and boost regulator circuits switch at 3 MHz to minimize the size of external passive components.

The FAN540X provides battery charging in three phases: conditioning, constant current, and constant voltage.

To ensure USB compliance and minimize charging time, the input current is limited to the value set through the I<sup>2</sup>C host. Charge termination is determined by a programmable minimum current level. A safety timer with reset control provides a safety backup for the I<sup>2</sup>C host.

The integrated circuit (IC) automatically restarts the charge cycle when the battery falls below an internal threshold. If the input source is removed, the IC enters a high-impedance mode with leakage from the battery to the input prevented. Charge status is reported back to the host through the I<sup>2</sup>C port. Charge current is reduced when the die temperature reaches 120°C.

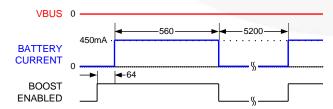

The FAN540X can operate as a boost regulator on command from the system. The boost regulator includes a soft-start that limits inrush current from the battery.

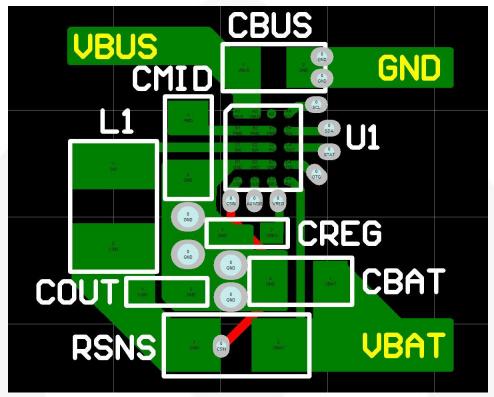

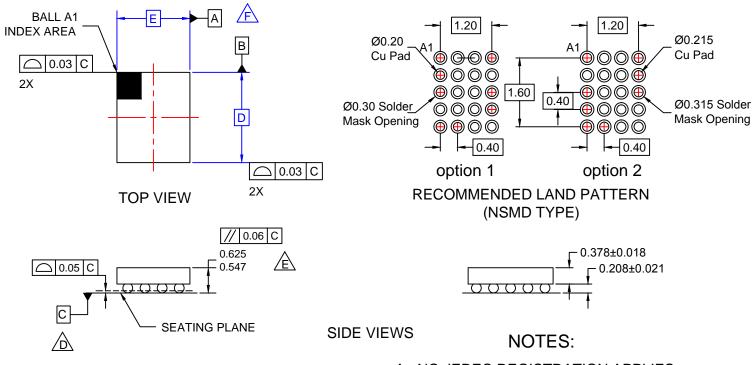

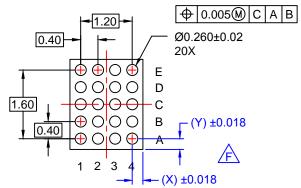

The FAN540X is available in a 1.96 x 1.87 mm, 20-bump, 0.4 mm pitch, WLCSP package.

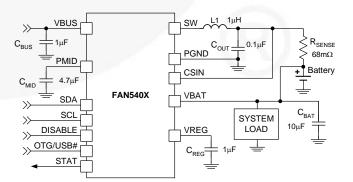

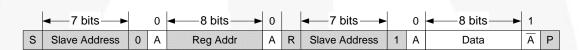

Figure 1. Typical Application (FAN5403-05 Pin Out)

# **Ordering Information**

| Part Number                | Temperature Range | Package                                         | PN Bits: IC_INFO[4:3] | Packing Method |

|----------------------------|-------------------|-------------------------------------------------|-----------------------|----------------|

| FAN5400UCX                 | -40 to 85°C       |                                                 | 01                    | Tape and Reel  |

| FAN5401UCX                 | -40 to 85°C       |                                                 | 00                    | Tape and Reel  |

| FAN5402UCX                 | -40 to 85°C       | 20-Bump, Wafer-<br>Level Chip-Scale             | 01                    | Tape and Reel  |

| FAN5403UCX                 | -40 to 85°C       | Package (WLCSP),                                | 10                    | Tape and Reel  |

| FAN5403BUCX <sup>(1)</sup> | -40 to 85°C       | 0.4 mm Pitch,<br>Estimated Size: 1.96 x 1.87 mm | 10                    | Tape and Reel  |

| FAN5404UCX                 | -40 to 85°C       |                                                 | 11                    | Tape and Reel  |

| FAN5405UCX                 | -40 to 85°C       |                                                 | 10                    | Tape and Reel  |

| FAN5405BUCX <sup>(1)</sup> | -40 to 85°C       |                                                 | 10                    | Tape and Reel  |

#### Note:

**Table 1. Feature Comparison Summary**

| Part<br>Number | PN Bits:<br>REG3[4:3] | Slave<br>Address | Automatic<br>Charge | Special<br>Charger <sup>(2)</sup> | Safety<br>Limits | Battery<br>Absent<br>Behavior | E2 Pin      | VREG<br>(E3 Pin) |   |   |      |

|----------------|-----------------------|------------------|---------------------|-----------------------------------|------------------|-------------------------------|-------------|------------------|---|---|------|

| FAN5400        | 01                    | 1101011          | Yes                 | No                                | No               | OFF                           | AUXPWR      |                  |   |   |      |

| FAN5401        | 00                    | 1101011          | No                  | No                                | No               | OFF                           | (Connect to | `                | ` | ` | PMID |

| FAN5402        | 01                    | 1101011          | Yes                 | No                                | No               | ON                            | VBAT)       | 1                |   |   |      |

| FAN5403        | 10                    | 1101011          | Yes                 | Yes                               | Yes              | OFF                           |             |                  |   |   |      |

| FAN5404        | 11                    | 1101011          | No                  | Yes                               | Yes              | OFF                           | DISABLE     | 1.8V             |   |   |      |

| FAN5405        | 10                    | 1101010          | Yes                 | Yes                               | Yes              | ON                            |             |                  |   |   |      |

#### Note

**Table 2. Recommended External Components**

| Component        | Description                   | Vendor                                        | Parameter        | Тур. | Unit |

|------------------|-------------------------------|-----------------------------------------------|------------------|------|------|

| L1               | 4 11 2007 4 2 4 2040          | Murata: LQM2MPN1R0M                           | L                | 1.0  | μН   |

| LI               | 1 μH, 20%, 1.3 A, 2016        | or Equivalent                                 | DCR (Series R)   | 85   | mΩ   |

| Сват             | 10 μF, 20%, 6.3 V, X5R, 0603  | Murata: GRM188R60J106M<br>TDK: C1608X5R0J106M | С                | 10   | μF   |

| C <sub>MID</sub> | 4.7 μF, 10%, 6.3 V, X5R, 0603 | Murata: GRM188R60J475K<br>TDK: C1608X5R0J475K | C <sup>(3)</sup> | 4.7  | μF   |

| C <sub>BUS</sub> | 1.0 μF, 10%, 25 V, X5R, 0603  | Murata GRM188R61E105K<br>TDK:C1608X5R1E105M   | С                | 1.0  | μF   |

#### Note:

3. 6.3 V rating is sufficient for C<sub>MID</sub> since PMID is protected from over-voltage surges on VBUS by Q3 (Figure 3).

<sup>1.</sup> FAN5403BUCX and FAN5405BUCX Includes backside lamination

<sup>2.</sup> Special charger is a current limited charger that is not a USB compliant source.

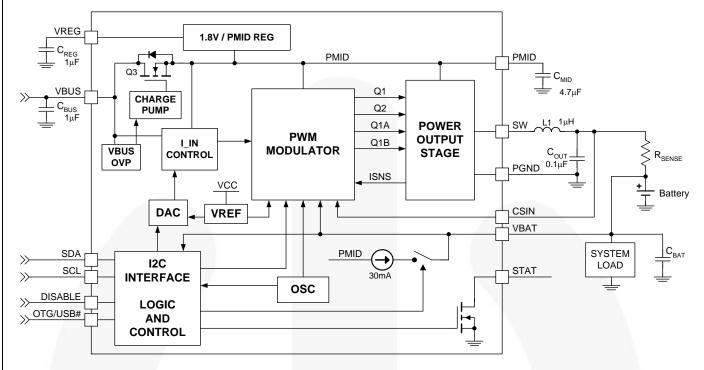

# **Block Diagram**

Figure 2. IC and System Block Diagram

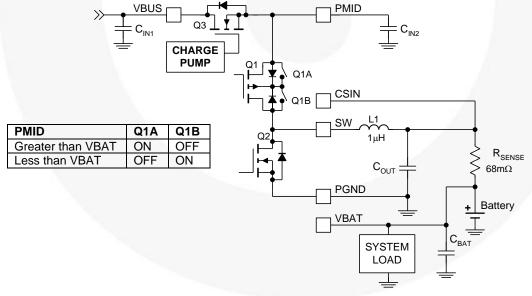

Figure 3. Power Stage

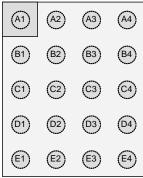

# **Pin Configuration**

**Top View**

[5]

[64]

[63]

[64]

[64]

[63]

(A4)

(B4)

(C4)

(A3)

(B3)

(C3)

(A2)

(B2)

(C2)

(D2)

(E2)

**Bottom View**

(A1)

(B1)

(C1)

(D1)

(E1)

Figure 4. WLCSP-20 Pin Assignments

# **Pin Definitions**

| Pin#   | Name    | Part #                          | Description                                                                                                                                                                                                                                              |

|--------|---------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2 | VBUS    | ALL                             | Charger Input Voltage and USB-OTG output voltage. Bypass with a 1 $\mu F$ capacitor to PGND.                                                                                                                                                             |

| А3     | NC      | ALL                             | No Connect. No external connection is made between this pin and the IC's internal circuitry.                                                                                                                                                             |

| A4     | SCL     | ALL                             | I <sup>2</sup> C Interface Serial Clock. This pin should not be left floating.                                                                                                                                                                           |

| B1-B3  | PMID    | ALL                             | <b>Power Input Voltage</b> . Power input to the charger regulator, bypass point for the input current sense, and high-voltage input switch. Bypass with a minimum of 4.7 $\mu$ F, 6.3 V capacitor to PGND.                                               |

| B4     | SDA     | ALL                             | I <sup>2</sup> C Interface Serial Data. This pin should not be left floating.                                                                                                                                                                            |

| C1-C3  | SW      | ALL                             | Switching Node. Connect to output inductor.                                                                                                                                                                                                              |

| C4     | STAT    | ALL                             | <b>Status</b> . Open-drain output indicating charge status. The IC pulls this pin LOW when charge is in process.                                                                                                                                         |

| D1-D3  | PGND    | ALL                             | <b>Power Ground</b> . Power return for gate drive and power transistors. The connection from this pin to the bottom of $C_{\text{MID}}$ should be as short as possible.                                                                                  |

| D4     | OTG     | ALL                             | <b>On-The-Go</b> . Enables boost regulator in conjunction with OTG_EN and OTG_PL bits (see <i>Table 16</i> ). On VBUS Power-On Reset (POR), this pin sets the input current limit for t <sub>15MIN</sub> charging.                                       |

| E1     | CSIN    | ALL                             | Current-Sense Input. Connect to the sense resistor in series with the battery. The IC uses this node to sense current into the battery. Bypass this pin with a 0.1 $\mu$ F capacitor to PGND                                                             |

| E2     | AUXPWR  | FAN5400,<br>FAN5401,<br>FAN5402 | <b>Auxiliary Power</b> . Connect to the battery pack to provide IC power during High-Impedance Mode. Bypass with a 1 μF capacitor to PGND.                                                                                                               |

| E2     | DISABLE | FAN5403,<br>FAN5404,<br>FAN5405 | <b>Charge Disable</b> . If this pin is HIGH, charging is disabled. When LOW, charging is controlled by the I <sup>2</sup> C registers. When this pin is HIGH, the 15-minute timer is reset. This pin does not affect the 32-second timer.                |

| E3     | VREG    | ALL                             | Regulator Output. Connect to a $1\mu F$ capacitor to PGND. This pin can supply up to 2 mA or DC load current. For FAN5400-FAN5402, the output voltage is PMID, which is limited to 6.5 V. For FAN5403-FAN5405, the output voltage is regulated to 1.8 V. |

| E4     | VBAT    | ALL                             | <b>Battery Voltage</b> . Connect to the positive (+) terminal of the battery pack. Bypass with a $0.1~\mu\text{F}$ capacitor to PGND if the battery is connected through long leads.                                                                     |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            |                             | Parameter                                | Min. | Max. | Unit |

|-------------------|-----------------------------|------------------------------------------|------|------|------|

| M                 | VDLIC Voltage               | Continuous                               | -1.4 | 20.0 | V    |

| $V_{BUS}$         | VBUS Voltage                | Pulsed, 100 ms Maximum Non-Repetitive    |      | 20.0 | V    |

| V <sub>STAT</sub> | STAT Voltage                |                                          | -0.3 | 16.0 | V    |

| VI                | PMID Voltage                |                                          |      | 7.0  | V    |

| VI                | SW, CSIN, VBAT, AUXPWR,     | DISABLE Voltage                          | -0.3 | 7.0  | V    |

| Vo                | Voltage on Other Pins       |                                          | -0.3 | V    |      |

| dV <sub>BUS</sub> | Maximum VBUS Slope above    | e 5.5 V when Boost or Charger are Active |      | 4    | V/µs |

| ESD               | Electrostatic Discharge     | Human Body Model per JESD22-A114         | 20   | 000  | V    |

| E9D               | Protection Level            | Charged Device Model per JESD22-C101     | 5    | 00   | V    |

| TJ                | Junction Temperature        |                                          | -40  | +150 | °C   |

| T <sub>STG</sub>  | Storage Temperature         |                                          | -65  | +150 | °C   |

| TL                | Lead Soldering Temperature, | 10 Seconds                               | V.   | +260 | °C   |

#### Note:

Lesser of 6.5 V or V<sub>I</sub> + 0.3 V.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol             | Parameter                                                |                       |     | Max. | Units               |

|--------------------|----------------------------------------------------------|-----------------------|-----|------|---------------------|

| V <sub>BUS</sub>   | Supply Voltage                                           |                       | 4   | 6    | V                   |

| $V_{BAT(MAX)}$     | Maximum Battery Voltage when Boost enabled               | //                    | 4.5 | V    |                     |

| _dV <sub>BUS</sub> | Negative VBUS Slew Rate during VBUS Short Circuit,       | T <sub>A</sub> ≤ 60°C |     | 4    | \// <sub>**</sub> 0 |

| dt                 | C <sub>MID</sub> ≤ 4.7 μF, see VBUS Short While Charging | T <sub>A</sub> ≥ 60°C |     | 2    | V/μs                |

| T <sub>A</sub>     | Ambient Temperature                                      | bient Temperature     |     | +85  | °C                  |

| TJ                 | Junction Temperature (see Thermal Regulation and Prote   | ection section)       | -30 | +120 | °C                  |

# **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_A$ . For measured data, see Table 11.

| Symbol            | Parameter                              | Typical | Units |

|-------------------|----------------------------------------|---------|-------|

| $\theta_{\sf JA}$ | Junction-to-Ambient Thermal Resistance | 60      | °C/W  |

| $\theta_{\sf JB}$ | Junction-to-PCB Thermal Resistance     | 20      | °C/W  |

# **Electrical Specifications**

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}$ =5.0 V;  $HZ_MODE$ ;  $QPA_MODE$ =0; (Charge Mode);  $QPA_MODE$ =0; (Charge Mode); (Charge Mode);

| Symbol              | Parameter                             | Condi                                                                                                                     | tions                                                                                                                    | Min.  | Тур. | Max.  | Units |

|---------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Power Supp          | lies                                  |                                                                                                                           |                                                                                                                          | •     |      | •     |       |

|                     |                                       | $V_{BUS} > V_{BUS(min)}$ , PW                                                                                             | M Switching                                                                                                              |       | 10   |       | mA    |

| I <sub>VBUS</sub>   | VBUS Current                          | Not Switching (Batte                                                                                                      | V <sub>BUS</sub> > V <sub>BUS(min)</sub> ; PWM Enabled,<br>Not Switching (Battery OVP<br>Condition); I_IN Setting=100 mA |       | 2.5  |       | mA    |

|                     |                                       | 0°C < T <sub>J</sub> < 85°C, H <sub>Z</sub><br>V <sub>BAT</sub> < V <sub>LOWV</sub> , 32S M                               |                                                                                                                          |       | 63   | 90    | μА    |

| $I_{LKG}$           | VBAT to VBUS Leakage Current          | 0°C < T <sub>J</sub> < 85°C, H <sub>Z</sub><br>V <sub>BAT</sub> =4.2 V, V <sub>BUS</sub> =0                               |                                                                                                                          |       | 0.2  | 5.0   | μА    |

| l                   | Battery Discharge Current in High-    | 0°C < T <sub>J</sub> < 85°C, HZ<br>V <sub>BAT</sub> =4.2 V                                                                | Z_MODE=1,                                                                                                                |       |      | 20    |       |

| I <sub>BAT</sub>    | Impedance Mode                        | FAN5403-05, DISAB<br>0°C < T <sub>J</sub> < 85°C, V <sub>B</sub>                                                          |                                                                                                                          |       |      | 10    | μА    |

| Charger Vol         | tage Regulation                       |                                                                                                                           |                                                                                                                          |       |      |       |       |

|                     | Charge Voltage Range                  |                                                                                                                           |                                                                                                                          | 3.5   |      | 4.4   |       |

| $V_{OREG}$          | Charry Voltage Assurage               | T <sub>A</sub> =25°C                                                                                                      |                                                                                                                          | -0.5% |      | +0.5% | V     |

|                     | Charge Voltage Accuracy               | T <sub>J</sub> =0 to 125°C                                                                                                |                                                                                                                          | -1%   |      | +1%   |       |

| Charging Cu         | irrent Regulation                     |                                                                                                                           |                                                                                                                          |       |      |       | •     |

|                     | Output Charge Current Range           | V <sub>LOWV</sub> < V <sub>BAT</sub> < V <sub>ORE</sub><br>V <sub>BUS</sub> > V <sub>SLP</sub> , R <sub>SENSE</sub>       |                                                                                                                          | 550   |      | 1250  | mA    |

|                     | Charge Current Accuracy Across Rsense | 20 mV <u>&lt;</u> V <sub>IREG</sub> <u>&lt;</u>                                                                           | FAN5400-02                                                                                                               | 95    | 100  | 105   | %     |

| IOCHRG              |                                       | 40 mV                                                                                                                     | FAN5403-05                                                                                                               | 92    | 97   | 102   |       |

|                     |                                       | \/ . 40 m\/                                                                                                               | FAN5400-02                                                                                                               | 97    | 100  | 103   |       |

|                     |                                       | V <sub>IREG</sub> > 40 mV                                                                                                 | FAN5403-05                                                                                                               | 94    | 97   | 100   |       |

| Weak Batter         | y Detection                           |                                                                                                                           |                                                                                                                          | //    |      |       |       |

|                     | Weak Battery Threshold Range          |                                                                                                                           |                                                                                                                          | 3.4   |      | 3.7   | V     |

| $V_{LOWV}$          | Weak Battery Threshold Accuracy       |                                                                                                                           |                                                                                                                          | -5    |      | +5    | %     |

|                     | Weak Battery Deglitch Time            | Rising Voltage, 2 m                                                                                                       | / Overdrive                                                                                                              |       | 30   |       | ms    |

| Logic Levels        | s: DISABLE, SDA, SCL, OTG             |                                                                                                                           |                                                                                                                          |       |      |       | •     |

| V <sub>IH</sub>     | High-Level Input Voltage              |                                                                                                                           |                                                                                                                          | 1.05  |      |       | V     |

| V <sub>IL</sub>     | Low-Level Input Voltage               |                                                                                                                           |                                                                                                                          |       | 7-17 | 0.4   | V     |

| I <sub>IN</sub>     | Input Bias Current                    | Input Tied to GND o                                                                                                       | r V <sub>IN</sub>                                                                                                        |       | 0.01 | 1.00  | μΑ    |

| Charge Tern         | nination Detection                    |                                                                                                                           |                                                                                                                          |       |      |       |       |

|                     | Termination Current Range             | $V_{BAT} > V_{OREG} - V_{RCH}$<br>$R_{SENSE}$ =68 m $\Omega$                                                              | $V_{BUS} > V_{SLP}$                                                                                                      | 50    |      | 400   | mA    |

| I <sub>(TERM)</sub> | T 1 1 1 0 1 1 1                       | [V <sub>CSIN</sub> - V <sub>BAT</sub> ] from 3 mV to 20 mV<br>[V <sub>CSIN</sub> - V <sub>BAT</sub> ] from 20 mV to 40 mV |                                                                                                                          | -25   |      | +25   | %     |

| (. = 1 (11)         | Termination Current Accuracy          |                                                                                                                           |                                                                                                                          | -5    |      | +5    |       |

|                     | Termination Current Deglitch Time     | 2 mV Overdrive                                                                                                            |                                                                                                                          |       | 30   |       | ms    |

| 1.8 V Linear        | Regulator                             | •                                                                                                                         |                                                                                                                          | 1     |      |       | •     |

| $V_{REG}$           | 1.8 V Regulator Output                | I <sub>REG</sub> from 0 to 2 mA,                                                                                          | FAN5403-05                                                                                                               | 1.7   | 1.8  | 1.9   | V     |

Continued on the following page...

# **Electrical Specifications**

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}$ =5.0 V;  $HZ_MODE$ ;  $OPA_MODE$ =0; (Charge Mode); SCL, SDA, OTG=0 or 1.8 V; and typical values are for  $T_J$ =25°C.

| Symbol                   | Parameter                                                                       | Conditions                                                                                                    | Min. | Тур.  | Max. | Units |

|--------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Input Power              | Source Detection                                                                |                                                                                                               | •    | · •   | ·    | •     |

| V <sub>IN(MIN)1</sub>    | VBUS Input Voltage Rising                                                       | To Initiate and Pass VBUS Validation                                                                          |      | 4.29  | 4.42 | V     |

| V <sub>IN(MIN)2</sub>    | Minimum VBUS during Charge                                                      | During Charging                                                                                               |      | 3.71  | 3.94 | V     |

| t <sub>VBUS_VALID</sub>  | VBUS Validation Time                                                            |                                                                                                               |      | 30    |      | ms    |

| Special Cha              | rger (V <sub>BUS</sub> ) (FAN5403 – FAN5405)                                    |                                                                                                               |      |       | •    |       |

| $V_{SP}$                 | Special Charger Setpoint Accuracy                                               |                                                                                                               | -3   |       | +3   | %     |

| Input Curren             | nt Limit                                                                        |                                                                                                               |      |       | •    |       |

|                          |                                                                                 | I <sub>IN</sub> Set to 100 mA                                                                                 | 88   | 93    | 98   | 0     |

| I <sub>INLIM</sub>       | Input Current Limit Threshold                                                   | I <sub>IN</sub> Set to 500 mA                                                                                 | 450  | 475   | 500  | mA    |

| V <sub>REF</sub> Bias Ge | enerator                                                                        |                                                                                                               | •    |       | ·    | •     |

| V                        | Bias Regulator Voltage                                                          | V <sub>BUS</sub> > V <sub>IN(MIN)</sub> or V <sub>BAT</sub> > V <sub>BAT(MIN)</sub>                           |      |       | 6.5  | V     |

| $V_{REF}$                | Short-Circuit Current Limit                                                     |                                                                                                               |      | 20    |      | mA    |

| Battery Rech             | harge Threshold                                                                 |                                                                                                               | v    |       |      |       |

| V                        | Recharge Threshold                                                              | Below V <sub>(OREG)</sub>                                                                                     | 100  | 120   | 150  | mV    |

| $V_{RCH}$                | Deglitch Time                                                                   | V <sub>BAT</sub> Falling Below V <sub>RCH</sub> Threshold                                                     |      | 130   |      | ms    |

| STAT Outpu               | t                                                                               |                                                                                                               |      |       |      |       |

| V <sub>STAT(OL)</sub>    | STAT Output Low                                                                 | I <sub>STAT</sub> =10 mA                                                                                      |      |       | 0.4  | V     |

| I <sub>STAT(OH)</sub>    | STAT High Leakage Current                                                       | V <sub>STAT</sub> =5 V                                                                                        |      |       | 1    | μΑ    |

| Battery Dete             | ection                                                                          |                                                                                                               |      | II.   |      |       |

| I <sub>DETECT</sub>      | Battery Detection Current before Charge Done (Sink Current) <sup>(5)</sup>      | Begins after Termination Detected                                                                             |      | -0.80 |      | mA    |

| t <sub>DETECT</sub>      | Battery Detection Time                                                          | and V <sub>BAT</sub> ≤ V <sub>OREG</sub> −V <sub>RCH</sub>                                                    |      | 262   |      | ms    |

| Sleep Comp               | arator                                                                          |                                                                                                               | A    |       |      |       |

| $V_{SLP}$                | Sleep-Mode Entry Threshold, V <sub>BUS</sub> – V <sub>BAT</sub>                 | $2.3 \text{ V} \leq \text{V}_{\text{BAT}} \leq \text{V}_{\text{OREG}}, \text{V}_{\text{BUS}} \text{ Falling}$ | 0    | 0.04  | 0.10 | V     |

| V <sub>SLP_EXIT</sub>    | Deglitch Time for VBUS Rising<br>Above V <sub>SLP</sub> + V <sub>SLP_EXIT</sub> | Rising Voltage                                                                                                |      | 30    |      | ms    |

| Power Switc              | thes (see Figure 3)                                                             |                                                                                                               |      |       |      |       |

|                          | Q3 On Resistance (VBUS to PMID)                                                 | I <sub>IN(LIMIT)</sub> =500 mA                                                                                |      | 180   | 250  |       |

| $R_{DS(ON)}$             | Q1 On Resistance (PMID to SW)                                                   |                                                                                                               |      | 130   | 225  | mΩ    |

|                          | Q2 On Resistance (SW to GND)                                                    |                                                                                                               |      | 150   | 225  |       |

| Charger PW               | M Modulator                                                                     |                                                                                                               |      |       |      |       |

| f <sub>SW</sub>          | Oscillator Frequency                                                            |                                                                                                               | 2.7  | 3.0   | 3.3  | MHz   |

| D <sub>MAX</sub>         | Maximum Duty Cycle                                                              |                                                                                                               |      |       | 100  | %     |

| D <sub>MIN</sub>         | Minimum Duty Cycle                                                              |                                                                                                               |      | 0     |      | %     |

| I <sub>SYNC</sub>        | Synchronous to Non-Synchronous<br>Current Cut-Off Threshold <sup>(6)</sup>      | Low-Side MOSFET (Q2) Cycle-by-<br>Cycle Current Limit                                                         |      | 140   |      | mA    |

Continued on the following page...

# **Electrical Specifications**

Unless otherwise specified: according to the circuit of Figure 1; recommended operating temperature range for  $T_J$  and  $T_A$ ;  $V_{BUS}$ =5.0 V;  $HZ_MODE$ ;  $OPA_MODE$ =0; (Charge Mode); SCL, SDA, OTG=0 or 1.8 V; and typical values are for  $T_J$ =25°C.

| Symbol                  | Parameter                                   | Conditions                                                                                                          | Min. | Тур. | Max. | Units |

|-------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Boost Mode              | Operation (OPA_MODE=1, HZ_MOI               | DE=0)                                                                                                               | •    | •    | •    | •     |

| M                       | Decet Output Valters at VIDLIC              | $2.5~\text{V} < \text{V}_{\text{BAT}} < 4.5~\text{V},~\text{I}_{\text{LOAD}}$ from 0 to 200 mA                      | 4.80 | 5.07 | 5.17 |       |

| $V_{BOOST}$             | Boost Output Voltage at VBUS                | $2.7 \text{ V} < \text{V}_{\text{BAT}} < 4.5 \text{ V}, \text{ I}_{\text{LOAD}} \text{ from 0 to}$ $200 \text{ mA}$ | 4.85 | 5.07 | 5.17 | V     |

| I <sub>BAT(BOOST)</sub> | Boost Mode Quiescent Current                | PFM Mode, V <sub>BAT</sub> =3.6 V, I <sub>OUT</sub> =0                                                              |      | 140  | 300  | μΑ    |

| I <sub>LIMPK(BST)</sub> | Q2 Peak Current Limit                       |                                                                                                                     | 1100 | 1380 | 1660 | mA    |

| 11)// 0                 | Minimum Battery Voltage for Boost           | While Boost Active                                                                                                  |      | 2.42 |      | V     |

| UVLO <sub>BST</sub>     | Operation                                   | To Start Boost Regulator                                                                                            |      | 2.58 | 2.70 | V     |

| VBUS Load               | Resistance                                  |                                                                                                                     |      |      |      |       |

| D                       | VIDLO 4- DOND Di-4-                         | Normal Operation                                                                                                    |      | 1500 |      | ΚΩ    |

| R <sub>VBUS</sub>       | VBUS to PGND Resistance                     | Charger Validation                                                                                                  |      | 100  |      | Ω     |

| Protection a            | nd Timers                                   |                                                                                                                     |      |      |      |       |

| VDLIC                   | VBUS Over-Voltage Shutdown                  | V <sub>BUS</sub> Rising                                                                                             | 6.09 | 6.29 | 6.49 | V     |

| VBUS <sub>OVP</sub>     | Hysteresis                                  | V <sub>BUS</sub> Falling                                                                                            |      | 100  |      | mV    |

| I <sub>LIMPK(CHG)</sub> | Q1 Cycle-by-Cycle Peak Current<br>Limit     | Charge Mode                                                                                                         | Y    | 2.3  |      | Α     |

| V                       | Battery Short-Circuit Threshold             | V <sub>BAT</sub> Rising                                                                                             | 1.95 | 2.00 | 2.05 | V     |

| V <sub>SHORT</sub>      | Hysteresis                                  | V <sub>BAT</sub> Falling                                                                                            |      | 100  |      | V     |

| I <sub>SHORT</sub>      | Linear Charging Current                     | V <sub>BAT</sub> < V <sub>SHORT</sub>                                                                               | 20   | 30   | 40   | mA    |

| _                       | Thermal Shutdown Threshold <sup>(7)</sup>   | T <sub>J</sub> Rising                                                                                               |      | 145  |      | °C    |

| T <sub>SHUTDWN</sub>    | Hysteresis <sup>(7)</sup>                   | T <sub>J</sub> Falling                                                                                              |      | 10   |      |       |

| T <sub>CF</sub>         | Thermal Regulation Threshold <sup>(7)</sup> | Charge Current Reduction Begins                                                                                     |      | 120  |      | °C    |

| t <sub>INT</sub>        | Detection Interval                          |                                                                                                                     | //   | 2.1  |      | S     |

| 4                       | 32-Second Timer <sup>(8)</sup>              | Charger Enabled                                                                                                     | 20.5 | 25.2 | 28.0 |       |

| t <sub>328</sub>        | 52-Second Tiller                            | Charger Disabled                                                                                                    | 18.0 | 25.2 | 34.0 | S     |

| t <sub>15MIN</sub>      | 15-Minute Timer                             | 15-Minute Mode (FAN5400,<br>FAN5402, FAN5404, FAN5405)                                                              | 12.0 | 13.5 | 15.0 | min   |

| $\Delta t_{LF}$         | Low-Frequency Timer Accuracy                | Charger Inactive                                                                                                    | -25  |      | 25   | %     |

### Notes:

- 5. Negative current is current flowing from the battery to  $V_{\text{BUS}}$  (discharging the battery).

- 6. Q2 always turns on for 60 ns, then turns off if current is below I<sub>SYNC</sub>.

- 7. Guaranteed by design; not tested in production.

- 8. This tolerance (%) applies to all timers on the IC, including soft-start and deglitching timers.

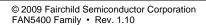

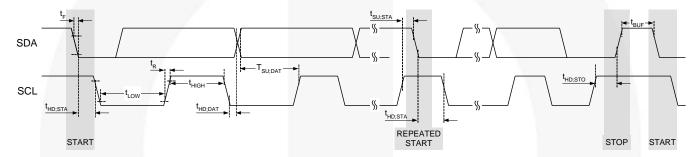

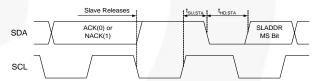

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                                 | Conditions                               | Min.                                  | Тур.              | Max. | Units |

|---------------------|-------------------------------------------|------------------------------------------|---------------------------------------|-------------------|------|-------|

|                     |                                           | Standard Mode                            |                                       |                   | 100  |       |

| ,                   |                                           | Fast Mode                                |                                       |                   | 400  |       |

| f <sub>SCL</sub>    | SCL Clock Frequency                       | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                                       |                   | 3400 | kHz   |

|                     |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |                                       |                   | 1700 | 1     |

|                     | Bus-Free Time between STOP                | Standard Mode                            |                                       | 4.7               |      |       |

| t <sub>BUF</sub>    | and START Conditions                      | Fast Mode                                |                                       | 1.3               |      | μS    |

|                     |                                           | Standard Mode                            |                                       | 4                 |      | μS    |

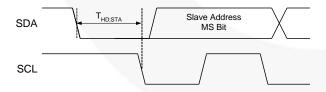

| t <sub>HD;STA</sub> | START or Repeated START<br>Hold Time      | Fast Mode                                |                                       | 600               |      | ns    |

|                     | Hold Tillle                               | High-Speed Mode                          |                                       | 160               |      | ns    |

|                     |                                           | Standard Mode                            |                                       | 4.7               |      | μS    |

|                     |                                           | Fast Mode                                |                                       | 1.3               |      | μS    |

| t <sub>LOW</sub>    | SCL LOW Period                            | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                                       | 160               |      | ns    |

|                     |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 320               |      | ns    |

|                     |                                           | Standard Mode                            |                                       | 4                 |      | μS    |

|                     |                                           | Fast Mode                                |                                       | 600               |      | ns    |

| t <sub>HIGH</sub>   | SCL HIGH Period                           | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                                       | 60                |      | ns    |

|                     |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |                                       | 120               |      | ns    |

|                     | Repeated START Setup Time                 | Standard Mode                            |                                       | 4.7               |      | μS    |

| t <sub>SU;STA</sub> |                                           | Fast Mode                                |                                       | 600               |      | ns    |

|                     |                                           | High-Speed Mode                          |                                       | 160               |      | ns    |

|                     |                                           | Standard Mode                            |                                       | 250               |      |       |

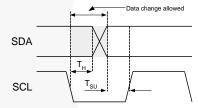

| t <sub>SU:DAT</sub> | Data Setup Time                           | Fast Mode                                |                                       | 100               | į į  | ns    |

| 00,5711             |                                           | High-Speed Mode                          |                                       | 10                |      |       |

|                     |                                           | Standard Mode                            | 0                                     |                   | 3.45 | μS    |

|                     |                                           | Fast Mode                                | 0                                     |                   | 900  | ns    |

| t <sub>HD;DAT</sub> | Data Hold Time                            | High-Speed Mode, C <sub>B</sub> ≤ 100 pF | 0                                     |                   | 70   | ns    |

|                     |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF | 0                                     |                   | 150  | ns    |

|                     |                                           | Standard Mode                            | 20 +                                  | 0.1C <sub>B</sub> | 1000 |       |

|                     |                                           | Fast Mode                                | 20 +                                  | 0.1C <sub>B</sub> | 300  | -     |

| $t_{RCL}$           | SCL Rise Time                             | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                                       | 10                | 80   | ns    |

|                     |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |                                       | 20                | 160  |       |

|                     |                                           | Standard Mode                            | 20 +                                  | 0.1C <sub>B</sub> | 300  |       |

|                     |                                           | Fast Mode                                |                                       | 0.1C <sub>B</sub> | 300  |       |

| t <sub>FCL</sub>    | SCL Fall Time                             | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                                       | 10                | 40   | ns    |

|                     |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |                                       | 20                | 80   | -     |

|                     |                                           | Standard Mode                            | 20 +                                  | 0.1C <sub>B</sub> | 1000 |       |

| t <sub>RDA</sub>    | SDA Rise Time<br>Rise Time of SCL after a | Fast Mode                                |                                       | 0.1C <sub>B</sub> | 300  | 1     |

| t <sub>RCL1</sub>   | Repeated START Condition                  | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                                       | 10                | 80   | ns    |

|                     | and after ACK Bit                         | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |                                       | 20                | 160  | -     |

Continued on the following page...

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol              | Parameter                    | Conditions                               | Min. | Тур.              | Max. | Units |

|---------------------|------------------------------|------------------------------------------|------|-------------------|------|-------|

|                     | Standard Mode                | Standard Mode                            | 20 + | 0.1C <sub>B</sub> | 300  |       |

| t <sub>FDA</sub>    | SDA Fall Time                | Fast Mode                                | 20 + | 0.1C <sub>B</sub> | 300  | 1     |

|                     | SDA Fall Time                | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 80   | ns    |

|                     |                              | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 160  |       |

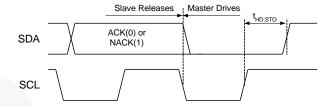

|                     |                              | Standard Mode                            |      | 4                 |      | μS    |

| t <sub>SU;STO</sub> | Stop Condition Setup Time    | Fast Mode                                |      | 600               |      | ns    |

|                     |                              | High-Speed Mode                          |      | 160               |      | ns    |

| Св                  | Capacitive Load for SDA, SCL |                                          |      |                   | 400  | pF    |

# **Timing Diagrams**

Figure 5. I<sup>2</sup>C Interface Timing for Fast and Slow Modes

Figure 6. I<sup>2</sup>C Interface Timing for High-Speed Mode

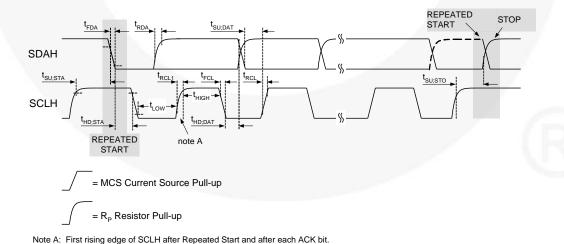

# **Charge Mode Typical Characteristics**

Unless otherwise specified, circuit of Figure 1, V<sub>OREG</sub>=4.2 V, V<sub>BUS</sub>=5.0 V, and T<sub>A</sub>=25°C.

900 800 700 Current (mA) 600 500 **Battery Charge** 400 300 200 5.0VBUS 100 4.5VBUS 2.5 3.5 4 4.5 Battery Voltage, VBAT (V)

Figure 7. Battery Charge Current vs.  $V_{\text{BUS}}$  with  $I_{\text{INLIM}}$ =100 mA

Figure 8. Battery Charge Current vs.  $V_{\text{BUS}}$  with  $I_{\text{INLIM}} = 500 \text{ mA}$

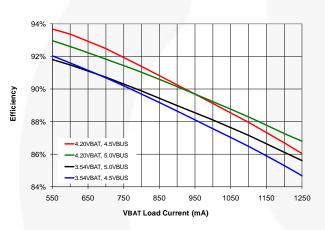

Figure 9. Charger Efficiency, No I<sub>INLIM</sub>, I<sub>OCHARGE</sub>=1,250 mA

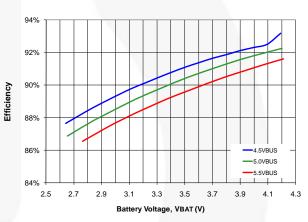

Figure 10. Charger Efficiency vs. V<sub>BUS</sub>, I<sub>INLIM</sub>=500 mA

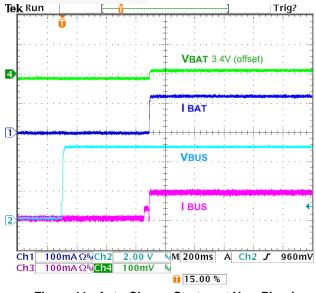

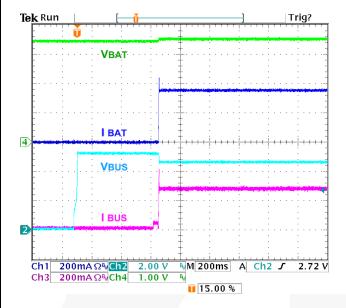

Figure 11. Auto-Charge Startup at V<sub>BUS</sub> Plug-in, I<sub>INLIM</sub>=100 mA, OTG=1, V<sub>BAT</sub>=3.4 V

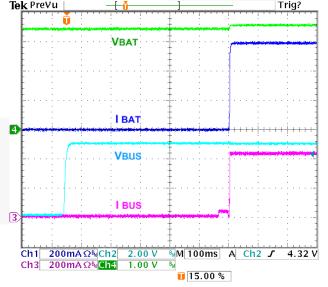

Figure 12. Auto-Charge Startup at V<sub>BUS</sub> Plug-in, I<sub>INLIM</sub>=500 mA, OTG=1, V<sub>BAT</sub>=3.4 V

# **Charge Mode Typical Characteristics**

Unless otherwise specified, circuit of Figure 1, V<sub>OREG</sub>=4.2 V, V<sub>BUS</sub>=5.0 V, and T<sub>A</sub>=25°C.

Tek Stop

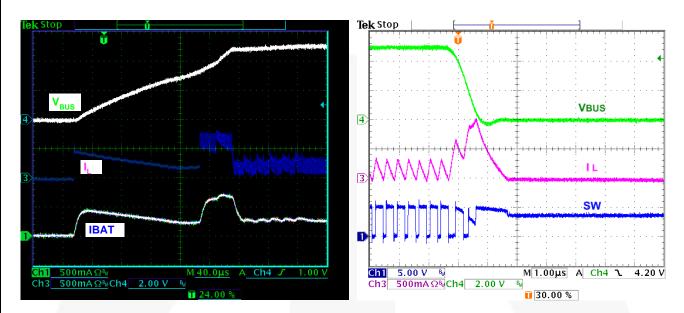

Figure 13. AutoCharge Startup with 300 mA Limited Charger / Adaptor, I<sub>INLIM</sub>=500 mA, OTG=1, V<sub>BAT</sub>=3.4 V

Figure 14. Charger Startup with HZ\_MODE Bit Reset,  $I_{INLIM}$ =500 mA,  $I_{OCHARGE}$ =950 mA, OREG=4.2 V,  $V_{BAT}$ =3.6 V

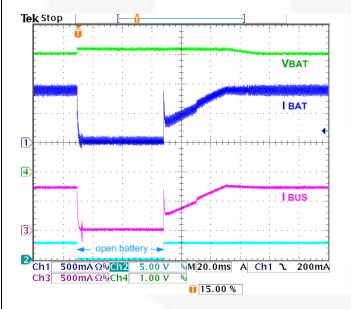

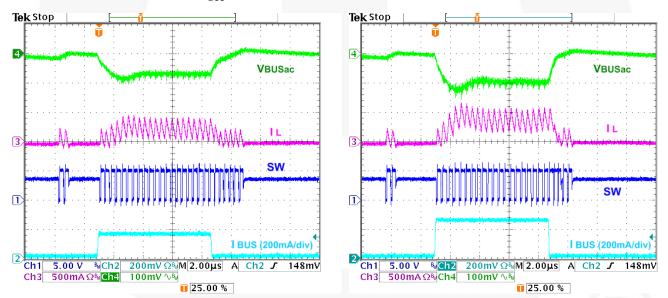

Figure 15. Battery Removal / Insertion during Charging, V<sub>BAT</sub>=3.9 V, I<sub>OCHARGE</sub>=950 mA, No I<sub>INLIM</sub>, TE=0

Figure 16. Battery Removal / Insertion during Charging,  $V_{BAT}$ =3.9 V,  $I_{OCHARGE}$ =950 mA, No  $I_{INLIM}$ , TE=1

# **Charge Mode Typical Characteristics**

Unless otherwise specified, circuit of Figure 1, V<sub>OREG</sub>=4.2 V, V<sub>BUS</sub>=5.0 V, and T<sub>A</sub>=25°C.

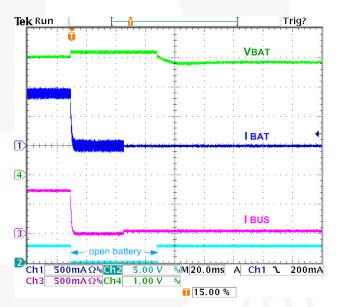

Figure 17. No Battery at V<sub>BUS</sub> Power-up; FAN5400, FAN5403

Figure 18. No Battery at V<sub>BUS</sub> Power-up; FAN5402, FAN5405

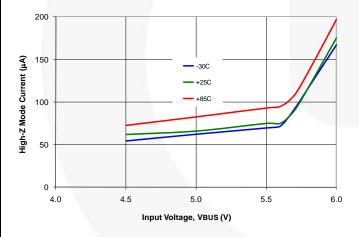

Figure 19. VBUS Current in High-Impedance Mode with Battery Open

Figure 20. V<sub>REG</sub> 1.8 V Output Regulation

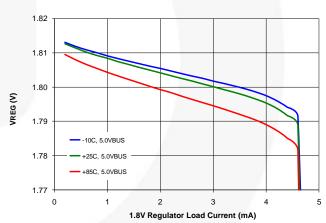

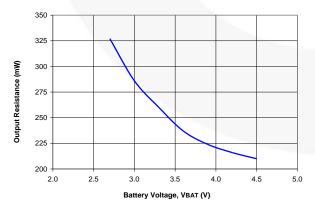

# **Boost Mode Typical Characteristics**

Unless otherwise specified, using circuit of Figure 1, V<sub>BAT</sub>=3.6 V, T<sub>A</sub>=25°C.

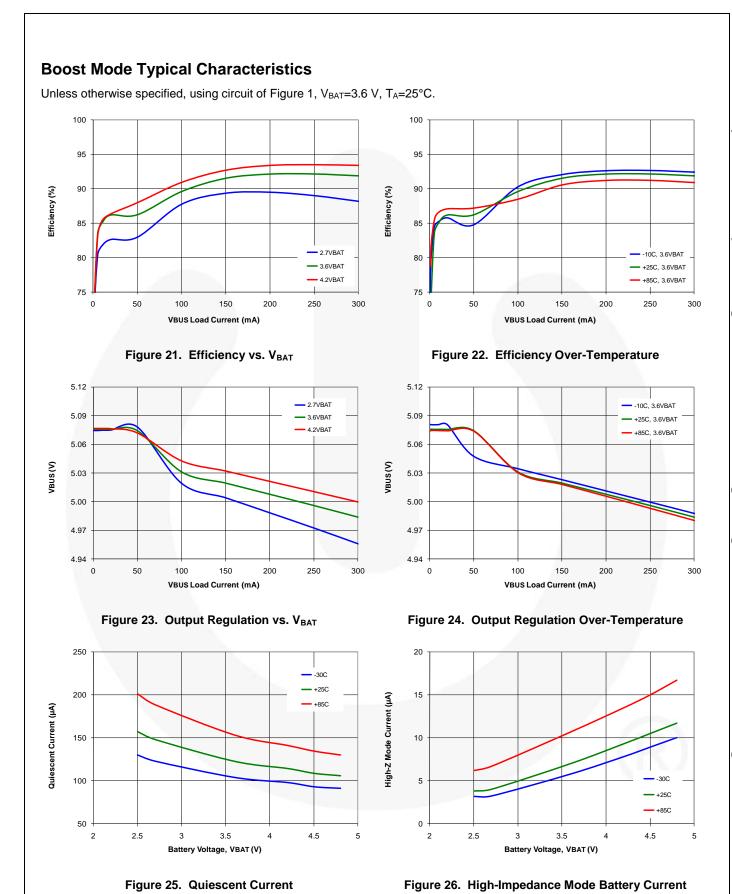

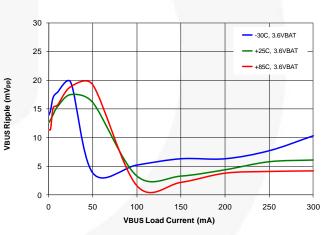

Figure 27. Boost PWM Waveform

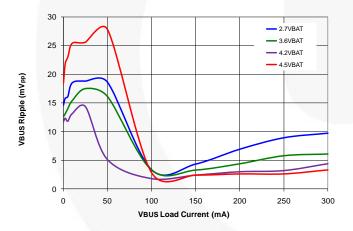

Figure 29. Output Ripple vs. V<sub>BAT</sub>

Figure 28. Boost PFM Waveform

Figure 30. Output Ripple vs. Temperature

# **Boost Mode Typical Characteristics**

Unless otherwise specified, using circuit of Figure 1, V<sub>BAT</sub>=3.6 V, T<sub>A</sub>=25°C.

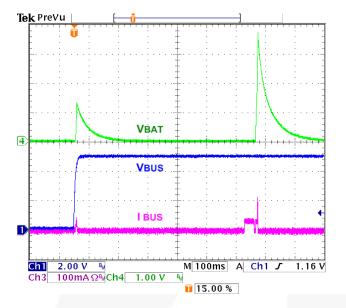

Figure 31. Startup, 3.6  $V_{BAT},$  44  $\Omega$  Load, Additional 10  $\mu F,$  X5R Across  $V_{BUS}$

Figure 32.  $V_{BUS}$  Fault Response, 3.6  $V_{BAT}$

Figure 33. Load Transient, 5-155-5 mA, t<sub>R</sub>=t<sub>F</sub>=100 ns

Figure 34. Load Transient, 5-255-5 mA, t<sub>R</sub>=t<sub>F</sub>=100 ns

# **Circuit Description / Overview**

When charging batteries with a current-limited input source, such as USB, a switching charger's high efficiency over a wide range of output voltages minimizes charging time.

FAN540X combines a highly integrated synchronous buck regulator for charging with a synchronous boost regulator, which can supply 5 V to USB On-The-Go (OTG) peripherals. The regulator employs synchronous rectification for both the charger and boost regulators to maintain high efficiency over a wide range of battery voltages and charge states.

The FAN540X has three operating modes:

- Charge Mode: Charges a single-cell Li-ion or Li-polymer battery.

- Boost Mode: Provides 5 V power to USB-OTG with an integrated synchronous rectification boost regulator using the battery as input.

- High-Impedance Mode:

Both the boost and charging circuits are OFF in this mode. Current flow from VBUS to the battery or from the battery to VBUS is blocked in this mode. This mode consumes very little current from VBUS or the battery.

Note: Default settings are denoted by **bold typeface**.

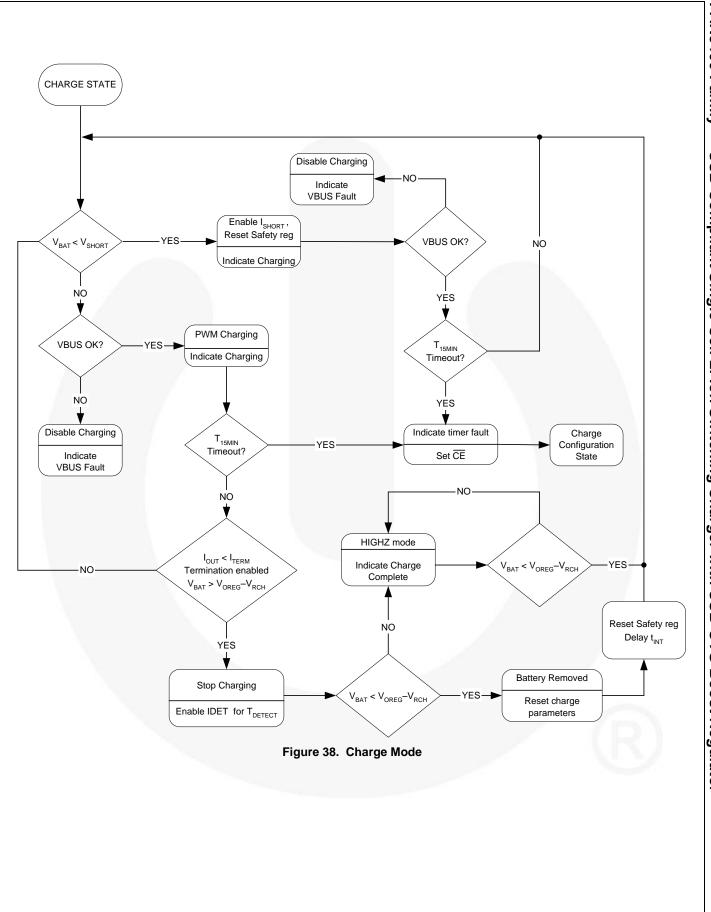

# **Charge Mode**

In Charge Mode, FAN540X employs four regulation loops:

- Input Current: Limits the amount of current drawn from VBUS. This current is sensed internally and can be programmed through the I<sup>2</sup>C interface.

- 2. Charging Current: Limits the maximum charging current. This current is sensed using an external R<sub>SENSE</sub> resistor.

- 3. Charge Voltage: The regulator is restricted from exceeding this voltage. As the internal battery voltage rises, the battery's internal impedance and R<sub>SENSE</sub> work in conjunction with the charge voltage regulation to decrease the amount of current flowing to the battery. Battery charging is completed when the voltage across R<sub>SENSE</sub> drops below the I<sub>TERM</sub> threshold.

- Temperature: If the IC's junction temperature reaches 120°C, charge current is continuously reduced until the IC's temperature stabilizes at 120°C.

In addition, the FAN5403-05 employ an additional loop to limit the amount of drop on VBUS to a programmable voltage ( $V_{SP}$ ) to accommodate "special chargers" that limit current to a lower current than might be available from a "normal" USB wall charger.

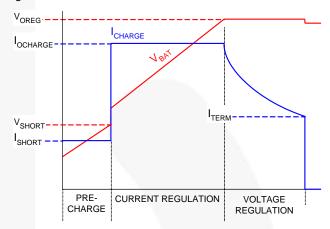

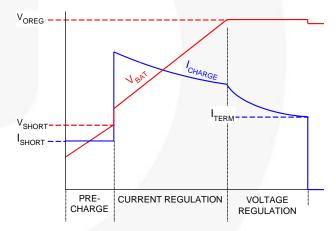

### **Battery Charging Curve**

If the battery voltage is below  $V_{SHORT}$ , a linear current source pre-charges the battery until  $V_{BAT}$  reaches  $V_{SHORT}$ . The PWM charging circuit is then started and the battery is charged

with a constant current if sufficient input power is available. The current slew rate is limited to prevent overshoot.

The FAN540X is designed to work with a current-limited input source at VBUS. During the current regulation phase of charging,  $I_{\text{INLIM}}$  or the programmed charging current limits the amount of current available to charge the battery and power the system. The effect of  $I_{\text{INLIM}}$  on  $I_{\text{CHARGE}}$  can be seen in Figure 36.

Figure 35. Charge Curve, ICHARGE Not Limited by IINLIM

Figure 36. Charge Curve, I<sub>INLIM</sub> Limits I<sub>CHARGE</sub>

Assuming that  $V_{OREG}$  is programmed to the cell's fully charged "float" voltage, the current that the battery accepts with the PWM regulator limiting its output (sensed at VBAT) to  $V_{OREG}$  declines, and the charger enters the voltage regulation phase of charging. When the current declines to the programmed  $I_{TERM}$  value, the charge cycle is complete. Charge current termination can be disabled by resetting the TE bit (REG1[3]).

The charger output or "float" voltage can be programmed by the OREG bits from 3.5 V to 4.44 V in 20 mV increments, as shown in Table 3.

Table 3. OREG Bits (OREG[7:2]) vs. Charger  $V_{OUT}$  ( $V_{OREG}$ ) Float Voltage

| (V <sub>OREG</sub> ) Float Voltage |     |       |  |  |

|------------------------------------|-----|-------|--|--|

| Decimal                            | Hex | VOREG |  |  |

| 0                                  | 00  | 3.50  |  |  |

| 1                                  | 01  | 3.52  |  |  |

| 2                                  | 02  | 3.54  |  |  |

| 3                                  | 03  | 3.56  |  |  |

| 4                                  | 04  | 3.58  |  |  |

| 5                                  | 05  | 3.60  |  |  |

| 6                                  | 06  | 3.62  |  |  |

| 7                                  | 07  | 3.64  |  |  |

| 8                                  | 08  | 3.66  |  |  |

| 9                                  | 09  | 3.68  |  |  |

| 10                                 | 0A  | 3.70  |  |  |

| 11                                 | 0B  | 3.72  |  |  |

| 12                                 | 0C  | 3.74  |  |  |

| 13                                 | 0D  | 3.76  |  |  |

| 14                                 | 0E  | 3.78  |  |  |

| 15                                 | 0F  | 3.80  |  |  |

| 16                                 | 10  | 3.82  |  |  |

| 17                                 | 11  | 3.84  |  |  |

| 18                                 | 12  | 3.86  |  |  |

| 19                                 | 13  | 3.88  |  |  |

| 20                                 | 14  | 3.90  |  |  |

| 21                                 | 15  | 3.92  |  |  |

| 22                                 | 16  | 3.94  |  |  |

| 23                                 | 17  | 3.96  |  |  |

| 24                                 | 18  | 3.98  |  |  |

| 25                                 | 19  | 4.00  |  |  |

| 26                                 | 1A  | 4.02  |  |  |

| 27                                 | 1B  | 4.04  |  |  |

| 28                                 | 1C  | 4.06  |  |  |

| 29                                 | 1D  | 4.08  |  |  |

| 30                                 | 1E  | 4.10  |  |  |

|                                    |     |       |  |  |

| D       |     | VODEO |

|---------|-----|-------|

| Decimal | Hex | VOREG |

| 32      | 20  | 4.14  |

| 33      | 21  | 4.16  |

| 34      | 22  | 4.18  |

| 35      | 23  | 4.20  |

| 36      | 24  | 4.22  |

| 37      | 25  | 4.24  |

| 38      | 26  | 4.26  |

| 39      | 27  | 4.28  |

| 40      | 28  | 4.30  |

| 41      | 29  | 4.32  |

| 42      | 2A  | 4.34  |

| 43      | 2B  | 4.36  |

| 44      | 2C  | 4.38  |

| 45      | 2D  | 4.40  |

| 46      | 2E  | 4.42  |

| 47      | 2F  | 4.44  |

| 48      | 30  | 4.44  |

| 49      | 31  | 4.44  |

| 50      | 32  | 4.44  |

| 51      | 33  | 4.44  |

| 52      | 34  | 4.44  |

| 53      | 35  | 4.44  |

| 54      | 36  | 4.44  |

| 55      | 37  | 4.44  |

| 56      | 38  | 4.44  |

| 57      | 39  | 4.44  |

| 58      | 3A  | 4.44  |

| 59      | 3B  | 4.44  |

| 60      | 3C  | 4.44  |

| 61      | 3D  | 4.44  |

| 62      | 3E  | 4.44  |

The following charging parameters can be programmed by the host through I<sup>2</sup>C:

**Table 4. Programmable Charging Parameters**

| Parameter                      | Name               | Register  |

|--------------------------------|--------------------|-----------|

| Output Voltage Regulation      | Voreg              | REG2[7:2] |

| Battery Charging Current Limit | I <sub>OCHRG</sub> | REG4[6:4] |

| Input Current Limit            | I <sub>INLIM</sub> | REG1[7:6] |

| Charge Termination Limit       | I <sub>TERM</sub>  | REG4[2:0] |

| Weak Battery Voltage           | $V_{LOWV}$         | REG1[5:4] |

A new charge cycle begins when one of the following occurs:

- The battery voltage falls below V<sub>OREG</sub> V<sub>RCH</sub>

- VBUS Power On Reset (POR) clears and the battery voltage is below the weak battery threshold (V<sub>LOWV</sub>).

This occurs for all versions except the FAN5401.

- CE or HZ\_MODE is reset through I<sup>2</sup>C write to CONTROL1 (R1) register.

## Charge Current Limit (IOCHARGE)

Table 5. I<sub>OCHARGE</sub> (REG4 [6:4]) Current as Function of I<sub>OCHARGE</sub> Bits and R<sub>SENSE</sub> Resistor Values

| DEC | BIN | HEX | V <sub>RSENSE</sub> | I <sub>OCHAR</sub> | <sub>GE</sub> (mA) |

|-----|-----|-----|---------------------|--------------------|--------------------|

| DEC | DIN | ПЕХ | (mV)                | 68 mΩ              | 100 m $\Omega$     |

| 0   | 000 | 00  | 37.4                | 550                | 374                |

| 1   | 001 | 01  | 44.2                | 650                | 442                |

| 2   | 010 | 02  | 51.0                | 750                | 510                |

| 3   | 011 | 03  | 57.8                | 850                | 578                |

| 4   | 100 | 04  | 64.6                | 950                | 646                |

| 5   | 101 | 05  | 71.4                | 1050               | 714                |

| 6   | 110 | 06  | 78.2                | 1150               | 782                |

| 7   | 111 | 07  | 85.0                | 1250               | 850                |

#### **Termination Current Limit**

Current charge termination is enabled when TE (REG1[3])=1. Typical termination current values are given in Table 6.

Table 6.  $I_{\text{TERM}}$  Current as Function of  $I_{\text{TERM}}$  Bits (REG4[2:0]) and  $R_{\text{SENSE}}$  Resistor Values

|                   | FAN5400 - FAN5402     |                        |        | FAN540              | 03 - FA                | N5405  |

|-------------------|-----------------------|------------------------|--------|---------------------|------------------------|--------|

|                   | . V <sub>RSENSE</sub> | I <sub>TERM</sub> (mA) |        | V <sub>RSENSE</sub> | I <sub>TERM</sub> (mA) |        |

| I <sub>TERM</sub> | (mV)                  | 68 mΩ                  | 100 mΩ | (mV)                | 68 mΩ                  | 100 mΩ |

| 0                 | 3.4                   | 50                     | 34     | 3.3                 | 49                     | 33     |

| 1                 | 6.8                   | 100                    | 68     | 6.6                 | 97                     | 66     |

| 2                 | 10.2                  | 150                    | 102    | 9.9                 | 146                    | 99     |

| 3                 | 13.6                  | 200                    | 136    | 13.2                | 194                    | 132    |

| 4                 | 17.0                  | 250                    | 170    | 16.5                | 243                    | 165    |

| 5                 | 20.4                  | 300                    | 204    | 19.8                | 291                    | 198    |

| 6                 | 23.8                  | 350                    | 238    | 23.1                | 340                    | 231    |

| 7                 | 27.2                  | 400                    | 272    | 26.4                | 388                    | 264    |

When the charge current falls below I<sub>TERM</sub> for a period of 32 ms; PWM charging stops and the STAT bits change to READY (00) for about 500 ms while the IC determines whether the battery and charging source are still connected. The STAT bits then change to CHARGE DONE (10), provided the battery and charger are still connected.

## **PWM Controller in Charge Mode**

The IC uses a current-mode PWM controller to regulate the output voltage and battery charge currents. The synchronous rectifier (Q2) has a negative current limit that turns off Q2 at 140 mA to prevent current flow from the battery.

# **Safety Timer**

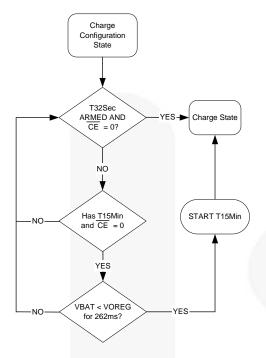

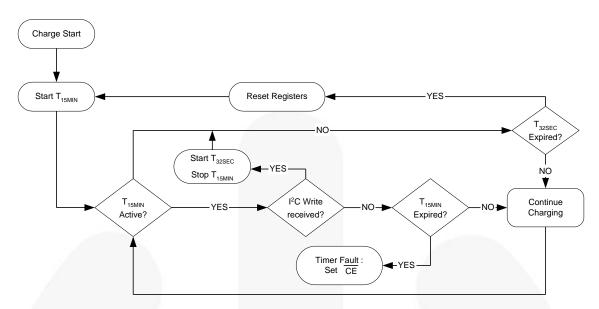

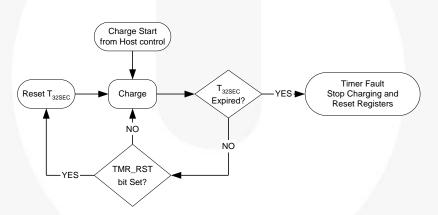

This section references Figure 41 and Figure 42.

At the beginning of charging, the IC starts a 15-minute timer ( $t_{15\text{MIN}}$ ). When this timer times out, charging is terminated. Writing to any register through I<sup>2</sup>C stops and resets the  $t_{15\text{MIN}}$  timer, which in turn starts a 32-second timer ( $t_{32\text{S}}$ ). Setting the TMR\_RST bit (REG0[7]) resets the  $t_{32\text{S}}$  timer. If the  $t_{32\text{S}}$  timer times out, charging is terminated, the registers are set to their default values, and charging resumes using the default values with the  $t_{15\text{MIN}}$  timer running.

Normal charging is controlled by the host with the  $t_{328}$  timer running to ensure that the host is alive. Charging with the  $t_{15\text{MIN}}$  timer running is used for charging that is unattended by the host. If the  $t_{15\text{MIN}}$  timer expires, the IC turns off the charger, sets the  $\overline{\text{CE}}$  bit, and indicates a timer fault (110) on the FAULT bits (REG0[2:0]). This sequence prevents overcharge if the host fails to reset the  $t_{328}$  timer.

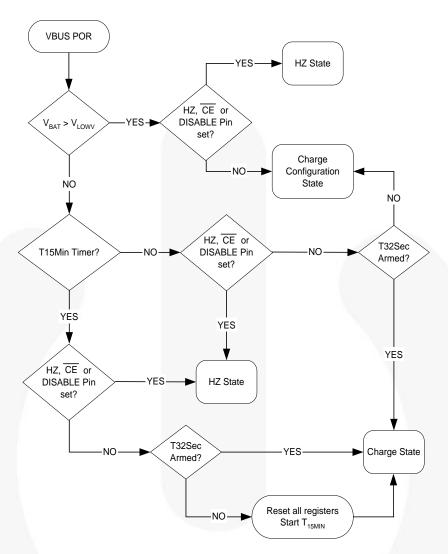

# V<sub>BUS</sub> POR / Non-Compliant Charger Rejection

When the IC detects that  $V_{BUS}$  has risen above  $V_{IN(MIN)1}$  (4.4 V), the IC applies a 110  $\Omega$  load from VBUS to GND. To clear the VBUS POR (Power-On-Reset) and begin charging, VBUS must remain above  $V_{IN(MIN)1}$  and below VBUS<sub>OVP</sub> for  $t_{VBUS\_VALID}$  (30 ms) before the IC initiates charging. The VBUS validation sequence always occurs before charging is initiated or re-initiated (for example, after a VBUS OVP fault or a  $V_{RCH}$  recharge initiation).

t<sub>VBUS\_VALID</sub> ensures that unfiltered 50 / 60 Hz chargers and other non-compliant chargers are rejected.

### **USB-Friendly Boot Sequence**

For all versions except FAN5401, FAN5404

At VBUS POR, when the battery voltage is above the weak battery threshold (V<sub>LOWV</sub>), the IC operates in accordance with its  $I^2C$  register settings. If  $V_{BAT} < V_{LOWV}$ , the IC sets all registers to their default values and enables the charger using an input current limit controlled by the OTG pin (100 mA if OTG is LOW and 500 mA if OTG is HIGH). This feature can revive a battery whose voltage is too low to ensure reliable host operation. Charging continues in the absence of host communication even after the battery has reached V<sub>OREG</sub>, whose default value is 3.54 V, and the charger remains active until t<sub>15MIN</sub> times out. Once the host processor begins writing to the IC, charging parameters are set by the host, which must continually reset the tags timer to continue charging using the programmed charging parameters. If t<sub>328</sub>,times out, the register defaults are loaded, the FAULT bits are set to 110, STAT is pulsed HIGH, and charging continues with default charge parameters.

The FAN5401 and FAN5404 do not automatically initiate charging at VBUS POR. Instead, they wait for the host to initiate charging through I<sup>2</sup>C commands.

### **Input Current Limiting**

To minimize charging time without overloading VBUS current limitations, the IC's input current limit can be programmed by the I<sub>INLIM</sub> bits (REG1[7:6]).

**Table 7. Input Current Limit**

| I <sub>INLIM</sub> REG1[7:6] | Input Current Limit |

|------------------------------|---------------------|

| 00                           | 100 mA              |

| 01                           | 500 mA              |

| 10                           | 800 mA              |

| 11                           | No limit            |

For all versions except the FAN5401 and FAN5404, the OTG pin establishes the input current limit when  $t_{15\text{MIN}}$  is running. For the FAN5401 and FAN5404, no charging occurs automatically at VBUS POR, so the input current limit is established by the  $I_{\text{INLIM}}$  bits.

# **Flow Charts**

Figure 37. Charger VBUS POR

Figure 39. Charge Configuration

Figure 40. HZ-State

Figure 41. Timer Flow Chart for FAN5400, FAN5402, FAN5403, FAN5405

Figure 42. Timer Flow Chart for FAN5401, FAN5404

# **Special Charger**

FAN5403-05 Only

The FAN5403, FAN5404, and FAN5405 have additional functionality to limit input current in case a current-limited "special charger" is supplying VBUS. The FAN5403-05 slowly increases the charging current until either:

I<sub>INLIM</sub> or I<sub>OCHARGE</sub> is reached

or

V<sub>BUS</sub>=V<sub>SP</sub>.

If  $V_{BUS}$  collapses to  $V_{SP}$  when the current is ramping up, the FAN5403-05 charge with an input current that keeps  $V_{BUS}$ = $V_{SP}$ . When the  $V_{SP}$  control loop is limiting the charge current, the SP bit (REG5[4]) is set.

Table 8. V<sub>SP</sub> as Function of SP Bits (REG5[2:0])

| S   |     |     |                 |

|-----|-----|-----|-----------------|

| DEC | BIN | HEX | V <sub>SP</sub> |

| 0   | 000 | 00  | 4.213           |

| 1   | 001 | 01  | 4.293           |

| 2   | 010 | 02  | 4.373           |

| 3   | 011 | 03  | 4.453           |

| 4   | 100 | 04  | 4.533           |

| 5   | 101 | 05  | 4.613           |

| 6   | 110 | 06  | 4.693           |

| 7   | 111 | 07  | 4.773           |

## **Safety Settings**

FAN5403-FAN5405 Only

The FAN5403-05 contain a SAFETY register (REG6) that prevents the values in OREG (REG2[7:2]) and IOCHARGE (REG4[6:4]) from exceeding the values of the VSAFE and ISAFE values.

After V<sub>BAT</sub> exceeds V<sub>SHORT</sub>, the SAFETY register is loaded with its default value and may be written only before any other register is written. After writing to any other register, the SAFETY register is locked until V<sub>BAT</sub> falls below V<sub>SHORT</sub>.

The ISAFE (REG6[6:4]) and VSAFE (REG6[3:0]) registers establish values that limit the maximum values of  $I_{OCHARGE}$  and  $V_{OREG}$  used by the control logic. If the host attempts to write a value higher than VSAFE or ISAFE to OREG or IOCHARGE, respectively; the VSAFE, ISAFE value appears as the OREG, IOCHARGE register value, respectively.

Table 9. I<sub>SAFE</sub> (I<sub>OCHARGE</sub> Limit) as Function of ISAFE Bits (REG6[6:4])

| ISAFE | ISAFE (REG6[6:4]) |     |                            |                   |        |

|-------|-------------------|-----|----------------------------|-------------------|--------|

| DEC   | <b>5</b> 11.1     |     | \/ (m\/)                   | I <sub>SAFE</sub> | (mA)   |

| DEC   | BIN               | HEX | ( V <sub>RSENSE</sub> (mV) | 68 mΩ             | 100 mΩ |

| 0     | 000               | 00  | 37.4                       | 550               | 374    |

| 1     | 001               | 01  | 44.2                       | 650               | 442    |

| 2     | 010               | 02  | 51.0                       | 750               | 510    |

| 3     | 011               | 03  | 57.8                       | 850               | 578    |

| 4     | 100               | 04  | 64.6                       | 950               | 646    |

| 5     | 101               | 05  | 71.4                       | 1050              | 714    |

| 6     | 110               | 06  | 78.2                       | 1150              | 782    |

| 7     | 111               | 07  | 85.0                       | 1250              | 850    |

Table 10.  $V_{SAFE}$  ( $V_{OREG}$  Limit) as Function of VSAFE Bits (REG6[3:0])

| VSAF | E (REG | 6[3:0]) |                          |               |

|------|--------|---------|--------------------------|---------------|

| DEC  | BIN    | HEX     | Max. OREG<br>(REG2[7:2]) | VOREG<br>Max. |

| 0    | 0000   | 00      | 100011                   | 4.20          |

| 1    | 0001   | 01      | 100100                   | 4.22          |

| 2    | 0010   | 02      | 100101                   | 4.24          |

| 3    | 0011   | 03      | 100110                   | 4.26          |

| 4    | 0100   | 04      | 100111                   | 4.28          |

| 5    | 0101   | 05      | 101000                   | 4.30          |

| 6    | 0110   | 06      | 101001                   | 4.32          |

| 7    | 0111   | 07      | 101010                   | 4.34          |

| 8    | 1000   | 08      | 101011                   | 4.36          |

| 9    | 1001   | 09      | 101100                   | 4.38          |

| 10   | 1010   | 0A      | 101101                   | 4.40          |

| 11   | 1011   | 0B      | 101110                   | 4.42          |

| 12   | 1100   | 0C      | 101111                   | 4.44          |

| 13   | 1101   | 0D      | 110000                   | 4.44          |

| 14   | 1110   | 0E      | 110001                   | 4.44          |

| 15   | 1111   | 0F      | 110010                   | 4.44          |

# Thermal Regulation and Protection