National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

March 28, 2011

-----

# LP2998

# **DDR-I and DDR-II Termination Regulator**

## **General Description**

National Semiconductor

The LP2998 linear regulator is designed to meet JEDEC SSTL-2 and JEDEC SSTL-18 specifications for termination of DDR1-SDRAM and DDR-II memory. The device contains a high-speed operational amplifier to provide excellent response to load transients. The output stage prevents shoot through while delivering 1.5A continuous current as required for DDR1-SDRAM termination, and 0.5A continuous current as required for DDR-II termination. The LP2998 also incorporates a V<sub>SENSE</sub> pin to provide superior load regulation and a V<sub>REF</sub> output as a reference for the chipset and DIMMs.

An additional feature found on the LP2998 is an active low shutdown ( $\overline{SD}$ ) pin that provides Suspend To RAM (STR) functionality. When  $\overline{SD}$  is pulled low, the V<sub>TT</sub> output will tristate providing a high impedance output, while V<sub>REF</sub> remains active. A power savings advantage can be obtained in this mode through lower quiescent current.

### **Features**

- Source and sink current

- Low output voltage offset

- No external resistors required

- Linear topology

- Suspend to Ram (STR) functionality

- Low external component count

- Thermal Shutdown

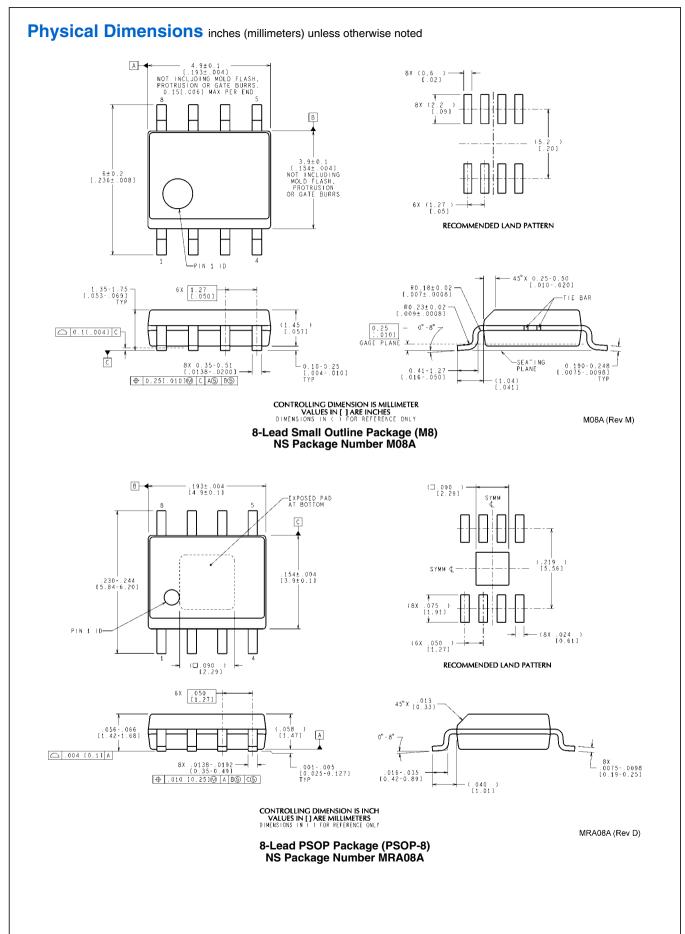

- Available in SO-8, PSOP-8 packages

## **Applications**

- DDR-I, DDR-II and DDR-III Termination Voltage

- SSTL-18 Termination

- SSTL-2 and SSTL-3 Termination

- HSTL Termination

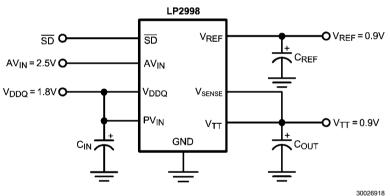

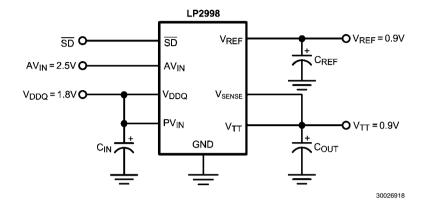

# **Typical Application Circuit**

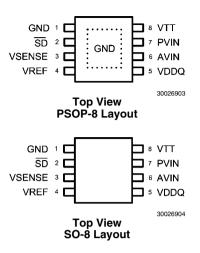

# **Connection Diagrams**

# **Pin Descriptions**

| SO-8 Pin or PSOP-8 Pin | Name   | Function                                                              |  |

|------------------------|--------|-----------------------------------------------------------------------|--|

| 1                      | GND    | Ground.                                                               |  |

| 2                      | SD     | Shutdown.                                                             |  |

| 3                      | VSENSE | Feedback pin for regulating V <sub>TT</sub> .                         |  |

| 4                      | VREF   | Buffered internal reference voltage of V <sub>DDQ</sub> /2.           |  |

| 5                      | VDDQ   | Input for internal reference equal to V <sub>DDQ</sub> /2.            |  |

| 6                      | AVIN   | Analog input pin.                                                     |  |

| 7                      | PVIN   | Power input pin.                                                      |  |

| 8                      | VTT    | Output voltage for connection to termination resistors.               |  |

|                        | EP     | Exposed pad thermal connection. Connect to soft Ground (PSOP-8 only). |  |

# **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Supplied As              |

|--------------|--------------|---------------------|--------------------------|

| LP2998MA     | SO-8         | M08A                | 95 Units per Rail        |

| LP2998MAX    | SO-8         | M08A                | 2500 Units Tape and Reel |

| LP2998MAE    | SO-8         | M08A                | 250 Units Tape and Reel  |

| LP2998MR     | PSOP-8       | MRA08A              | 95 Units per Rail        |

| LP2998MRX    | PSOP-8       | MRA08A              | 2500 Units Tape and Reel |

| LP2998MRE    | PSOP-8       | MRA08A              | 250 Units Tape and Reel  |

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Junction Temp. Range (*Note 4*) AVIN to GND

-40°C to +125°C 2.2V to 5.5V

| –0.3V to +6V    |

|-----------------|

| -0.3V to AVIN   |

| –0.3V to +6V    |

| –65°C to +150°C |

| 150°C           |

| 260°C           |

| 151°C/W         |

| 43°C/W          |

| 1kV             |

|                 |

| <b>Electrical Characteristics</b>         | Specifications with standard typeface are for $T_J = 25^{\circ}C$ and limits in <b>boldface type</b>    |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------|

| apply over the full Operating Temperature | <b>Range</b> ( $T_J = -40^{\circ}C$ to $+125^{\circ}C$ ) ( <i>Note 5</i> ). Unless otherwise specified, |

| VIN = AVIN = PVIN = 2.5V.                 |                                                                                                         |

| Symbol            | Parameter                          | Conditions                       | Min   | Тур   | Max   | Units |

|-------------------|------------------------------------|----------------------------------|-------|-------|-------|-------|

|                   | V <sub>REF</sub> Voltage (DDR I)   | VIN = VDDQ = 2.3V                | 1.135 | 1.158 | 1.185 | V     |

|                   |                                    | VIN = VDDQ = 2.5V                | 1.235 | 1.258 | 1.285 | V     |

|                   |                                    | VIN = VDDQ = 2.7V                | 1.335 | 1.358 | 1.385 | V     |

|                   | V <sub>REF</sub> Voltage (DDR II)  | PVIN = VDDQ = 1.7V               | 0.837 | 0.860 | 0.887 | V     |

| $V_{REF}$         |                                    | PVIN = VDDQ = 1.8V               | 0.887 | 0.910 | 0.937 | V     |

|                   |                                    | PVIN = VDDQ = 1.9V               | 0.936 | 0.959 | 0.986 | V     |

|                   | V <sub>REF</sub> Voltage (DDR III) | PVIN = VDDQ = 1.35V              | 0.669 | 0.684 | 0.699 | V     |

|                   |                                    | PVIN = VDDQ = 1.5V               | 0.743 | 0.758 | 0.773 | V     |

|                   |                                    | PVIN = VDDQ = 1.6V               | 0.793 | 0.808 | 0.823 | V     |

| Z <sub>VREF</sub> | V <sub>REF</sub> Output Impedance  | I <sub>REF</sub> = -30 to +30 μA |       | 2.5   |       | kΩ    |

| $\mathbf{\omega}$ |  |

|-------------------|--|

| ົ                 |  |

| ົ                 |  |

| N                 |  |

| 0                 |  |

|                   |  |

Г

| Symbol                    | Parameter                                                                                                 | Conditions                               | Min    | Тур    | Max   | Un       |

|---------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------|--------|--------|-------|----------|

|                           |                                                                                                           | I <sub>OUT</sub> = 0A                    |        |        |       |          |

|                           |                                                                                                           | VIN = VDDQ = 2.3V                        | 1.120  | 1.159  | 1.190 | ν        |

|                           |                                                                                                           | VIN = VDDQ = 2.5V                        | 1.210  |        |       | l v      |

|                           |                                                                                                           | VIN = VDDQ = 2.7V                        | 1.320  |        |       | ν        |

|                           | V <sub>TT</sub> Output Voltage (DDR I) ( <i>Note 8</i> )                                                  | I <sub>OUT</sub> = +/- 1.5A              |        |        |       |          |

|                           |                                                                                                           | VIN = VDDQ = 2.3V                        | 1 1 25 | 1 1 50 | 1.190 | \        |

|                           |                                                                                                           |                                          |        | 1.159  |       |          |

|                           |                                                                                                           | VIN = VDDQ = 2.5V                        |        | 1.259  |       |          |

|                           |                                                                                                           | VIN = VDDQ = 2.7V                        | 1.325  | 1.359  | 1.390 | \        |

|                           |                                                                                                           | I <sub>OUT</sub> = 0A, AVIN = 2.5V       |        |        |       |          |

|                           |                                                                                                           | PVIN = VDDQ = 1.7V                       |        | 0.856  |       | \        |

|                           |                                                                                                           | PVIN = VDDQ = 1.8V                       | 0.874  | 0.908  | 0.939 | \        |

|                           | V <sub>TT</sub> Output Voltage (DDR II) ( <i>Note 8</i> )                                                 | PVIN = VDDQ = 1.9V                       | 0.923  | 0.957  | 0.988 | \        |

|                           |                                                                                                           | I <sub>OUT</sub> = +/- 0.5A, AVIN = 2.5V |        |        |       |          |

|                           |                                                                                                           | PVIN = VDDQ = 1.7V                       | 0.820  | 0.856  | 0.890 | <u>۱</u> |

|                           |                                                                                                           | PVIN = VDDQ = 1.8V                       | 0.870  | 0.908  | 0.940 | \        |

|                           |                                                                                                           | PVIN = VDDQ = 1.9V                       | 0.920  | 0.957  | 0.990 | ۱        |

| $V_{TT}$                  |                                                                                                           | I <sub>OUT</sub> = 0A, AVIN = 2.5V       |        |        |       |          |

|                           |                                                                                                           | PVIN = VDDQ = 1.35V                      | 0 656  | 0.677  | 0.698 | \        |

|                           |                                                                                                           | PVIN = VDDQ = 1.5V                       |        | 0.752  |       |          |

|                           |                                                                                                           |                                          |        |        |       |          |

|                           |                                                                                                           | PVIN = VDDQ = 1.6V                       | 0.781  |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = +0.2A, AVIN = 2.5V    | 0.667  | 0.688  | 0.710 | \        |

|                           |                                                                                                           | PVIN = VDDQ = 1.35V                      |        |        |       |          |

|                           | V <sub>TT</sub> Output Voltage (DDR III) ( <i>Note 8</i> )                                                | I <sub>OUT</sub> = -0.2A, AVIN = 2.5V    | 0.641  | 0.673  | 0.694 | ١        |

|                           |                                                                                                           | PVIN = VDDQ = 1.35V                      |        |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = +0.4A, AVIN = 2.5V    | 0.740  | 0.763  | 0.786 | ١        |

|                           |                                                                                                           | PVIN = VDDQ = 1.5V                       |        |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = -0.4A, AVIN = 2.5V    | 0.731  | 0.752  | 0.773 | ۱        |

|                           |                                                                                                           | PVIN = VDDQ = 1.5V                       |        |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = +0.5A, AVIN = 2.5V    | 0.790  | 0.813  | 0.836 | ١        |

|                           |                                                                                                           | PVIN = VDDQ = 1.6V                       |        |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = -0.5A, AVIN = 2.5V    | 0.781  | 0.802  | 0.823 | ۱ ا      |

|                           |                                                                                                           | PVIN = VDDQ = 1.6V                       |        |        |       |          |

|                           | V <sub>TT</sub> Output Voltage Offset (V <sub>BEE</sub> – V <sub>TT</sub> ) for DDR I ( <i>Note 8</i> )   | I <sub>OUT</sub> = 0A                    | -30    | 0      | 30    | m        |

|                           |                                                                                                           |                                          | -30    | 0      | 30    | m        |

|                           |                                                                                                           | $I_{OUT} = -1.5A$                        |        |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = +1.5A                 | -30    | 0      | 30    | m        |

|                           | V <sub>TT</sub> Output Voltage Offset (V <sub>REF</sub> – V <sub>TT</sub> ) for DDR II ( <i>Note 8</i> )  |                                          |        |        |       |          |

|                           |                                                                                                           | I <sub>OUT</sub> = 0A                    | -30    | 0      | 30    | m        |

| $\text{VOS}_{\text{Vtt}}$ |                                                                                                           | I <sub>OUT</sub> = -0.5A                 | -30    | 0      | 30    | m        |

|                           |                                                                                                           | I <sub>OUT</sub> = +0.5A                 | -30    | 0      | 30    | m        |

|                           | V <sub>TT</sub> Output Voltage Offset (V <sub>REF</sub> – V <sub>TT</sub> ) for DDR III ( <i>Note 8</i> ) | I <sub>OUT</sub> = 0A                    | -30    | 0      | 30    | m        |

|                           |                                                                                                           | $I_{OUT} = \pm 0.2A$                     | -30    | 0      | 30    | m        |

|                           |                                                                                                           | $I_{OUT} = \pm 0.4A$                     | -30    | 0      | 30    | m        |

|                           |                                                                                                           |                                          |        | _      |       |          |

|                           |                                                                                                           | $I_{OUT} = \pm 0.5A$                     | -30    | 0      | 30    | m        |

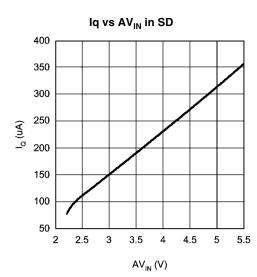

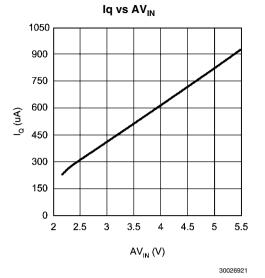

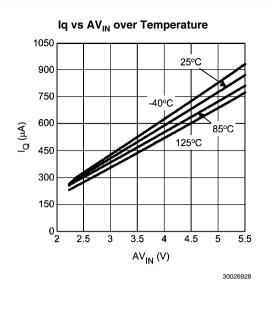

| ۱ <sub>Q</sub>            | Quiescent Current (Note 6)                                                                                | I <sub>OUT</sub> = 0A                    |        | 320    | 500   | μ        |

| $Z_{VDDQ}$                | VDDQ Input Impedance                                                                                      |                                          |        | 100    |       | k        |

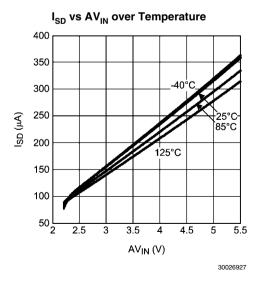

| I <sub>SD</sub>           | Quiescent current in shutdown ( <i>Note 6</i> )                                                           | SD = 0V                                  |        | 115    | 150   | μ        |

|                           | Shutdown leakage current                                                                                  | SD = 0V                                  |        | 2      | 5     | μ        |

|                           |                                                                                                           |                                          | 10     | -      |       | <u> </u> |

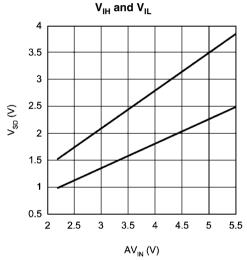

| V <sub>IH</sub>           | Minimum Shutdown High Level                                                                               |                                          | 1.9    |        |       | \        |

| V <sub>IL</sub>           | Maximum Shutdown Low Level                                                                                |                                          |        |        | 0.8   | \        |

| lv                        | V <sub>TT</sub> leakage current in shutdown                                                               | SD = 0V                                  |        | 1      | 10    | μ        |

|                           | 1                                                                                                         | V <sub>TT</sub> = 1.25V                  |        |        |       |          |

| Symbol              | Parameter                          | Conditions | Min | Тур | Max | Units |

|---------------------|------------------------------------|------------|-----|-----|-----|-------|

| ISENSE              | V <sub>SENSE</sub> Input current   |            |     | 13  |     | nA    |

| T <sub>SD</sub>     | Thermal Shutdown ( <i>Note 7</i> ) |            |     | 165 |     | °C    |

| T <sub>SD_HYS</sub> | Thermal Shutdown Hysteresis        |            |     | 10  |     | °C    |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating range indicates conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and test conditions see Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: VDDQ voltage must be less than 2 x (AVIN - 1) or 6V, whichever is smaller.

Note 3: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

Note 4: At elevated temperatures, devices must be derated based on thermal resistance. The device in the SO-8 package must be derated at θ<sub>JA</sub> = 151.2° C/W junction to ambient with no heat sink.

Note 5: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 6: Quiescent current is defined as the current flow into AVIN.

Note 7: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(MAX)}$ , the junction to ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature and the regulator will go into thermal shutdown.

Note 8:  $V_{TT}$  load regulation is tested by using a 10 ms current pulse and measuring  $V_{TT}$ .

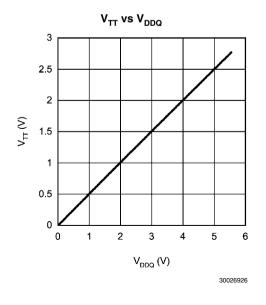

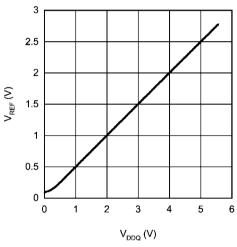

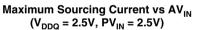

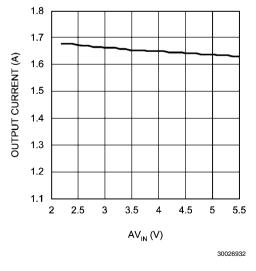

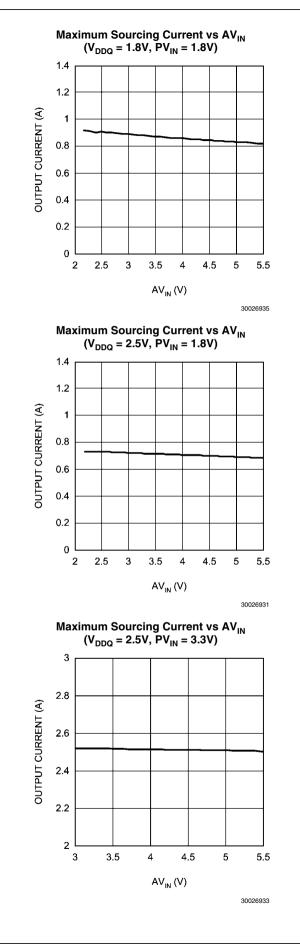

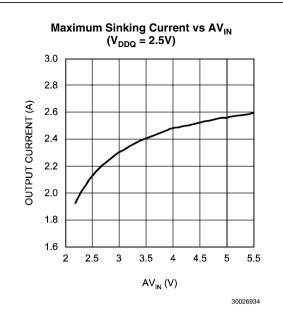

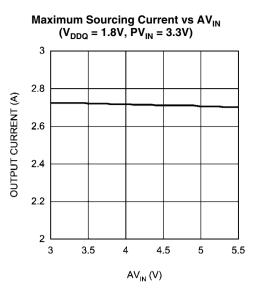

# Typical Performance Characteristics Unless otherwise specified VIN = AVIN = PVIN = 2.5V

30026937

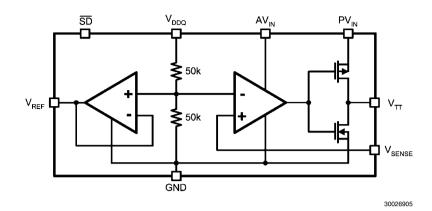

## **Block Diagram**

## **Description**

The LP2998 is a linear bus termination regulator designed to meet the JEDEC requirements of SSTL-2 and SSTL-18. The output,  $V_{TT}$  is capable of sinking and sourcing current while regulating the output voltage equal to VDDQ / 2. The output stage has been designed to maintain excellent load regulation while preventing shoot through. The LP2998 also incorporates two distinct power rails that separates the analog circuitry from the power output stage. This allows a split rail approach to be utilized to decrease internal power dissipation. It also permits the LP2998 to provide a termination solution for the next generation of DDR-SDRAM memory (DDRII). The LP2998 can also be used to provide a termination voltage for other logic schemes such as SSTL-3 or HSTL.

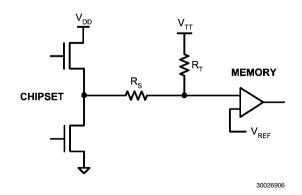

Series Stub Termination Logic (SSTL) was created to improve signal integrity of the data transmission across the memory bus. This termination scheme is essential to prevent data error from signal reflections while transmitting at high frequencies encountered with DDR-SDRAM. The most common form of termination is Class II single parallel termination. This involves one  $R_{\rm S}$  series resistor from the chipset to the memory and one  $R_{\rm T}$  termination resistor. Typical values for  $R_{\rm S}$  and  $R_{\rm T}$  are 25 Ohms, although these can be changed to scale the current requirements from the LP2998. This implementation can be seen below in .

FIGURE 1. SSTL-Termination Scheme

## **Pin Descriptions**

#### **AVIN AND PVIN**

AVIN and PVIN are the input supply pins for the LP2998. AVIN is used to supply all the internal control circuitry. PVIN, however, is used exclusively to provide the rail voltage for the output stage used to create  $V_{\mbox{\scriptsize TT}}.$  These pins have the capability to work off separate supplies, under the condition that AVIN is always greater than or equal to PVIN. For SSTL-18 applications, it is recommended to connect PVIN to the 1.8V rail used for the memory core and AVIN to a rail within its operating range of 2.2V to 5.5V (typically a 2.5V supply). PVIN should always be used with either a 1.8V or 2.5V rail. This prevents the thermal limit from tripping because of excessive internal power dissipation. If the junction temperature exceeds the thermal shutdown threshold, the part will enter a shutdown state identical to the manual shutdown where  $V_{\tau\tau}$ is tri-stated and  $V_{\text{REF}}$  remains active. A lower rail, such as 1.5V can be used but it will reduce the maximum output current. Therefore it is not recommended for most termination schemes.

#### VDDQ

VDDQ is the input used to create the internal reference voltage for regulating V<sub>TT</sub>. The reference voltage is generated from a resistor divider of two internal 50k $\Omega$  resistors. This guarantees that V<sub>TT</sub> will precisely track VDDQ / 2. The optimal implementation of VDDQ is as a remote sense. This can be achieved by connecting VDDQ directly to the 1.8V rail at the DIMM instead of PVIN. This ensures that the reference voltage precisely tracks the DDR memory rails without a large voltage drop from the power lines. For SSTL-18 applications, VDDQ will be a 1.8V signal, which will create a 0.9V termination voltage at V<sub>TT</sub> (See Electrical Characteristics Table for exact values of V<sub>TT</sub> over temperature).

#### V<sub>SENSE</sub>

The purpose of the sense pin is to provide improved remote load regulation. In most motherboard applications, the termination resistors will connect to V<sub>TT</sub> in a long plane. If the output voltage was regulated only at the output of the LP2998, then the long trace will cause a significant IR drop resulting in a termination voltage lower at one end of the bus than the other. The V<sub>SENSE</sub> pin can be used to improve this performance by connecting it to the middle of the bus. This will provide a better distribution across the entire termination bus. If remote load regulation is not used, then the V<sub>SENSE</sub> pin must still be con-

-P2998

nected to V<sub>TT</sub>. Care should be taken when a long V<sub>SENSE</sub> trace is implemented in close proximity to the memory. Noise pick-up in the V<sub>SENSE</sub> trace can cause problems with precise regulation of V<sub>TT</sub>. A small 0.1uF ceramic capacitor placed next to the V<sub>SENSE</sub> pin can help filter any high frequency signals and prevent errors.

#### SHUTDOWN

The LP2998 contains an active low shutdown pin that can be used for suspend to RAM functionality. In this condition, the V<sub>TT</sub> output will tri-state while the V<sub>REF</sub> output remains active providing a constant reference signal for the memory and chipset. During shutdown, V<sub>TT</sub> should not be exposed to voltages that exceed PVIN. With the shutdown pin asserted low the quiescent current of the LP2998 will drop. However, VD-DQ will always maintain its constant impedance of 100k $\Omega$  for generating the internal reference. Therefore, to calculate the total power loss in shutdown, both currents need to be considered. For more information refer to the Thermal Dissipation section. The shutdown pin also has an internal pull-up current. Therefore, to turn the part on, the shutdown pin can either be connected to AVIN or left open.

#### $\mathbf{V}_{\mathsf{REF}}$

$V_{\mathsf{REF}}$  provides the buffered output of the internal reference voltage VDDQ / 2. This output should be used to provide the reference voltage for the Northbridge chipset and memory. Since the inputs typically have an extremely high impedance, there should be little current drawn from  $V_{\mathsf{REF}}$ . For improved performance, an output bypass capacitor can be placed, close to the pin, to help with noise. A ceramic capacitor in the range of 0.1  $\mu F$  to 0.01  $\mu F$  is recommended. This output remains active during the shutdown state and thermal shutdown events for the suspend to RAM functionality.

#### V<sub>TT</sub>

$V_{TT}$  is the regulated output that is used to terminate the bus resistors. It is capable of sinking and sourcing current while regulating the output precisely to VDDQ / 2. The LP2998 is designed to handle continuous currents of up to +/- 1.5A with excellent load regulation. If a transient is expected to last above the maximum continuous current rating for a significant amount of time, then the bulk output capacitor should be sized large enough to prevent an excessive voltage drop. If the LP2998 is to operate in elevated temperatures for long durations, care should be taken to ensure that the maximum operating junction temperature is not exceeded. Proper thermal de-rating should always be used (Please refer to the Thermal Dissipation section). If the junction temperature exceeds the thermal shutdown threshold,  $V_{TT}$  will tri-state until the part returns below the temperature hysteresis trip-point.

## **Component Selections**

#### **INPUT CAPACITOR**

The LP2998 does not require a capacitor for input stability, but it is recommended for improved performance during large load transients to prevent the input rail from dropping. The input capacitor should be located as close as possible to the PVIN pin. Several recommendations exist and is dependent on the application required. A typical value recommended for AL electrolytic capacitors is 22  $\mu$ F. Ceramic capacitors can also be used. A value in the range of 10  $\mu$ F with X5R or better would be an ideal choice. The input capacitance can be reduced if the LP2998 is placed close to the bulk capacitance from the output of the 1.8V DC-DC converter. For the AVIN

pin, a small 0.1uF ceramic capacitor is sufficient to prevent excessive noise from coupling into the device.

#### **OUTPUT CAPACITOR**

The LP2998 has been designed to be insensitive of output capacitor size or ESR (Equivalent Series Resistance). This allows the flexibility to use any capacitor desired. The choice for output capacitor will be determined solely on the application and the requirements for load transient response of V<sub>TT</sub>. As a general recommendation the output capacitor should be sized above 100 µF with a low ESR for SSTL applications with DDR-SDRAM. The value of ESR should be determined by the maximum current spikes expected and the extent at which the output voltage is allowed to droop. Several capacitor options are available on the market and a few of these are highlighted below:

AL - It should be noted that many aluminum electrolytics only specify impedance at a frequency of 120 Hz, which indicates they have poor high frequency performance. Only aluminum electrolytics that have an impedance specified at a higher frequency (100 kHz) should be used for the LP2998. To improve the ESR several AL electrolytics can be combined in parallel for an overall reduction. An important note to be aware of is the extent at which the ESR will change over temperature. Aluminum electrolytic capacitors tend to have rapidly increasing ESR at cold temperatures.

Ceramic - Ceramic capacitors typically have a low capacitance, in the range of 10 to 100  $\mu F$ . They also have excellent AC performance for bypassing noise because of very low ESR (typically less than 10 m\Omega). However, some dielectric types do not have good capacitance characteristics as a function of voltage and temperature. Because of the typically low value of capacitance, it is recommended to use ceramic capacitors in parallel with another capacitor such as an aluminum electrolytic. A dielectric of X5R or better is recommended for all ceramic capacitors.

Hybrid - Several hybrid capacitors such as OS-CON and SP are available from several manufacturers. These offer a large capacitance while maintaining a low ESR. These are the best solution when size and performance are critical, although their cost is typically higher than any other capacitor type.

## **Thermal Dissipation**

Since the LP2998 is a linear regulator, any current flow from  $V_{TT}$  will result in internal power dissipation and heat generation. To prevent damaging the part by exceeding the maximum allowable operating junction temperature, care should be taken to derate the part based on the maximum expected ambient temperature and power dissipation. The maximum allowable internal temperature rise ( $T_{Rmax}$ ) can be calculated given the maximum ambient temperature ( $T_{Amax}$ ) of the application and the maximum allowable junction temperature ( $T_{Jmax}$ ).

### $T_{Rmax} = T_{Jmax} - T_{Amax}$

From this equation, the maximum power dissipation ( ${\rm P}_{\rm Dmax}$ ) of the part can be calculated:

$$P_{\text{Dmax}} = T_{\text{Rmax}} / \theta_{\text{JA}}$$

The  $\theta_{JA}$  of the LP2998 will depend on several variables: the package used; the thickness of copper; the number of vias and the airflow. For instance, the  $\theta_{JA}$  of the SO-8 is 163°C/W with the package mounted to a standard 8x4 2-layer board with 1oz. copper, no airflow, and 0.5W dissipation at room temperature. This value can be reduced to 151.2°C/W by changing to a 3x4 board with 2 oz. copper that is the JEDEC

standard. Figure 2 shows how the  $\theta_{JA}$  varies with airflow for the two boards mentioned.

FIGURE 2.  $\theta_{JA}$  vs Airflow (SO-8)

Additional improvements can be made by the judicious use of vias to connect the part and dissipate heat to an internal ground plane. Using larger traces and more copper on the top side of the board can also help. With careful layout, it is possible to reduce the  $\theta_{JA}$  further than the nominal values shown in *Figure 2*

Optimizing the  $\theta_{JA}$  and placing the LP2998 in a section of a board exposed to lower ambient temperature allows the part

to operate with higher power dissipation. The internal power dissipation can be calculated by summing the three main sources of loss: output current at  $V_{TT}$ , either sinking or sourcing, and quiescent currents at AVIN and VDDQ. During the active state (when shutdown is not held low) the total internal power dissipation can be calculated from the following equations:

Where,

P\

$$P_{AVIN} = I_{AVIN} * V_{AVIN}$$

$\mathsf{P}_\mathsf{D} = \mathsf{P}_\mathsf{AVIN} + \mathsf{P}_\mathsf{VDDQ} + \mathsf{P}_\mathsf{VTT}$

$$V_{DDQ} = V_{VDDQ} * I_{VDDQ} = V_{VDDQ^2} \times R_{VDDQ}$$

To calculate the maximum power dissipation at V<sub>TT</sub>, both the sinking and sourcing current conditions need to be examined. Although only one equation will add into the total, V<sub>TT</sub> cannot source and sink current simultaneously.

$$P_{VTT} = V_{VTT} \times I_{LOAD}$$

(Sinking) or

$$P_{VTT} = (V_{PVIN} - V_{VTT}) \times I_{LOAD}$$

(Sourcing)

The power dissipation of the LP2998 can also be calculated during the shutdown state. During this condition the output  $V_{TT}$  will tri-state. Therefore, that term in the power equation will disappear as it cannot sink or source any current (leakage is negligible). The only losses during shutdown will be the reduced quiescent current at AVIN and the constant impedance that is seen at the VDDQ pin.

$$P_{\rm D} = P_{\rm AVIN} + P_{\rm VDDQ}$$

$$P_{AVIN} = I_{AVIN} \times V_{AVIN}$$

$$P_{VDDQ} = V_{VDDQ} * I_{VDDQ} = V_{VDDQ^2} \times R_{VDDQ}$$

## **Typical Application Circuits**

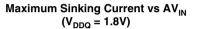

Several different application circuits have been shown in *Figure 3* through *Figure 12* to illustrate some of the options that are possible in configuring the LP2998. Graphs of the individual circuit performance can be found in the *Typical Performance Characteristics* section of the datasheet. These curves illustrate how the maximum output current is affected by changes in AVIN and PVIN.

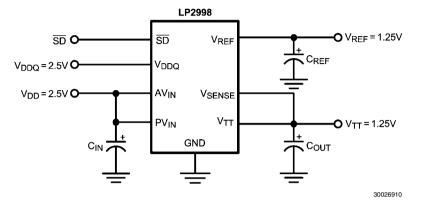

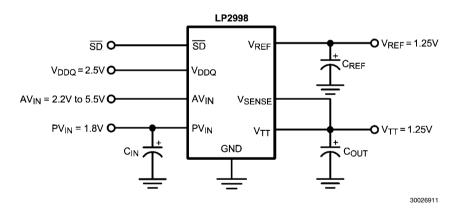

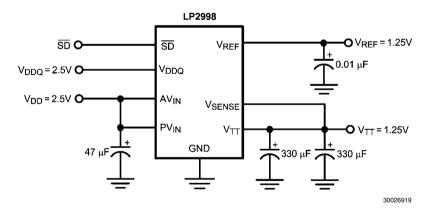

#### **SSTL-2 APPLICATIONS**

For the majority of applications that implement the SSTL-2 termination scheme it is recommended to connect all the input rails to the 2.5V rail. This provides an optimal trade-off between power dissipation and component count and selection. An example of this circuit can be seen in *Figure 3*.

FIGURE 3. Recommended SSTL-2 Implementation

If power dissipation or efficiency is a major concern then the LP2998 has the ability to operate on split power rails (see *Figure 4*). The output stage (PVIN) can be operated on a lower rail such as 1.8V and the analog circuitry (AVIN) can be connected to a higher rail such as 2.5V, 3.3V or 5V. This allows the internal power dissipation to be lowered when sourcing

current from V<sub>TT</sub>. The disadvantage of this circuit is that the maximum continuous current is reduced because of the lower rail voltage, although it is adequate for all motherboard SSTL-2 applications. Increasing the output capacitance can also help if periods of large load transients will be encountered.

FIGURE 4. Lower Power Dissipation SSTL-2 Implementation

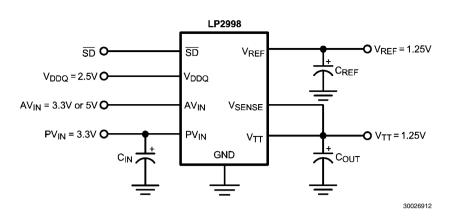

The third option for SSTL-2 applications in the situation that a 1.8V rail is not available and it is not desirable to use 2.5V, is to connect the LP2998 power rail to 3.3V (see *Figure 5*). In this situation AVIN will be limited to operation on the 3.3V or 5V rail as PVIN can never exceed AVIN. This configuration has the ability to provide the maximum continuous output current at the downside of higher thermal dissipation. Care should be taken to prevent the LP2998 from experiencing large current levels which cause the device to exceed the maximum operating junction temperature. Because of this risk it is not recommended to supply the output stage with a voltage higher than a nominal 3.3V rail.

FIGURE 5. SSTL-2 Implementation With Higher Voltage Rails

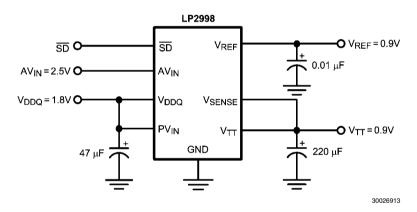

#### **DDR-II APPLICATIONS**

With the separate VDDQ pin and an internal resistor divider it is possible to use the LP2998 in applications utilizing DDR-II memory. *Figure 6* and *Figure 7* show several implementations of recommended circuits with output curves displayed in the *Typical Performance Characteristics*. Figure 6 shows the recommended circuit configuration for DDR-II applications. The output stage is connected to the 1.8V rail and the AVIN pin can be connected to either a 2.5, 3.3V or 5.5V rail.

FIGURE 6. Recommended DDR-II Termination

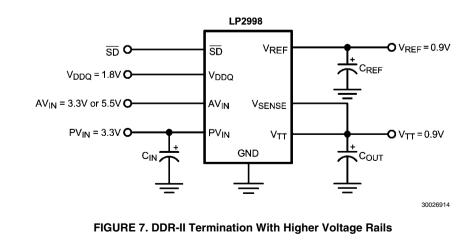

If it is not desirable to use the 1.8V rail it is possible to connect the output stage to a 3.3V rail. Care should be taken to not exceed the maximum operating junction temperature as the thermal dissipation increases with lower  $V_{TT}$  output voltages.

For this reason it is not recommended to power PVIN with a rail higher than the nominal 3.3V. The advantage of this configuration is that it has the ability to source and sink a higher maximum continuous current.

#### LEVEL SHIFTING

-P2998

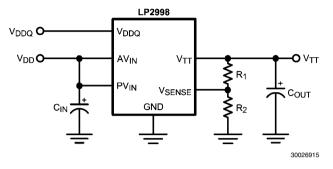

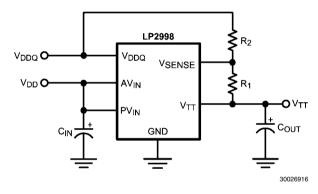

If standards other than SSTL-2 are required, such as SSTL-3, it may be necessary to use a different scaling factor than 0.5 times  $V_{DDQ}$  for regulating the output voltage. Several options are available to scale the output to any voltage required. One method is to level shift the output by using feedback resistors

from V<sub>TT</sub> to the V<sub>SENSE</sub> pin. This has been illustrated in *Figure* 8 and *Figure 9*. *Figure 8* shows how to use two resistors to level shift V<sub>TT</sub> above the internal reference voltage of VDDQ/ 2. To calculate the exact voltage at V<sub>TT</sub> the following equation can be used.

$$V_{TT} = VDDQ/2 (1 + R1/R2)$$

FIGURE 8. Increasing VTT by Level Shifting

Conversely, the R2 resistor can be placed between V<sub>SENSE</sub> and V<sub>DDQ</sub> to shift the V<sub>TT</sub> output lower than the internal reference voltage of VDDQ/2. The equation relating to VTT and the resistors can be used as shown:

V<sub>TT</sub> = VDDQ/2 (1 - R1/R2)

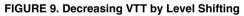

#### **HSTL APPLICATIONS**

The LP2998 can be easily adapted for HSTL applications by connecting  $V_{\text{DDQ}}$  to the 1.5V rail. This will produce a  $V_{\text{TT}}$  and

$V_{\text{REF}}$  voltage of approximately 0.75V for the termination resistors. AVIN and PVIN should be connected to a 2.5V rail for optimal performance.

#### QDR APPLICATIONS

Quad data rate (QDR) applications utilize multiple channels for improved memory performance. However, this increase in bus lines increases the current levels required for termination. The recommended approach in terminating multiple channels is to use a dedicated LP2998 for each channel. This simplifies layout and reduces the internal power dissipation for each regulator. Separate  $V_{\text{REF}}$  signals can be used for each DIMM bank from the corresponding regulator with the chipset reference provided by a local resistor divider or one of the LP2998 signals. Because  $V_{REF}$  and  $V_{TT}$  are expected to track and the part to part variations are minor, there should be little difference between the reference signals of each LP2998.

#### **OUTPUT CAPACITOR SELECTION**

For applications utilizing the LP2998 to terminate SSTL-2 I/O signals the typical application circuit shown in *Figure 11* can be implemented.

FIGURE 11. Typical SSTL-2 Application Circuit

This circuit permits termination in a minimum amount of board space and component count. Capacitor selection can be varied depending on the number of lines terminated and the maximum load transient. However, with motherboards and other applications where  $V_{TT}$  is distributed across a long plane, it is recommended to use multiple bulk capacitors in

addition to high frequency decoupling. *Figure 12* depicts an example circuit where 2 bulk output capacitors could be situated at both ends of the  $V_{TT}$  plane for optimal placement. Large aluminum electrolytic capacitors are typically used for their low ESR and low cost.

FIGURE 12. Typical SSTL-2 Application Circuit for Motherboards

In most PC applications, an extensive amount of decoupling is required because of the long interconnects encountered with the DDR-SDRAM DIMMs mounted on modules. As a result, bulk aluminum electrolytic capacitors in the range of 1000uF are typically used.

## **PCB Layout Considerations**

- 1. The input capacitor for the power rail should be placed as close as possible to the PVIN pin.

- 2.  $V_{\text{SENSE}}$  should be connected to the  $V_{\text{TT}}$  termination bus at the point where regulation is required. For motherboard applications an ideal location would be at the center of the termination bus.

- 3.  $V_{DDQ}$  can be connected remotely to the  $V_{DDQ}$  rail input at either the DIMM or the Chipset. This provides the most accurate point for creating the reference voltage.

- 4. For improved thermal performance excessive top side copper should be used to dissipate heat from the

package. Numerous vias from the ground connection to the internal ground plane will help. Additionally these can be located underneath the package if manufacturing standards permit.

- 5. Care should be taken when routing the V<sub>SENSE</sub> trace to avoid noise pickup from switching I/O signals. A 0.1uF ceramic capacitor located close to the <sub>SENSE</sub> can also be used to filter any unwanted high frequency signal. This can be an issue especially if long <sub>SENSE</sub> traces are used.

- 6.  $V_{\text{REF}}$  should be bypassed with a 0.01  $\mu$ F or 0.1  $\mu$ F ceramic capacitor for improved performance. This capacitor should be located as close as possible to the  $V_{\text{REF}}$  pin.

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959

National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com