## 8206 ERROR DETECTION AND CORRECTION UNIT

- Detects All Single Bit, and Double Bit and Most Multiple Bit Errors

- **Corrects All Single Bit Errors**

| • | 3 Selections | 8206-1 | 8206  |

|---|--------------|--------|-------|

|   | Detection    | 35 ns  | 42 ns |

|   | Correction   | 55 ns  | 67 ns |

- **■** Syndrome Outputs for Error Logging

- Automatic Error Scrubbing with 8207

- **Expandable to Handle 80 Bit Memories**

- Separate Input and Output Busses—No Timing Strobes Required

- Supports Read With and Without Correction, Writes, Partial (Byte) Writes, and Read-Modify-Writes

- HMOS III Technology for Low Power

- **■** 68 Pin Leadless JEDEC Package

- 68 Pin Grid Array Package

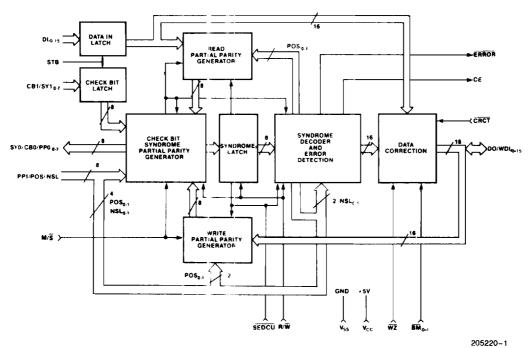

The HMOS 8206 Error Detection and Correction Unit is a high-speed device that provides error detection and correction for memory systems (static and dynamic) requiring high reliability and performance. Each 8206 handles 8 or 16 data bits and up to 8 check bits. 8206's can be cascaded to provide correction and detection for up to 80 bits of data. Other 8206 features include the ability to handle byte writes, memory initialization, and error logging.

Figure 1. 8206 Block Diagram

The complete document for this product is available on Intel's "Data-on-Demand" CD-ROM product. Contact your local Intel field sales office, Intel technical distributor, or call 1-800-548-4725.