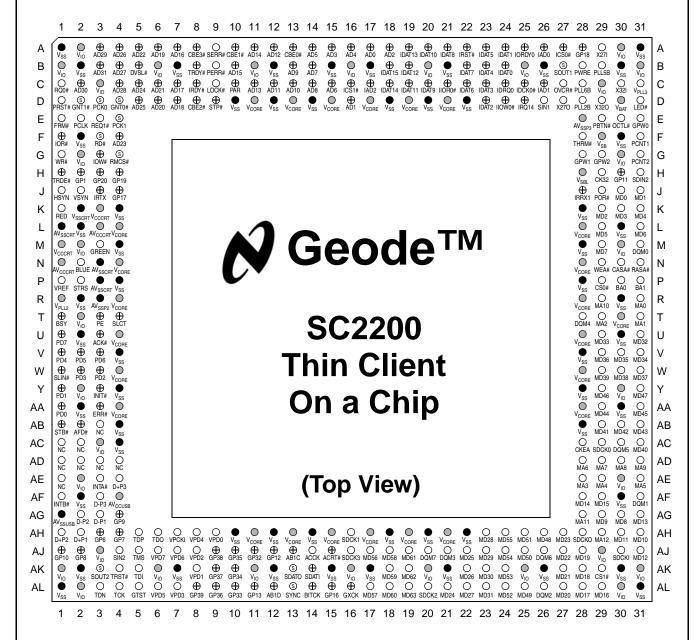

## Geode™ SC2200 Thin Client On a Chip

### **General Description**

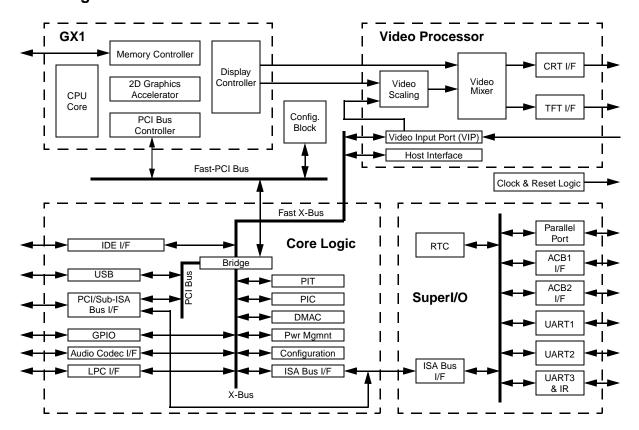

The Geode™ SC2200 Thin Client On a Chip device is a member of the National Semiconductor® IA (Information Appliance) On a Chip family of fully integrated x86 system chips. The Geode SC2200 includes:

- The Geode GX1 processor module combines advanced CPU performance with Intel MMX support, fully accelerated 2D graphics, a 64-bit synchronous DRAM (SDRAM) interface, a PCI bus controller, and a display controller.

- A low-power CRT and TFT Video Processor module with a Video Input Port (VIP), and a hardware video accelerator for scaling, filtering, and color space conversion.

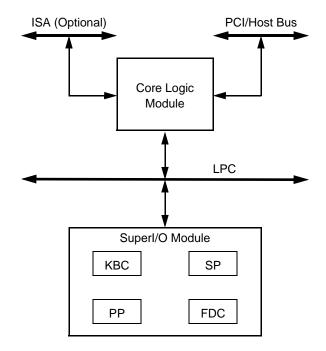

- The Core Logic module includes: PC/AT functionality, a USB interface, an IDE interface, a PCI bus interface, an LPC bus interface, Advanced Configuration Power Interface (ACPI) version 1.0 compliant power management, and an audio codec interface.

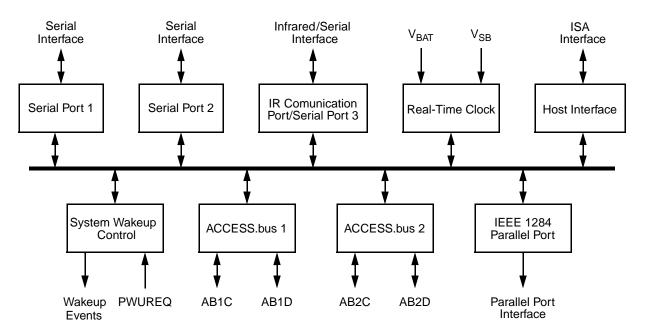

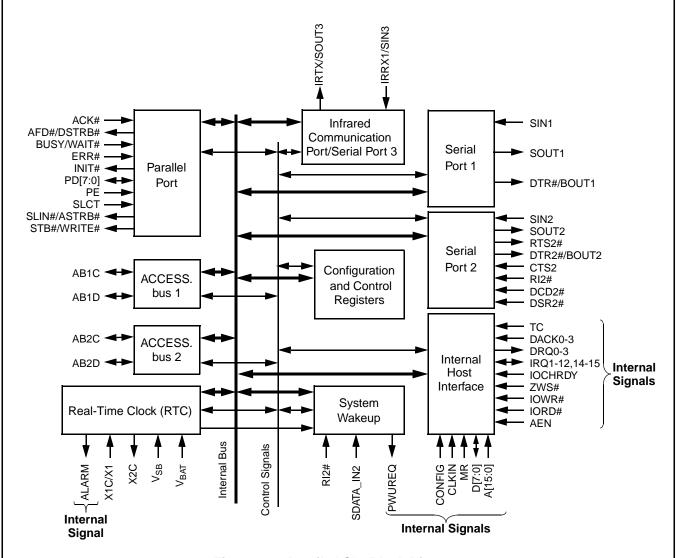

- The SuperI/O module has: three Serial Ports (UART1, UART2, and UART3 with fast infrared), a Parallel Port, two ACCESS.bus (ACB) interfaces, and a Real-Time Clock (RTC).

The block diagram shows the relationships between the modules.

These features, combined with the device's small form factor and low power consumption, make it ideal as the core for a thin client application.

### **Block Diagram**

National Semiconductor and Virtual System Architecture are registered trademarks of National Semiconductor Corporation. Geode and VSA are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

### **Features**

#### **General Features**

- 32-Bit x86 processor, up to 300 MHz, with MMX instruction set support

- Memory controller with 64-bit SDRAM interface

- 2D graphics accelerator

- CRT controller with hardware video accelerator

- CCIR-656 video input port with direct video for full screen display

- PC/AT functionality

- PCI bus controller

- IDE interface, two channels

- USB, three ports, OHCI (OpenHost Controller Interface) version 1.0 compliant

- Audio, AC97/AMC97 version 2.0 compliant

- Virtual System Architecture<sup>®</sup> (VSA<sup>TM</sup>) technology support

- Power management, ACPI (Advanced Configuration Power Interface) version 1.0 compliant

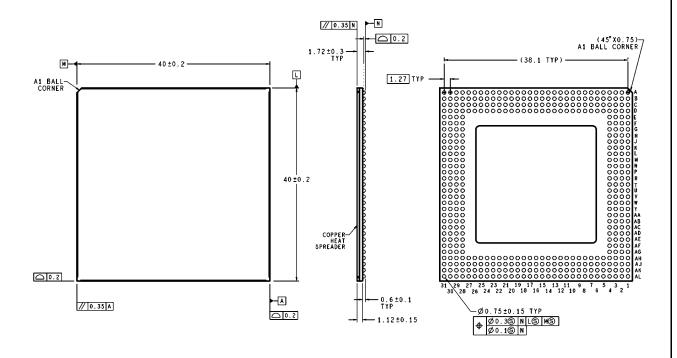

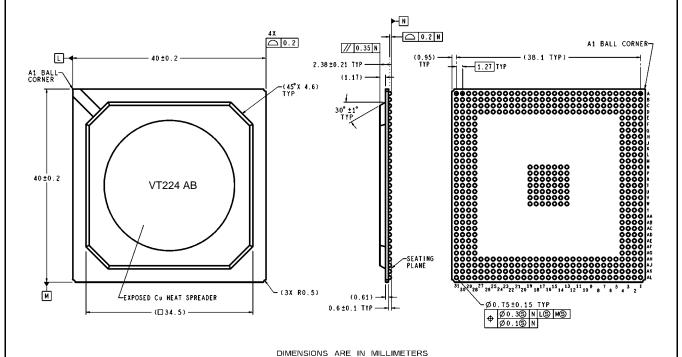

- Package:

- 432-Terminal EBGA (Enhanced Ball Grid Array)

- 481-Terminal TEPBGA (Thermally Enhanced Plastic Ball Grid Array)

### **GX1 Processor Module**

- CPU Core:

- 32-Bit x86, 300 MHz, with MMX compatible instruction set support

- 16 KB unified L1 cache

- Integrated Floating Point Unit (FPU)

- Re-entrant SMM (System Management Mode) enhanced for VSA

- 2D Graphics Accelerator:

- Accelerates BitBLTs, line draw and text

- Supports all 256 raster operations

- Supports transparent BLTs

- Runs at core clock frequency

#### ■ Memory Controller:

- 64-Bit SDRAM interface

- 66 MHz to 100 MHz frequency range

- Direct interface with CPU/cache, display controller and 2D graphic accelerator

- Supports clock suspend and power-down/selfrefresh

- Up to two banks of SDRAM (8 devices total) or one SODIMM

#### ■ Display Controller:

- Hardware graphics frame buffer compress/decompress

- Hardware cursor, 32x32 pixels

#### Video Processor Module

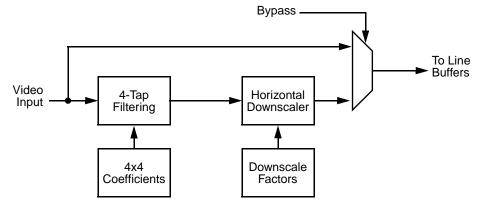

- Video Accelerator:

- Flexible video scaling support of up to 8x (horizontally and vertically)

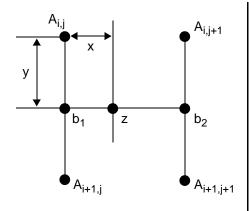

- Bilinear interpolation filters (with two taps, and eight phases) to smooth output video

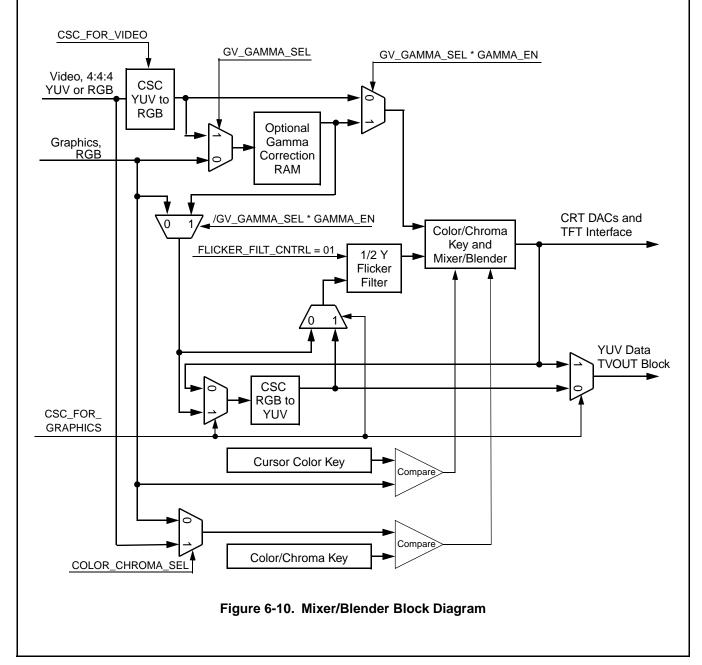

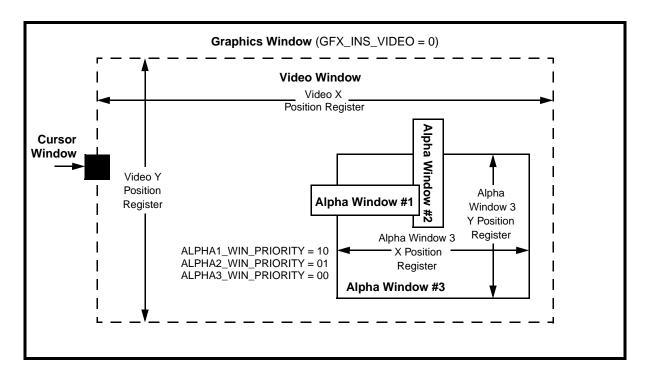

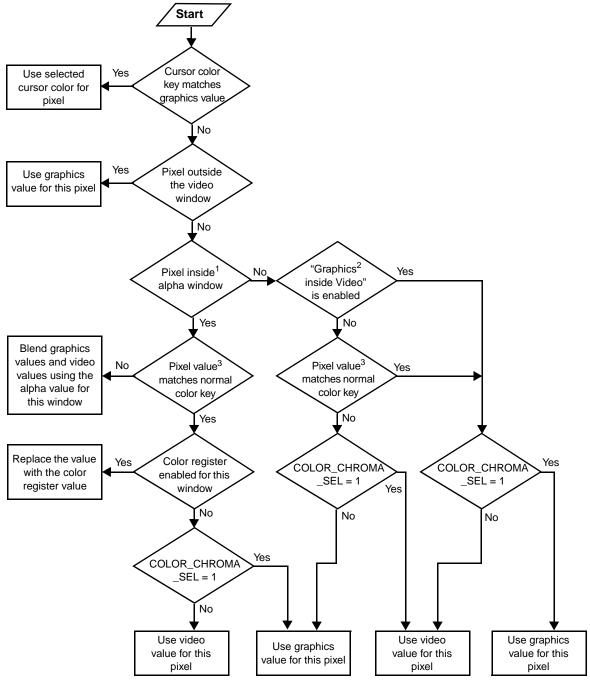

- Video/Graphics Mixer:

- 8-bit value alpha blending

- Three blending windows with constant alpha value

- Color key

- Video Input Port (VIP):

- Video capture or display

- CCIR-656 format and VESA Video Interface Port Rev 1.1 compliant

- Lock display timing to video input timing (GenLock)

- Able to transfer video data into main memory

- Direct video transfer for full screen display

- Separate memory location for VBI

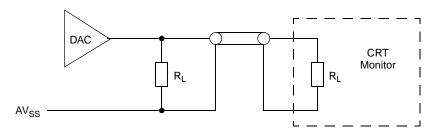

#### ■ CRT Interface:

- Uses three 8-bit DACs

- Supports up to 135 MHz

- 1280x1024 non-interlaced CRT @ 8 bpp, up to 75 Hz

- 1024x768 non-interlaced CRT @ 16 bpp, up to 85 Hz

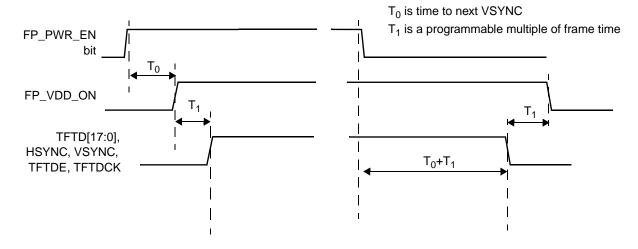

#### ■ TFT Interface:

- Direct connection to TFT panels

- 800x600 non-interlaced TFT @ 16 bpp graphics, up to 85 Hz

- 1024x768 non-interlaced TFT @ 16 bpp graphics, up to 75 Hz

- Connects to Geode CS9211 companion for DSTN panel support

- TFT on IDE: FPCLK max is 40 MHz

- TFT on Parallel Port: FPCLK max is 80 MHz

### Features (Continued)

#### **Core Logic Module**

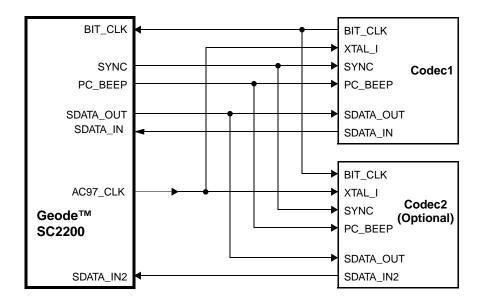

- Audio Codec Interface:

- AC97/AMC97 (Rev. 2.0) codec interface

- Six DMA channels

- PC/AT Functionality:

- Programmable Interrupt Controller (PIC), 8259A-equivalent

- Programmable Interval Timer (PIT), 8254-equivalent

- DMA Controller (DMAC), 8237-equivalent

- Power Management:

- ACPI 1.0 compliant

- Sx state control of three power planes

- Cx/Sx state control of clocks and PLLs

- Thermal event input

- Wakeup event support:

- Three general-purpose events

- AC97 codec event

- UART2 RI# signal

- Infrared (IR) event

- General Purpose I/Os (GPIOs):

- 27 multiplexed GPIO signals

- Low Pin Count (LPC) Bus Interface:

- Specification version 1.0 compatible

- PCI Bus Interface:

- PCI version 2.1 compliant with wakeup capability

- 32-Bit data path, up to 33 MHz

- Glueless interface for an external PCI device

- Fixed priority

- 3.3V signal support only

- Sub-ISA Bus Interface:

- Up to 16 MB addressing

- Supports a chip select for ROM or Flash EPROM boot device

- Supports either:

- M-Systems DiskOnChip DOC2000 Flash file system

- NAND EEPROM

- Supports up to two chip selects for external I/O devices

- 8-Bit (optional 16-bit) data bus width

- Shares balls with PCI signals

- Is not a subtractive agent

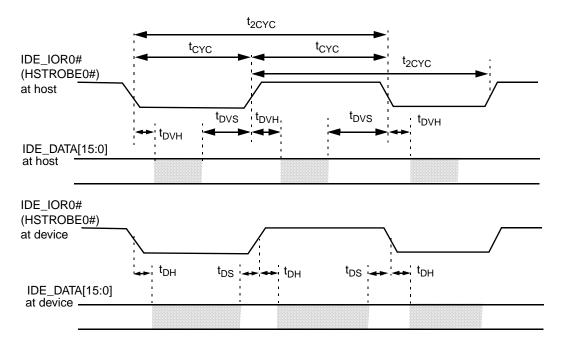

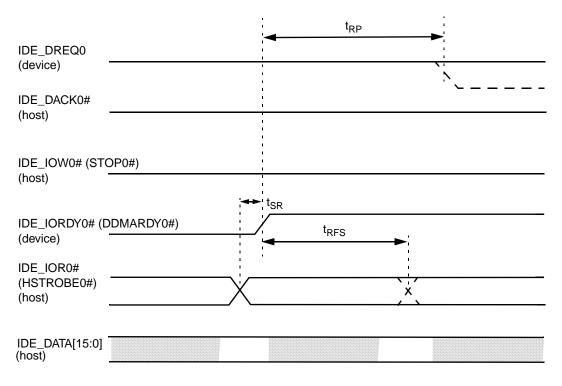

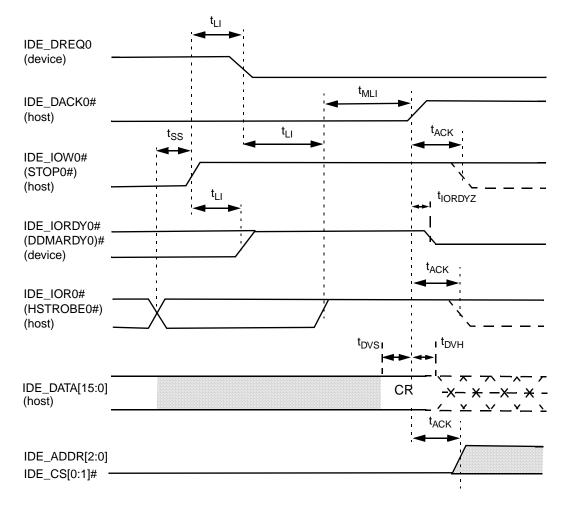

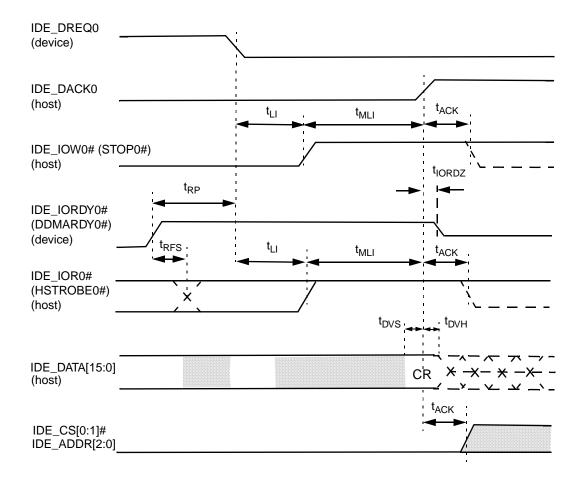

#### ■ IDE Interface:

- Two IDE channels for up to four external IDE devices

- Supports ATA-33 synchronous DMA mode transfers, up to 33 MB/s

- Universal Serial Bus (USB):

- USB OpenHCI 1.0 compliant

- Three ports

#### SuperI/O Module

- Real-Time Clock (RTC):

- DS1287, MC146818 and PC87911 compatible

- Multi-century calendar

- ACCESS.bus (ACB) Interface:

- Two ACB interface ports

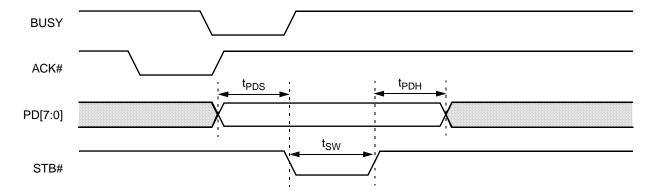

- Parallel Port:

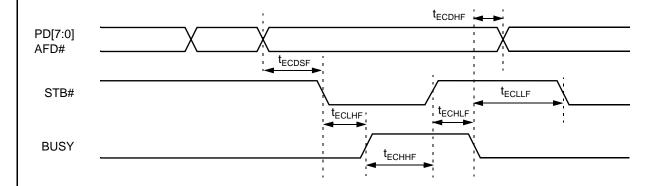

- EPP 1.9 compliant

- IEEE 1284 ECP compliant, including level 2

- Serial Port (UART):

- UART1, 16550A compatible (SIN, SOUT, BOUT pins), used for SmartCard interface

- UART2, 16550A compatible

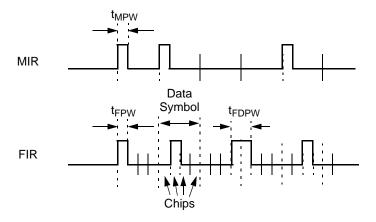

- Enhanced UART with fast Infrared (IR)

#### Other Features

- High-Resolution Timer:

- 32-Bit counter with 1 μs count interval

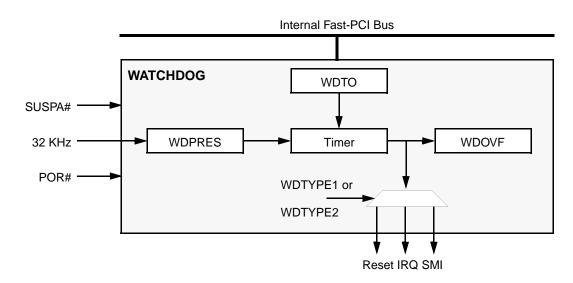

- WATCHDOG Timer:

- Interfaces to INTR, SMI, Reset

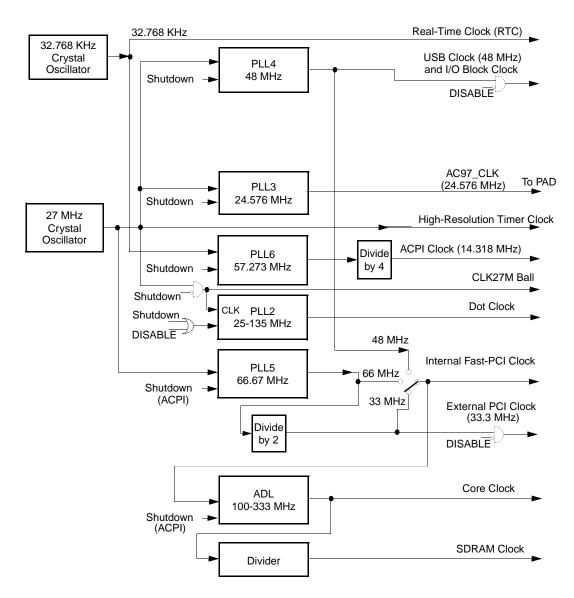

- Clocks:

- Input (external crystals):

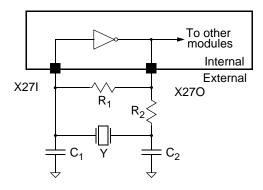

- 32.768 KHz (internal clock oscillator)

- 27 MHz (internal clock oscillator)

- Output:

- AC97 clock (24.576 MHz)

- Memory controller clock (66 MHz to 100 MHz)

- PCI clock (33 MHz)

- JTAG Testability:

- Bypass, Extest, Sample/Preload, IDcode, Clamp, HIZ

- Voltages:

- Internal logic: 233/266 MHz @ 1.8V and 300 MHz @ 2.1V

- Battery: 3V

- I/O: 3.3V

- Standby: 3.3V

# **Table of Contents**

| 1.0 | Arch | itectur | e Overview                                   |

|-----|------|---------|----------------------------------------------|

|     | 1.1  | GX1 M   | ODULE                                        |

|     |      | 1.1.1   | Memory Controller                            |

|     |      | 1.1.2   | Fast-PCI Bus                                 |

|     |      | 1.1.3   | Display                                      |

|     | 1.2  | VIDEO   | PROCESSOR MODULE                             |

|     |      | 1.2.1   | GX1 Module Interface                         |

|     |      | 1.2.2   | Video Input Port                             |

|     |      | 1.2.3   | Core Logic Module Interface                  |

|     |      | 1.2.4   | CRT DAC                                      |

|     | 1.3  | CORE    | LOGIC MODULE                                 |

|     |      | 1.3.1   | Other Interfaces of the Core Logic Module16  |

|     | 1.4  | SUPER   | I/O MODULE                                   |

|     | 1.5  |         | I, TIMERS, AND RESET LOGIC                   |

|     | 1.0  | 1.5.1   | Reset Logic                                  |

|     |      | 1.0.1   | 1.5.1.1 Power-On Reset                       |

|     |      |         | 1.5.1.2 System Reset                         |

|     | ٥.   |         |                                              |

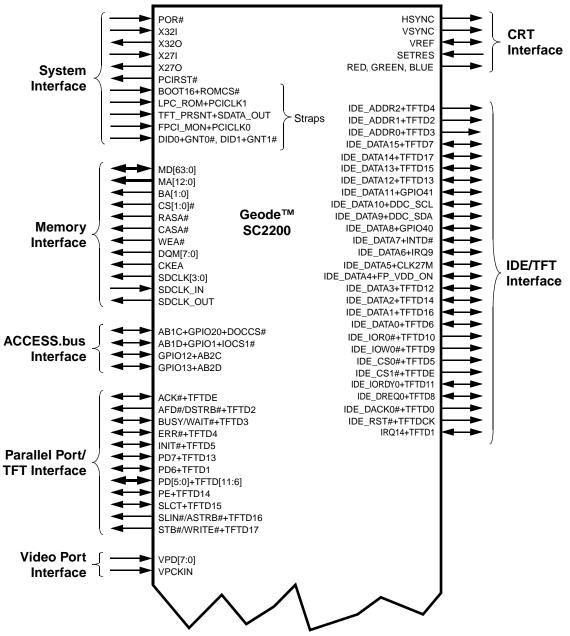

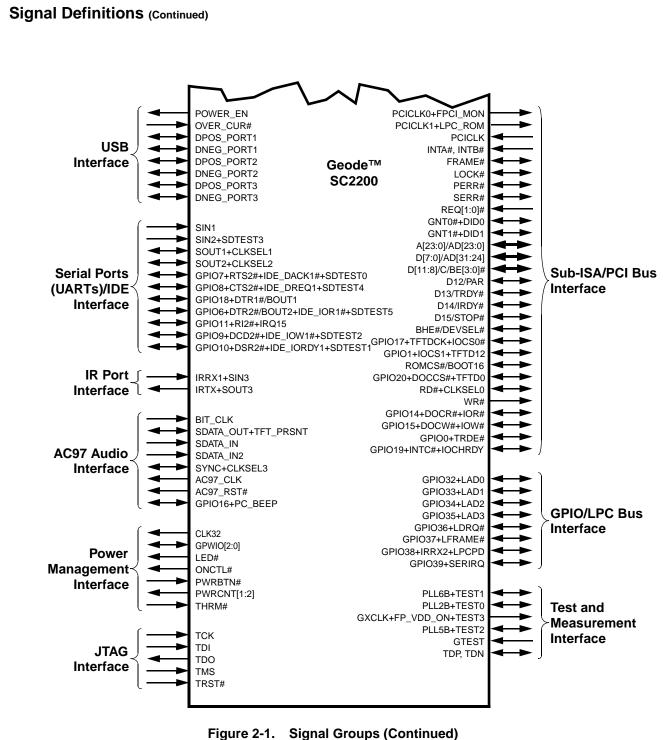

| 2.0 | •    |         | nitions                                      |

|     | 2.1  |         | SSIGNMENTS                                   |

|     | 2.2  | _       | OPTIONS51                                    |

|     | 2.3  | MULTIF  | PLEXING CONFIGURATION52                      |

|     | 2.4  | SIGNAI  | DESCRIPTIONS56                               |

|     |      | 2.4.1   | System Interface56                           |

|     |      | 2.4.2   | Memory Interface Signals57                   |

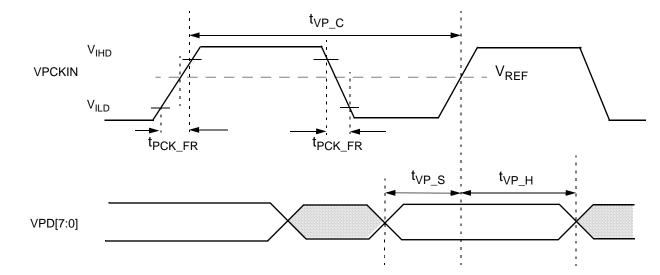

|     |      | 2.4.3   | Video Port Interface Signals                 |

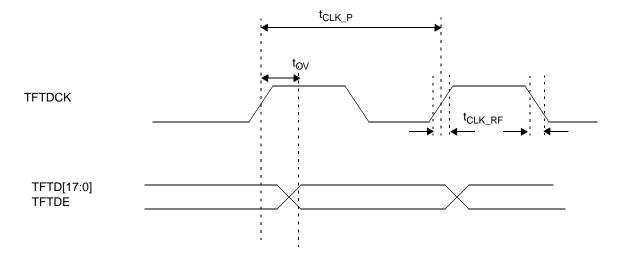

|     |      | 2.4.4   | CRT/TFT Interface Signals                    |

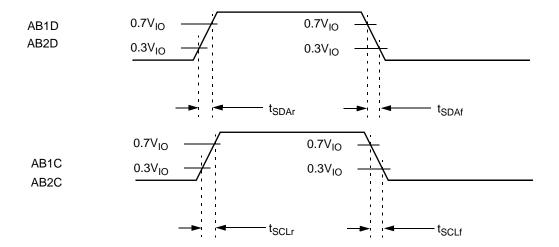

|     |      | 2.4.5   | ACCESS.bus Interface Signals61               |

|     |      | 2.4.6   | PCI Bus Interface Signals61                  |

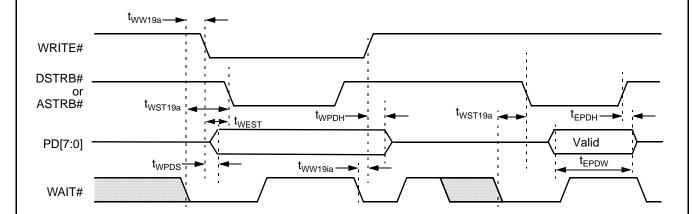

|     |      | 2.4.7   | Sub-ISA Interface Signals                    |

|     |      | 2.4.8   | Low Pin Count (LPC) Bus Interface Signals    |

|     |      | 2.4.9   | IDE Interface Signals                        |

|     |      | 2.4.10  | Universal Serial Bus (USB) Interface Signals |

|     |      | 2.4.11  | Serial Ports (UARTs) Interface Signals70     |

|     |      | 2.4.12  | Parallel Port Interface Signals              |

|     |      | 2.4.13  | Fast Infrared (IR) Port Interface Signals    |

|     |      | 2.4.14  | AC97 Audio Interface Signals                 |

|     |      | 2.4.15  | Power Management Interface Signals           |

|     |      | 2.4.16  | GPIO Interface Signals                       |

|     |      | 2.4.17  | Debug Monitoring Interface Signals           |

|     |      | 2.4.18  | JTAG Interface Signals                       |

|     |      | 2.4.19  | Test and Measurement Interface Signals       |

|     |      | 2.4.20  | Power, Ground and No Connections             |

|     |      |         |                                              |

# Table of Contents (Continued)

| 3.0 |             |          | •                  | n Block 80                                             |

|-----|-------------|----------|--------------------|--------------------------------------------------------|

|     | 3.1         |          |                    | BLOCK ADDRESSES80                                      |

|     | 3.2         | MULTIF   | PLEXING, IN        | ITERRUPT SELECTION, AND BASE ADDRESS REGISTERS 81      |

|     | 3.3         | WATCH    | HDOG               | 88                                                     |

|     |             | 3.3.1    | Functional         | Description                                            |

|     |             |          | 3.3.1.1            | WATCHDOG Timer                                         |

|     |             | 3.3.2    | WATCHDO            | DG Registers89                                         |

|     |             |          | 3.3.2.1            | Usage Hints                                            |

|     | 3.4         | HIGH-F   | RESOLUTIO          | N TIMER90                                              |

|     |             | 3.4.1    | Functional         | Description                                            |

|     |             | 3.4.2    | High-Resc          | lution Timer Registers90                               |

|     |             |          | 3.4.2.1            | Usage Hints                                            |

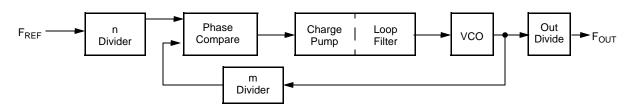

|     | 3.5         | CLOCK    | GENERAT            | ORS AND PLLS                                           |

|     |             | 3.5.1    | 27 MHz Cı          | rystal Oscillator                                      |

|     |             | 3.5.2    | GX1 Modu           | ıle Core Clock                                         |

|     |             | 3.5.3    | Internal Fa        | st-PCI Clock94                                         |

|     |             | 3.5.4    | SuperI/O (         | Clocks95                                               |

|     |             | 3.5.5    | Core Logic         | Module Clocks95                                        |

|     |             | 3.5.6    | Video Prod         | cessor Clocks95                                        |

|     |             | 3.5.7    | Clock Reg          | isters95                                               |

| 4.0 | Supe        | erI/O Mo | odule              |                                                        |

|     | <b>4</b> .1 |          |                    | 99                                                     |

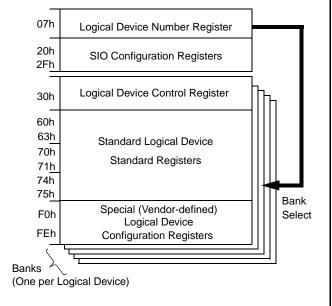

|     | 4.2         |          |                    | ECTURE                                                 |

|     | 4.3         |          |                    | STRUCTURE/ACCESS                                       |

|     | 4.5         | 4.3.1    |                    | a Register Pair                                        |

|     |             | 4.3.1    |                    | egical Device Registers                                |

|     |             | 4.3.3    |                    | Infiguration Setup                                     |

|     |             | 4.3.4    |                    | ecoding                                                |

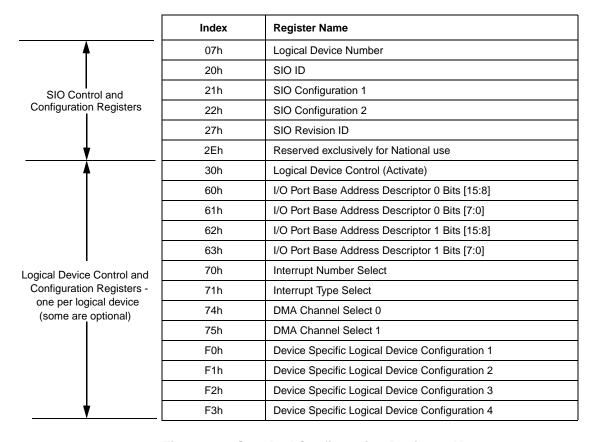

|     | 4.4         |          |                    | IGURATION REGISTERS                                    |

|     | 4.4         |          |                    |                                                        |

|     |             | 4.4.1    |                    | ol and Configuration Registers                         |

|     |             | 4.4.2    | 4.4.2.1            | LDN 00h - Real-Time Clock                              |

|     |             |          | 4.4.2.1<br>4.4.2.2 | LDN 01h - Real-Time Clock                              |

|     |             |          | 4.4.2.3            | LDN 02h - Infrared Communication Port or Serial Port 3 |

|     |             |          | 4.4.2.4            | LDN 03h and 08h - Serial Ports 1 and 2111              |

|     |             |          | 4.4.2.5            | LDN 05h and 06h - ACCESS.bus Ports 1 and 2             |

|     | 1 E         | DEAL T   | 4.4.2.6            | LDN 07h - Parallel Port                                |

|     | 4.5         | 4.5.1    |                    | K (RTC)                                                |

|     |             | 4.5.1    |                    | Generation                                             |

|     |             | 4.5.2    | 4.5.2.1            | Internal Oscillator                                    |

|     |             |          | 4.5.2.1            | External Oscillator                                    |

|     |             |          | 4.5.2.3            | Timing Generation                                      |

|     |             |          | 4.5.2.4            | Timekeeping                                            |

|     |             |          | 4.5.2.5            | Alarms                                                 |

|     |             |          | 4.5.2.6            | Power Supply                                           |

|     |             |          | 4.5.2.7<br>4.5.2.8 | System Power States                                    |

|     |             |          | 4.5.2.9            | Interrupt Handling                                     |

|     |             |          | 4.5.2.10           | Battery-Backed RAMs and Registers                      |

|     |             |          |                    |                                                        |

| Tabl | e of C | ontents        | G (Continued)                                                                                         |

|------|--------|----------------|-------------------------------------------------------------------------------------------------------|

|      |        | 4.5.3          | RTC Registers                                                                                         |

|      |        |                | 4.5.3.1 Usage Hints                                                                                   |

|      |        | 4.5.4          | RTC General-Purpose RAM Map                                                                           |

|      | 4.6    | SYSTE          | M WAKEUP CONTROL (SWC)125                                                                             |

|      |        | 4.6.1          | Event Detection                                                                                       |

|      |        |                | 4.6.1.1 Audio Codec Event                                                                             |

|      |        |                | 4.6.1.2 CEIR Address                                                                                  |

|      |        | 4.6.2          | SWC Registers                                                                                         |

|      | 4.7    |                | SS.BUS INTERFACE                                                                                      |

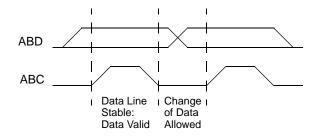

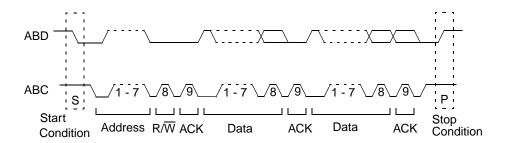

|      |        | 4.7.1          | Data Transactions                                                                                     |

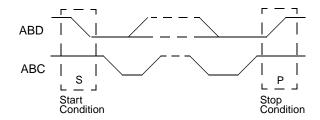

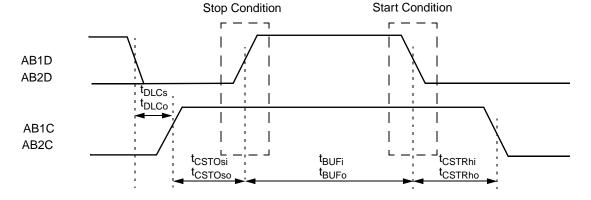

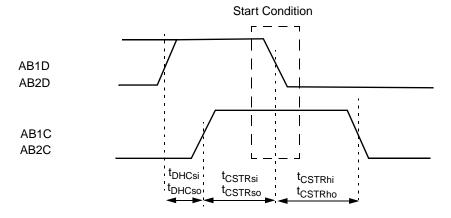

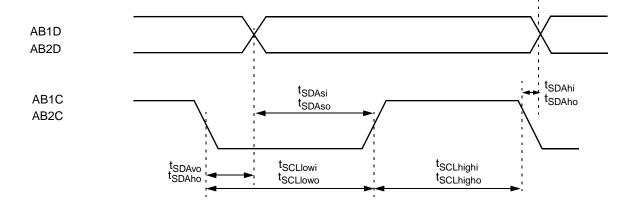

|      |        | 4.7.2          | Start and Stop Conditions                                                                             |

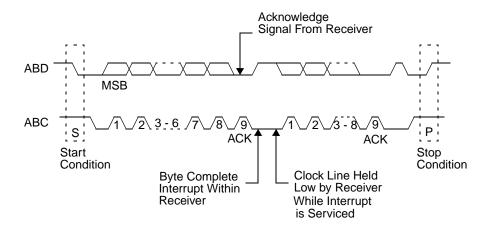

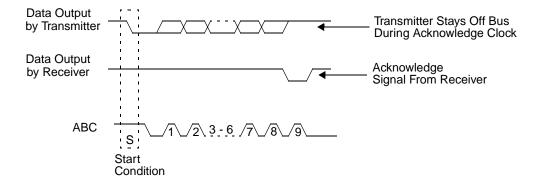

|      |        | 4.7.3          | Acknowledge (ACK) Cycle                                                                               |

|      |        | 4.7.4<br>4.7.5 | Acknowledge After Every Byte Rule                                                                     |

|      |        | 4.7.5<br>4.7.6 | Arbitration on the Bus                                                                                |

|      |        | 4.7.7          | Master Mode                                                                                           |

|      |        | 4.7.7          | 4.7.7.1 Master Stop                                                                                   |

|      |        | 4.7.8          | Slave Mode                                                                                            |

|      |        | 4.7.9          | Configuration                                                                                         |

|      |        | 4.7.10         | ACB Registers                                                                                         |

|      | 4.8    | LEGAC          | CY FUNCTIONAL BLOCKS138                                                                               |

|      |        | 4.8.1          | Parallel Port                                                                                         |

|      |        |                | 4.8.1.1 Parallel Port Register and Bit Maps                                                           |

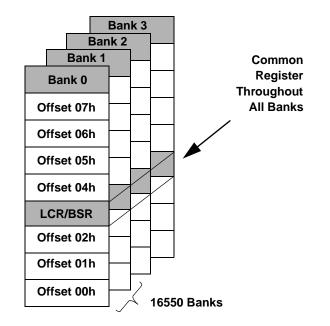

|      |        | 4.8.2          | UART Functionality (SP1 and SP2)                                                                      |

|      |        |                | 4.8.2.1 UART Mode Register Bank Overview                                                              |

|      |        | 4.8.3          | 4.8.2.2 SP1 and SP2 Register and Bit Maps for UART Functionality                                      |

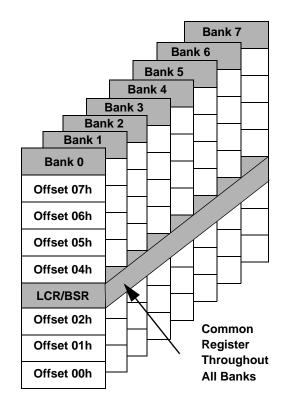

|      |        | 4.0.0          | 4.8.3.1 IR/SP3 Mode Register Bank Overview                                                            |

|      |        |                | 4.8.3.2 IRCP/SP3 Register and Bit Maps                                                                |

| 5.0  | Core   | Logic          | Module                                                                                                |

|      | 5.1    | FEATU          | RE LIST                                                                                               |

|      | 5.2    |                | LE ARCHITECTURE                                                                                       |

|      |        | 5.2.1          | Fast-PCI Interface to External PCI Bus                                                                |

|      |        |                | 5.2.1.1 Processor Mastered Cycles                                                                     |

|      |        |                | 5.2.1.2 External PCI Mastered Cycles                                                                  |

|      |        |                | 5.2.1.3 Core Logic Internal or Sub-ISA Mastered Cycles                                                |

|      |        |                | 5.2.1.4       External PCI Bus       152         5.2.1.5       Bus Master Request Priority       152  |

|      |        | 5.2.2          | PSERIAL Interface                                                                                     |

|      |        |                | 5.2.2.1 Video Retrace Interrupt                                                                       |

|      |        | 5.2.3          | IDE Controller                                                                                        |

|      |        |                | 5.2.3.1 IDE Configuration Registers                                                                   |

|      |        |                | 5.2.3.2       PIO Mode                                                                                |

|      |        |                | 5.2.3.4 UltraDMA/33 Mode                                                                              |

|      |        | 5.2.4          | Universal Serial Bus                                                                                  |

|      |        | 5.2.5          | Sub-ISA Bus Interface                                                                                 |

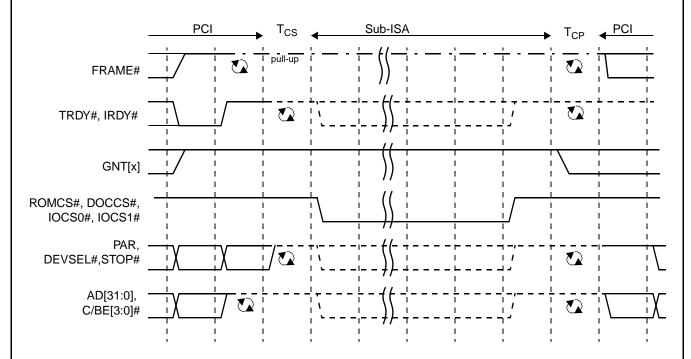

|      |        |                | 5.2.5.1 Sub-ISA Bus Cycles                                                                            |

|      |        |                | 5.2.5.2 Sub-ISA Support of Delayed PCI Transactions                                                   |

|      |        |                | 5.2.5.3       Sub-ISA Bus Data Steering       158         5.2.5.4       I/O Recovery Delays       158 |

| I    |        |                |                                                                                                       |

|      |        |                | 5.2.5.5 ISA DMA                                                                                       |

|      |        |                |                                                                                                       |

## Table of Contents (Continued)

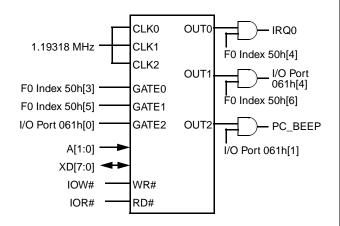

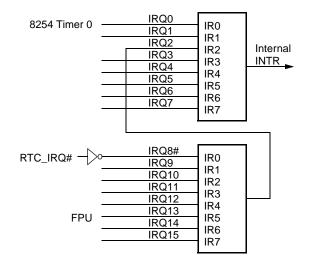

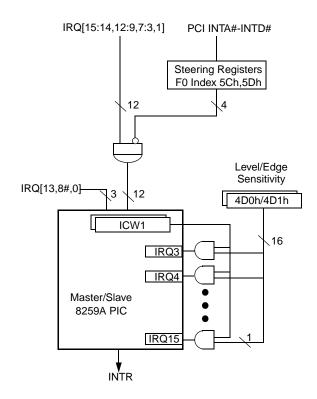

|     | 5.2.6  | AT Compa    | atibility Logic                             | 161 |

|-----|--------|-------------|---------------------------------------------|-----|

|     | 0.2.0  | 5.2.6.1     | DMA Controller                              |     |

|     |        | 5.2.6.2     | Programmable Interval Timer                 |     |

|     |        | 5.2.6.3     | Programmable Interrupt Controller           |     |

|     | 5.2.7  | I/O Ports ( | 092h and 061h System Control                |     |

|     | •      | 5.2.7.1     | I/O Port 092h System Control                |     |

|     |        | 5.2.7.2     | I/O Port 061h System Control                |     |

|     |        | 5.2.7.3     | SMI Generation for NMI                      |     |

|     | 5.2.8  | Kevboard    | Support                                     |     |

|     |        | 5.2.8.1     | Fast Keyboard Gate Address 20 and CPU Reset |     |

|     | 5.2.9  |             | nagement Logic                              |     |

|     | 0.2.0  | 5.2.9.1     | CPU States                                  |     |

|     |        | 5.2.9.1     | Sleep States                                |     |

|     |        | 5.2.9.3     | Power Planes Control                        |     |

|     |        | 5.2.9.4     | Power Management Events                     |     |

|     |        | 5.2.9.5     | Usage Hints                                 |     |

|     | 5.2.10 |             | nagement Programming                        |     |

|     | 0.20   | 5.2.10.1    | APM Support                                 |     |

|     |        | 5.2.10.2    | CPU Power Management                        |     |

|     |        | 5.2.10.3    | Peripheral Power Management                 |     |

|     |        | 5.2.10.4    | Power Management Programming Summary        |     |

|     | 5.2.11 | GPIO Inte   | rface                                       |     |

|     | 5.2.12 |             | Audio                                       |     |

|     | 0.22   | 5.2.12.1    | Data Transport Hardware                     |     |

|     |        | 5.2.12.2    | AC97 Codec Interface                        |     |

|     |        | 5.2.12.3    | VSA Technology Support Hardware             |     |

|     |        | 5.2.12.4    | IRQ Configuration Registers                 |     |

|     |        | 5.2.12.5    | LPC Interface                               |     |

|     |        | 5.2.12.6    | LPC Interface Signal Definitions            |     |

|     |        | 5.2.12.7    | Cycle Types                                 |     |

|     |        | 5.2.12.8    | LPC Interface Support                       | 183 |

| 5.3 | REGIST | ER DESCE    | RIPTIONS                                    | 184 |

|     | 5.3.1  | PCI Confid  | guration Space and Access Methods           | 184 |

|     | 5.3.2  |             | Summary                                     |     |

| 5.4 |        | •           | ER SPACE                                    |     |

| 5.4 |        |             |                                             |     |

|     | 5.4.1  |             | PIO, and LPC Registers - Function 0         |     |

|     |        | 5.4.1.1     | GPIO Support Registers                      |     |

|     |        |             | LPC Support Registers                       |     |

|     | 5.4.2  |             | s and ACPI Registers - Function 1           |     |

|     |        | 5.4.2.1     | SMI Status Support Registers                |     |

|     |        | 5.4.2.2     | ACPI Support Registers                      |     |

|     | 5.4.3  | IDE Contro  | oller Registers - Function 2                | 263 |

|     |        | 5.4.3.1     | IDE Controller Support Registers            | 267 |

|     | 5.4.4  | Audio Reg   | jisters - Function 3                        | 269 |

|     |        | 5.4.4.1     | Audio Support Registers                     | 270 |

|     | 5.4.5  | X-Bus Exp   | pansion Interface - Function 5              | 284 |

|     |        | 5.4.5.1     | X-Bus Expansion Support Registers           |     |

|     | 5.4.6  |             | roller Registers - PCIUSB                   |     |

|     | 5.4.7  |             | cy Register Space                           |     |

|     | J.4.1  | IOA Legal   | y negisier space                            | 302 |

#### Table of Contents (Continued) 6.0 MODULE ARCHITECTURE ......317 6.1 6.2 6.2.1 6.2.1.1 6.2.1.2 6.2.1.3 6.2.2 Video Block 6.2.2.1 6.2.2.2 6.2.2.3 6.2.2.4 6.2.2.5 6.2.3 6.2.3.1 6.2.3.2 6.2.3.3 6.2.3.4 6.2.4 6.2.5 6.2.6 6.2.7 6.3 6.3.1 6.3.2 6.3.2.1 6.3.2.2 7.0 7.1.1 7.1.2 Optional Instruction Support ......357 7.1.3 8.0 8.1 GENERAL SPECIFICATIONS .......358 8.1.1 8.1.2 8.1.3 8.1.4 8.1.4.1 8.1.4.2 Definition and Measurement Techniques of SC2200 Current Parameters . . . . . 360 Definition of System Conditions for Measuring On Parameters .............361 8.1.4.3 8144 8.1.5 8.1.6

#### Table of Contents (Continued) 8.2 DC CHARACTERISTICS .......365 8.2.1 8.2.2 8.2.3 8.2.4 8.2.5 8.2.6 8.2.7 8.2.8 8.2.9 8.2.10 8.2.11 8.2.12 8.2.13 8.2.14 8.2.15 8.2.15.1 8.3 AC CHARACTERISTICS ......370 8.3.1 8.3.2 8.3.3 8.3.4 8.3.5 8.3.5.1 8.3.6 8.3.7 8.3.8 8.3.9 8.3.10 8.3.11 8.3.12 8.3.13 8.3.14 Power Management Interface ......424 8.3.15 8.3.16 9.0 Appendix A Support Documentation ...... 431 ORDER INFORMATION ......431 A.1 DATASHEET REVISION HISTORY ......431 A.2

### 1.0 Architecture Overview

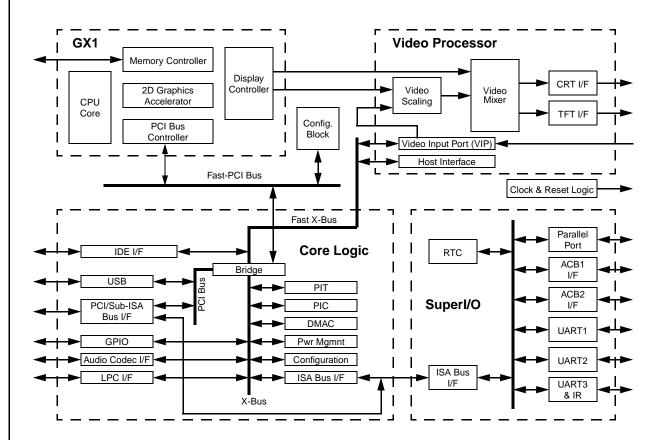

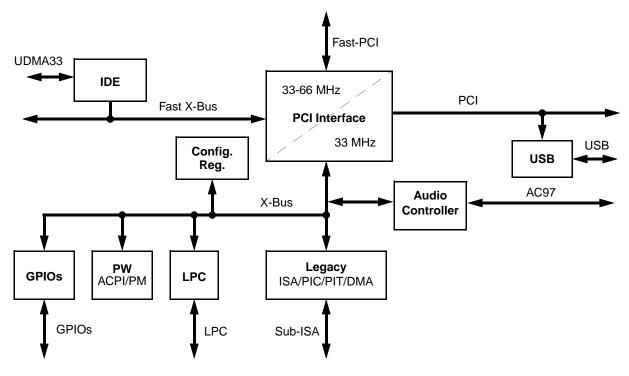

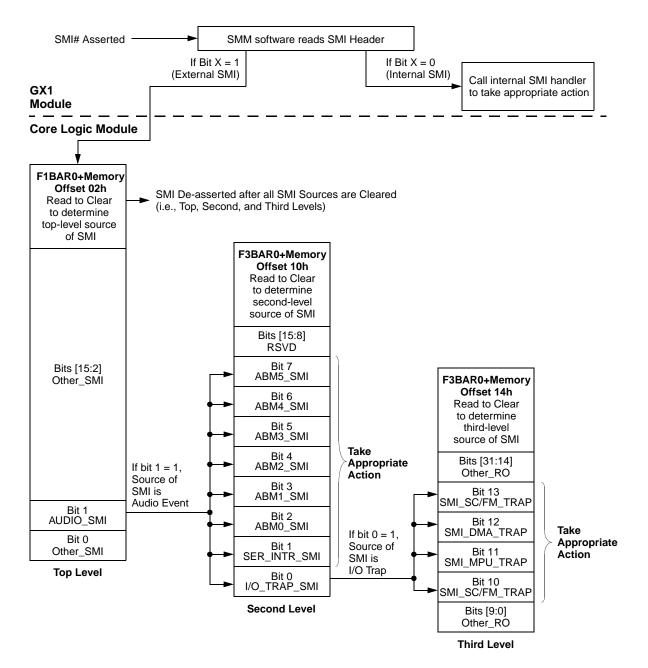

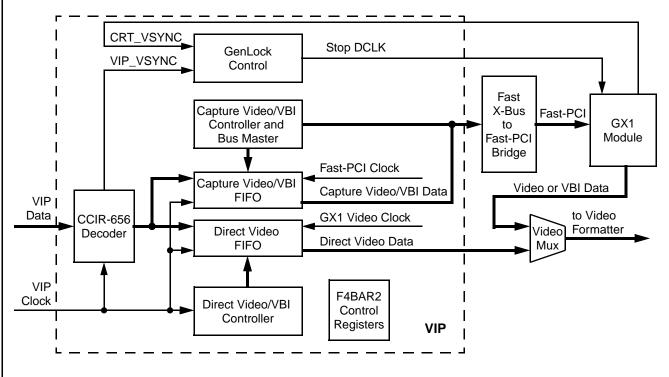

As illustrated in Figure 1-1, the SC2200 contains the following modules in one integrated device:

- GX1 Module:

- Combines advanced CPU performance with MMX support, fully accelerated 2D graphics, a 64-bit synchronous DRAM (SDRAM) interface and a PCI bus controller. Integrates GX1 silicon revision 8.1.1.

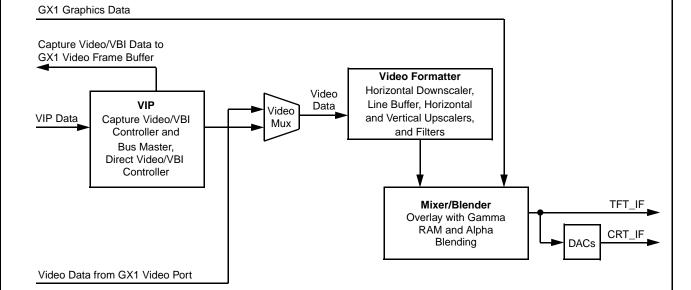

- Video Processor Module:

- A low-power CRT and TFT support module with a video input port, and a hardware video accelerator for scaling, filtering and color space conversion.

- · Core Logic Module:

- Includes PC/AT functionality, an IDE interface, a Universal Serial Bus (USB) interface, ACPI 1.0 compliant power management, and an audio codec interface.

- SuperI/O Module:

- Includes two Serial Ports, an Infrared (IR) Port, a Parallel Port, two ACCESS.bus interfaces, and a Real-Time Clock (RTC).

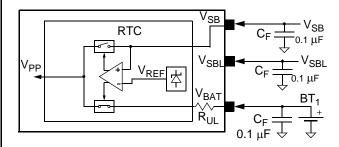

Figure 1-1. SC2200 Block Diagram

#### 1.1 GX1 MODULE

The GX1 processor (silicon revision 8.1.1) is the central module of the SC2200. For detailed information regarding the GX1 module, refer to the Geode GX1 Processor Series datasheet and the Geode GX1 Processor Series Silicon Revision 8.1.1 errata.

The SC2200's device ID is contained in the GX1 module. Software can detect the revision by reading the DIR0 and DIR1 Configuration registers (see Configuration registers in the Geode GX1 Processor Series datasheet). The SC2200 device errata contains the specific values.

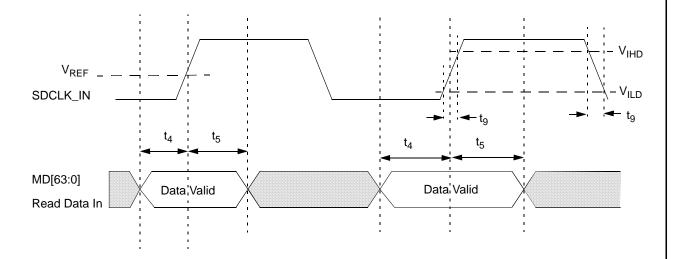

#### 1.1.1 Memory Controller

The GX1 module is connected to external SDRAM devices. For more information see Section 2.4.2 "Memory Interface Signals" on page 57, and the "Memory Controller" chapter in the *GX1 Processor Series datasheet*.

There are some differences in the SC2200's memory controller and the stand-alone GX1 processor's memory controller:

- There is drive strength/slew control in the SC2200 that is not in the GX1. The bits that control this function are in the MC\_MEM\_CNTRL1 and MC\_MEM\_CNTRL2 registers. In the GX1 processor, these bits are marked as reserved.

- 2) The SC2200 supports two banks of memory. The GX1 supports four banks of memory. In addition, the SC2200 supports a maximum of eight devices and the GX1 supports up to 32 devices. With this difference, the MC\_BANK\_CFG register is different.

Table 1-1 summarizes the 32-bit registers contained in the SC2200's memory controller. Table 1-2 gives detailed register/bit formats.

Table 1-1. SC2200 Memory Controller Register Summary

| GX_BASE+<br>Memory Offset | Width<br>(Bits) | Туре | Name/Function                                                  | Reset Value |

|---------------------------|-----------------|------|----------------------------------------------------------------|-------------|

| 8400h-8403h               | 32              | R/W  | MC_MEM_CNTRL1. Memory Controller Control Register 1            | 248C0040h   |

| 8404h-8407h               | 32              | R/W  | MC_MEM_CNTRL2. Memory Controller Control Register 2            | 00000801h   |

| 8408h-840Bh               | 32              | R/W  | MC_BANK_CFG. Memory Controller Bank Configuration              | 41104110h   |

| 840Ch-840Fh               | 32              | R/W  | MC_SYNC_TIM1. Memory Controller Synchronous Timing Register 1  | 2A733225h   |

| 8414h-8417h               | 32              | R/W  | MC_GBASE_ADD. Memory Controller Graphics Base Address Register | 00000000h   |

| 8418h-841Bh               | 32              | R/W  | MC_DR_ADD. Memory Controller Dirty RAM Address Register        | 00000000h   |

| 841Ch-841Fh               | 32              | R/W  | MC_DR_ACC. Memory Controller Dirty RAM Access Register         | 0000000xh   |

Table 1-2. SC2200 Memory Controller Registers

| Bit     | Description                                                                                                                                                                                                            |                                                                                                                                           |                                                  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|

| GX BASE | 8400h-8403h                                                                                                                                                                                                            | MC_MEM_CNTRL1 (R/W)                                                                                                                       | Reset Value: 248C0040h                           |  |  |  |  |  |

| 31:30   | MDCTL (MD[63:0] Drive Strength).                                                                                                                                                                                       |                                                                                                                                           |                                                  |  |  |  |  |  |

| 29      | RSVD (Reserved) Write as 0.                                                                                                                                                                                            | This changes, so is weakest.                                                                                                              |                                                  |  |  |  |  |  |

| 28:27   | '                                                                                                                                                                                                                      | Drive Strength). 11 is strongest, 00 is weake                                                                                             | est.                                             |  |  |  |  |  |

| 26      | RSVD (Reserved). Write as 0.                                                                                                                                                                                           |                                                                                                                                           |                                                  |  |  |  |  |  |

| 25:24   | MEMCTL (RASA#, CASA#, WEA#, CS[1:0]#, CKEA, DQM[7:0] Drive Strength). 11 is strongest, 00 is weakest.                                                                                                                  |                                                                                                                                           |                                                  |  |  |  |  |  |

| 23:22   | RSVD (Reserved). Write as 0.                                                                                                                                                                                           |                                                                                                                                           |                                                  |  |  |  |  |  |

| 21      | RSVD (Reserved). Must be written a                                                                                                                                                                                     | as 0. Wait state on the X-Bus x_data during i                                                                                             | read cycles - for debug only.                    |  |  |  |  |  |

| 20:18   | SDCLKRATE (SDRAM Clock Ratio                                                                                                                                                                                           | ). Selects SDRAM clock ratio.                                                                                                             |                                                  |  |  |  |  |  |

|         | 000: Reserved<br>001: ÷ 2<br>010: ÷ 2.5<br>011: ÷ 3 (Default)                                                                                                                                                          | 100: ÷ 3.5<br>101: ÷ 4<br>110: ÷ 4.5<br>111: ÷ 5                                                                                          |                                                  |  |  |  |  |  |

|         |                                                                                                                                                                                                                        | DCLKSTRT bit (bit 17 of this register) transit                                                                                            |                                                  |  |  |  |  |  |

| 17      | SDCLKSTRT (Start SDCLK). Start (ister). 0: Clear. 1: Enable.                                                                                                                                                           | operating SDCLK using the new ratio and sh                                                                                                | ift value (selected in bits [20:18] of this reg- |  |  |  |  |  |

|         | This bit must transition from zero (wr                                                                                                                                                                                 | itten to zero) to one (written to one) in order t                                                                                         | to start SDCLK or to change the shift value.     |  |  |  |  |  |

| 16:8    | RFSHRATE (Refresh Interval). This field determines the number of processor core clocks multiplied by 64 between refresh cycles to the DRAM. By default, the refresh interval is 00h. Refresh is turned off by default. |                                                                                                                                           |                                                  |  |  |  |  |  |

| 7:6     | RFSHSTAG (Refresh Staggering). four banks during refresh cycles:                                                                                                                                                       | This field determines number of clocks between                                                                                            | een the RFSH commands to each of the             |  |  |  |  |  |

|         | 00: 0 SDRAM clocks<br>01: 1 SDRAM clocks (Default)<br>10: 2 SDRAM clocks<br>11: 4 SDRAM clocks                                                                                                                         |                                                                                                                                           |                                                  |  |  |  |  |  |

|         | Staggering is used to help reduce po this field must be written as 00.                                                                                                                                                 | wer spikes during refresh by refreshing one b                                                                                             | pank at a time. If only one bank is installed,   |  |  |  |  |  |

| 5       | 2CLKADDR (Two Clock Address S                                                                                                                                                                                          | <b>Setup).</b> Assert memory address for one extra                                                                                        | clock before CS# is asserted.                    |  |  |  |  |  |

|         | 0: Disable.<br>1: Enable.                                                                                                                                                                                              |                                                                                                                                           |                                                  |  |  |  |  |  |

|         | This can be used to compensate for                                                                                                                                                                                     | address setup at high frequencies and/or hig                                                                                              | gh loads.                                        |  |  |  |  |  |

| 4       | RFSHTST (Test Refresh). This bit, v                                                                                                                                                                                    | when set high, generates a refresh request.                                                                                               | This bit is only used for testing purposes.      |  |  |  |  |  |

| 3       | are arbitrated at the same priority lev                                                                                                                                                                                | When enabled, processor, graphics pipeline a<br>vel. When disabled, processor requests are a<br>ys have the highest arbitration priority. |                                                  |  |  |  |  |  |

|         | 0: Enable.<br>1: Disable.                                                                                                                                                                                              |                                                                                                                                           |                                                  |  |  |  |  |  |

| 2       | <b>SMM_MAP (SMM Region Mapping</b><br>BFFFF in SDRAM.                                                                                                                                                                  | ). Maps the SMM memory region at GX_BAS                                                                                                   | SE+400000 to physical address A0000 to           |  |  |  |  |  |

|         | 0: Disable.<br>1: Enable.                                                                                                                                                                                              |                                                                                                                                           |                                                  |  |  |  |  |  |

| 1       | RSVD (Reserved). Write as 0.                                                                                                                                                                                           |                                                                                                                                           |                                                  |  |  |  |  |  |

| 0       | SDRAMPRG (Program SDRAM). W<br>LTMODE in MC_SYNC_TIM1.                                                                                                                                                                 | /hen this bit is set, the memory controller will                                                                                          | program the SDRAM MRS register using             |  |  |  |  |  |

|         | This bit must transition from zero (wr                                                                                                                                                                                 | ritten to zero) to one (written to one) in order                                                                                          | to program the SDRAM devices.                    |  |  |  |  |  |

Table 1-2. SC2200 Memory Controller Registers (Continued)

| Bit     | Description                                                                                                                 |                                 |                                                                                 |                                                                     |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

| GX_BASE | E+8404h-8407h                                                                                                               | MC_MEM_CNT                      | RL2 (R/W)                                                                       | Reset Value: 00000801h                                              |  |  |  |

| 31:14   | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

| 13:12   | SDCLKCTL (SDCLK High I<br>11 is strongest, 00 is weaker                                                                     |                                 | s the high drive and slew ra                                                    | ate of SDCLK[3:0] and SDCLK_OUT.                                    |  |  |  |

| 11      | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

| 10      | SDCLKOMSK# (Enable SD                                                                                                       | CLK_OUT). Turns on the ou       | tput.                                                                           |                                                                     |  |  |  |

|         | 0: Enable.<br>1: Disable.                                                                                                   |                                 |                                                                                 |                                                                     |  |  |  |

| 9       | SDCLK3MSK# (Enable SD                                                                                                       | CLK3). Turns on the output.     |                                                                                 |                                                                     |  |  |  |

|         | 0: Enable.<br>1: Disable.                                                                                                   |                                 |                                                                                 |                                                                     |  |  |  |

| 8       | SDCLK2MSK# (Enable SD                                                                                                       | CLK2). Turns on the output.     |                                                                                 |                                                                     |  |  |  |

|         | 0: Enable.<br>1: Disable.                                                                                                   |                                 |                                                                                 |                                                                     |  |  |  |

| 7       | SDCLK1MSK# (Enable SD                                                                                                       | CLK1). Turns on the output.     |                                                                                 |                                                                     |  |  |  |

|         | 0: Enable.<br>1: Disable.                                                                                                   |                                 |                                                                                 |                                                                     |  |  |  |

| 6       | SDCLK0MSK# (Enable SD                                                                                                       | CLK0). Turns on the output.     |                                                                                 |                                                                     |  |  |  |

|         | 0: Enable.<br>1: Disable.                                                                                                   |                                 |                                                                                 |                                                                     |  |  |  |

| 5:3     | SHFTSDCLK (Shift SDCLK shift function will not take eff                                                                     |                                 |                                                                                 | setup and hold time requirements. The RL1) transitions from 0 to 1: |  |  |  |

|         | 000: No shift<br>001: Shift 0.5 core clock<br>010: Shift 1 core clock<br>011: Shift 1.5 core clock                          | 101: S<br>110: S                | Shift 2 core clocks<br>Shift 2.5 core clocks<br>Shift 3 core clocks<br>Reserved |                                                                     |  |  |  |

| 2       | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

| 1       | RD (Read Data Phase). Sel                                                                                                   | ects if read data is latched or | ne or two core clock after th                                                   | ne rising edge of SDCLK.                                            |  |  |  |

|         | 0: 1 Core clock.<br>1: 2 Core clocks.                                                                                       |                                 |                                                                                 |                                                                     |  |  |  |

| 0       | FSTRDMSK (Fast Read Ma                                                                                                      | sk). Do not allow core reads    | to bypass the request FIFO                                                      | D.                                                                  |  |  |  |

|         | 0: Disable.<br>1: Enable.                                                                                                   |                                 |                                                                                 |                                                                     |  |  |  |

| GX_BASE | E+8408h-840Bh                                                                                                               | MC_BANK_CI                      | G (R/W)                                                                         | Reset Value: 41104110h                                              |  |  |  |

| 31:16   | RSVD (Reserved). Write as                                                                                                   | 0070h                           |                                                                                 |                                                                     |  |  |  |

| 15      | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

| 14      | SODIMM_MOD_BNK (SOD for SODIMM:                                                                                             | MM Module Banks - Banks         | 0 and 1). Selects number                                                        | of module banks installed per SODIMM                                |  |  |  |

|         | 0: 1 Module bank (Bank 0 or 1: 2 Module banks (Bank 0 a                                                                     |                                 |                                                                                 |                                                                     |  |  |  |

| 13      | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

| 12      | SODIMM_COMP_BNK (SODIMM Component Banks - Banks 0 and 1). Selects the number of component banks per module bank for SODIMM: |                                 |                                                                                 |                                                                     |  |  |  |

|         | 0: 2 Component banks. 1: 4 Component banks.                                                                                 |                                 |                                                                                 |                                                                     |  |  |  |

|         | Banks 0 and 1 must have the                                                                                                 | same number of componer         | t banks.                                                                        |                                                                     |  |  |  |

| 11      | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

| 10:8    | SODIMM_SZ (SODIMM Siz                                                                                                       | e - Banks 0 and 1). Selects     | the size of SODIMM:                                                             |                                                                     |  |  |  |

|         | 000: 4 MB 010: 16<br>001: 8 MB 011: 32                                                                                      |                                 | 110: 256 MB<br>111: 512 MB                                                      |                                                                     |  |  |  |

|         | This size is the total of both                                                                                              | oanks 0 and 1. Also, banks 0    | and 1 must be the same si                                                       | ize.                                                                |  |  |  |

| 7       | RSVD (Reserved). Write as                                                                                                   | 0.                              |                                                                                 |                                                                     |  |  |  |

Table 1-2. SC2200 Memory Controller Registers (Continued)

| 6:4     | SODIMM_PG_SZ (SODIMM Page Size - Banks 0 and 1). Selects the page size of SODIMM:                                                                                                                                                                                                                                                                                      |                                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | 000: 1 KB<br>001: 2 KB                                                                                                                                                                                                                                                                                                                                                 | 010: 4 KB<br>011: 8 KB                                   | 1xx: 16 KB<br>111: SODIMM no                                | ot installed                                                 |                                                                                                                        |  |  |  |

|         | Both banks 0 and                                                                                                                                                                                                                                                                                                                                                       | 1 must have the sa                                       | ame page size.                                              |                                                              |                                                                                                                        |  |  |  |

| 3:0     | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | <b>I).</b> Write as 0.                                   |                                                             |                                                              |                                                                                                                        |  |  |  |

| GX_BASE | +840Ch-840Fh                                                                                                                                                                                                                                                                                                                                                           |                                                          | MC_SYNC_TIM                                                 | 11 (R/W)                                                     | Reset Value: 2A733225h                                                                                                 |  |  |  |

| 31      | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | I). Write as 0.                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

| 30:28   | and the availabilit                                                                                                                                                                                                                                                                                                                                                    | y of the first piece o                                   | f output data. This pa                                      | rameter significantly affect                                 | n the registration of a read command<br>s system performance. Optimal setting<br>CCESS.bus interface to determine this |  |  |  |

|         | 000: Reserved<br>001: Reserved                                                                                                                                                                                                                                                                                                                                         | 010: 2 CLK<br>011: 3 CLK                                 | 100: 4 CLK<br>101: 5 CLK                                    | 110: 6 CLK<br>111: 7 CLK                                     |                                                                                                                        |  |  |  |

|         | This field will not                                                                                                                                                                                                                                                                                                                                                    | take effect until SDI                                    | RAMPRG (bit 0 of MC                                         | C_MEM_CNTRL1) transitio                                      | ns from 0 to 1.                                                                                                        |  |  |  |

| 27:24   | RC (RFSH to RF commands:                                                                                                                                                                                                                                                                                                                                               | SH/ACT Command                                           | d Period, tRC). Minim                                       | um number of SDRAM clo                                       | ck between RFSH and RFSH/ACT                                                                                           |  |  |  |

|         | 0000: Reserved<br>0001: 2 CLK<br>0010: 3 CLK<br>0011: 4 CLK                                                                                                                                                                                                                                                                                                            | 0100: 5 CLK<br>0101: 6 CLK<br>0110: 7 CLK<br>0111: 8 CLK | 1000: 9 CLK<br>1001: 10 CLK<br>1010: 11 CLK<br>1011: 12 CLK | 1100: 13 CLK<br>1101: 14 CLK<br>1110: 15 CLK<br>1111: 16 CLK |                                                                                                                        |  |  |  |

| 23:20   | RAS (ACT to PR                                                                                                                                                                                                                                                                                                                                                         | E Command Perio                                          | d, tRAS). Minimum n                                         | umber of SDRAM clocks b                                      | etween ACT and PRE commands:                                                                                           |  |  |  |

|         | 0000: Reserved<br>0001: 2 CLK<br>0010: 3 CLK<br>0011: 4 CLK                                                                                                                                                                                                                                                                                                            | 0100: 5 CLK<br>0101: 6 CLK<br>0110: 7 CLK<br>0111: 8 CLK | 1000: 9 CLK<br>1001: 10 CLK<br>1010: 11 CLK<br>1011: 12 CLK | 1100: 13 CLK<br>1101: 14 CLK<br>1110: 15 CLK<br>1111: 16 CLK |                                                                                                                        |  |  |  |

| 19      | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | I). Write as 0.                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

| 18:16   | RP (PRE to ACT                                                                                                                                                                                                                                                                                                                                                         | Command Period                                           | , tRP). Minimum num                                         | ber of SDRAM clocks betw                                     | veen PRE and ACT commands:                                                                                             |  |  |  |

|         | 000: Reserved<br>001: 1 CLK                                                                                                                                                                                                                                                                                                                                            | 010: 2 CLK<br>011: 3 CLK                                 | 100: 4 CLK<br>101: 5 CLK                                    | 110: 6 CLK<br>111: 7 CLK                                     |                                                                                                                        |  |  |  |

| 15      | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | I). Write as 0.                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

| 14:12   | ` •                                                                                                                                                                                                                                                                                                                                                                    |                                                          |                                                             |                                                              | RAM clock between ACT and otimal setting should be used:                                                               |  |  |  |

|         | 000: Reserved<br>001: 1 CLK                                                                                                                                                                                                                                                                                                                                            | 010: 2 CLK<br>011: 3 CLK                                 | 100: 4 CLK<br>101: 5 CLK                                    | 110: 6 CLK<br>111: 7 CLK                                     |                                                                                                                        |  |  |  |

| 11      | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | I). Write as 0.                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

| 10:8    | RRD (ACT(0) to ACT(1) Command Period, tRRD). Minimum number of SDRAM clocks between ACT and ACT command to two different component banks within the same module bank. The memory controller does not perform back-to-back Activate commands to two different component banks without a READ or WRITE command between them. Hence, this field should be written as 001. |                                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

| 7       | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | I). Write as 0.                                          |                                                             |                                                              |                                                                                                                        |  |  |  |

| 6:4     | ,                                                                                                                                                                                                                                                                                                                                                                      | PRE command pe<br>ank is precharged:                     | riod, tDPL). Minimum                                        | number of SDRAM clocks                                       | s from the time the last write datum is                                                                                |  |  |  |

|         | 000: Reserved<br>001: 1 CLK                                                                                                                                                                                                                                                                                                                                            | 010: 2 CLK<br>011: 3 CLK                                 | 100: 4 CLK<br>101: 5 CLK                                    | 110: 6 CLK<br>111: 7 CLK                                     |                                                                                                                        |  |  |  |

| 3:0     | RSVD (Reserved                                                                                                                                                                                                                                                                                                                                                         | I). Leave unchange                                       | d. Always returns a 1                                       | 01h.                                                         |                                                                                                                        |  |  |  |

Table 1-2. SC2200 Memory Controller Registers (Continued)

| Bit     | Description                                                                                                                                                                              |                                                                               |                                      |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|--|--|--|

| GX_BASE | E+8414h-8417h                                                                                                                                                                            | MC_GBASE_ADD (R/W)                                                            | Reset Value: 00000000h               |  |  |  |

| 31:18   | RSVD (Reserved). Write                                                                                                                                                                   | as 0.                                                                         |                                      |  |  |  |

| 17      | TE (Test Enable TEST[3:                                                                                                                                                                  | 0]).                                                                          |                                      |  |  |  |

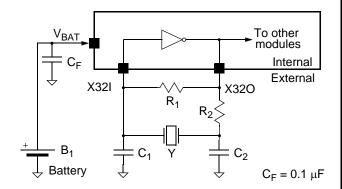

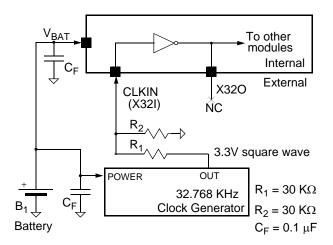

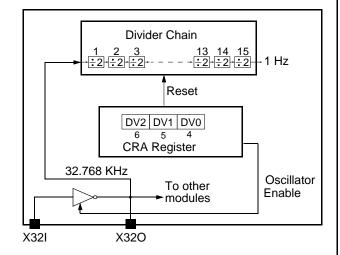

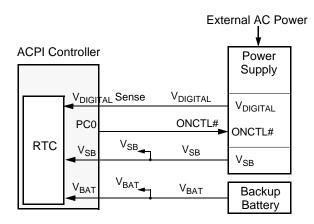

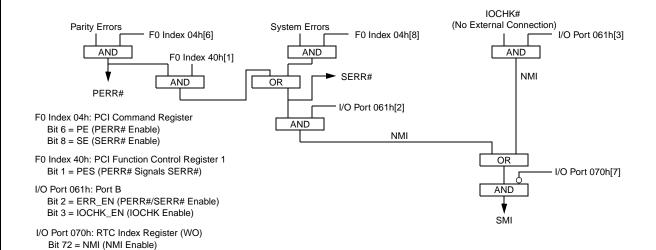

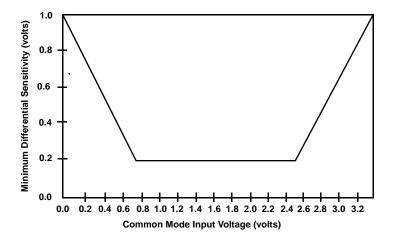

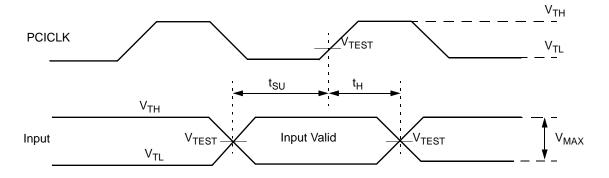

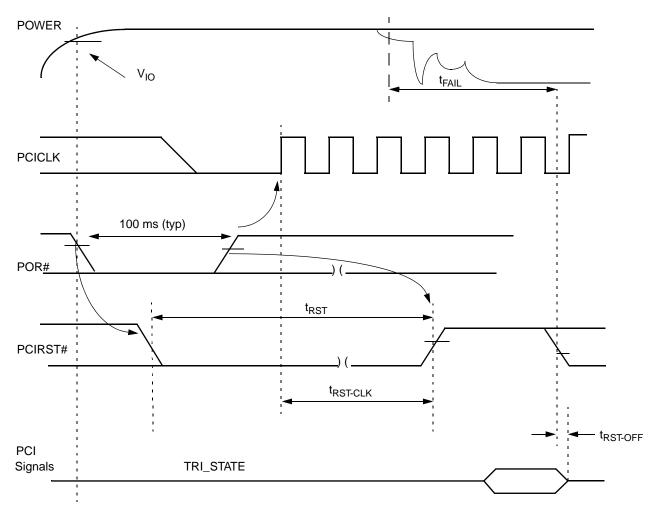

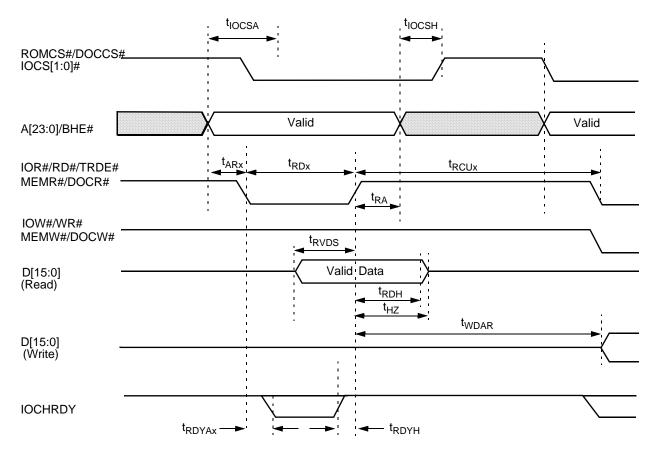

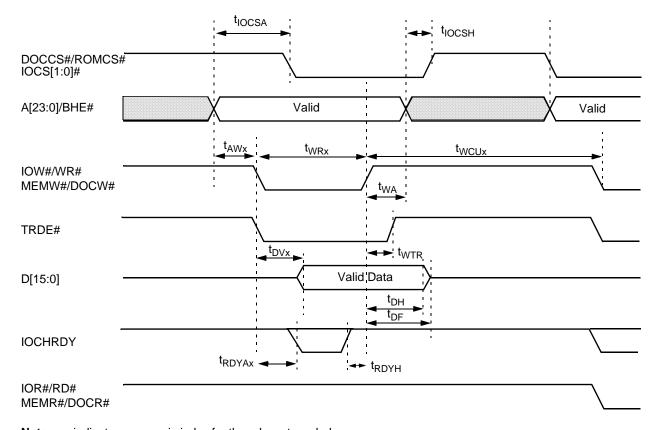

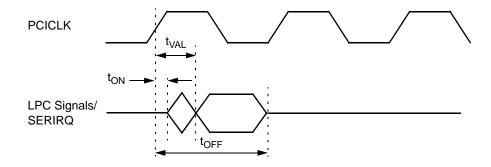

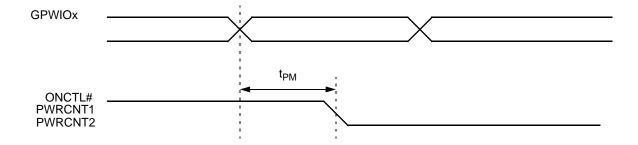

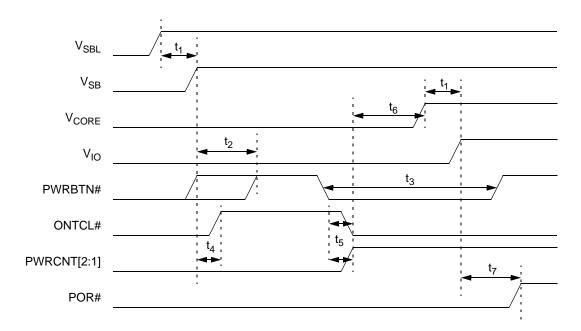

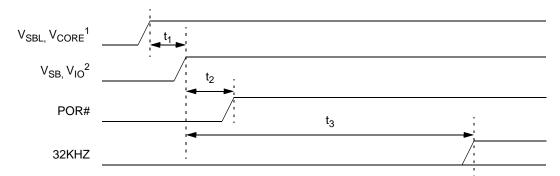

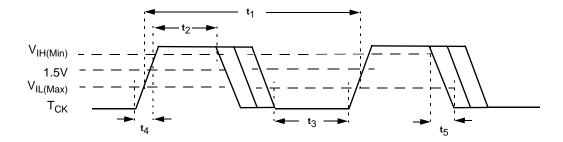

|         | 0: TEST[3:0] are driven log<br>1: TEST[3:0] pins are used                                                                                                                                | w (normal operation).<br>If to output test information.                       |                                      |  |  |  |