# Power-Line Communications Analog Front-End

Check for Samples: AFE032

# FEATURES

- Supports:

- CENELEC Bands A, B, C, D

- ARIB STD-T84, FCC

- FSK, SFSK, and NB-OFDM

- Conforms To:

- EN50065-1, -2, -3, -7

- FCC, Part 15

- ARIB STD-T84

- Standards:

- G3, PRIME, P1901.2, ITU-G.hnem

- Programmable Tx Low-Pass Filters and Rx Band-Pass Filters

- Integrated Power-Line Driver with Thermal and Overcurrent Protection

- Low-Power Consumption:

- 50 mW (Receiver Mode)

- Receive Sensitivity: 10 μV<sub>RMS</sub> (Typ)

- Four-Wire SPI<sup>™</sup> Interface

- Three Integrated Zero-Crossing Detectors

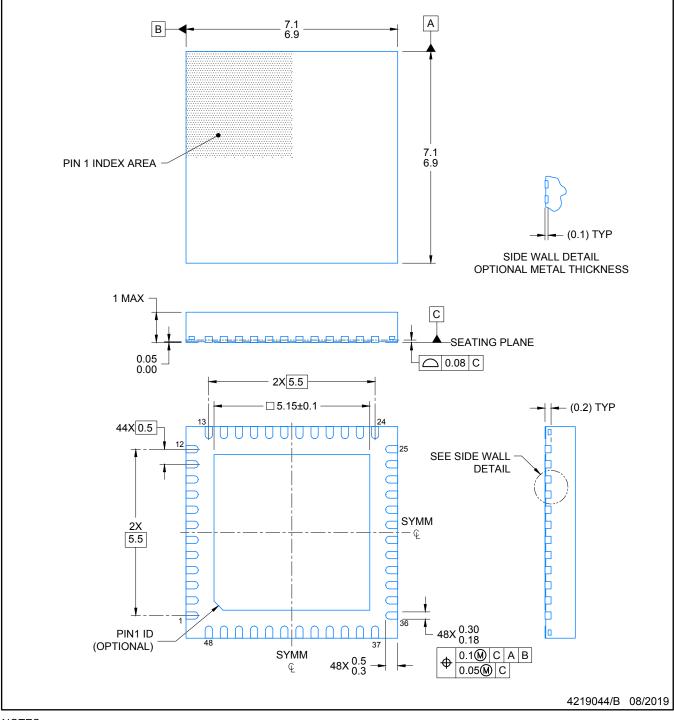

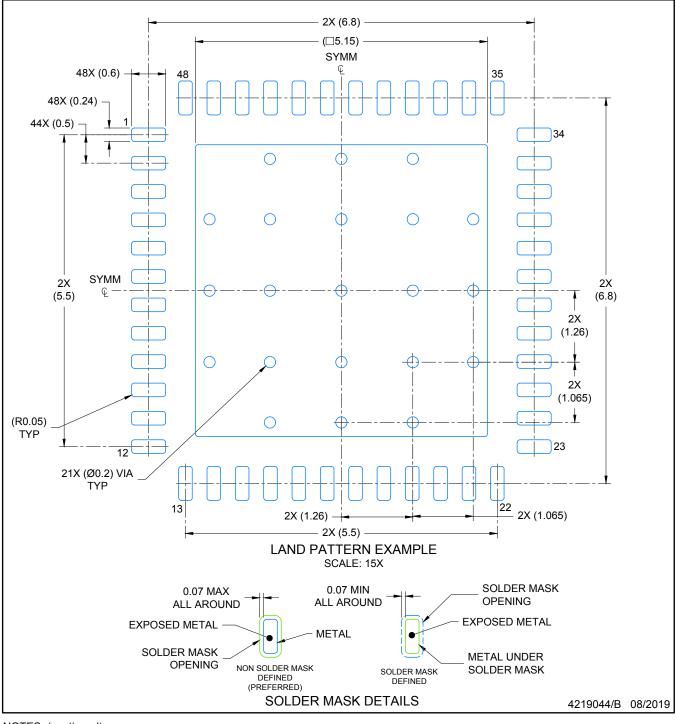

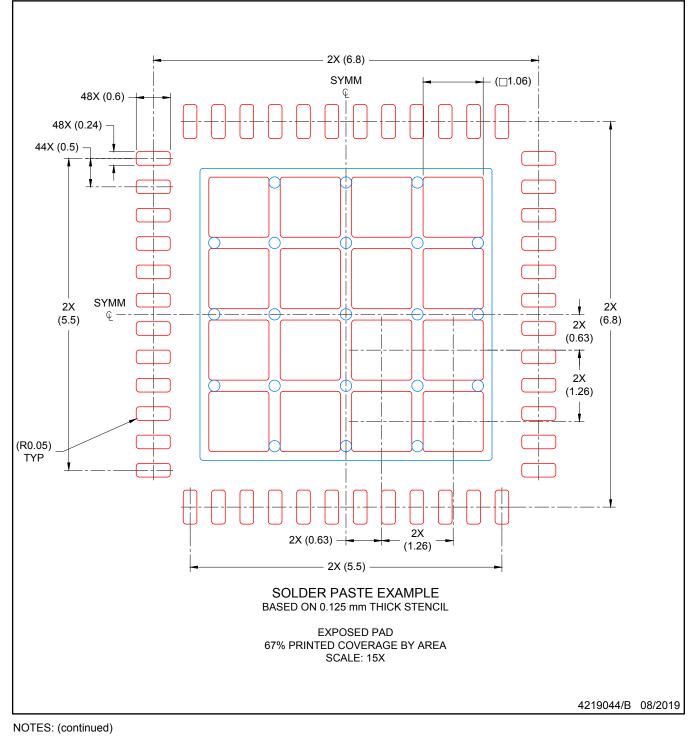

- Package: QFN-48 PowerPAD<sup>™</sup>

- Extended Temperature Range: -40°C to +125°C

# **APPLICATIONS**

- eMetering

- Home Area Networks

- Lighting

- Solar

- Pilot Wires and EVSEs

## DESCRIPTION

The AFE032 is a low-cost, integrated, power-line communications (PLC), analog front-end (AFE) device capable of transformer-coupled connections to the power-line while under the control of a digital signal processor (DSP) or microcontroller. This device is ideal for driving high-current, low-impedance lines up to 1.9 A into reactive loads.

The integrated receiver is able to detect signals down to 10  $\mu$ V<sub>RMS</sub> (G3-FCC mode) and is capable of a wide range of gain options to adapt to varying input-signal conditions. The monolithic integrated circuit provides high reliability in demanding power-line communication applications.

The AFE032 transmit power amplifier operates from a single supply in the range of 7 V to 24 V. At typical load current ( $I_{OUT} = 1.5 A_{PEAK}$ ), a wide output swing provides a 12-V<sub>PP</sub> capability with a nominal 15-V supply.

The device is internally protected against overtemperature and short-circuit conditions. The device also provides a selectable current limit. An interrupt output is provided, indicating current limit, thermal limit, and undervoltage. A shutdown pin is also available, and can be used to quickly place the device into the lowest-power state. Each functional block can be enabled or disabled to optimize power dissipation through the serial peripheral interface (SPI),

The AFE032 is housed in a thermally-enhanced, surface-mount, PowerPAD, QFN-48 package. Operation is specified over the extended industrial junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments. Illinois Capacitor is a trademark of Illinois Capacitor, Inc. SPI is a trademark of Motorola Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## ORDERING INFORMATION<sup>(1)</sup>

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                  |                                      |                               |                                 | VALUE                       | UNIT |

|------------------|--------------------------------------|-------------------------------|---------------------------------|-----------------------------|------|

| PA_VS            | Supply voltage (pins 44, 4           | 5)                            |                                 | +26                         | V    |

|                  |                                      |                               | Pins 3, 4, 6, 7, 8, 10          | DGND - 0.4 to DVDD + 0.4    | V    |

|                  |                                      | V II. (2)                     | Pins 13, 21, 28, 31, 32, 38, 39 | AGND - 0.4 to AVDD + 0.4    | V    |

|                  |                                      | Voltage <sup>(2)</sup>        | Pins 18, 19                     | PA_GND - 0.4 to PA_VS + 0.4 | V    |

|                  |                                      |                               | Pin 27                          | AVDD + 0.4 to 26            | V    |

|                  | Signal input terminals               |                               | Pins 3, 4, 6, 7, 8, 10          | ±10                         | mA   |

|                  |                                      | Current <sup>(2)</sup>        | Pins 13, 21, 28, 31, 32, 38, 39 | ±10                         | mA   |

|                  |                                      | Current                       | Pins 18, 19                     | ±10                         | mA   |

|                  |                                      |                               | Pin 35                          | ±10                         | mA   |

|                  |                                      |                               | Pins 5, 9, 47, 48               | DGND - 0.4 to DVDD + 0.4    | V    |

|                  |                                      | Voltage                       | Pins 14, 17, 20, 22, 33, 36, 37 | AGND - 0.4 to AVDD + 0.4    | V    |

|                  |                                      |                               | Pins 42, 43                     | PA_GND - 0.4 to PA_VS + 0.4 | V    |

|                  | Signal output terminals              | Current; short-circuit to GND | Pins 5, 9, 47, 48               | Continuous                  |      |

|                  |                                      | Current; short-circuit to GND | Pins 14, 17, 20, 22, 33, 36, 37 | Continuous                  |      |

|                  |                                      | Current; short-circuit to GND | Pins 42, 43                     | Continuous                  |      |

| AVDD             | Analog supply voltage (pir           | ns 11, 30)                    |                                 | 5.5                         | V    |

| DVDD             | Digital supply voltage               |                               |                                 | 5.5                         | V    |

| T <sub>A</sub>   | Operating temperature <sup>(3)</sup> |                               |                                 | -40 to +150                 | °C   |

| T <sub>stg</sub> | Storage temperature                  |                               |                                 | -55 to +150                 | °C   |

| TJ               | Junction temperature                 |                               |                                 | +150                        | °C   |

|                  |                                      | Human body model (HBM)        |                                 | 3000                        | V    |

| ESD              | Electrostatic discharge<br>ratings   | Machine model (MM)            |                                 | 200                         | V    |

|                  |                                      | Charged device model (CDM)    |                                 | 500                         | V    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.4 V beyond the supply rails should be current limited to 10 mA or less.

(3) The device automatically goes to shutdown above +165°C.

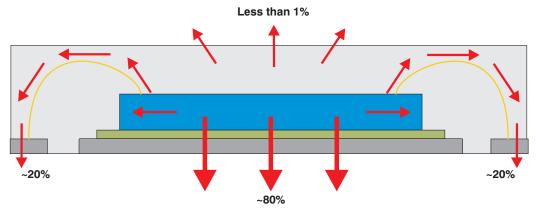

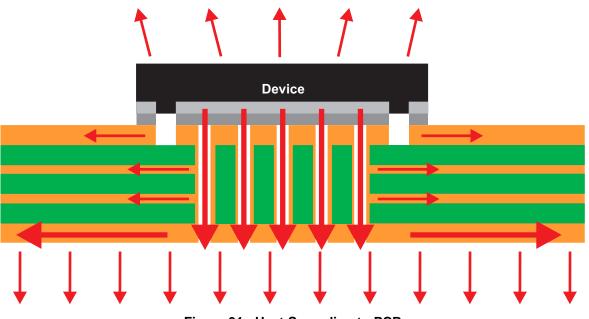

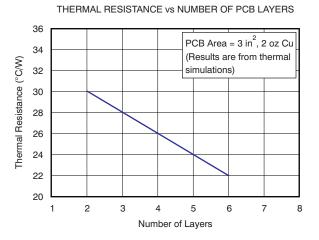

## THERMAL INFORMATION

|                    |                                              | AFE032    |       |

|--------------------|----------------------------------------------|-----------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                | RGZ (QFN) | UNITS |

|                    |                                              | 48 PINS   |       |

| θ <sub>JA</sub>    | Junction-to-ambient thermal resistance       | 22.5      |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 12.1      |       |

| θ <sub>JB</sub>    | Junction-to-board thermal resistance         | 7.5       | °C/W  |

| Ψյт                | Junction-to-top characterization parameter   | 2.0       | -C/W  |

| Ψјв                | Junction-to-board characterization parameter | 5.4       |       |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | 1.7       |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

**AFE032**

## **ELECTRICAL CHARACTERISTICS: Transmitter**

At  $T_{CASE} = +25^{\circ}C$ ,  $V_{PAVS} = 15$  V, and  $V_{AVDD} = V_{DVDD} = 3.3$  V, unless otherwise noted.

|                | PARAMET                                         | ER                 | TEST CONDITIONS                                                                                                      | MIN                         | TYP                                | MAX                             | UNIT                 |

|----------------|-------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------|---------------------------------|----------------------|

| DAC            |                                                 |                    |                                                                                                                      |                             |                                    |                                 |                      |

|                | Resolution                                      |                    | 12-bit DAC, internal $V_{REF} = 0.7 V$                                                                               | 165                         | 171                                | 176                             | μV                   |

| DR             | Data rate <sup>(1)</sup>                        |                    | DAC pin high, 12-bit word                                                                                            |                             | 4.8                                | 5.2                             | MSPS                 |

| G <sub>E</sub> | Gain error                                      |                    | Full-scale range, $T_J = -40^{\circ}C$ to +125°C                                                                     | -2%                         | ±0.5%                              | 2%                              |                      |

| DAC OU         | ITPUT                                           |                    |                                                                                                                      |                             |                                    |                                 |                      |

| Ro             | Output resistance                               |                    | G = 1, f = 100 kHz                                                                                                   |                             | 1                                  |                                 | kΩ                   |

| TX_PGA         | INPUT                                           |                    |                                                                                                                      |                             |                                    |                                 |                      |

|                | Input voltage rang                              | je                 |                                                                                                                      | (AGND +<br>0.15) /<br>gain  | (AVDD                              | – 0.15) /<br>gain               | V                    |

|                |                                                 |                    | G = 1.15 V/V                                                                                                         |                             | 52                                 |                                 | kΩ                   |

| <b>D</b>       | land and internet                               |                    | G = 2.3 V/V                                                                                                          |                             | 34                                 |                                 | kΩ                   |

| RI             | Input resistance                                |                    | G = 3.25 V/V                                                                                                         |                             | 26                                 |                                 | kΩ                   |

|                |                                                 |                    | G = 4.6 V/V                                                                                                          |                             | 20                                 |                                 | kΩ                   |

| G              | Gain                                            |                    |                                                                                                                      | 1.15, 2                     | 20<br>.3, 3.25, 4.6 <sup>(2)</sup> |                                 | V/V                  |

| G <sub>E</sub> | Gain error                                      |                    | Includes DAC, programmable filter, and TX_PGA for all gains, $T_J = -40^{\circ}$ C to +125°C                         | -2%                         | ±0.1%                              | 2%                              |                      |

|                | Gain error drift                                |                    | Includes DAC, programmable filter, and TX_PGA for all gains, $T_J = -40^{\circ}C$ to +125°C                          | -10                         | ±3                                 | +10                             | ppm/°C               |

| TX_PGA         | FREQUENCY RESP                                  | ONSE               |                                                                                                                      |                             |                                    |                                 |                      |

|                |                                                 |                    | $C_L = 20 \text{ pF}, \text{ G} = 1.15 \text{ V/V},$<br>$T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$ |                             | 30                                 |                                 | MHz                  |

| BW             | Bandwidth <sup>(3)</sup>                        |                    | $C_L = 20 \text{ pF}, \text{ G} = 2.3 \text{ V/V}, T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$       |                             | 21.5                               |                                 | MHz                  |

| DVV            | Banawidin                                       |                    | $C_L = 20 \text{ pF}, \text{ G} = 3.25 \text{ V/V}, T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$      |                             | 17.5                               | MHz<br>MHz<br>MHz<br>MHz<br>MHz |                      |

|                |                                                 |                    | $C_L = 20 \text{ pF}, \text{ G} = 4.6 \text{ V/V}, T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$       |                             | 15.5                               |                                 | MHz                  |

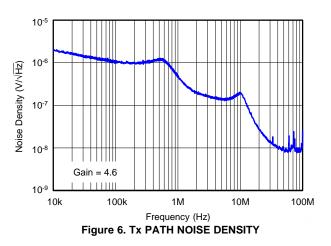

| TX PATH        | H TRANSMITTER NO                                | ISE <sup>(4)</sup> |                                                                                                                      |                             |                                    |                                 |                      |

|                |                                                 | CEN-A              | 35 kHz to 95 kHz                                                                                                     |                             | 370                                |                                 | $\mu V_{\text{RMS}}$ |

|                |                                                 | CEN-B              | 95 kHz to 125 kHz                                                                                                    |                             | 220                                |                                 | $\mu V_{\text{RMS}}$ |

|                |                                                 | CEN-C              | 125 kHz to 140 kHz                                                                                                   |                             | 160                                |                                 | $\mu V_{\text{RMS}}$ |

|                | Integrated noise<br>at PA output <sup>(5)</sup> | CEN-D              | 140 kHz to 148 kHz                                                                                                   |                             | 98                                 |                                 | $\mu V_{RMS}$        |

|                |                                                 | ARIB STD-T84       | 35 kHz to 420 kHz                                                                                                    |                             | 640                                |                                 | $\mu V_{RMS}$        |

|                |                                                 | FCC-LOW            | 35 kHz to 125 kHz                                                                                                    |                             | 384                                |                                 | $\mu V_{\text{RMS}}$ |

|                |                                                 | G3-FCC             | 150 kHz to 490 kHz                                                                                                   |                             | 565                                |                                 | $\mu V_{\text{RMS}}$ |

| POWER          | AMPLIFIER (PA) INF                              | TUT                |                                                                                                                      |                             |                                    |                                 |                      |

|                | Input voltage rang                              | je                 | For linear operation                                                                                                 | (PA_GND<br>+ 0.4) /<br>gain | (PA_V                              | S – 0.4) /<br>gain              | V                    |

|                | Input impedance                                 |                    |                                                                                                                      | -                           | 17                                 |                                 | kΩ                   |

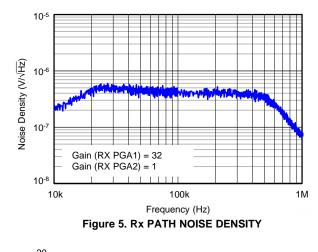

| PA FREG        | QUENCY RESPONSE                                 | E                  |                                                                                                                      | I                           |                                    | 1                               |                      |

| BW             | Bandwidth                                       |                    | I <sub>LOAD</sub> = 0 mA                                                                                             | 3.4                         | 3.82                               | 4.23                            | MHz                  |

| SR             | Slew rate                                       |                    | PA_VS = 24 V, 20-V step                                                                                              |                             | 75                                 |                                 | V/µs                 |

|                | Full-power bandw                                | idth               | $PA_VS = 24 \text{ V}, \text{ V}_{OUT} = 20 \text{ V}_{PP}$                                                          |                             | 1                                  |                                 | MHz                  |

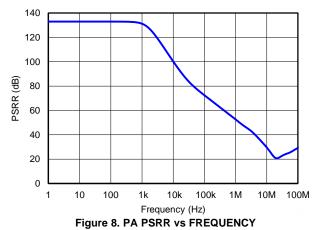

| PSRR           | Power-supply reje                               |                    | RTI, dc to $f = 50$ kHz                                                                                              | 80                          | 94                                 |                                 | dB                   |

(1) Refer to the Application Information section.

(2) This parameter is from DAC\_OUT to TX\_F\_OUT. This parameter includes the LPF gain error and is the dc gain. Adding LPF causes some loss of gain flatness.

This parameter is internal to the device. Bandwidth is designed and simulated over corners to ensure a low-distortion PGA in the (3) application.

Includes the DAC, programmable filter, TX\_PGA, and PA noise-reducing capacitor = 1 nF from DAC\_NRF to ground, PA\_NRF to (4) ground, and TX\_RF\_NRF to ground.

Includes the DAC, TX\_PGA (gain = 4.6), LPF, and PA. (5)

www.ti.com

STRUMENTS

EXAS

# **ELECTRICAL CHARACTERISTICS: Transmitter (continued)**

At  $T_{CASE}$  = +25°C,  $V_{PAVS}$  = 15 V, and  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, unless otherwise noted.

|                | PARAME                         | TER                                 | TEST CONDITIONS                                             | MIN     | TYP                | MAX         | UNIT                                         |

|----------------|--------------------------------|-------------------------------------|-------------------------------------------------------------|---------|--------------------|-------------|----------------------------------------------|

| PA OU          | TPUT                           |                                     |                                                             |         |                    |             |                                              |

|                |                                |                                     | I <sub>O</sub> = 200-mA sourcing, 1-ms pulse                |         |                    | 0.5         | V                                            |

|                | Voltage output                 | From PA_VS                          | I <sub>O</sub> = 1.5-A sourcing, 1-ms pulse                 |         |                    | 2.25        | V                                            |

| Vo             | swing                          | From PA GND                         | $I_0 = 200 \text{ mA sinking}, 1\text{-ms pulse}$           |         |                    | 0.5         | V                                            |

|                |                                | FIOIII FA_GIND                      | $I_0 = 1.5$ -A sinking, 1-ms pulse                          |         |                    | 1.5         | V                                            |

|                | Maximum continuous current, dc |                                     | Pin 26 connected to ground,<br>REG_PA_CURRENT_CFG[5:4] = 11 |         | 1.9                |             | А                                            |

|                | Output resistance              | e                                   | I <sub>O</sub> = 1.9 A, f = 500 kHz                         |         | 0.1                |             | Ω                                            |

|                | PA disabled outp               | ut impedance                        | f = 100 kHz, PA_NRF enabled                                 |         | 130    105         |             | kΩ    pF                                     |

|                | Resistor-selectable            |                                     | R <sub>SET</sub> connected from pin 26 to ground            | See the | Application In     | formation : | section                                      |

|                | Output current<br>limit        |                                     | Pin 26 connected to ground,<br>REG_PA_CURRENT_CFG[5:4] = 00 |         | 1.25               |             | А                                            |

|                |                                |                                     | Pin 26 connected to ground,<br>REG_PA_CURRENT_CFG[5:4] = 01 |         | 1.8                |             | А                                            |

|                |                                | Digitally-selectable <sup>(6)</sup> | Pin 26 connected to ground,<br>REG_PA_CURRENT_CFG[5:4] = 10 |         | 2.5                |             | kΩ    pF<br>section<br>A<br>A<br>A<br>A<br>A |

|                |                                |                                     | Pin 26 connected to ground,<br>REG_PA_CURRENT_CFG[5:4] = 11 |         | 3.0                |             | А                                            |

| PA TH          | ERMAL SHUTDOWN                 |                                     |                                                             |         |                    |             |                                              |

|                | Junction tempera               | ature at shutdown                   |                                                             |         | +165               |             | °C                                           |

|                | Hysteresis                     |                                     |                                                             |         | +15                |             | °C                                           |

|                | Return to normal               | operation                           |                                                             |         | +150               |             | °C                                           |

| PA TSE         | ENSE DIODE                     |                                     |                                                             |         |                    |             |                                              |

| η              | Diode ideality fac             | tor                                 |                                                             |         | 1.03               |             |                                              |

| PA GA          | IN                             |                                     |                                                             |         |                    |             |                                              |

| G              | Nominal gain                   |                                     | PA_OUT / PA_IN                                              |         | 7.4 <sup>(7)</sup> |             | V/V                                          |

| G <sub>E</sub> | Gain error                     |                                     | $T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$            | -2%     | 0.1%               | 2%          |                                              |

|                | Gain error drift               |                                     | $T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$            |         | ±5                 |             | ppm/°C                                       |

(6)

Refer to the *Application Information* section. This gain reflects a direct measurement on the PA block by itself. The gain in the signal chain composed by Tx PGA, Tx Filter and PA (7) equals the Tx PGA gain multiplied by 7 V/V (where 7 V/V is the gain of the PA block when its input is capacitively coupled to the Tx Filter output). Refer to the Power Amplifier Block section for more information.

AFE032

www.ti.com

#### SBOS669A - AUGUST 2013 - REVISED DECEMBER 2013

## ELECTRICAL CHARACTERISTICS: Programmable Filter

At  $T_{CASE}$  = +25°C,  $V_{PAVS}$  = 15 V, and  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, unless otherwise noted.

|                                                       | PARAME                               | TER          | TEST CONDITIONS                                                                     | MIN | TYP               | MAX | UNIT |

|-------------------------------------------------------|--------------------------------------|--------------|-------------------------------------------------------------------------------------|-----|-------------------|-----|------|

| LOW-PASS                                              | FILTER (LPF)                         |              | I                                                                                   |     |                   |     |      |

| 0.1.11                                                | CEN-A                                |              | 1-dB gain flatness, $T_J = -40^{\circ}C$ to +125°C                                  | 94  | 102               | 110 | kHz  |

| Cutoff<br>frequencies<br>in Tx<br>mode <sup>(1)</sup> | CEN-B, CEN-C, CE                     | N-D, FCC-LOW | 1-dB gain flatness, $T_J = -40^{\circ}C$ to +125°C                                  | 148 | 160               | 172 | kHz  |

|                                                       | ARIB STD-T84                         |              | 1-dB gain flatness, $T_J = -40^{\circ}C$ to +125°C                                  | 405 | 435               | 475 | kHz  |

| mode                                                  | G3-FCC                               |              | 1-dB gain flatness, $T_J = -40^{\circ}C$ to +125°C                                  | 470 | 505               | 540 | kHz  |

|                                                       | Transition time                      |              | PA_NRF, TX_RX_NRF, and DAC,<br>T <sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C |     | 80 <sup>(2)</sup> |     | μs   |

|                                                       | Tx to Rx                             |              | NRF enabled, $T_J = -40^{\circ}C$ to +125°C                                         |     | 30                |     | μs   |

| LPF OUTPU                                             | т                                    |              |                                                                                     |     |                   |     |      |

| R <sub>0</sub>                                        | Output impedance                     |              | f = 100 kHz                                                                         |     | 1                 |     | kΩ   |

| HIGH-PASS                                             | FILTER (HPF)                         |              |                                                                                     |     |                   |     |      |

|                                                       | CEN-A, CEN-B, CE<br>ARIB STD-T84, FC |              | 1-dB gain flatness, T <sub>J</sub> = -40°C to +125°C                                | 30  | 35                | 40  | kHz  |

|                                                       | G3-FCC                               |              | 1-dB gain flatness, $T_J = -40^{\circ}C$ to +125°C                                  | 120 | 132               | 152 | kHz  |

|                                                       | Transition time                      |              | PA_NRF, TX_RX_NRF, and DAC,<br>T <sub>J</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C |     | 30                |     | μs   |

|                                                       |                                      | Tx to Rx     | NRF enabled, $T_J = -40^{\circ}C$ to $+125^{\circ}C$                                |     | 80 <sup>(2)</sup> |     | μs   |

| HPF OUTPU                                             | т                                    | ·            | · · ·                                                                               | •   |                   | •   |      |

| R <sub>0</sub>                                        | Output impedance                     |              | f = 100 kHz                                                                         |     | 1                 |     | kΩ   |

(1) These cutoff frequencies are only valid when the filter is used as a low-pass filter. Refer to the *Register Map* section in the *Application Information* for register settings.

(2) See the Application Information section for the start-up procedure.

Texas Instruments

SBOS669A - AUGUST 2013 - REVISED DECEMBER 2013

www.ti.com

# ELECTRICAL CHARACTERISTICS: Receiver

At  $T_{CASE}$  = +25°C,  $V_{PAVS}$  = 15 V, and  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, unless otherwise noted.

|                | PARAMETER             | TEST CONDITIONS                                  | MIN TYP MAX                                             | UNIT   |

|----------------|-----------------------|--------------------------------------------------|---------------------------------------------------------|--------|

| RX_PG          | A1 INPUT              |                                                  |                                                         |        |

|                | Input voltage range   | For linear operation                             | (AGND +<br>0.15) / (AVDD - 0.15) /<br>gain gain         | V      |

|                |                       | G = 0.125 V/V                                    | 111.1                                                   | kΩ     |

|                |                       | G = 0.25 V/V                                     | 100                                                     | kΩ     |

|                |                       | G = 0.5 V/V                                      | 133                                                     | kΩ     |

|                |                       | G = 1 V/V                                        | 100                                                     | kΩ     |

| RI             | Input resistance      | G = 2 V/V                                        | 66                                                      | kΩ     |

|                |                       | G = 4 V/V                                        | 40                                                      | kΩ     |

|                |                       | G = 8 V/V                                        | 22                                                      | kΩ     |

|                |                       | G = 16 V/V                                       | 12                                                      | kΩ     |

|                |                       | G = 32 V/V                                       | 6                                                       | kΩ     |

| RX_PG          | A1 GAIN               |                                                  | -                                                       | -j     |

|                | DC gain               |                                                  | 0.125, 0.25, 0.5,<br>1, 2, 4, 8, 16, 32                 | V/V    |

| G <sub>E</sub> | Gain error            | For all gains, $T_J = -40^{\circ}C$ to +125°C    | -5% 5%                                                  |        |

|                | Gain error drift      | $T_{\rm J} = -40^{\circ}{\rm C}$ to +125°C       | ±100                                                    | ppm/°C |

| RX_PG          | A1 FREQUENCY RESPONSE |                                                  |                                                         |        |

|                |                       | C <sub>L</sub> = 20 pF, G = 0.125 V/V            | 47                                                      | MHz    |

|                |                       | C <sub>L</sub> = 20 pF, G = 0.25 V/V             | 18                                                      | MHz    |

|                |                       | C <sub>L</sub> = 20 pF, G = 0.5 V/V              | 6                                                       | MHz    |

|                |                       | C <sub>L</sub> = 20 pF, G = 1 V/V                | 4                                                       | MHz    |

| BW             | Bandwidth             | C <sub>L</sub> = 20 pF, G = 2 V/V                | 3                                                       | MHz    |

|                |                       | $C_L = 20 \text{ pF}, \text{ G} = 4 \text{ V/V}$ | 2.5                                                     | MHz    |

|                |                       | C <sub>L</sub> = 20 pF, G = 8 V/V                | 2.1                                                     | MHz    |

|                |                       | $C_{L} = 20 pF, G = 16 V/V$                      | 1.85                                                    | MHz    |

|                |                       | C <sub>L</sub> = 20 pF, G = 32 V/V               | 1.55                                                    | MHz    |

| RX_PG          | A2 INPUT              |                                                  |                                                         |        |

|                | Input voltage range   | For linear operation                             | (A <sub>GND</sub> + 0.15) / (AVDD - 0.15)/<br>gain gain | V      |

|                |                       | G = 1 V/V                                        | 54                                                      | kΩ     |

| RI             | Input resistance      | G = 4 V/V                                        | 21                                                      | kΩ     |

|                |                       | G = 16 V/V                                       | 5.5                                                     | kΩ     |

SBOS669A - AUGUST 2013 - REVISED DECEMBER 2013

## **ELECTRICAL CHARACTERISTICS: Receiver (continued)**

At  $T_{CASE}$  = +25°C,  $V_{PAVS}$  = 15 V, and  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, unless otherwise noted.

|                | PARAME                             | ΓER          | TEST CONDITIONS                                                  | MIN | TYP      | MAX | UNIT              |

|----------------|------------------------------------|--------------|------------------------------------------------------------------|-----|----------|-----|-------------------|

| Rx_PG          | GA2 GAIN                           |              |                                                                  |     |          |     |                   |

| G              | Gain                               |              |                                                                  |     | 1, 4, 16 |     | V/V               |

| G <sub>E</sub> | Gain error                         |              | For all gains, $T_J = -40^{\circ}C$ to $+125^{\circ}C$           | -2% |          | 2%  |                   |

|                | Gain error drift                   |              | $T_{\rm J} = -40^{\circ}{\rm C} \text{ to } +125^{\circ}{\rm C}$ |     | ±100     |     | ppm/°C            |

| RX_PG          | GA2 FREQUENCY RE                   | SPONSE       |                                                                  |     |          |     |                   |

|                |                                    |              | $C_L = 20 \text{ pF}, \text{ G} = 1 \text{ V/V}$                 |     | 6.73     |     | MHz               |

| BW             | Bandwidth                          |              | $C_L = 20 \text{ pF}, \text{ G} = 4 \text{ V/V}$                 |     | 5        |     | MHz               |

|                |                                    |              | C <sub>L</sub> = 20 pF, G = 16 V/V                               |     | 3        |     | MHz               |

| RX_PG          | GA2 OUTPUT                         |              |                                                                  |     |          |     |                   |

|                | Output resistance                  |              | G = 1, f = 100 kHz                                               |     | 1        |     | kΩ                |

| RX PA          | TH SENSITIVITY <sup>(1)</sup>      |              |                                                                  |     |          |     |                   |

|                |                                    | CEN-A        | 35 kHz to 95 kHz                                                 |     | 10       |     | $\mu V_{RMS}$     |

|                |                                    | CEN-B        | 95 kHz to 125 kHz                                                |     | 5        |     | μV <sub>RMS</sub> |

|                |                                    | CEN-C        | 125 kHz to 140 kHz                                               |     | 3        |     | $\mu V_{RMS}$     |

|                | Input-referred<br>integrated noise | CEN-D        | 140 kHz to 148 kHz                                               |     | 2        |     | $\mu V_{RMS}$     |

|                |                                    | ARIB STD-T84 | 35kHz to 400 kHz                                                 |     | 12       |     | $\mu V_{RMS}$     |

|                |                                    | FCC-LOW      | 35 kHz to 125 kHz                                                |     | 11       |     | $\mu V_{RMS}$     |

|                |                                    | G3-FCC       | 150 kHz to 490 kHz                                               |     | 10       |     | μV <sub>RMS</sub> |

(1) Noise-reducing capacitor = 1 nF from TX\_RX\_NRF to ground, RX\_PGA1 = 32, and RX\_PGA2 = 1.

## **ELECTRICAL CHARACTERISTICS: Noise-Reducing Filters**

## At $T_{CASE}$ = +25°C, $V_{PAVS}$ = 15 V, and $V_{AVDD}$ = $V_{DVDD}$ = 3.3 V, unless otherwise noted.

|                  | PARAMETER         | TEST CONDITIONS                                             | MIN TYP                 | MAX | UNIT |

|------------------|-------------------|-------------------------------------------------------------|-------------------------|-----|------|

| PA_NRF           | •                 |                                                             |                         | +   |      |

|                  | Bias voltage      |                                                             | V <sub>PAV S</sub> / 2  |     | V    |

| R <sub>OUT</sub> | Output resistance |                                                             | 4                       |     | kΩ   |

| t <sub>ON</sub>  | Turn-on time      | Noise-reducing capacitor = 1 nF from<br>PA_NRF to ground    | 250                     |     | ms   |

| t <sub>OFF</sub> | Turn-off time     |                                                             | 10                      |     | μs   |

| TX_RX_           | NRF               |                                                             |                         | ·   |      |

|                  | Bias voltage      |                                                             | V <sub>AVDD</sub> / 2   |     | V    |

| R <sub>OUT</sub> | Output resistance |                                                             | 1                       |     | kΩ   |

| t <sub>ON</sub>  | Turn-on time      | Noise-reducing capacitor = 1 nF from<br>TX_RX_NRF to ground | 10                      |     | μs   |

| t <sub>OFF</sub> | Turn-off time     |                                                             | 10                      |     | μs   |

| DAC_NF           | RF                |                                                             |                         | ·   |      |

|                  | Bias voltage      |                                                             | V <sub>AVDD</sub> / 4.7 |     | V    |

| R <sub>OUT</sub> | Output resistance |                                                             | 1                       |     | kΩ   |

| t <sub>ON</sub>  | Turn-on time      | Noise-reducing capacitor = 1 nF from<br>DAC_NRF to ground   | 10                      |     | μs   |

| t <sub>OFF</sub> | Turn-off time     |                                                             | 10                      |     | μs   |

www.ti.com

STRUMENTS

EXAS

# ELECTRICAL CHARACTERISTICS: Digital

At  $T_{CASE}$  = +25°C,  $V_{PAVS}$  = 15 V, and  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, unless otherwise noted.

|                 | PARAMETE                  | R                | TEST CONDITIONS                     | MIN             | TYP MAX                        | UNIT |

|-----------------|---------------------------|------------------|-------------------------------------|-----------------|--------------------------------|------|

| DIGITA          | L INPUTS (SCLK, DI, CS, S | SD, DAC, XCLK)   |                                     |                 |                                |      |

|                 | Leakage input current     |                  | $0 V \leq V_{IN} \leq DVDD$         | -1              | 0.01 1                         | μA   |

| V <sub>IH</sub> | High-level input voltage  | e                |                                     | 0.7 × DVDD      |                                | V    |

| V <sub>IL</sub> | Low-level input voltage   | )                |                                     |                 | 0.3 × DVDD                     | V    |

|                 | SD pin function           | SD pin high      | SD > 0.7 × DVDD                     | Dev             | vice in shutdown               |      |

|                 | (active high)             | SD pin low       | SD < 0.3 × DVDD                     | Device          | in normal operation            | 1    |

|                 | DAC pin function          | DAC pin high     | DAC > 0.7 × DVDD                    | SPI acc         | ess to DAC register            | s    |

|                 | (active high)             | DAC pin low      | DAC < 0.3 × DVDD                    | SPI access to c | SPI access to command and data |      |

|                 | XCLK frequency range      | •                | XCLK jitter < 180 ps                | 5               | 40                             | MHz  |

| DIGITA          | L OUTPUTS (DO, ZC_OUT     | )                |                                     |                 |                                |      |

| V <sub>OH</sub> | High-level output volta   | ge               | I <sub>OH</sub> = 3 mA              | DVDD - 0.4      | DVDD                           | V    |

| V <sub>OL</sub> | Low-level output voltage  | je               | $I_{OL} = -3 \text{ mA}$            | GND             | GND + 0.4                      | V    |

| DIGITA          | L OUTPUTS (INT, TX_FLA    | G, RX_FLAG)      |                                     |                 |                                |      |

| I <sub>OH</sub> | High-level output curre   | nt               | V <sub>OH</sub> = 3.3 V             |                 | 1                              |      |

| V <sub>OL</sub> | Low-level output voltage  | je               | I <sub>OL</sub> = 4 mA              |                 | 0.4                            | V    |

| I <sub>OL</sub> | Low-level output current  | nt               | V <sub>OL</sub> = 400 mV            | 4               |                                | mA   |

|                 | INT pin (active low,      | INT pin high     | INT sink high < 1 μA                | No              | ormal operation                |      |

|                 | open-drain)               | INT pin low      | INT < 0.4 V                         | Inter           | rupt has occurred              |      |

|                 | TX FLAG (active low,      | TX_FLAG pin high | TX_FLAG sink high < 1 μA            | Tx              | block disabled                 |      |

|                 | open-drain)               | TX_FLAG pin low  | TX_FLAG < 0.4 V                     | Т               | x block ready                  |      |

|                 | RX_FLAG (active           | RX_FLAG pin high | RX_FLAG sink high < 1 μA            | Rx              | block disabled                 |      |

|                 | low, open-drain)          | RX_FLAG pin low  | RX_FLAG < 0.4 V                     | R               | x block ready                  |      |

| GAIN T          | IMING                     |                  |                                     |                 |                                |      |

|                 | Gain select time          |                  |                                     |                 | 0.2                            | μs   |

| SHUTD           | OWN MODE TIMING           |                  |                                     |                 |                                |      |

|                 | Enable time               |                  | SD pin transitions from high to low |                 | 3                              | ms   |

|                 | Disable time              |                  | SD pin transitions from low to high |                 | 2                              |      |

| POR TI          | MING                      |                  |                                     |                 | 4                              |      |

|                 | Power-on reset power-     | up time          | DVDD ≥ 2 V                          |                 | 3                              | ms   |

SBOS669A - AUGUST 2013 - REVISED DECEMBER 2013

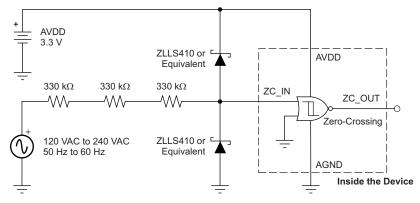

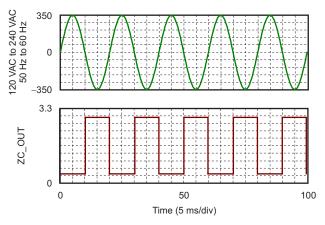

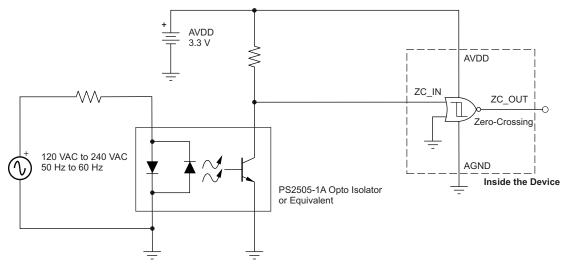

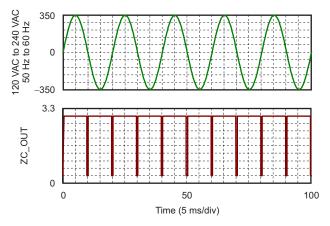

# ELECTRICAL CHARACTERISTICS: Zero-Crossing Detector

At  $T_{CASE}$  = +25°C,  $V_{PAVS}$  = 15 V, and  $V_{AVDD}$  =  $V_{DVDD}$  = 3.3 V, unless otherwise noted.

|                 | PARAMETER           | TEST CONDITIONS                                                | MIN  | TYP | MAX  | UNIT |

|-----------------|---------------------|----------------------------------------------------------------|------|-----|------|------|

|                 | Input voltage range |                                                                | AGND |     | AVDD | V    |

|                 | Input current range |                                                                | -10  |     | 10   | mA   |

| R <sub>IN</sub> | Input resistance    | $AGND \le V_{IN} \le AVDD$                                     |      | 2   |      | MΩ   |

| C <sub>IN</sub> | Input capacitance   |                                                                |      | 4   | 1.35 | pF   |

|                 | Rising threshold    |                                                                | 0.45 | 0.9 |      | V    |

|                 | Falling threshold   |                                                                | 0.25 | 0.5 | 0.75 | V    |

|                 | Hysteresis          |                                                                | 0.2  | 0.4 | 0.6  | V    |

|                 | Jitter              | 50 Hz and 60 Hz, 240 $V_{\text{RMS}}$ and 120 $V_{\text{RMS}}$ |      | 10  |      | ns   |

## ELECTRICAL CHARACTERISTICS: Power Supply

At  $T_{CASE} = +25^{\circ}C$ ,  $T_{J} = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{PAVS} = 15$  V, and  $V_{AVDD} = V_{DVDD} = 3.3$  V, unless otherwise noted.

|                     | PARAMETER          | TEST CONDITIONS                                                                | MIN | TYP | MAX | UNIT |

|---------------------|--------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| OPERATI             | NG SUPPLY RANGE    |                                                                                |     |     | I   |      |

| PA_VS               | Power amplifier    |                                                                                | 7   | 15  | 24  | V    |

| DVDD                | Digital supply     |                                                                                |     | 3.3 |     | V    |

| AVDD                | Analog supply      |                                                                                |     | 3.3 |     | V    |

| QUIESCE             | NT CURRENT (SD pin | low)                                                                           |     |     |     |      |

|                     |                    | I <sub>O</sub> = 0 V, PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 00 | 40  | 48  | 56  | mA   |

| IQ <sub>PA_VS</sub> | D                  | I <sub>O</sub> = 0 V, PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 01 | 68  | 78  | 88  | mA   |

|                     | Power amplifier    | I <sub>O</sub> = 0 V, PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 10 | 84  | 96  | 108 | mA   |

|                     |                    | I <sub>O</sub> = 0 V, PA = on <sup>(1)</sup> ,<br>REG_PA_CURRENT_CFG[7:6] = 11 | 10  | 17  | 24  | mA   |

|                     |                    | Tx configuration <sup>(2)</sup>                                                | 1.5 | 2.5 | 3.5 | mA   |

| IQ <sub>DVDD</sub>  | Digital supply     | Rx configuration <sup>(3)</sup>                                                | 1.1 | 2.1 | 3.1 | mA   |

|                     |                    | All blocks disabled <sup>(4)</sup>                                             |     | 330 | 450 | μA   |

|                     |                    | Tx configuration <sup>(3)</sup>                                                | 8   | 11  | 14  | mA   |

| IQ <sub>AVDD</sub>  | Analog supply      | Rx configuration <sup>(4)</sup>                                                | 9   | 13  | 17  | mA   |

|                     |                    | All blocks disabled <sup>(4)</sup>                                             |     | 25  | 100 | μA   |

| SHUTDO              | WN                 |                                                                                |     |     |     |      |

| SD <sub>PA_VS</sub> | Power amplifier    | SD pin high                                                                    |     | 40  | 150 | μA   |

| SD <sub>DVDD</sub>  | Digital supply     | SD pin high                                                                    |     | 330 | 400 | μA   |

| SD <sub>AVDD</sub>  | Analog supply      | SD pin high                                                                    |     | 25  | 50  | μA   |

(1) PA and PA output enabled.

(2) The DAC, TX\_PGA, low-pass filter, PA, PA\_NRF, TX\_RX\_NRF, and DAC\_NRF blocks are enabled in the Tx configuration. All other blocks are disabled.

(3) The RX\_PGA1, high-pass filter, low-pass filter, RX\_PGA2, and TX\_RX\_NRF blocks are enabled in the Rx configuration. All other blocks are disabled.

(4) All internal blocks disabled, SD pin low.

www.ti.com

STRUMENTS

ÈXAS

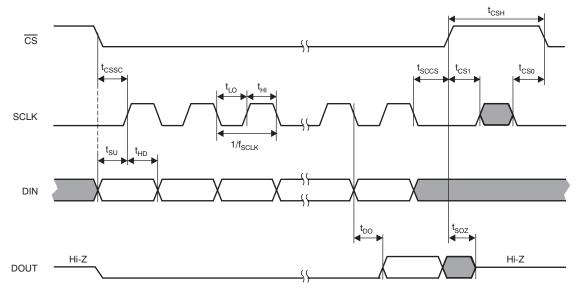

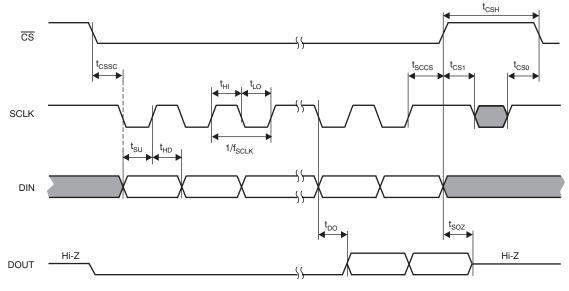

## **SPI TIMING REQUIREMENTS**

|                   | PARAMETER                                                    | MIN  | TYP | MAX | UNIT                             |

|-------------------|--------------------------------------------------------------|------|-----|-----|----------------------------------|

|                   | Input capacitance                                            |      | 1   |     | pF                               |

| t <sub>RFI</sub>  | Input rising and falling time ( $\overline{CS}$ , DIN, SCLK) |      |     | 2   | ns                               |

| t <sub>RFO</sub>  | DOUT rising and falling time                                 |      |     | 10  | ns                               |

| t <sub>CSH</sub>  | CS high time                                                 | 10   |     |     | DAC_CLK<br>cycles <sup>(1)</sup> |

| t <sub>CS0</sub>  | SCLK edge to $\overline{CS}$ falling edge setup time         | 10   |     |     | ns                               |

| t <sub>CSSC</sub> | CS falling edge to first SCLK edge setup time                | 10   |     |     | ns                               |

| f <sub>SCLK</sub> | SCLK frequency                                               |      | 20  | 30  | MHz                              |

| t <sub>HI</sub>   | SCLK high time                                               | 16.7 | 25  |     | ns                               |

| t <sub>LO</sub>   | SCLK low time                                                | 16.7 | 25  |     | ns                               |

| t <sub>SCCS</sub> | SCLK last edge to $\overline{CS}$ rising edge setup time     | 10   |     |     | ns                               |

| t <sub>CS1</sub>  | CS rising edge to SCLK edge setup time                       | 10   |     |     | ns                               |

| t <sub>SU</sub>   | DIN setup time                                               | 5    |     |     | ns                               |

| t <sub>HD</sub>   | DIN hold time                                                | 5    |     |     | ns                               |

| t <sub>DO</sub>   | SCLK to DOUT valid propagation delay                         |      |     | 16  | ns                               |

| t <sub>soz</sub>  | CS rising edge to DOUT forced to Hi-Z                        |      |     | 20  | ns                               |

(1)  $\overline{\text{CS}}$  pin must remain high for at least ten DAC\_CLK cycles after a write operation and must remain high for at least five DAC\_CLK cycles after a read operation.

#### www.ti.com

## TIMING DIAGRAMS

Figure 1. SPI Mode 0,0

Figure 2. SPI Mode 1,1

www.ti.com

### **PIN CONFIGURATION**

NOTE: Connect exposed thermal pad to ground.

#### SBOS669A - AUGUST 2013 - REVISED DECEMBER 2013

#### **PIN DESCRIPTIONS**

| NAME               | PIN NO. | DESCRIPTION                                                                                             |

|--------------------|---------|---------------------------------------------------------------------------------------------------------|

| AGND1              | 12      | Analog ground                                                                                           |

| AGND2              | 29      | Analog ground                                                                                           |

| AVDD1              | 11      | Analog supply                                                                                           |

| AVDD2              | 30      | Analog supply                                                                                           |

| CS                 | 6       | SPI digital chip-select input                                                                           |

| DAC                | 7       | DAC mode select digital input                                                                           |

| DAC_OUT            | 14      | DAC analog output                                                                                       |

| <br>DAC_NRF        | 16      | DAC noise-reducing filter analog input                                                                  |

| DGND               | 1       | Digital ground                                                                                          |

| DGND2              | 24      | Digital ground                                                                                          |

| DIN                | 4       | SPI digital input                                                                                       |

| DNC                | 15, 34  | Do not connect                                                                                          |

| DOUT               | 5       | SPI digital output (push or pull)                                                                       |

| DVDD               | 2       | Digital supply                                                                                          |

| INT                | 9       | Interrupt on undervoltage, undercurrent, or thermal overload (digital output, open-drain, active low)   |

| NC                 | 23, 25  | No internal connection (connect to GND or leave unconnected)                                            |

| PA_GND1            | 41      | Power amplifier ground                                                                                  |

| _                  | 41      |                                                                                                         |

| PA_GND2<br>PA_GND3 | 31      | Power amplifier ground (connect to PA_GND1, pin 41) Power amplifier ground (connect to PA_GND1, pin 41) |

| _                  |         |                                                                                                         |

| PA_IN              | 18      | Power amplifier analog input                                                                            |

| PA_ISET            | 26      | Power amplifier current-limit adjust pin (left open if not used)                                        |

| PA_NRF             | 19      | Power amplifier noise-reducing filter analog input                                                      |

| PA_OUT1            | 43      | Power amplifier output                                                                                  |

| PA_OUT2            | 42      | Power amplifier output (connect to PA_OUT1, pin 43)                                                     |

| PA_VS1             | 45      | Power amplifier supply                                                                                  |

| PA_VS2             | 44      | Power amplifier supply (connect to PA_VS1, pin 45)                                                      |

| PA_VS3             | 46      | Power amplifier supply (connect to PA_VS1, pin 45)                                                      |

| RX_F_OUT           | 22      | Receiver filter analog output                                                                           |

| RX_FLAG            | 48      | Receiver ready flag (digital output, open-drain, active low)                                            |

| RX_PGA1_IN         | 27      | Receiver PGA1 analog input                                                                              |

| RX_PGA2_IN         | 21      | Receiver PGA2 analog input                                                                              |

| RX_PGA2_OUT        | 20      | Receiver PGA2 analog output                                                                             |

| SCLK               | 3       | SPI serial clock input                                                                                  |

| SD                 | 8       | System shutdown digital input (active high)                                                             |

| TSENSE             | 35      | Analog temperature sensing diode (anode)                                                                |

| TX_F_OUT           | 17      | Transmit filter analog output                                                                           |

| TX_FLAG            | 47      | Transmitter ready flag (digital output, open-drain, active low)                                         |

| TX_PGA_IN          | 13      | Transmitter PGA analog input                                                                            |

| TX_RX_NRF          | 28      | Transmitter and receiver noise-reducing filter analog input                                             |

| XCLK               | 10      | DAC clock digital input                                                                                 |

| ZC_IN1             | 39      | Zero-crossing detector 1, analog input                                                                  |

| ZC_IN2             | 38      | Zero-crossing detector 2, analog input                                                                  |

| ZC_IN3             | 32      | Zero-crossing detector 3, analog input                                                                  |

| ZC_OUT1            | 37      | Zero-crossing detector 1, digital output (push or pull)                                                 |

| ZC_OUT2            | 36      | Zero-crossing detector 2, digital output (push or pull)                                                 |

| ZC_OUT3            | 33      | Zero-crossing detector 3, digital output (push or pull)                                                 |

www.ti.com

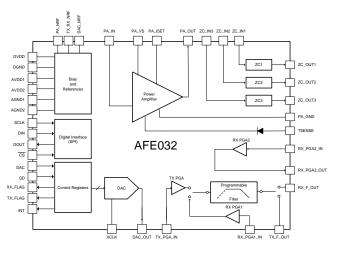

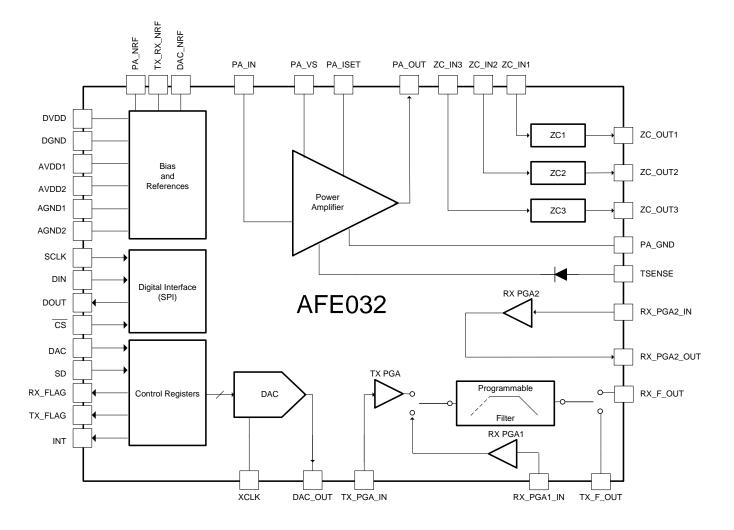

# FUNCTIONAL BLOCK DIAGRAM

କ୍ରି -20

-40

-50

-60

1000

Gain -30

#### SBOS669A - AUGUST 2013 - REVISED DECEMBER 2013

# www.ti.com **TYPICAL CHARACTERISTICS** 10 0 -10

90 kHz (CENELEC A)

420 kHz (ARIB)

490 kHz (FCC)

10k

140 kHz (CENELEC B to D)

100k

Frequency (Hz)

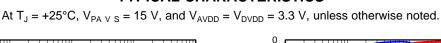

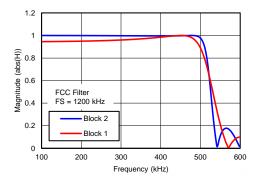

Figure 3. Tx, Rx LOW-PASS FILTER GAIN vs FREQUENCY

1M

10M

Figure 4. Rx BAND-PASS FILTER GAIN vs FREQUENCY

www.ti.com

## **APPLICATION INFORMATION**

## **GENERAL DESCRIPTION**

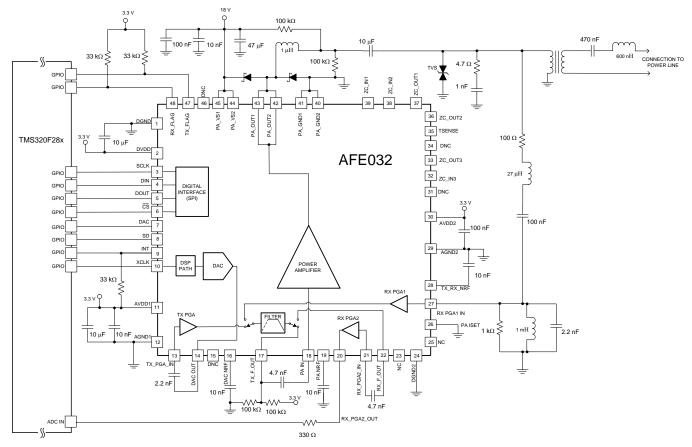

The AFE032 is an integrated, power-line communication, analog front-end device that functions in conjunction with a microcontroller. The device conditions data generated in a microcontroller and transmits such data onto power lines through a line-coupling circuit.

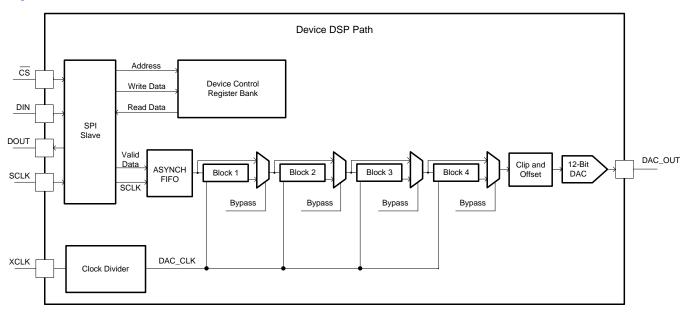

The device includes several primary functional blocks:

- A power amplifier (PA) transmits data onto power lines through a line-coupling circuit.

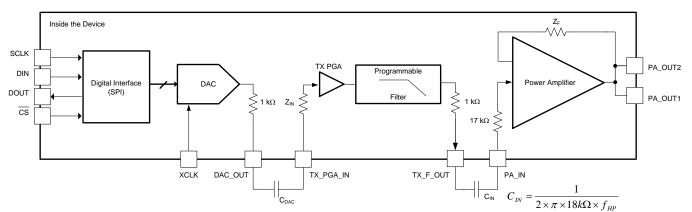

- The transmit path (Tx) consists of a high-precision, digital-to-analog converter (DAC), programmable amplifier (TX\_PGA), and low-pass filter (LPF).

- The receive path (Rx) consists of two programmable amplifiers (RX\_PGA1 and RX\_PAG2) and a band-pass filter [(an LPF and a high-pass filter (HPF)].

## **BLOCK DESCRIPTIONS**

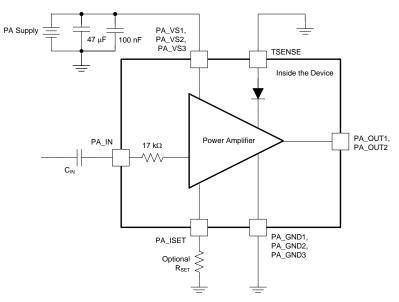

#### **Power Amplifier Block**

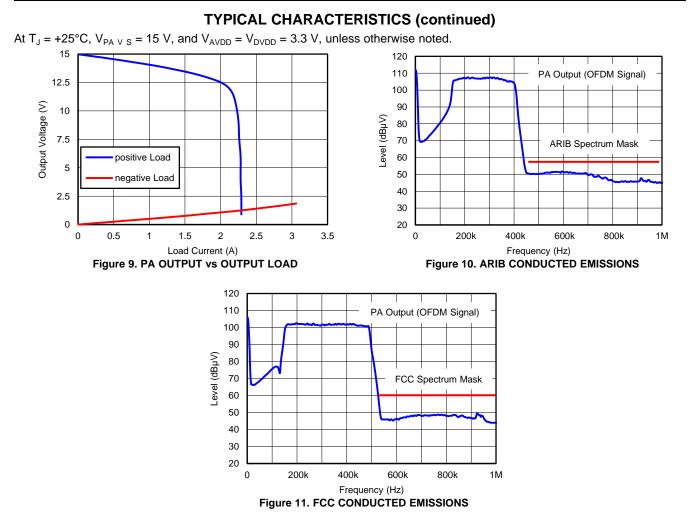

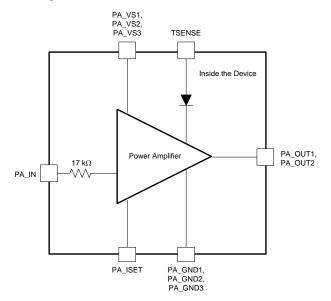

The power amplifier (PA) block consists of a high slew rate, high-voltage, and high-current operational amplifier. The PA is configured with an inverting gain of 7 V/V, has a low-pass filter response, and maintains excellent linearity and low distortion throughout its bandwidth. The PA is specified to operate from 7 V to 24 V and can deliver up to  $\pm 1.9$  A of continuous output current over the specified junction temperature range of  $-40^{\circ}$ C to  $\pm 125^{\circ}$ C. The PA block is shown in Figure 12.

Figure 12. PA Block Equivalent Circuit

NSTRUMENTS

(1)

**EXAS**

SBOS669A-AUGUST 2013-REVISED DECEMBER 2013

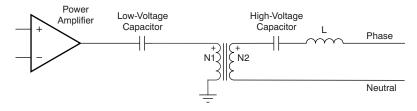

Connecting the PA in a typical power line communication (PLC) application requires few additional components. Figure 13 shows the typical connections to the PA block.

Figure 13. Typical Connections to the PA

The external capacitor ( $C_{IN}$ ) introduces a single-pole, high-pass characteristic to the PA transfer function. The  $C_{IN}$  and PA combination has a band-pass response because of the inherent low-pass transfer function from the PA. The value of the high-pass cutoff frequency is determined by  $C_{IN}$  reacting with the input resistance of the PA circuit, and can be determined by Equation 1:

$$C_{IN} = \frac{1}{2 \times \pi \times 18 \text{ k}\Omega \times f_{HP}}$$

where:

- C<sub>IN</sub> = external input capacitor and

- f<sub>HP</sub> = desired high-pass cutoff frequency.

For example, setting  $C_{IN}$  to 3.3 nF results in a high-pass cutoff frequency of 2.9 kHz. The voltage rating for  $C_{IN}$  should be determined to withstand operation up to the PA power-supply voltage.

When the transmitter is not in use, the output can be disabled and placed in a high-impedance state by following the procedure outlined in the *Power Amplifier Enable Sequence* section.

Refer to the *Initialization Sequence* and *Power Amplifier Enable Sequence* sections for details on the proper sequence when enabling the power amplifier.

AFE032

(2)

## www.ti.com

#### PA Current Limiting

The PA\_ISET pin (pin 26) provides a resistor-programmable output current limit for the PA block. Equation 2 determines the value of the external  $R_{SET}$  resistor attached to this pin.

$$I_{\text{LIM}} = \frac{1.2 \text{ V} \times 16.320 \text{ k}\Omega}{\text{R}_{\text{INT}} + \text{R}_{\text{SET}}}$$

where:

- R<sub>SET</sub> = the value of the external resistor connected between pin 26 and ground,

- R<sub>INT</sub> = the value of the internal resistor as programmed by the SPI interface in Table 18 (bits 4 and 5), and

- I<sub>lim</sub> = the value of the desired current limit for the PA.

R<sub>INT</sub> bit setting for bits 4 and 5 in Table 18 are listed in Table 1.

| BIT SETTING | R <sub>INT</sub> VALUE |  |  |  |  |  |

|-------------|------------------------|--|--|--|--|--|

| 00          | 17 kΩ                  |  |  |  |  |  |

| 01          | 11 kΩ                  |  |  |  |  |  |

| 10          | 8 kΩ                   |  |  |  |  |  |

| 11          | 1.2 kΩ                 |  |  |  |  |  |

| Table 1. R <sub>INT</sub> Bit Set | tings |

|-----------------------------------|-------|

|-----------------------------------|-------|

Note that there is a 30% tolerance on the I<sub>lim</sub> value given by Equation 2.

#### Tx Block

The Tx block consists of the Tx PGA and Tx filter.

The Tx PGA is a low-noise, high-performance, programmable gain amplifier. In DAC mode [where the DAC pin, pin 7, is a logic '1' and Tx enable (bit 4 in the REG\_RX/TX\_CTL register) is a logic '1'], the Tx PGA operates as the internal digital-to-analog converter (DAC) output buffer with programmable gain. The Tx PGA gain is programmed through the serial interface. The Tx PGA gain settings are 1.15 V/V, 2.3 V/V, 3.25 V/V, and 4.6 V/V. Gain is selectable via the TX\_PGA gain pins (bits 2 to 0 in the REG\_RX/TX\_CTL register).

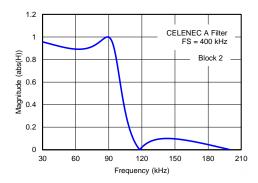

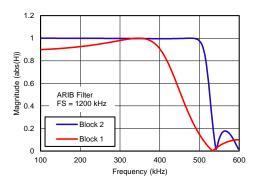

The Tx filter is a unity-gain, fourth-order, low-pass filter. The Tx filter cutoff frequency is selectable between the CENELEC (bands A, B, C, or D), ARIB, or FCC modes. The LPF band select bits (bits 6 to 4 in the REG\_HPF/LPF\_CFG register) determine the cutoff frequency.

When in DAC mode, the device accepts serial data from the microprocessor and writes that data to the internal DAC registers.

Proper connections for the Tx signal path for DAC mode operation are shown in Figure 14.

(1) For the capacitor value of  $C_{IN}$ ,  $f_{HP}$  is the desired lower cutoff frequency and 17 k $\Omega$  is the PA input resistance.

## Figure 14. Recommended Tx Signal Chain Connections

The capacitors listed in Figure 14 should be rated to withstand the full AVDD power-supply voltage for  $C_{DAC}$  and PA\_VS for  $C_{IN}$ .

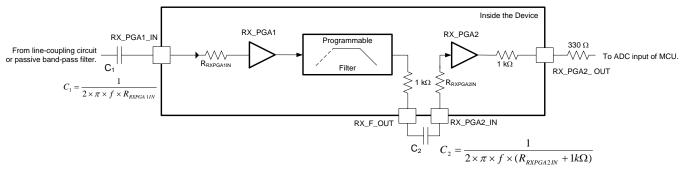

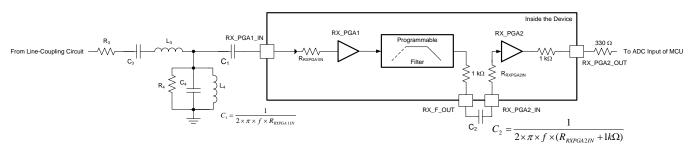

### **Rx Block**

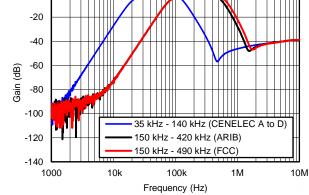

The Rx block consists of the Rx PGA1, Rx filter, and Rx PGA2. Both Rx PGA1 and Rx PGA2 are high-performance programmable gain amplifiers that can be configured through the SPI interface.

Rx PGA1 can operate as either an attenuator or in gain. The Rx PGA1 gain steps are 0.125 V/V, 0.25 V/V, 0.5 V/V, 1 V/V, 2 V/V, 4 V/V, 8 V/V, 16 V/V, and 32 V/V. Gains are selectable with the RX\_PGA1 gain bits (bits 7 to 4 in the REG\_RXPGA\_CFG register). Configuring the Rx PGA1 as an attenuator (at gains less than 1 V/V) is useful for applications where large interference signals are present within the signal band. Attenuating the large interference allows these signals to pass through the analog Rx signal chain without causing an overload; the interference signal can then be processed and removed within the microprocessor as necessary. Similarly, if a transmitter is located close to the receiver, gains less than 1 V/V may be needed.

The Rx PGA2 gain steps are 1 V/V, 4 V/V, and 16 V/V. Gains are selectable through the RX\_PGA2 gain bits (bits 3 to 1 in the REG\_RXPGA\_CFG register).

The Rx filter is a very low-noise, unity-gain, fourth-order, low-pass or band-pass filter. The Rx filter cutoff frequency is selectable between the CENELEC (bands A, B, C, or D), ARIB, or FCC modes. The LPF band select bits (bits 6 to 4 of the REG\_HPF/LPF\_REG register) determine the cutoff frequency for the LPF. The HPF band select bits (bits 1 and 2 of the REG\_HPF/LPF\_REG register) set up the cutoff frequency of the HPF.

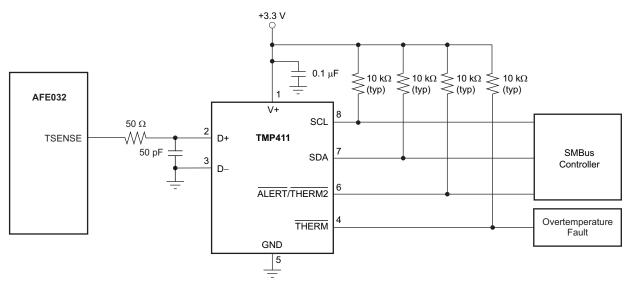

Recommended connections for the Rx signal chain are shown in Figure 15.

- (1) For capacitor value C<sub>1</sub>, f is the desired lower cutoff frequency and R<sub>RXPAG1IN</sub> is the input resistance of RX\_PGA1.

- (2) For capacitor value C<sub>2</sub>, f is the desired lower cutoff frequency and R<sub>RXPAG2IN</sub> is the input resistance of RX\_PGA2.

#### Figure 15. Recommended Connections for Rx Signal Chain

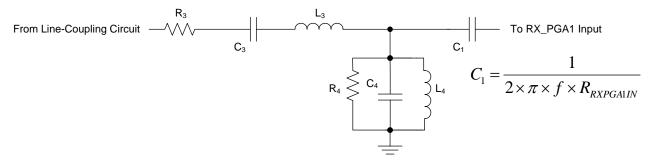

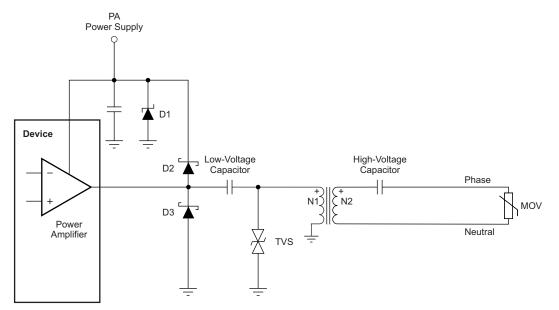

Figure 16 shows, a fourth-order, passive band-pass filter that is optional but recommended for applications with high performance needs. The external passive band-pass filter removes unwanted, out-of-band signals from the signal path, and it prevents such signals from reaching the active internal filters within the device.

(1) For capacitor value  $C_1$ , f is the desired lower cutoff frequency and  $R_{RXPGA1IN}$  is the input resistance of RX\_PGA1.

#### Figure 16. Passive Band-Pass Rx Filter

#### www.ti.com

The following steps can be used to quickly design the passive pass-band filter. (Note that these steps produce an approximate result.)

- 1. Choose the filter characteristic impedance,  $Z_C$ :

- For a –6-db passband attenuation:  $R_3 = R_4 = Z_C$ .

- For a 0-db passband attenuation:  $R_4 = Z_C$ ,  $R_3 = 10 \times Z_C$ .

- 2. Calculate values for  $C_3$ ,  $C_4$ ,  $L_3$ , and  $L_4$  using the following equations:

$$C_{3} = \frac{1}{2 \times \pi \times f_{3} \times Z_{C}}$$

$$C_{4} = \frac{1}{2 \times \pi \times f_{4} \times Z_{C}}$$

$$L_{3} = \frac{Z_{C}}{2 \times \pi \times f_{3}}$$

$$L_{4} = \frac{Z_{C}}{2 \times \pi \times f_{4}}$$

Table 2 and Table 3 show standard values for common applications.

# Table 2. Recommended Component Values for Fourth-Order Passive Band-Pass Filters (0-dB Pass-Band Attenuation)

| FREQUENCY BAND  | FREQUENCY<br>RANGE<br>(kHz) | CHARACTERISTIC<br>IMPEDANCE | R3    | R4<br>(kΩ) | C3<br>(nF) | C4<br>(nF) | L3<br>(µH) | L4<br>(µH) |

|-----------------|-----------------------------|-----------------------------|-------|------------|------------|------------|------------|------------|

| CENELEC A       | 35 to 95                    | 1 kΩ                        | 1 kΩ  | 10         | 4.7        | 1.5        | 1500       | 4700       |

| CENELEC B, C, D | 95 to 150                   | 1 kΩ                        | 1 kΩ  | 10         | 1.7        | 1          | 1200       | 1500       |

| SFSK            | 63 to 74                    | 1 kΩ                        | 1 kΩ  | 10         | 2.7        | 2.2        | 2200       | 2200       |

| FCC and ARIB    | 15 to 600                   | 100 Ω                       | 100 Ω | 1          | 100        | 2.2        | 27         | 1000       |

#### Table 3. Recommended Component Values for Fourth-Order Passive Band-Pass Filters (-6-dB Pass-Band Attenuation)

| FREQUENCY BAND  | FREQUENCY<br>RANGE<br>(kHz) | CHARACTERISTIC<br>IMPEDANCE | R3    | R4    | C3<br>(nF) | C4<br>(nF) | L3<br>(µH) | L4<br>(μΗ) |

|-----------------|-----------------------------|-----------------------------|-------|-------|------------|------------|------------|------------|

| CENELEC A       | 35 to 95                    | 1 kΩ                        | 1 kΩ  | 1 kΩ  | 4.7        | 1.5        | 1500       | 4700       |