## ANALOG DEVICES

## High Resolution 16-Bit D/A Converters

## AD DAC71/AD DAC72\*

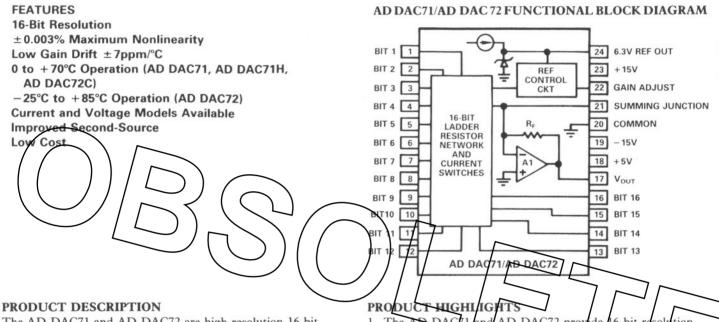

The AD DAC71 and AD DAC72 are high resolution 16-bit hybrid IC digital-to-analog converters including reference, scaling resistors and output amplifier (V models).

The devices offer outstanding accuracy, including maximum linearity error of 0.003% at room temperature and maximum gain drifts of 15ppm/°C (AD DAC71, AD DAC71H, AD DAC72C) and 7ppm/°C (AD DAC72). This performance is possible due to the innovative design, using proprietary monolithic D/A converter chips. Laser-trimmed thin film resistors provide the linearity and wide temperature range for guaranteed monotonicity.

The AD DAC71 and AD DAC72 digital inputs are TTL-compatible. Coding is complementary straight binary (CSB) for unipolar output versions and complementary offset binary (COB) for bipolar output versions.

All versions are packaged in a 24-pin metal DIP. The AD DAC71, AD DAC71H and AD DAC72C are specified for operation from 0 to  $+70^{\circ}$ C, and the AD DAC72 is specified from  $-25^{\circ}$ C to  $+85^{\circ}$ C. The AD DAC71H, AD DAC72 and AD DAC72C are supplied in hermetically-sealed packages.

The AD DAC71 and AD DAC72 are intended to serve as improved second sources to DAC71 and DAC72 devices from other manufacturers.

- 1. The AD DAC/1 and AD DAC72 provide 16-bit resolution with 0.003% linearity error.

- 2. The proprietary chips used in the hybrid design provide excellent stability over temperature and improved reliability.

- Unipolar and bipolar current and voltage output versions are available to fill a wide range of system requirements.

- The AD DAC71 and AD DAC72 are improved second source replacements for DAC71 and DAC72 devices from other manufacturers.

1

# **SPECIFICATIONS** (@ $T_A = +25^{\circ}C$ , rated power supplies unless otherwise noted)

| MODEL                                                                                                                                                                                                                                                | AD DA<br>MIN                    | TYP                                        | MAX                                                                                                     | MIN          | AD DAC7.<br>TYP                            | 2C<br>MAX                                                                                                | MIN        | AD DAC7                                    | 2<br>MAX                                                                                                    | UNITS                                                                             |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------|------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|

| DIGITAL INPUTS<br>Resolution<br>Logic Levels (TTL-Compatible) <sup>1</sup><br>Logical "1"<br>Logical "0"                                                                                                                                             | +2.4                            | 16                                         | + 5.5                                                                                                   | + 2.4<br>+ 0 | 16                                         | + 5.5<br>+ 0.4                                                                                           | + 2.4      | 16<br>•                                    | + 5.5                                                                                                       | Bits<br>V dc                                                                      |        |

| ACCURACY <sup>2</sup><br>Linearity Error at 25°C<br>Gain Error <sup>4</sup> , Voltage<br>Current<br>Offset Error <sup>4</sup> , Voltage, Unipolar<br>Voltage, Bipolar<br>Current, Unipolar<br>Current, Bipolar<br>Monotonicity Temp. Range (14-Bits) | 0                               | $\pm 0.01$<br>$\pm 0.05$<br>$\pm 0.1$      | $\pm 0.003$<br>$\pm 0.1$<br>$\pm 0.25$<br>$\pm 2.0$<br>$\pm 5.0$<br>$\pm 1.0$<br>$\pm 5.0$<br>$\pm 5.0$ | 0            | $\pm 0.05 \pm 0.05 \pm 0.1$                | $\pm 0.003$<br>$\pm 0.15$<br>$\pm 0.25$<br>$\pm 2.0$<br>$\pm 10.0$<br>$\pm 1.0$<br>$\pm 5.0$<br>$\pm 50$ | + 0        | $\pm 0.05 \pm 0.05 \pm 0.1$                | +0.4<br>$\pm 0.003$<br>$\pm 0.15$<br>$\pm 0.25$<br>$\pm 2.0$<br>$\pm 10.0$<br>$\pm 1.0$<br>$\pm 5.0$<br>+70 | V dc<br>% of FSR <sup>3</sup><br>%<br>mV<br>mV<br>μA<br>μA<br>°C                  |        |

| DRIFT (Over Specified Temp. Range)<br>Total Bipolar Drift (includes gain, offset,<br>and linearity drift)<br>Voltage<br>T <sub>min</sub> to 25°C<br>25°C to T <sub>max</sub><br>Current<br>T <sub>min</sub> to T <sub>max</sub>                      |                                 | ±7<br>±7<br>±15                            | ± 15<br>± 15                                                                                            |              | ± 7<br>± 7<br>± 15                         | ± 15<br>± 15                                                                                             |            | ± 5<br>± 5<br>± 10                         | ± 19<br>± 11                                                                                                | ppm of FSR/°C<br>ppm of FSR/°C                                                    | а<br>А |

| Voltage, Uniplar<br>Tmin to 25°C<br>+ 25°C to Tmax<br>Voltage, Biglolar                                                                                                                                                                              |                                 | 215                                        | ± 0.083<br>± 0.083                                                                                      |              | 115                                        | ± 0.083<br>± 0.083                                                                                       |            | 10                                         | ± 0.100<br>± 0.072                                                                                          | ppm of FSR/°C<br>% of FSR<br>% of FSR                                             |        |

| T <sub>min</sub> to 425°C<br>+ 25°C to T <sub>ma</sub><br>Success, Unity flar (T <sub>min</sub> to T <sub>max</sub> )<br>Bigener (T <sub>min</sub> to T <sub>max</sub> )                                                                             |                                 | $\left\langle \right\rangle$               | $\pm 0.071$<br>$\pm 0.01$<br>$\pm 0.23$<br>$\pm 0.23$                                                   | $\zeta$      | $\overline{}$                              | $\pm 0.071$<br>$\pm 0.071$<br>$\pm 0.23$<br>$\pm 0.23$                                                   |            |                                            | $\pm 0.100$<br>$\pm 0.072$<br>$\pm 0.24$<br>$\pm 0.24$                                                      | % of FSR<br>% of FSR<br>% of FSR<br>% of FSR                                      |        |

| TEMPERATURE OEFFICIENTS<br>Gain<br>Voltage<br>T <sub>min</sub> to + 25°C<br>+ 25°C to T <sub>max</sub><br>Current                                                                                                                                    | $\left[ \left[ \right] \right]$ | ±15                                        | ±15<br>±15                                                                                              |              | ± 15                                       | )<br>± 15<br>± 15                                                                                        | /          |                                            | ±15<br>±7                                                                                                   | ppm of FSR/ C                                                                     |        |

| Offset<br>Voltage, Unipolar<br>Bipolar<br>Current, Unipolar<br>Bipolar<br>Differential Linearity over Temperature<br>Linearity Error over Temperature                                                                                                |                                 | ± 1<br>± 15                                | $\begin{array}{c} \pm 2 \\ \pm 10 \\ \pm 1 \\ \pm 2 \\ \pm 2 \end{array}$                               |              | ± 1<br>± 15                                | $\pm 10$<br>$\pm 1$<br>$\pm 2$<br>$\pm 2$                                                                |            |                                            | ± 2<br>± 8<br>± 1<br>± 1<br>± 1                                                                             | ppm of FSR/°C<br>ppm of FSR/°C<br>ppm of FSR/°C<br>ppm of FSR/°C<br>ppm of FSR/°C |        |

| SETTLING TIME<br>Voltage Models (to ± 0.003% of FSR)<br>Output: 20V Step<br>ILSB Step <sup>6</sup><br>Slew Rate<br>Current Models (to ± 0.003% of FSR) <sup>7</sup>                                                                                  |                                 | 5<br>3<br>20                               | 10<br>5                                                                                                 |              | 5<br>3<br>20                               | 10<br>5                                                                                                  | 01         | 5<br>3<br>20                               | 10<br>5                                                                                                     | ppm of FSR-C<br>μs<br>μs<br>V/μs                                                  |        |

| Output: 2mA step 10Ω to 100Ω Load<br>1kΩ Load<br>Switching Transient<br>ANALOG OUTPUT                                                                                                                                                                |                                 | 500                                        | 1<br>3                                                                                                  |              | 500                                        | 1<br>3                                                                                                   |            | 500                                        | 1<br>3                                                                                                      | μs<br>μs<br>mV                                                                    |        |

| Voltage Models<br>RangesCSB<br>COB<br>Output Current<br>Output Impedance (dc)<br>Short Circuit Duration<br>Current Models                                                                                                                            | ± 5<br>Inde                     | 0 to + 10<br>± 10<br>0.05<br>efinite to Co | mmon                                                                                                    | ± 5<br>Inde  | 0 to + 10<br>± 10<br>0.05<br>finite to Com | ітол                                                                                                     | ±5<br>Inde | 0 to + 10<br>± 10<br>0.05<br>finite to Com | imon                                                                                                        | V<br>V<br>mA<br>Ω                                                                 |        |

| Ranges-CSB<br>COB<br>Output Impedance-Unipolar<br>Bipolar                                                                                                                                                                                            |                                 | 0 to - 2<br>± 1<br>6.0<br>3.0              |                                                                                                         |              | 0 to 2<br>±1<br>6.0<br>3.0                 |                                                                                                          |            | 0 to - 2<br>± 1<br>6.0<br>3.0              |                                                                                                             | mA<br>mA<br>kΩ<br>kΩ                                                              |        |

| Compliance<br>NTERNAL REFERENCE VOLTAGE<br>Maximum External Current <sup>8</sup><br>Temp. Coeff. of Drift                                                                                                                                            | 6.0                             | 6.3                                        | + 10<br>6.6<br>± 3<br>± 10                                                                              | 1.5<br>6.0   | 6.3                                        | + 10<br>6.6<br>+ 3<br>+ 10                                                                               | 6.0        | 6.3                                        | + 10<br>6.6<br>+ 3<br>+ 5                                                                                   | V<br>V<br>mA<br>ppm/°C                                                            |        |

| OWER SUPPLY SENSITIVITY<br>Unipolar Offset<br>± 15V dc<br>+ 5V dc<br>Bipolar Offset<br>± 15V dc                                                                                                                                                      |                                 | ± 0.0001<br>± 0.0001<br>± 0.0004           |                                                                                                         |              | ± 0.0001<br>± 0.0001                       |                                                                                                          |            | ± 0.0001<br>± 0.0001                       |                                                                                                             | % of FSR/% Vs<br>% of FSR/% Vs                                                    |        |

| + SV dc                                                                                                                                                                                                                                              |                                 | ± 0.0004<br>± 0.0001                       |                                                                                                         |              | ± 0.0004<br>± 0.0001                       |                                                                                                          |            | ± 0.0004<br>± 0.0001                       |                                                                                                             | % of FSR/% V <sub>S</sub><br>% of FSR/% V <sub>S</sub>                            |        |

| MODEL                                                                  | AD DAG<br>MIN | C71/AD D<br>TYP     | AC71H<br>MAX | A<br>MIN | D DAC72<br>TYP      | 2C<br>MAX | MIN A   | D DAC7.<br>TYP      | 2<br>MAX | UNITS                                                  |

|------------------------------------------------------------------------|---------------|---------------------|--------------|----------|---------------------|-----------|---------|---------------------|----------|--------------------------------------------------------|

| POWER SUPPLY SENSITIVITY<br>(Continued)<br>Gain<br>± 15V dc<br>+ 5V dc |               | ± 0.001<br>± 0.0005 |              |          | + 0.001<br>± 0.0005 |           |         | ± 0,001<br>± 0.0005 | 4        | % of FSR/% V <sub>S</sub><br>% of FSR/% V <sub>S</sub> |

| POWER SUPPLY REQUIREMENTS                                              |               |                     |              |          |                     |           |         |                     |          |                                                        |

| DAC71/72                                                               | ± 14.5,       | ±15.0,              | • 15.5,      | : 14.5,  | ± 15.0,             | : 15.5,   | ± 14.5, | ± 15.0,             | : 15.5,  |                                                        |

|                                                                        | + 4.75        | + 5.0               | + 5.25       | + 4.75   | + 5.0               | + 5.25    | + 4.75  | + 5.0               | + 5.25   | V dc                                                   |

| Supply Drain, +15V dc (no load)                                        |               | 10                  | 20           | 1        | 10                  | 20        |         | 10                  | 20       | mA                                                     |

| - 15V dc (no load)                                                     |               | 30                  | 55           |          | 30                  | 55        |         | 30                  | 55       | mA                                                     |

| + 5V dc (logic supply)                                                 |               | 10                  | 20           |          | 10                  | 20        |         | 10                  | 20       | mA                                                     |

| TEMPERATURE RANGE                                                      |               |                     |              |          |                     |           |         |                     |          | 1.000 0000                                             |

| Specification                                                          | 0             |                     | + 70         | 0        |                     | + 70      | - 25    |                     | + 85     | °C                                                     |

| Operating (double above Drift Specs)                                   | - 25          |                     | + 85         | - 25     |                     | + 85      | 55      |                     | + 100    | °C                                                     |

| Storage                                                                | - 55          |                     | + 100        | - 55     |                     | + 100     | - 55    |                     | + 110    | °C                                                     |

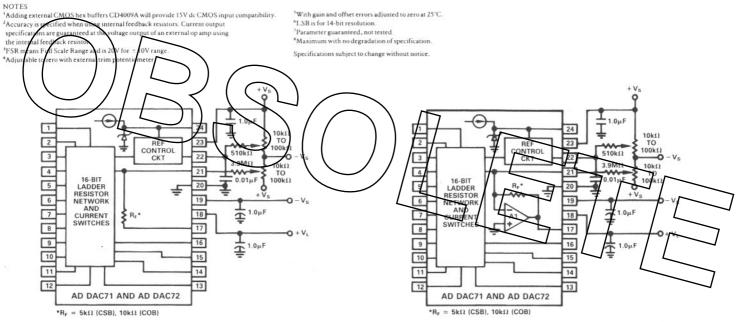

Figure 1. External Adjustment and Voltage Supply Connection Diagram, Current Model

Figure 2. External Adjustment and Voltage Supply Connection Diagram, Voltage Model

#### **ORDERING GUIDE**

| Model Output    |         | Input Code            | Temperature<br>Range | Seal     | Package<br>Option* |

|-----------------|---------|-----------------------|----------------------|----------|--------------------|

| AD DAC71–COB–I  | Current | Comp. Offset Binary   | 0 to + 70°C          | Polymer  | DH-24D             |

| AD DAC71–CSB–I  | Current | Comp. Straight Binary | 0 to + 70°C          | Polymer  | DH-24D             |

| AD DAC71H–COB–I | Current | Comp. Offset Binary   | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC71H–CSB–I | Current | Comp. Straight Binary | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC72C–COB–I | Current | Comp. Offset Binary   | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC72C–CSB–I | Current | Comp. Straight Binary | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC72–COB–I  | Current | Comp. Offset Binary   | - 25°C to + 85°C     | Hermetic | DH-24D             |

| AD DAC72–CSB–I  | Current | Comp. Straight Binary | - 25°C to + 85°C     | Hermetic | DH-24D             |

| AD DAC71–COB–V  | Voltage | Comp. Offset Binary   | 0 to + 70°C          | Polymer  | DH-24D             |

| AD DAC71–CSB–V  | Voltage | Comp. Straight Binary | 0 to + 70°C          | Polymer  | DH-24D             |

| AD DAC71H–COB–V | Voltage | Comp. Offset Binary   | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC71H–CSB–V | Voltage | Comp. Straight Binary | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC72C–COB–V | Voltage | Comp. Offset Binary   | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC72C–CSB–V | Voltage | Comp. Straight Binary | 0 to + 70°C          | Hermetic | DH-24D             |

| AD DAC72–COB–V  | Voltage | Comp. Offset Binary   | - 25°C to + 85°C     | Hermetic | DH-24D             |

| AD DAC72–CSB–V  | Voltage | Comp. Straight Binary | - 25°C to + 85°C     | Hermetic | DH-24D             |

\*See Section 13 for package outline information.

2

### PRESERVING THE ACCURACY OF THE AD DAC/1 AND AD DAC72

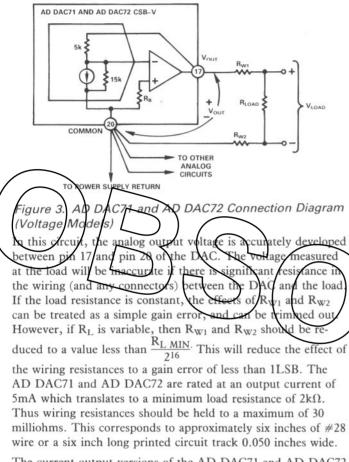

A great deal of care must be exercised when using high resolution converters such as the AD DAC71 and AD DAC72. Since one least significant bit of a 16-bit converter (LSB) represents an analog voltage of only 153 microvolts out of a 10V scale, normally negligible error sources become significant. Series resistances of connectors and wiring can be major contributors, as can thermocouple effects. Figure 3 illustrates the connections for voltage output versions of the AD DAC71 and AD DAC72.

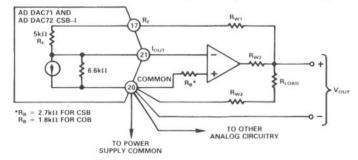

The current output versions of the AD DAC71 and AD DAC72 use an external operational amplifier to convert the output current to an output voltage. The recommended configuration is shown in Figure 4. Notice that this configuration permits the voltage at

*Figure 4. Connections for AD DAC71 and AD DAC72 Current Output Versions*

the load to the sensed remotely. The resistance  $(R_{W1})$  of the lead connecting the load to the internal feedback resistor introduces a gain error equal to  $\frac{R_{W1}}{R_{LOAD}}$ , independent of  $R_{LOAD}$ and  $R_{W2}$ . The error contributed by  $R_{W3}$  depends upon where the output is measured. If the output is measured between the top of  $R_{LOAD}$  and pin 20 of the DAC, no error results since  $R_{W3}$  effectively becomes part of the load resistance.

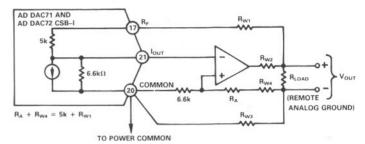

In applications where  $R_{\rm W3}$  is large or large currents flow in  $R_{\rm W3},$  it is necessary to use remote sensing as shown in Figure 5.

This circuit uses the output amplifier as a subtractor stage. Any spurious voltage developed across  $R_{\rm W3}$  becomes a common mode voltage and its error contribution is reduced by the common mode rejection of the op amp.

In the circuits of both Figure 4 and Figure 5,  $R_{W2}$ 's effect is negligible since it is inside the loop of the amplifier. If current boosting is required in order to drive heavy loads, a suitable booster stage can be inserted between the amplifier's output and the load. Since the loop is closed from the load end, offsets and other errors induced by the booster are eliminated.

It important to minimize thermodouple effects in circuitry is also using the AD/DAC71 and AD DAC72. Recalling that 1LSB of a 16 bit, 10 volt scale converter is only 153 microvolts, a stray uncompensated thermocouple can introduce several LSBs offset in response to minor changes in ambient temperature. Any part of a circuit which includes a junction between two dissimilar metals forms a thermocouple. Such junctions include connectors, sockets, and any soldered connections. The solution to thermocouple errors is to insure that every junction is cancelled by an identical, but opposite, junction at the same temperature. While this is often automatically accomplished (for example, in a connector carrying both signal and return leads), careful attention should be given to the physical layout of circuits using the AD DAC71 and AD DAC72.

Another source of signal degradation in high-resolution converter circuits is magnetically-coupled interference from stray fields. Signal and return leads should be arranged in a way which minimizes both length and the total cross-section area of the loop. Of course, high resolution circuits should be located as far as possible from any sources of electromagnetic interference, including power transformers, digital logic and electromechanical devices.

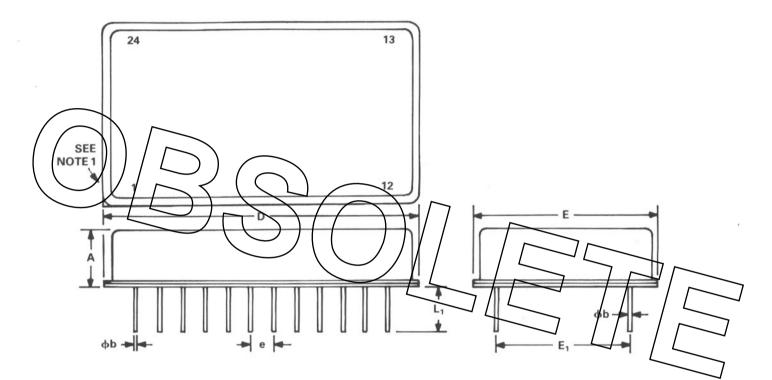

|                | INCH      | IES   | MILLIM |       |       |

|----------------|-----------|-------|--------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN    | MAX   | NOTES |

| A              |           | 0.250 |        | 6.35  |       |

| φb             | 0.016     | 0.020 | 0.41   | 0.51  |       |

| D              |           | 1.385 |        | 35.18 |       |

| E              |           | 0.810 |        | 20.57 |       |

| E1             | 0.590     | 0.610 | 15.00  | 15.50 | 3     |

| е              | 0.100 BSC |       | 2.54   | 2     |       |

| L <sub>1</sub> | 0.140     | 0.210 | 3.56   | 5.33  |       |

- NOTES 1. Index area; a colored bead or identification mark is located at lead one.

- 2. The basic pin spacing is 0.100" (2.54mm) between centerlines.

- 3.  $E_1$  shall be measured at the centerline of the leads.