# DP8340/NS32440 IBM 3270 Protocol Transmitter/Encoder

## **General Description**

The DP8340/NS32440 generates a complete encoding of parallel data for high speed serial transmission which conforms to the protocol as defined by the IBM 3270 information display system standard. The DP8340/NS32440 converts parallel input data into a serial data stream. Although the IBM standard covers biphase serial data transmission over a coax line, the DP8340/NS32440 also adapts to general high speed serial data transmission over other than coax lines, at frequencies either higher or lower than the IBM standard.

The DP8340/NS32440 and its complementary chip, the DP8341 (receiver/decoder) have been designed to provide maximum flexibility in system designs. The separation of the transmitter/receiver functions provides convenient addition of more receivers at one end of a biphase line without the need of unused transmitters. This is specifically advantageous in control units where typical biphase data is multiplexed over many biphase lines and the number of receivers generally exceeds the number of transmitters.

### **Features**

- Ten bits per data byte transmission

- Single-byte or multi-byte transmission

- Internal parity generation (even or odd)

- Internal crystal controlled oscillator used for the generation of all required chip timing frequencies

- Clock output directly drives receiver (DP8341) clock input

- Input data holding register

- Automatic clear status response feature

- Line drivers at data outputs provide easy interface to biphase coax line or general transmission lines

- < 2 ns driver output skew</p>

- Bipolar technology provides TTL input/output compatibility

- Data outputs power up/down glitch free

- Internal power up clear and reset

- Single +5V power supply

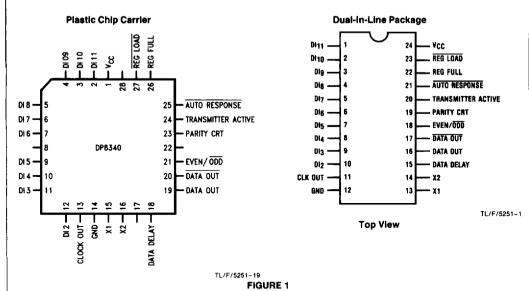

## **Connection Diagrams**

Order Number DP8340/NS32440 J, N or V See NS Package Number J24A, N24A or V28A

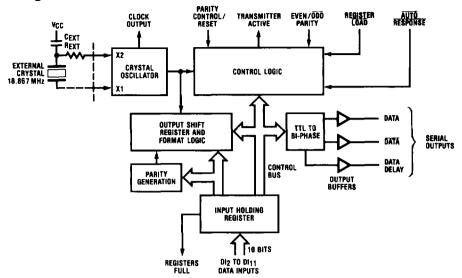

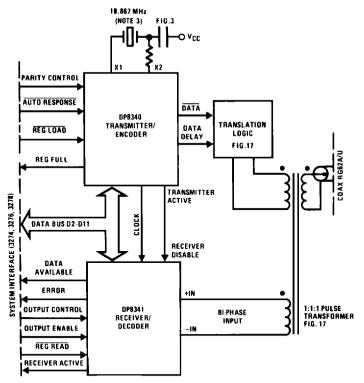

## **Block Diagram**

FIGURE 2. DP8340/NS32440 Serial Bi-Phase Transmitter/Encoder Block Diagram

TI /F/5251-2

### **Functional Description**

Figure 2 is a block diagram of the DP8340/NS32440 biphase Transmitter/Encoder. The transmitter/encoder contains a crsytal oscillator whose input is a crsytal with a frequency eight (8) times the data rate. A Clock Output is provided to drive the DP8341 receiver/decoder Clock Input and other system components at the oscillator frequency. Additionally, the oscillator drives the control logic and output shift register/format logic blocks.

Data is parallel loaded from the sytem data bus to the transmitter/encoder's input holding register. This data is in turn loaded by the transmitter/encoder to its output shift register if this register was empty at the time of the load. During this load, message formatting and parity are generated. The formatted message is then shifted out at the bit rate frequency to the TTL to biphase block which generates the proper data bit formatting. The three data outputs, DATA, DATA, and DATA DELAY provide for flexible interface to the coax line with a minimum of external components.

The Control Logic block interfaces to all blocks to insure proper chip operation and sequencing. It controls the type of parity generation through the Even/Odd Parity input. An additional feature provided by the transmitter/encoder is generation of odd parity and placement in bit 10 position

while still maintaining even or odd parity in the bit 12 position. This is the format of data word bytes and other commands in the 3270 Standard. The Parity Control input is the pin which controls when this operation is in effect.

Another feature of the transmitter/encoder is the internal TT/AR (Transmission Turnaround/Auto Response) capability. After each Write type message from the control unit in the 3270 Standard, the receiving unit must respond with clean status (bits 2 through 11). With the transmitter/encoder, this function is accomplished simply by forcing the Auto-Response input to the Logic "0" state.

Operation of the transmitter/encoder is automatic. After the first data byte is loaded, the Transmitter Active output is set and the transmitter/encoder immediately formats the input data and serially shifts it out its data outputs. If the message is a multi-byte message, the internal format logic will modify the message data format for multibyte as long as the next byte is loaded to the input holding register before the last data bit of the previous data byte is transferred out of the internal output shift register. After all data is shifted out of the transmitter/encoder the Transmitter Active output will return to the inactive state.

## **Detailed Pin/Functional Description**

#### Crystal Inputs X1 and X2

The oscillator is controlled by an external, parallel resonant crystal connected between the X1 and X2 pins. Normally, a fundamental mode crystal is used to determine the operating frequency of the osicillator; however, overtone mode crystals may be used.

#### Crystal Specifications (Parallel Resonant)

Type

AT-cut crystal

Tolerance

0.005% at 25°C

Stability

0.01% from 0°C to +70°C

Resonance

Fundamental (Parallel)

Maximum Series Resistance

Dependent on Frequency (For 18.867 MHz, 50Ω)

Load Capacitance

15 pF

TO PIN X2

PIN (14)

TO PIN X2

PIN (13)

R

C

C

TO PIN X2

PIN (13)

R

C

C

TO PIN X2

PIN (13)

R

C

C

TO PIN X2

10 MHz to 500Ω

20 MHz ± 10%

20 MHz

120Ω

± 10%

15 pF

TL/F/5251-3

FIGURE 3. Connection Diagram

If the DP8340/NS32440 transmitter is clocked by a system (clock crystal oscillator not used), pin 13 (X1 input) should be clocked directly using a Schottky series (74S) circuit. Pin 14 (X2 input) may be left open. The clocking frequency must be set at eight times the data bit rate. Maximum input frequency is 28 MHz. For the IBM 3270 Interface, this frequency is 18.867 MHz. At this frequency, the serial bit rate will be 2.358 Mbits/sec.

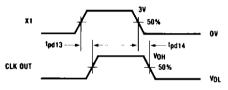

#### Clock Output

The Clock Output is a buffered output derived directly from the crystal oscillator block and clocks at the oscillator frequency. It is designed to directly drvie the DP8341 receiver/ decoder Clock Input as well as other system components.

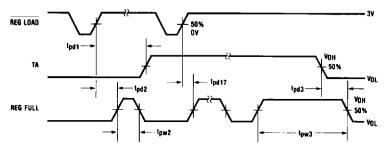

#### Registers Full

This output is used as a flag by the external operating system. A logic "1" (active state) on this output indicates that both the internal output shift register and the input holding register contain active data. No additional data should be loaded until this output returns to the logic "0" state (inactive state).

#### **Transmitter Active**

This output will be in the logic "1" state while the transmitter/encoder is about to transmit or in the process of transmitting data. Otherwise, it will assume the logic "0" state indicating no data presently in either the input holding or output shift registers.

#### Register Load

The Register Load input is used to load data from the Data Inputs to the input holding register. The loading function

is edge sensitive, the data present during the logic "0" state of this input is loaded, and the input data must be valid before the logic "0" to logic "1" transition. It is after this transition that the transmitter/encoder begins formatting of data for serial transmission.

#### Auto Response (TT/AR)

This input provides for automatic clear data transmission (all bits in logic "0") without the need of loading all zero's. When a logic "0" is forced on this input the transmitter/encoder immediately responds with transmission of "clean status". This function is necessary after the completion of each write type command and in other functions in the 3270 specification. In the logic "1" state the transmitter/encoder transmits data entered on the Data Inputs.

#### Even/Odd Parity

This input sets the internal logic of the DP8340/NS32440 transmitter/encoder to generate either even or odd parity for the data byte in the bit 12 position. When this pin is in the logic "0" state odd parity is generated. In the logic "1" state even parity is generated. This feature is useful when the control unit is performing a loop back check and at the same time the controller wishes to verify proper data transmission with its receiver/decoder.

#### Parity Control/Reset

Depending on the type of message transmitted, it is at times necessary in the IBM 3270 specification to generate an additional parity bit in the bit 10 position. The bit generated is odd parity on the previous eight (8) bits of data. When the Parity Control input is in the logic "1" state the data entered at the Data Bit 10 position is placed in the transmitted word. With the Parity Control input in the logic "0" state the Data Bit 10 input is ignored and odd parity on the previous data bits is placed in the normal bit 10 position while overall word parity (bit 12) is even or odd (controlled by Even/Odd Parity input). This eliminates the need for external logic to generate the parity on the data bits.

**Truth Table**

| Parity Control Input | Transmitted Data Bit 10       |

|----------------------|-------------------------------|

| Logic "1"            | Data entered on Data Input 10 |

| Logic "0"            | Odd Parity on 8-bit data byte |

When this input is driven to a voltage that exceeds the power supply level (9V to 13V) the transmitter/encoder is reset.

#### Serial Outputs-DATA, DATA, and DATA DELAY

These three output pins provide for convenient application of data to the biphase Coax line (see *Figure 15* for application). The Data outputs are a direct bit representation of the biphase data while the DATA DELAY output provides the necessary increment to clearly define the four (4) DC levels of the pulse. The DATA and DATA outputs add flexibility to the DP8340/NS32440 transmitter/encoder for use in high speed differential line driving applications.

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Lead Temperature (Soldering, 10 sec.) 300°C

Maximum Power Dissipation @25°C\*

Cavity Package

Dual-In-Line Package

Plastic Chip Carrier

2237 mW 2500 mW 1720 mw

\*Derate cavity package 14.9 mW/\*C above 25°C; derate dual-in-line package 20 mW/\*C above 25°C; derate PCC package 13.8 mW/\*C above 25°C.

## **Operating Conditions**

| -                                  | Min  | Max  | Units |

|------------------------------------|------|------|-------|

| Supply Voltage, (V <sub>CC</sub> ) | 4.75 | 5.25 | ٧     |

| Ambient Temperature, TA            | 0    | +70  | ۰c    |

## Electrical Characteristics (Notes 2 and 3)

| Symbol           | Parameter                                                                              | Conditions                                         | Min | Тур  | Max  | Unite |

|------------------|----------------------------------------------------------------------------------------|----------------------------------------------------|-----|------|------|-------|

| ViH              | Logic "1" Input Voltage<br>(All Inputs Except X1 and X2)                               |                                                    | 2.0 |      |      | ٧     |

| V <sub>IL</sub>  | Logic "0" Input Voltage<br>(All Inputs Except X1 and X2)                               |                                                    |     |      | 0.8  | >     |

| VCLAMP           | Input Clamp Voltage<br>(Ali Inputs Except X1 and X2)                                   | $i_{IN} = -12  \text{mA}$                          |     | -0.8 | -1.2 | >     |

| hн               | Logic "1" Input Current<br>Register Load Input                                         | V <sub>CC</sub> = 5.25V<br>V <sub>IN</sub> = 5.25V |     | 0.3  | 120  | μΑ    |

|                  | All Others Except X1 and X2                                                            |                                                    |     | 0.1  | 40   | μΑ    |

| l <sub>IL</sub>  | Logic "0" Input Current<br>Register Load Input                                         | $V_{CC} = 5.25V$ $V_{IN} = 0.5V$                   |     | - 15 | -300 | μА    |

|                  | All Inputs Except X1 and X2                                                            |                                                    |     | -5   | -100 | μΑ    |

| V <sub>OH1</sub> | Logic "1" All Outputs Except CLK OUT,<br>DATA, DATA, and DATA DELAY                    | I <sub>OH</sub> = -100 μA                          | 3.2 | 3.9  |      | ٧     |

|                  |                                                                                        | I <sub>OH</sub> = -1 mA                            | 2.5 | 3.4  |      | ٧     |

| V <sub>OH2</sub> | Logic "1" for CKL OUT, DATA, DATA and DATA DELAY Outputs                               | I <sub>OH</sub> = -10 mA                           | 2.6 | 3.0  |      | ٧     |

| V <sub>QL1</sub> | Logic "0" All Outputs Except CLK OUT,<br>DATA, DATA and DATA DELAY Outputs             | I <sub>OL</sub> = 5 mA                             |     | 0.35 | 0.5  | v     |

| V <sub>OL2</sub> | Logic "0" for CLK OUT, DATA,  DATA and DATA DELAY Outputs                              | I <sub>OL</sub> = 20 mA                            |     | 0.4  | 0.6  | v     |

| los <sub>1</sub> | Short Circuit Current for All Outputs<br>Except CLK OUT, DATA, DATA, and<br>DATA DELAY | V <sub>OUT</sub> = 0V<br>(Note 4)                  | -10 | -30  | -100 | mA    |

| l <sub>OS2</sub> | Short Circuit Current for DATA, DATA, and DATA DELAY Outputs                           | V <sub>OUT</sub> = 0V<br>(Note 4)                  | -50 | -140 | -350 | mA    |

| los3             | Short Circuit Current for CLK OUT                                                      | (Note 4)                                           | -30 | -90  | -200 | mA    |

| lcc              | Power Supply Current                                                                   | V <sub>CC</sub> = 5.25V                            |     | 170  | 250  | mA    |

## Timing Characteristics Oscillator Frequency = 18.867 MHz (Notes 2 and 3)

| Symbol           | Parameter                                                      | Conditions                   | Min | Тур | Max | Unita |

|------------------|----------------------------------------------------------------|------------------------------|-----|-----|-----|-------|

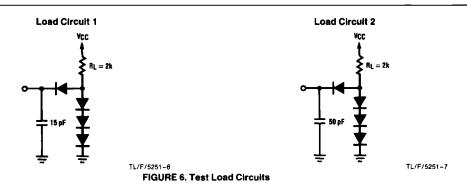

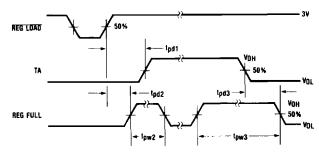

| <sup>t</sup> pd1 | REG LOAD to Transmitter Active (T <sub>A</sub> ) Positive Edge | Load Circuit 1<br>Figure 7   |     | 60  | 90  | ns    |

| t <sub>pd2</sub> | REG LOAD to REG Full; Positive Edge                            | Load Circuit 1 Figure 7      |     | 45  | 75  | ns    |

| t <sub>pd3</sub> | Register Full to TA; Negative Edge                             | Load Circuit 1 Figure 7      |     | 40  | 70  | ns    |

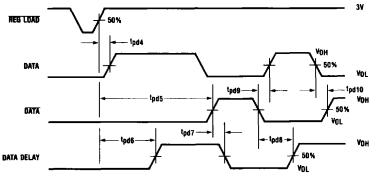

| t <sub>pd4</sub> | Positive Edge of REG LOAD to Positive Edge of DATA             | Load Circuits 1 & 2 Figure 9 |     | 50  | 80  | ns    |

## Timing Characteristics Oscillator Frequency = 18.867 MHz (Notes 2 and 3) (Continued)

| Symbol                                  | Parameter                                                                              | Conditions                                | Min | Тур        | Max         | Units   |

|-----------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------|-----|------------|-------------|---------|

| t <sub>pd5</sub>                        | REG LOAD to DATA; Positive Edge                                                        | Load Circuits 1 & 2<br>Figure 9, (Note 6) |     | 380        | 475         | ns      |

| t <sub>pd6</sub>                        | REG LOAD to DATA DELAY; Positive Edge                                                  | Load Circuits 1 & 2<br>Figure 9, (Note 6) |     | 160        | 250         | ns      |

| t <sub>pd7</sub>                        | Positive Edge of DATA to Negative Edge of DATA DELAY                                   | Load Circuit 2<br>Figure 9, (Note 6)      |     | 100        | 115         | ns      |

| t <sub>pd8</sub>                        | Positive Edge of DATA DELAY to Negative Edge of DATA                                   | Load Circuit 2<br>Figure 9, (Note 6)      |     | 110        | 125         | ns      |

| t <sub>pd9</sub> ,<br>t <sub>pd10</sub> | Skew between DATA and DATA                                                             | Load Circuit 2<br>Figure 9                |     | 2          | 6           | ns      |

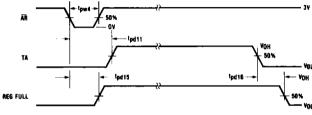

| t <sub>pd11</sub>                       | Negative Edge of Auto Response to Positive Edge of TA                                  | Load Circuit 1<br>Figure 10               |     | 70         | 110         | ns      |

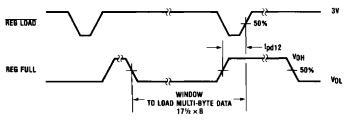

| t <sub>pd12</sub>                       | Maximum Time Delay to Load Second Byte after Positive Edge of REG FULL                 | Load Circuit 1<br>Figure 8, (Note 6)      |     |            | 4 × T -50   | ns      |

| t <sub>pd13</sub>                       | X1 to CLK OUT; Positive Edge                                                           | Load Circuit 2<br>Figure 13               |     | 21         | 30          | ns      |

| t <sub>pd14</sub>                       | X1 to CLK OUT; Negative Edge                                                           | Load Circuit 2<br>Figure 13               |     | 23         | 33          | ns      |

| t <sub>pd15</sub>                       | Negative Edge of AR to Positive<br>Edge of REG FULL                                    | Load Circuit 1<br>Figure 10               |     | 45         | 75          | ns      |

| <sup>t</sup> pd16                       | Skew between TA and REG FULL during<br>Auto Response                                   | Load Circuit 1<br>Figure 10               |     | 50         | 80          | ns      |

| t <sub>pd17</sub>                       | REG LOAD to REG FULL; Positive Edge for Second Byte                                    | Load Circuit 1<br>Figure 14               |     | 45         | 75          | ns      |

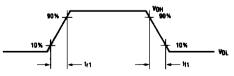

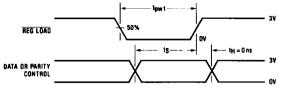

| t <sub>pw1</sub>                        | REG LOAD Pulse Width                                                                   | Figure 12                                 | 40  |            |             | ns      |

| t <sub>pw2</sub>                        | First REG FULL Pulse Width (Note 5)                                                    | Load Circuit 1<br>Figure 7, (Note 6)      |     | 8 × T + 60 | 8 × T + 100 | ns      |

| t <sub>pw3</sub>                        | REG FULL Pulse Width prior to Ending Sequence (Note 5)                                 | Load Circuit 1,<br>Figure 7, (Note 6)     |     | 5 × B      |             | ns      |

| t <sub>pw4</sub>                        | Pulse Width for Auto Response                                                          | Figure 10                                 | 40  |            |             | ns      |

| ts                                      | Data Setup Time prior to REG LOAD<br>Positive Edge, Hold Time (t <sub>H</sub> ) = 0 ns | Figure 12                                 |     | 15         | 25          | ns      |

| t <sub>r1</sub>                         | Rise Time for DATA, DATA, and DATA DELAY Output Waveform                               | Load Circuit 2<br>Figure 11               |     | 7          | 13          | ns      |

| t <sub>f1</sub>                         | Fall Time for DATA, DATA, and DATA DELAY Output Waveform                               | Load Circuit 2<br>Figure 11               |     | 5          | 11          | ns      |

| t <sub>r2</sub>                         | Rise Time for TA and REG FULL                                                          | Load Circuit 1<br>Figure 15               |     | 20         | 30          | ns      |

| t <sub>f2</sub>                         | Fall Time for TA and REG FULL                                                          | Load Circuit 1<br>Figure 15               |     | 15         | 25          | ns      |

| f <sub>MAX</sub>                        | Data Rate Frequency (Clock Input must be 8X this Frequency)                            | (Note 7)                                  | DC  |            | 3.5         | Mbits/s |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified, min./max. limits apply across the 0°C to +70°C temperature range and the 4.75V to 5.25V power supply range. All typical values are for T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5.0V.

Note 3: All currents into device pins are shown as positive; all currents out of device pins are shown as negative; all voltages are referenced to ground, unless otherwise specified. All values shown as max, or min, are so classified on absolute basis.

Note 4: Only one output should be shorted at a time. Output should not be shorted for more than one second at a time.

Note 5: T = 1/(Oscillator Frequency), unit for T should be ns. B = 8T

Note 6: Oscillator Frequency Dependent.

Note 7: For the IBM 3270 Interface, the data rate frequency is 2.358 Mblts/s. 28 MHz clock frequency corresponds to 3.75% jitter when referenced to Figure 10 of DP8341 Datasheet.

TL/F/5251-8

TL/F/5251-9

TL/F/5251~10

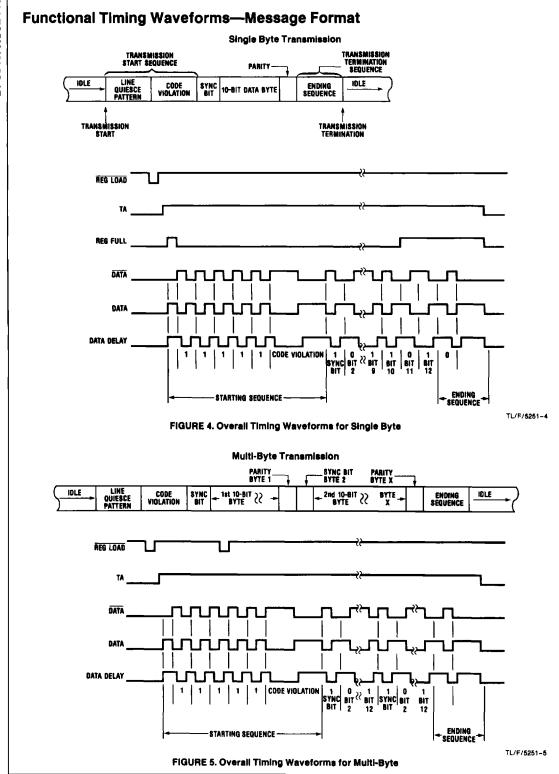

# **Timing Waveforms**

FIGURE 7. Timing Waveforms for Single Byte Transfer

FIGURE 8. Maximum Window to Load Multi-Byte Data

FIGURE 9. Timing Waveforms for Three Serial Outputs

# Timing Waveforms (Continued)

FIGURE 10. Timing Waveforms for Auto-Response

TL/F/5251-11

TL/F/5251-13

TL/F/5251-15

TL/F/5251-14

FIGURE 11. Output Waveform for DATA, DATA DELAY (Load Circuit 2)

FIGURE 12. Register Load Waveform Requirement

FIGURE 13. Timing Waveforms for Clock Pulse

FIGURE 14. Timing Waveforms for Two Byte Transfer

$$^{\rm TL/F/5251-16}$$  FIGURE 15. Rise and Fall Time Measurement for TA and REG Full

## **Typical Applications**

FIGURE 16. Typical Applications for IBM 3270 Interface

DATA DELAY DATA DELAY

TL/F/5251-18

TL/F/5251-17

Note 1: Resistance values are in  $\Omega_{\star} \pm 5\%$ ,  $\frac{1}{4}$  W

Note 2: T1 is a 1:1:1 pulse transformer, L<sub>MIN</sub> = 500 µH for 18 MHz system clock. Pulse Engineering Part No. 5762/Surface Mount, 5762M/PE-85762. Technitrol Part No. 11LHA, Valor Electronics Part No. CT1501 or equivalent transformers.

Note 3: Crystal manufacturer's Midland Ross Corp. NEL Unit Part No. NE-18A (C2560N) @ 18.867 MHz and the Viking Group of San Jose, CA Part No. VXB46NS @ 18.867 MHz.

FIGURE 17. Translation Logic