# PART NUMBER

## 54LS192BEA-ROCV

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

#### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

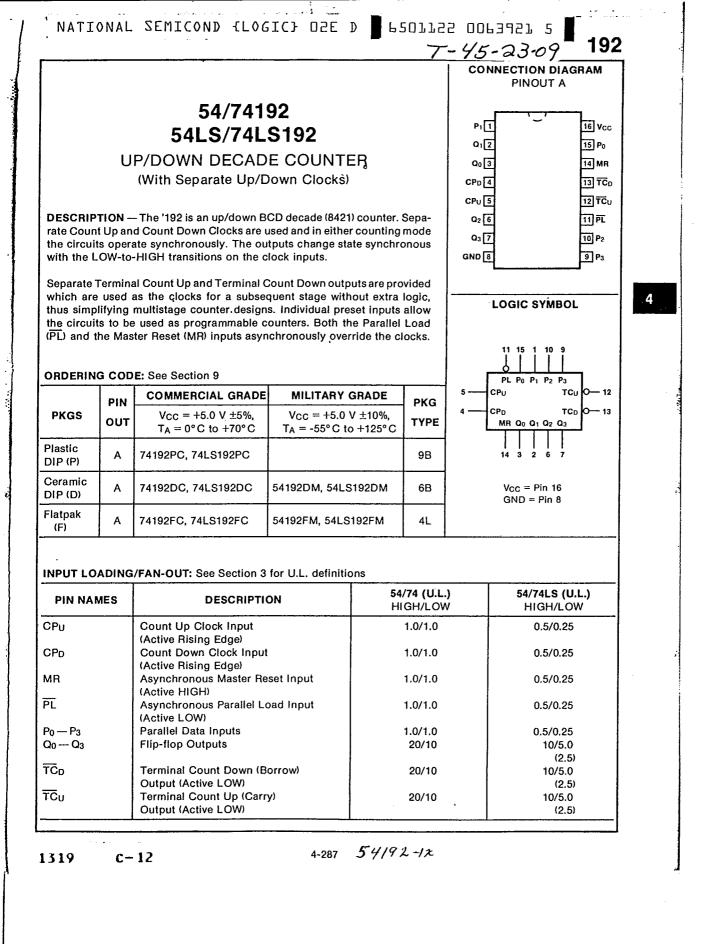

NATIONAL SEMICOND {LOGIC} D2E D 6501122 D063922 7 192 T-45-23-09 . . .

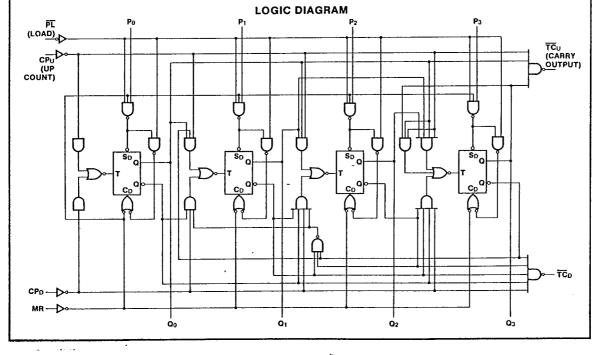

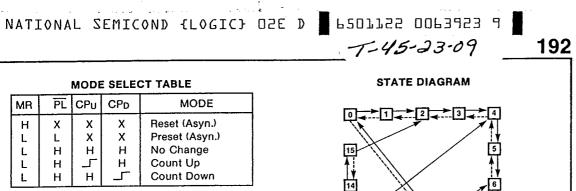

**FUNCTIONAL DESCRIPTION** — The '192 and '193 are asynchronously presettable decade and 4-bit binary synchronous up/down (reversible) counters. The operating modes of the '192 decade counter and the '193 binary counter are identical, with the only difference being the count sequences as noted in the State Diagram. Each circuit contains four master/slave flip-flops, with internal gating and steering logic to provide master reset, individual preset, count up and count down operations.

Each flip-flop contains JK feedback from slave to master such that a LOW-to-HIGH transition on its T input causes the slave, and thus the Q output to change state. Synchronous switching, as opposed to ripple counting, is achieved by driving the steering gates of all stages from a common Count Up line and a common Count Down line, thereby causing all state changes to be initiated simultaneously. A LOW-to-HIGH transition on the Count Up input will advance the count by one; a similar transition on the Count Down input will decrease the count by one. While counting with one clock input, the other should be held HIGH. Otherwise, the circuit will either count by twos or not at all, depending on the state of the first flip-flop, which cannot toggle as long as either Clock input is LOW.

The Terminal Count Up  $(\overline{TC}_U)$  and Terminal Count Down  $(\overline{TC}_D)$  outputs are normally HIGH. When a circuit has reached the maximum count state (9 for the '192, 15 for the '193), the next HIGH-to-LOW transition of the Count Up Clock will cause  $\overline{TC}_U$  to go LOW.  $\overline{TC}_U$  will stay LOW until CPU goes HIGH again, thus effectively repeating the Count Up Clock, but delayed by two gate delays. Similarly, the  $\overline{TC}_D$  output will go LOW when the circuit is in the zero state and the Count Down Clock goes LOW. Since the  $\overline{TC}$  outputs repeat the clock waveforms, they can be used as the clock input signals to the next higher order circuit in a multistage counter.

$$\overline{TC}_{U} = Q_{0} \bullet Q_{3} \bullet \overline{CP}_{U}$$

$$\overline{TC}_{D} = \overline{Q}_{0} \bullet \overline{Q}_{1} \bullet \overline{Q}_{2} \bullet \overline{Q}_{3} \bullet \overline{CP}_{D}$$

Each circuit has an asynchronous parallel load capability permitting the counter to be preset. When the Parallel Load ( $\overrightarrow{PL}$ ) and the Master Reset (MR) inputs are LOW, information present on the Parallel Data inputs ( $P_0 - P_3$ ) is loaded into the counter and appears on the outputs regardless of the conditions of the clock inputs. A HIGH signal on the Master Reset input will disable the preset gates, override both Clock inputs, and latch each Q output in the LOW state. If one of the Clock inputs is LOW during and after a reset or load operation, the next LOW-to-HIGH transition of that Clock will be interpreted as a legitimate signal and will be counted.

1320

C-13

<sup>4-288 54192-2</sup>x

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

Marine and and and

•

ŵ

4.00

4.

| DC CHARACTERISTICS OVER OPERATING | TEMPERATURE RANGE (unless otherwise specified) |

|-----------------------------------|------------------------------------------------|

|-----------------------------------|------------------------------------------------|

| SYMBOL PARAMETE | evupor.                         | DADAMETER |            | 54         | /74        | 54/7         | 74LS | UNITS                                                                    | CONDITIONS |

|-----------------|---------------------------------|-----------|------------|------------|------------|--------------|------|--------------------------------------------------------------------------|------------|

|                 | PARAMETER                       | MIn       | Max        | Min        | Max        | onno         |      |                                                                          |            |

| los             | Output Short<br>Circuit Current | XM<br>XC  | -20<br>-18 | -65<br>-65 | -20<br>-20 | -100<br>-100 | mA   | Vcc = Max                                                                |            |

| lcc             | Power Supply Current            | XM<br>XC  |            | 89<br>102  | -          | 34<br>34     | mA   | V <sub>CC</sub> = Max; MR, $\overline{PL}$ = Gnc<br>Other Inputs = 4.5 V |            |

#### AC CHARACTERISTICS: $V_{CC}$ = +5.0 V, $T_A$ = +25°C (See Section 3 for waveforms and load configurations)

|              |                                                                           | 54/74                    | 54/74LS    |       |                 |

|--------------|---------------------------------------------------------------------------|--------------------------|------------|-------|-----------------|

| SYMBOL       | PARAMETER                                                                 | CL = 15 pF<br>RL = 400 Ω | CL = 15 pF | UNITS | CONDITIONS      |

|              |                                                                           | Min Max                  | Min Max    |       |                 |

| fmax         | Maximum Count Frequency                                                   | 25                       | 30         | MHz   | Figs. 3-1, 3-8  |

| tplн<br>tpнL | Propagation Delay<br>CP <sub>U</sub> or CP <sub>D</sub> to Q <sub>n</sub> | 38<br>47                 | 31<br>28   | ns    |                 |

| tPLH<br>tPHL | Propagation Delay<br>CPu to TCu                                           | 26<br>24                 | 16<br>21   | ns    | Figs. 3-1, 3-5  |

| tplH<br>tpHL | Propagation Delay<br>CP <sub>D</sub> to TC <sub>D</sub>                   | 24<br>24                 | 16<br>24   |       |                 |

| tplh<br>tphL | Propagation Delay<br>P <sub>n</sub> to Q <sub>n</sub>                     |                          | 20<br>30   | ns    | Figs. 3-1, 3-5  |

| tplH<br>tpHL | Propagation Delay<br>PL to Q <sub>n</sub>                                 | 40<br>40                 | 32<br>30   | ns    | Figs. 3-1, 3-16 |

| tphL         | Propagation Delay, MR to Qn                                               | 35                       | 25         |       | 1.13-1.0        |

C-14 1321

54192-3×

### NATIONAL SEMICOND {LOGIC} 030 Jacob 06501322 0063924 0 192

**T**-45-23-09

4

| SYMBOL                                   | PARAMETER                          | 54/74    |     | 54/74LS    |     | UNITS | CONDITIONS                                           |

|------------------------------------------|------------------------------------|----------|-----|------------|-----|-------|------------------------------------------------------|

|                                          |                                    | Min      | Мах | Min        | Max |       |                                                      |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time HIGH or LOW<br>Pn to PL | 20<br>20 |     | 20<br>10   |     | ns    | Fig. 3-13<br>CP <sub>U</sub> = CP <sub>D</sub> = LOW |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time HIGH or LOW<br>Pn to PL  | 0<br>3.0 |     | 3.0<br>3.0 |     |       |                                                      |

| t <sub>w</sub> (L)                       | CP Pulse Width LOW                 | 20       |     | 17         |     | ns    | Fig. 3-8                                             |

| t <sub>w</sub> (L)                       | PL Pulse Width LOW                 | 20       |     | 20         |     | ns    | Fig. 3-16                                            |

| t <sub>w</sub> (H)                       | MR Pulse Width HIGH                | 20       |     | 15         |     |       |                                                      |

| trec                                     | Recovery Time, MR to CP            | 6.0      |     | 3.0        |     |       |                                                      |

| trec                                     | Recovery Time, PL to CP            | 6.0      |     | 10         |     |       |                                                      |

D-01

4-290 54192-4x

1322