# **TSB42AA9/TSB42AA9I**

StorageLynx 1394 Link-Layer Controller for ATA/ATAPI Storage Products

# Data Manual

July 2002

**MSDS 1394**

SLLS453B

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

# Contents

| Section |        | Title          |                                                     |     |  |

|---------|--------|----------------|-----------------------------------------------------|-----|--|

| 1       | Introd | duction .      |                                                     | 1–1 |  |

|         | 1.1    | Descrip        | tion                                                | 1–1 |  |

|         | 1.2    | Feature        | S                                                   | 1–1 |  |

|         | 1.3    |                | Documents                                           | 1–2 |  |

|         | 1.4    | Termina        | al Assignments/Package                              | 1–2 |  |

|         | 1.5    | Termina        | al Descriptions                                     | 1–3 |  |

|         | 1.6    | Chapter        | r References                                        | 1–4 |  |

| 2       |        |                | ription                                             | 2–1 |  |

|         | 2.1    |                | nal Block Diagram                                   | 2–1 |  |

|         | 2.2    |                | nal Block Descriptions                              |     |  |

|         |        | 2.2.1          | IEEE 1394a Link Core                                |     |  |

|         |        | 2.2.2          | Receive Packet Router                               |     |  |

|         |        | 2.2.3          | Transmit Packetizer                                 |     |  |

|         |        | 2.2.4          | SBP-2 Transport Protocol Engine                     |     |  |

|         |        |                | 2.2.4.1 Management Agent                            |     |  |

|         |        |                | 2.2.4.2 Command Agent                               |     |  |

|         |        | 005            | 2.2.4.3 Data Transfer Control                       | -   |  |

|         |        | 2.2.5          |                                                     |     |  |

|         |        |                | 2.2.5.1 Data FIFO                                   |     |  |

|         |        | 0.0.0          | 2.2.5.2 Control FIFO                                | 2–5 |  |

|         |        | 2.2.6<br>2.2.7 | Embedded 8052 Processor      Internal ROM           |     |  |

|         |        | 2.2.7          | Configuration ROM Fast Access Storage               | 2-0 |  |

|         |        | 2.2.0          | (Parameter RAM)                                     | 2–6 |  |

|         |        | 2.2.9          | ATA/ATAPI Interface                                 |     |  |

|         |        | 2.2.10         | Flash PROM/EPROM Interface                          |     |  |

|         |        | 2.2.11         | 2-Wire Serial EEPROM Bus Interface                  |     |  |

|         | 2.3    | Operatio       | onal Modes                                          | 2–7 |  |

|         | 2.4    | Chapter        | r References                                        | 2–8 |  |

| 3       | Confi  | guration       | Registers (CFR)                                     | 3–1 |  |

|         | 3.1    | Registe        | r Map                                               | 3–1 |  |

|         | 3.2    | Registe        | r Descriptions                                      | 3–2 |  |

|         |        | 3.2.1          | Version Register at 00h                             | 3–2 |  |

|         |        | 3.2.2          | Reserved Register at 04h                            | 3–2 |  |

|         |        | 3.2.3          | Control Register at 08h                             | 3–3 |  |

|         |        | 3.2.4          | Interrupt and Interrupt Mask Register at 0C and 10h | 3–3 |  |

|         |        | 3.2.5          | Cycle Timer Register at 14h                         | 3–5 |  |

|   |        | 3.2.6      | Reserved Register at 18h                                     | 3–5  |

|---|--------|------------|--------------------------------------------------------------|------|

|   |        | 3.2.7      | Maintenance Control Register at 1Ch                          | 3–5  |

|   |        | 3.2.8      | Reserved Register at 20h                                     | 3–6  |

|   |        | 3.2.9      | PHY Access Register at 24h                                   | 3–6  |

|   |        | 3.2.10     | ATA/ATAPI Interface Configuration Register at 28h            | 3–6  |

|   |        | 3.2.11     | ATA/ATAPI Access Register at 2Ch                             | 3–7  |

|   |        | 3.2.12     | FIFO Status Register at 30h                                  | 3–8  |

|   |        | 3.2.13     | 1394 Bus Reset Register at 34h                               | 3–9  |

|   |        | 3.2.14     | Taskfile (0) Register at 38h                                 | 3–9  |

|   |        | 3.2.15     | Taskfile (1) Register at 3Ch                                 | 3–9  |

|   |        | 3.2.16     | Taskfile (2) Register at 40h                                 | 3–10 |

|   |        | 3.2.17     | Reserved Register at 44h–48h                                 | 3–10 |

|   |        | 3.2.18     | Asynchronous Retry/Priority Budget Register at 4Ch           | 3–10 |

|   |        | 3.2.19     | Control Transmit FIFO: First and Continue<br>Register at 50h | 3–10 |

|   |        | 3.2.20     | Control Transmit FIFO: Update Register at 54h                | 3–11 |

|   |        | 3.2.21     | Reserved at 58h                                              | 3–11 |

|   |        | 3.2.22     | Control Receive FIFO Register at 5C                          | 3–11 |

|   |        | 3.2.23     | SBP-2 Control Register at 60h                                | 3–11 |

|   |        | 3.2.24     | SBP-2 Status Register at 64h                                 | 3–12 |

|   |        | 3.2.25     | Parameter Data Register at 60Ch                              | 3–12 |

|   |        | 3.2.26     | Parameter Data Register 6Ch                                  | 3–13 |

|   |        | 3.2.27     | Command Set Dependent Status FIFO: First and Continue at 70h | 3–13 |

|   |        | 3.2.28     | Command Set Dependent Status FIFO: Update at 74h             | 3–13 |

|   |        | 3.2.29     | Data FIFO Access Register at 78h                             | 3–14 |

|   |        | 3.2.30     | Reserved at 7Ch                                              | 3–14 |

| 4 | Config | guration F | ROM                                                          | 4–1  |

|   | 4.1    | Configura  | ation ROM Requirements (All Values in Hex)                   | 4–1  |

|   | 4.2    | Paramete   | er RAM                                                       | 4–3  |

| 5 | Firmw  |            |                                                              |      |

|   | 5.1    |            | mmand Set                                                    |      |

|   | 5.2    | Supporte   | d Commands                                                   | 5–2  |

|   |        | 5.2.1      | INQUIRY                                                      | 5–2  |

|   |        | 5.2.2      | MODE SENSE (6) and MODE SENSE (10)                           | 5–2  |

|   |        | 5.2.3      | READ (6) and READ (10)                                       |      |

|   |        | 5.2.4      | READ CAPACITY                                                |      |

|   |        | 5.2.5      | TEST UNIT READY                                              | 5–2  |

|   |        | 5.2.6      | VERIFY (10)                                                  | 5–2  |

|   |        | 5.2.7      | WRITE (6) and WRITE (10)                                     | 5–2  |

|   |        | 5.2.8      | WRITE BUFFER                                                 | 5–3  |

|   |        | 5.2.9      | PASS THROUGH                                                 | 5–3  |

| 6 | Memo   |            | ces                                                          | 6–1  |

|   | 6.1    | External   | Flash PROM/EPROM                                             | 6–1  |

|    | 6.2     | Serial EEPROM                                                | 6–1  |

|----|---------|--------------------------------------------------------------|------|

| 7  | Interfa | ce Timing                                                    | 7–1  |

|    | 7.1     | ATA/ATAPI Interface Timing                                   | 7–1  |

|    | 7.2     | Serial EEPROM Interface Timing                               | 7–1  |

|    | 7.3     | External Flash PROM Interface                                | 7–1  |

| 8  | Electri | cal Characteristics                                          | 8–1  |

|    | 8.1     | Absolute Maximum Ratings Over Free-Air Temperature Range     | 8–1  |

|    | 8.2     | Package Thermal Resistance (Rq) Characteristics <sup>†</sup> | 8–1  |

|    | 8.3     | Recommended Operating Conditions                             | 8–1  |

|    | 8.4     | Electrical Characteristics Over Recommended Ranges of        |      |

|    |         | Supply Voltage and Operating Free-Air Temperature            | 8–2  |

| 9  | Memo    | ry Recommendations for StorageLynx                           | 9–1  |

|    | 9.1     | Choice of Internal or External Program Code                  | 9–1  |

|    | 9.2     | Access Time Requirements of FLASH or EPROM                   | 9–1  |

|    | 9.3     | Memory Usage                                                 | 9–1  |

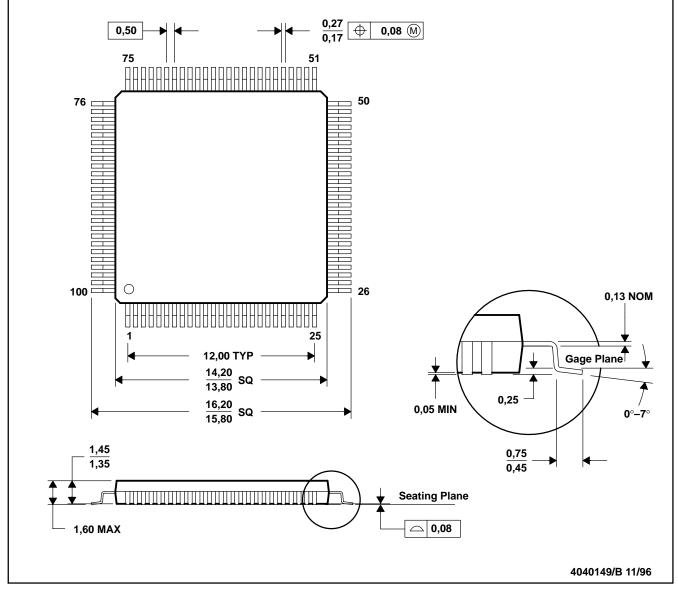

| 10 | Mech    | anical Data                                                  | 10–1 |

# List of Illustrations

| Figu | ire Title                               | Page |

|------|-----------------------------------------|------|

| 2–1  | StorageLynx Block Diagram               | 2–1  |

| 2–2  | PRIORITY_BUDGET Register                | 2–2  |

| 2–3  | Mode 0, ATA/ATAPI Bridge, Internal ROM  | 2–7  |

| 2–4  | Mode 1, ATA/ATAPI Bridge, External ROM  | 2–8  |

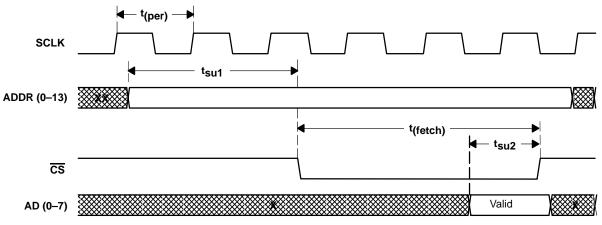

| 7–1  | External Flash Instruction Fetch Timing | 7–1  |

# **List of Tables**

| Tabl | e Title                                          | Page |

|------|--------------------------------------------------|------|

| 2–1  | CSR Registers                                    | 2–2  |

| 2–2  | General Asynchronous Request Header Format       | 2–3  |

| 2–3  | General Asynchronous Response Header Format      | 2–3  |

| 2–4  | Command Agent Registers                          | 2–5  |

| 2–5  | Operational Modes                                | 2–7  |

| 3–1  | StorageLynx Register Map                         | 3–1  |

| 3–2  | Direction Tag Descriptions                       | 3–2  |

| 3–3  | Command Block Register Addressing From ATA/ATAPI |      |

|      | Access Register                                  | 3–8  |

| 5–1  | SCSI Commands Supported for ATA Devices          | 5–1  |

| 7–1  | Instruction Fetch Timing Parameters              | 7–1  |

# **1** Introduction

# 1.1 Description

The Texas Instruments TSB42AA9 (StorageLynx) is a 1394 Link Layer Controller designed to function as a native bridge between the 1394 bus and ATA (AT Attachment) or ATAPI (AT Attachment with Packet Interface) data storage applications. These data storage devices can include external hard disk drives (HDDs), ZIP drives, magneto-optical (MO) drives, ORB drives, CD-ROMs, CD-R/Ws, DVD-ROMs, and DVD-RAMs. The ATA/ATAPI interface of the TSB42AA9 supports signaling and timing for programmed input/output (PIO) modes 0–4, direct memory access (DMA) modes 0–2, and Ultra DMA modes 0–4. The 1394 interface of StorageLynx is IEEE P1394a<sup>[1]</sup> and IEEE Std 1394-1995<sup>[2]</sup> compliant, and it supports 400, 200, and 100 Mbps serial bus data rates.

StorageLynx is particularly designed for any data storage application that supports the SBP-2<sup>[3]</sup> (Serial Bus Protocol 2) transaction layer as a target device. The TSB42AA9 automates the SBP-2 target controller functions by implementing the management and command agents in hardware. Data handling is also executed in hardware, with no assistance from the processor needed to setup a DMA transaction to fetch data from the ATA/ATAPI device and return it to the SBP-2 initiator via the 1394 bus. StorageLynx translates SBP-2 protocol commands to ATA/ATAPI commands using the hardware-implemented functions and an embedded 8052 processor executing firmware. The firmware is located in the internal ROM of the device or optionally, an external memory location.

A 2-wire serial bus interface is included on the TSB42AA9. This interface enables configuration ROM information required by IEEE Std 1394-1995<sup>[2]</sup> and SBP-2 to be loaded from a serial EEPROM into the device's internal parameter RAM. The internal parameter RAM allows StorageLynx faster access to important configuration information as well as automatic responses to configuration ROM read requests from the system host. In addition, StorageLynx provides a memory interface which can be used to access firmware from an external Flash PROM/EPROM for testing and development purposes, or to support storage applications which require specialized functionality. The StorageLynx memory interface also supports write operations to the Flash PROM/EPROM, removing the need for parts to be in sockets and allowing for easy software downloads. Flash memory is not required unless custom functionality and in-system reprogrammability are requirements.

# 1.2 Features

- Serial bus data rates of 100, 200, and 400 Mbps

- IEEE P1394a compliant and IEEE Std 1394-1995

- Automated SBP-2 transport protocol engine

- ATA/ATAPI command translation by embedded processor and firmware

- Programmable ATA/ATAPI interface supporting PIO modes 0–4, DMA modes 0–2, and Ultra DMA modes 0–4

- Automated 1394 and SBP-2 header removal and insertion

- Internal parameter RAM for fast access to configuration ROM and key SBP-2 parameters

- Automatic response to configuration ROM quadlet and block read requests

- External flash PROM / EPROM interface for easy program code changes during prototyping

- Separate address and data busses for the external flash PROM / EPROM interface (no external latches)

- 16K internal ROM program memory

- 576 Byte (128 quadlet) transmit control FIFO, 576 byte (128 quadlet) receive control FIFO

- Bidirectional data FIFO

- 0.18 micron CMOS technology with embedded RAM and ROM

- Space-saving 100 pin TQFP package

#### 1.3 Related Documents

- TSB42AA9 (StorageLynx) EVM User's Guide (literature number SLLU017)

- IEEE P1394a, Draft Standard for a High Performance Serial Bus (Supplement)

- T10 Project 1155D, ANSI NCTIS.xxx-199x, Serial Bus Protocol 2 (SBP-2)

- NCITS T10 1240D, Reduced Block Commands Revision 10 (RBC)

- American National Standards Institute, ANSI NCITS 317-1998, AT Attachment with Packet Interface Extension—(ATA/ATAPI-5 v3.0)

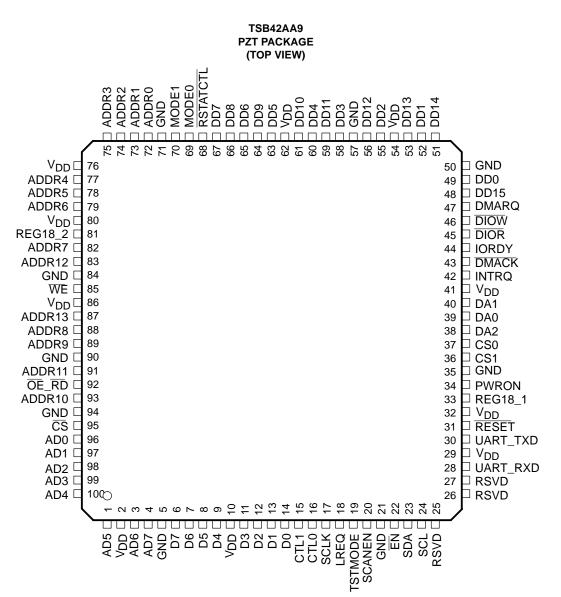

#### 1.4 Terminal Assignments/Package

# 1.5 Terminal Descriptions

The terminal descriptions in this section are grouped by functionality with the package pin numbers added for reference. The following conventions are used in the tables: signals with overbar denote an active low signal; (I) denotes an input; (O) denotes an output; (I/O) denotes a 3-state input and output.

| TERMINAL                               |                                                                         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                                   | NO.                                                                     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                        | POWER                                                                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GND                                    | 5, 21, 35, 50,<br>57, 71, 84, 90,<br>94                                 | ļ   | Device ground terminals                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| VDD                                    | 2, 10, 29, 32,<br>41, 54, 62, 76,<br>80, 86                             | Ι   | 3.3V power supply terminals                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| REG18_1,<br>REG18_2                    | 33, 81                                                                  | 0   | Regulates the 3.3 V supply for core 1.8 V. These pins should be tied to GND through 0.1 $\mu\text{F}$ decoupling capacitors.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| EN                                     | 22                                                                      | Ι   | Enable for 1.8 V regulators (active low). This pin should be tied to GND during normal operation.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| RESET                                  | 31                                                                      | I   | Power-on reset input (active low).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                        |                                                                         | -   | ATA/ATAPI INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| DD[15:0]                               | 48, 51, 53, 56,<br>59, 61, 64, 66,<br>67, 65, 63, 60,<br>58, 55, 52, 49 | I/O | Host-device data bus. This is an 8- or 16-bit bidirectional data interface between the host and the storage device. The lower 8 bits are used for 8-bit register transfers. Data transfers are 16-bits wide. DD15 is the most significant bit.                                                                                                                                                                                          |  |  |  |  |  |  |

| DA[2:0]                                | 38, 40, 39                                                              | 0   | Device address 0 to 2. This is the 3-bit binary coded address asserted by the host to access a register or data port in the storage device.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| CS0                                    | 37                                                                      | 0   | Chip select 0 (active low). This chip select signal is used by the host to select the command block registers in the ATA controller in the storage device.                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| CS1                                    | 36                                                                      | 0   | Chip select 1 (active low). This chip select signal is used by the host to select the command block registers in the ATA controller.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| INTRQ                                  | 42                                                                      | I   | Interrupt request. This signal is used by the ATA controller in the storage device to interrupt its host system. INTRQ is asserted only when the controller has a pending interrupt.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| DMACK                                  | 43                                                                      | 0   | DMA acknowledge (active low). This signal from the host handshakes with the DMARQ for the DMA transfers.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| DMARQ                                  | 47                                                                      | I   | DMA request. This signal, used for DMA data transfers between host and storage device, is asserted by the ATA controller in the device when it is ready to transfer data to or from the host. This signal is released (high impedance state) whenever the device is not selected or is selected and no DMA command is in progress.                                                                                                      |  |  |  |  |  |  |

| I <u>ORDY</u><br>(DDMARDY,<br>DSTROBE) | 44                                                                      | I   | I/O ready. This signal is negated to extend the transfer cycle of any host ATA register access (read or write) when the ATA controller is not ready to respond to a data transfer request. The use of IORDY is required for PIO modes 3 and above, and otherwise is optional.                                                                                                                                                           |  |  |  |  |  |  |

|                                        |                                                                         |     | (Ultra DMA ready (active low). This signal is a flow control for Ultra DMA data out bursts. It is asserted by the ATA device to indicate to the host that the device is ready to receive Ultra DMA data out bursts.                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                        |                                                                         |     | Ultra DMA data strobe. This signal is the data in strobe from the device for an Ultra DMA data in burst.)                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| DIOR<br>(HDMARDY,<br>HSTROBE)          | 45                                                                      | 0   | Read strobe signal (active low). The falling edge of DIOR enables data from the ATA device onto the signals, DD (7:0) or DD (15:0). The rising edge of DIOR latches data into the device. The device does not act on the data until it is latched. The direction of data (16 bits) transfer is controlled by DIOR and DIOW. (Ultra DMA ready (active low). This is a flow control signal for ultra DMA in bursts. It is asserted by the |  |  |  |  |  |  |

|                                        |                                                                         |     | host to indicate to the device that the host is ready to receive ultra DMA data in bursts.<br>Ultra DMA data strobe. This is the data out strobe from the host for an ultra DMA data out burst.)                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| DIOW<br>(STOP)                         | 46                                                                      | 0   | Write strobe signal (active low). The rising edge of DIOW latches data from the signals, DD (7:0) or DD (15:0), into the ATA device. The ATA device does not act on the data until it is latched. The direction of data (16 bits) transfer is controlled by DIOR and DIOW.                                                                                                                                                              |  |  |  |  |  |  |

|                                        |                                                                         |     | (Stop ultra DMA burst. This signal is negated by the host prior to initiation of an ultra DMA burst.)                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| RSTATCTL                               | 68                                                                      | 0   | Reset ATA controller (active low). This output allows the host to asynchronously reset the ATA controller of the device.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| TER        | MINAL                                                           |     |                                                                                                                                                                                                                                                                                          |  |  |  |

|------------|-----------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.   |                                                                 | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                              |  |  |  |

|            |                                                                 |     | PHY INTERFACE                                                                                                                                                                                                                                                                            |  |  |  |

| CTL1, CTL0 | 15, 16                                                          | I/O | PHY-link control bus. CTL1 and CTL0 indicate the four operations that can occur on this interface (see Annex J of the IEEE 1394-1995 standard <sup>[2]</sup> for more information about the four operations).                                                                            |  |  |  |

| D7 – D0    | 6, 7, 8, 9, 11,<br>12, 13, 14                                   | I/O | PHY-link data bus. Data is expected on D0–1 for 100 Mb/s packets, D0–D3 for 200 Mb/s, and D0–D7 for 400 Mb/s. D0 is the most significant bit.                                                                                                                                            |  |  |  |

| LREQ       | 18                                                              | 0   | Link request. LREQ is an output that makes bus requests and register access requests to the PHY.                                                                                                                                                                                         |  |  |  |

| SCLK       | 17                                                              | Ι   | System clock. SCLK is a 49.152-MHz clock supplied by the PHY±100 ppm.                                                                                                                                                                                                                    |  |  |  |

|            |                                                                 |     | FLASH PROM/EPROM INTERFACE                                                                                                                                                                                                                                                               |  |  |  |

| ADDR[13:0] | 87, 83, 91, 93,<br>89, 88, 82, 79,<br>78, 77, 75, 74,<br>73, 72 | 0   | Flash PROM/EPROM address bus. ADDR is a 14-bit address bus between StorageLynx and its (optional) external memory. ADDR13 is the most significant bit.                                                                                                                                   |  |  |  |

| AD[7:0]    | 4, 3, 1, 100,<br>99, 98, 97, 96                                 | I/O | Flash PROM/EPROM data bus. AD is a birdirectional 8-bit data bus between StorageLynx and its (optional) external memory. AD7 is the most significant bit.                                                                                                                                |  |  |  |

| CS         | 95                                                              | 0   | Flash PROM/EPROM chip enable (active low). CS is the external memory chip enable.                                                                                                                                                                                                        |  |  |  |

| OE_RD      | 92                                                              | 0   | Flash PROM/EPROM output enable (active low). OE_RD is the external memory output enable.                                                                                                                                                                                                 |  |  |  |

| WE         | 85                                                              | 0   | Flash PROM/EPROM write enable (active low). WE is the external memory write enable. During normal operation this signal is asserted high.                                                                                                                                                |  |  |  |

|            |                                                                 |     | 2-wire Serial Bus                                                                                                                                                                                                                                                                        |  |  |  |

| SDA        | 23                                                              | I/O | Serial Data. SDA is the data interface for the serial EEPROM. SDA should be pulled up with a 10K resistor at the serial EEPROM.                                                                                                                                                          |  |  |  |

| SCL        | 24                                                              | 0   | Serial Clock. SCL provides serial clock signaling. 100 kHz (Nclk/256) for serial EEPROM.                                                                                                                                                                                                 |  |  |  |

|            |                                                                 |     | RESERVED                                                                                                                                                                                                                                                                                 |  |  |  |

| RSVD       | 25, 26, 27                                                      |     | Reserved. Test Signals                                                                                                                                                                                                                                                                   |  |  |  |

|            |                                                                 |     | MISCELLANEOUS                                                                                                                                                                                                                                                                            |  |  |  |

| UART_RXD   | 28                                                              | I   | UART RXD. Mux-selectable input. On power up, this signal is sampled to set the embedded processor clock speed setting. A detected logic high sets the internal clock to 50 MHz (pull-up through a 10K resistor). A logic low sets the clock to 25 MHz (pull down through a 1K resistor). |  |  |  |

| UART_TXD   | 30                                                              | 0   | UART TXD. Mux-selectable output.                                                                                                                                                                                                                                                         |  |  |  |

| MODE0      | 69                                                              | Ι   | MODE0. This signal is device configuration select 0. See Table 2–4.                                                                                                                                                                                                                      |  |  |  |

| MODE1      | 70                                                              | Ι   | MODE1. This signal is device configuration select 1. See Table 2–4.                                                                                                                                                                                                                      |  |  |  |

| PWRON      | 34                                                              | 0   | Power on. This signal is asserted on power up. PWRON is negated when an SBP–2 logout occurs. This signal can also be used as a general-purpose output.                                                                                                                                   |  |  |  |

| TSTMODE    | 19                                                              | I   | Test mode select. Tie to GND during normal operation.                                                                                                                                                                                                                                    |  |  |  |

| SCANEN     | 20                                                              | Ι   | Test mode scan enable. Tie to GND during normal operation.                                                                                                                                                                                                                               |  |  |  |

# 1.6 Chapter References

- 1. IEEE P1394a, Draft Standard for a High Performance Serial Bus (Supplement)

- 2. IEEE Std 1394–1995, Standard for a High Performance Serial Bus

- 3. T10 Project 1155D, ANSI NCTIS.xxx-199x, Serial Bus Protocol 2 (SBP-2)

# 2 Detailed Description

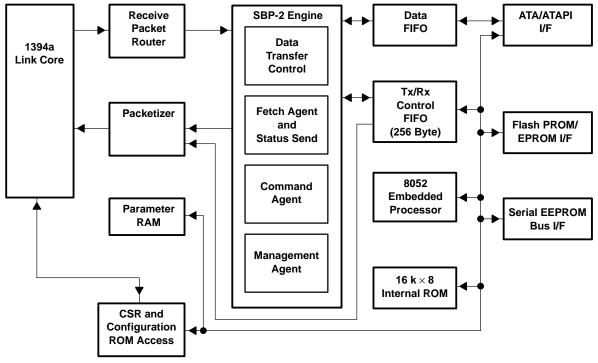

TASB42AA9 comprises:

- IEEE P1394a Compliant Link Core

- Receive Packet Router

- Transmit Packetizer

- SBP-2 Transport Protocol Engine

- FIFOs (Control Tx/Rx and Data)

- Embedded 8052 Processor

- Internal ROM (16K × 8)

- Configuration ROM Registers (Parameter RAM)

- ATA/ATAPI Interface

- Flash PROM/EPROM Interface

- 2-wire Serial EEPROM Bus Interface

# 2.1 Functional Block Diagram

The functional block architecture of TSB42AA9 is shown in Figure 2–1.

#### 2.2 Functional Block Descriptions

#### 2.2.1 IEEE 1394a Link Core

The TSB42AA9 contains an IEEE P1394a compatible link core. The link layer is the protocol layer responsible for the interface between the transaction layer and physical layers for asynchronous transactions. The link core

communicates with a 1394 PHY at speeds of 100, 200, or 400 Mbps by transmitting and receiving IEEE 1394–1995/P1394a serial bus packets. The link core builds packets during transmission and generates the cyclic redundancy check (CRC) values. During packet reception, the link core decodes packets and performs data checking. StorageLynx is not required to contend for Bus Manager, Cycle Master, or Isochronous Resource Manager (IRM) on the 1394 bus because it does not support isochronous transactions.

The StorageLynx link core implements the minimum control and status registers (CSR) necessary for an SBP–2 target device. The CSRs are arranged by the core registers required by ISO/IEC 13213:1994<sup>[1]</sup>, the bus dependent registers required by 1394–1995 standard<sup>[2]</sup>/P1394a standard<sup>[1]</sup>, and the unit architecture registers required by the SBP–2 protocol standard<sup>[4]</sup>. Table 2–1 depicts the locations and functions of the core registers. The start address location of the initial register space is FFFF F000 0000h offset from the initial node space.

| OFFSET           | REGISTER NAME   | DESCRIPTION                                                        |

|------------------|-----------------|--------------------------------------------------------------------|

| 000h STATE_CLEAR |                 | State and control information                                      |

| 004h             | STATE_SET       | Sets STATE_CLEAR bits                                              |

| 008h             | NODE_IDS        | Specifies 16 bit node_ID of the node                               |

| 00Ch             | RESET_START     | Resets the node's state                                            |

| 018–01Ch         | SPLIT_TIMEOUT   | Time limit for split transactions                                  |

| 200h             | CYCLE_TIME      | Maintains cycle time for isochronous transactions (not supported). |

| 210h             | BUSY_TIMEOUT    | Controls transaction layer retries                                 |

| 218h             | PRIORITY_BUDGET | Controls asynchronous priority arbitration                         |

| Table | 2–1.        | CSR | Registers    |

|-------|-------------|-----|--------------|

| Table | <b>4</b> I. |     | I C GIBLOI B |

Also included in Table 2–1 are the bus-dependant registers described by the 1394–1995/P1394a standards for a target device, these registers are the CYCLE\_TIME, BUSY\_TIMEOUT, and PRIORITY\_BUDGET registers. The StorageLynx link core supplements the PRIORITY\_BUDGET register to the minimum CSR.

The PRIORITY\_BUDGET register is implemented because the 1394a specification allows nodes that are transmitting asynchronous packets to arbitrate for the bus more than once during a fairness interval (cycle). This means that StorageLynx can arbitrate for the 1394 bus more often and thus transmit more asynchronous packets increasing data throughput. The pri\_max field of the PRIORITY\_BUDGET register shown in Figure 2–2 defines the maximum number of asynchronous priority requests that can be performed by StorageLynx per fairness interval. It is read only (Default = 3Fh). The pri\_req field defines the current number of additional asynchronous priority requests that can be attempted during the present fairness interval. The bus manager node is responsible for reading the value of the pri\_req field. See the IEEE 1394–1995 standard, 1394a standard, and CSR architecture descriptions of the link core and 1394 protocol for more detail on arbitration enhancements.

#### Format

| 31–14          | 13–08   | 07–06 | 05–00     |

|----------------|---------|-------|-----------|

| Definition     |         |       |           |

| Reserved       | Pri_max | r     | Pri_req   |

| Initial values |         |       |           |

| Zeros          | Value   | r     | Zeros     |

| Read effects   |         |       |           |

| Zeros          | Value   | Z     | Undefined |

| Write effects  |         |       |           |

| Ignored        |         |       | Stored    |

Figure 2–2. PRIORITY\_BUDGET Register

#### 2.2.2 Receive Packet Router

The receive packet router examines the header information of received 1394 packets to determine their destination (see Table 2–2). The Destination\_ID in the header contains a combination of the 1394 bus address and the physical ID of StorageLynx. The Destination\_Offset specifies the address location within the TSB42AA9 that is being accessed. The Source\_ID identifies the 1394 node that is sending the packet. During SBP–2 operation, request and response packets are routed to the correct agent/FIFO by decoding the header information, specifically the Source\_ID field or the Destination\_ID and Destination\_Offset fields. The Tlabel field of a request packet is used to route its corresponding response packet. A Tlabel is a transaction label that is specified by a node sending a request. This same value is then returned to the node in the response packet sent by StorageLynx.

| 31–24                  | 31–24 23–16 15–08 |              | 07–00         |           |           |  |

|------------------------|-------------------|--------------|---------------|-----------|-----------|--|

|                        | D                 | Tlabel       | RT            | Tcode     | Priority  |  |

|                        | Source ID         |              |               | Destinati | on_Offset |  |

| Destination_Offset     |                   |              |               |           |           |  |

|                        |                   | Packet Type- | Specific Data |           |           |  |

| Header CRC             |                   |              |               |           |           |  |

| FIELD NAME DESCRIPTION |                   |              |               |           |           |  |

| Table 2–2. | <b>General As</b> | ynchronous Req | uest Header Format |

|------------|-------------------|----------------|--------------------|

|------------|-------------------|----------------|--------------------|

|                    | Header CRC                                                                                                            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| FIELD NAME         | DESCRIPTION                                                                                                           |

| Destination ID     | Destination ID – Contains the address of the target node.                                                             |

| Tlabel             | Transaction Label- A label specified by the requester that identifies this transaction.                               |

| RT                 | Retry Code – This code specifies whether this packet is an attempted retry and defines the retry protocol to be used. |

| Tcode              | Transaction Code – Identifies type of request being made.                                                             |

| Priority           | Not used.                                                                                                             |

| Source ID          | Source ID – Identifies the node that is sending this packet.                                                          |

| Destination_Offset | Destination Offset – Specifies the address location within the target node that is being accessed.                    |

| Header CRC         | Header CRC – CRC value for the header.                                                                                |

#### Table 2–3. General Asynchronous Response Header Format

|                |                                                              | ai / log noni ono ao ne        | openee neade                              |          | iat               |                    |  |  |  |  |  |  |

|----------------|--------------------------------------------------------------|--------------------------------|-------------------------------------------|----------|-------------------|--------------------|--|--|--|--|--|--|

| 31–24          | 23–16                                                        | 15-                            | -08                                       |          | 07                | -00                |  |  |  |  |  |  |

| D              | estination ID                                                | Tlabel                         | Tlabel RT                                 |          |                   |                    |  |  |  |  |  |  |

|                | Source ID                                                    | Rcode                          |                                           | R        | eserved           | -                  |  |  |  |  |  |  |

|                |                                                              | Reserved                       |                                           |          |                   |                    |  |  |  |  |  |  |

|                |                                                              | Packet Type–Specific I         | Data                                      |          |                   |                    |  |  |  |  |  |  |

|                |                                                              | Header CRC                     |                                           |          |                   |                    |  |  |  |  |  |  |

| FIELD NAME     |                                                              | DESC                           | CRIPTION                                  |          |                   |                    |  |  |  |  |  |  |

| Destination ID | Destination ID – Contains th                                 | e address of the node recei    | address of the node receiving the packet. |          |                   |                    |  |  |  |  |  |  |

| Tlabel         | Transaction Label- Contains                                  | s the value sent by the requ   | ester for this transac                    | ction.   |                   |                    |  |  |  |  |  |  |

| RT             | Retry Code – This code spe                                   | cifies whether this packet is  | an attempted retry a                      | and defi | nes the retry pro | ptocol to be used. |  |  |  |  |  |  |

| Tcode          | Transaction Code – Identifie                                 | s type of response being ma    | ade.                                      |          |                   |                    |  |  |  |  |  |  |

| Priority       | Priority Not used.                                           |                                |                                           |          |                   |                    |  |  |  |  |  |  |

| Source ID      | Source ID – Identifies the node that is sending this packet. |                                |                                           |          |                   |                    |  |  |  |  |  |  |

| Rcode          | Response Code – Specifies                                    | the result of this transaction | ۱.                                        |          |                   |                    |  |  |  |  |  |  |

| Hoodor CBC     | Header CBC CBC value f                                       | ar the header                  |                                           |          |                   |                    |  |  |  |  |  |  |

Header CRC Header CRC – CRC value for the header.

#### 2.2.3 Transmit Packetizer

The transmit packetizer provides automated packetization services for 1394 transmit packets. The outgoing data stream from the Data FIFO is transmitted in packets with appropriate header information provided by the packetizer.

The destination address (Destination\_ID and Destination\_Offset) is incremented based on the size of the data payload sent in the previous packet, so the next packet destination address is correct. The packetizer also provides transaction control services that control packet transmission priority between packets in the Control FIFO and in the Data FIFO. It also controls split transaction management and busy retry. If an acknowledge packet with a busy code is received by StorageLynx, the packetizer is responsible for resending the packet until the packet succeeds or the retry limit is reached.

# 2.2.4 SBP-2 Transport Protocol Engine

Serial Bus Protocol 2 (SBP-2) is a transport protocol that defines the means for communicating commands sourced by a device connected to the serial bus (initiator) to other devices on the serial bus (targets). SBP-2 also defines the means required for the transfer of data or status associated with these commands. StorageLynx is designed to provide the SBP-2 protocol required by a target device. StorageLynx accelerates much of the SBP-2 protocol by implementing it in hardware. This hardwired functionality is distributed in the StorageLynx architecture to affect SBP-2 acceleration of management, command, and data movement during respective phases of operation. The TSB42AA9 is not designed to provide SBP-2 initiator services.

A target agent is the part of the SBP-2 Engine that receives signals that indicate when an initiator has a command ready. There are two types of target agent; one that can process one command at a time, and one that can manage linked lists of commands. In the first case, the initiator signals the command to the agent by means of a block write request with the address of the command. In the other case, the initiator adds new commands to an active list and rings a doorbell that causes the agent to fetch another command from the system memory. These two types of target agents are known respectively as the management agent and the command block agent.

#### 2.2.4.1 Management Agent

The management agent can accept various types of requests (commands) from an initiator node such as: login, task management, and logout. The first request an initiator makes is always a login request. After the initiator completes a login, the management agent can accept task management requests from the initiator. Ultimately, the initiator will generate a logout command to release the target. Management agents service a single request at a time.

The initiator node processes a request by writing the address of the management operation request block (ORB) containing the request to the pointer register of the management agent. The target then fetches the ORB by reading it over the 1394 bus and stores it in the management ORB registers where it is processed. Whenever the management agent register is written to, the management agent reads and fetches ORBs automatically.

The management agent register location is specified in the configuration ROM. The StorageLynx management agent register base address is offset by 10000h from the initial CSR space at FFFF\_F000\_0000h. All management agent ORBs are 32-byte data structures written to the register at FFFF\_F001\_0000h. The management agent is also responsible for storing management information as outlined in the SBP-2 protocol[1].

The management agent supported in the hardware of the TSB42AA9 can process the following types of management ORB requests:

- Login

- Query Login

- Reconnect

- Set Password

- Logout

- Abort Task Set

- Target Reset

# 2.2.4.2 Command Agent

A successful login request to the management agent of StorageLynx returns the address of the command block agent. Command block agents service command block ORBs that are structured in the form of a linked list or a page table. Command ORBs are used to encapsulate data transfer or device control commands from the initiator for transmission to the target device. A target system's command set and device type determine the size of the ORBs. This size is reported in the StorageLynx (target) configuration ROM.

The command agent of StorageLynx also implements CSRs as shown in Table 2–4 at a predefined offset that is reported by the target device during the login processed by the management agent. The command agent location is FFFF\_F001\_0020h, which is 32 bytes above the location of the management agent. See the SBP-2 protocol<sup>[1]</sup> for more detail on the command agent responsibilities.

| RELATIVE OFFSET | NAME                      | DESCRIPTION                                                |

|-----------------|---------------------------|------------------------------------------------------------|

| 00h             | AGENT_STATE               | Reports command (fetch) agent state                        |

| 04h             | AGENT_RESET               | Resets command agent                                       |

| 08h             | ORB_POINTER               | Address of ORB                                             |

| 10h             | DOORBELL                  | Signals command agent to refetch an address pointer        |

| 14h             | UNSOLICITED_STATUS_ENABLE | Acknowledges the initiator's receipt of unsolicited status |

| 18h–1Ch         |                           | Reserved                                                   |

# 2.2.4.3 Data Transfer Control

The data transfer control block is responsible for moving large blocks of data between the initiator (host) and target (storage) devices. The data block also performs the buffer management functions at the ATA/ATAPI (target) interface. Buffer management includes controlling buffer direction (Tx or Rx) and packet sizes, filling and emptying the buffer without overflow or underflow, and detecting errors. It is responsible for managing the size and number of read / write transactions necessary to transfer all the requested data since data block lengths may be larger than the maximum data payload that can be accommodated in a single transaction. The data control block may choose any appropriate size for the data transfer transactions subject to alignment, speed, and data payload length constraints specified by the command ORB that requested the data. Refer to the SBP-2 protocol<sup>[1]</sup> for more detail on the data transfer control block responsibilities.

# 2.2.5 FIFO

The StorageLynx FIFO is partitioned according to the type of information it contains. Separate storage for control (management / command) and data is provided. The FIFO also provides a packet buffer for data exchange between the attached ATA/ATAPI device and the 1394 serial bus.

# 2.2.5.1 Data FIFO

The data FIFO is used for the transfer of data to/from the ATA/ATAPI interface. The data FIFO provides sufficient storage for two maximum size asynchronous packets at the maximum bus speed of 400 Mbps. The data movement direction determines whether the FIFO is a transmit or a receive FIFO.

# 2.2.5.2 Control FIFO

The control FIFO is used for the transfer of the commands to the embedded processor. The FIFO is partitioned with a fixed size transmit FIFO and receive FIFO. The embedded processor reads the Rx FIFO, also known as the general receive FIFO (GRF), through a dedicated CFR address (see section 3.2.22). Reading all four byte addresses stored in the register causes new data to be pulled from the receive FIFO and become available for reading. Two accesses to a single byte address in the Rx FIFO CFR address range can also cause a new quadlet to be fetched from the Rx FIFO. The embedded processor can write the Tx FIFO, also known as the asynchronous transmit FIFO (ATF),

through a dedicated CFR address (see section 3.2.19, Control Transmit FIFO: First and Continue Register). Writing all four byte addresses in the register causes more data to be queued into the Tx FIFO. Two write accesses to a byte address in the Tx FIFO CFR address also causes a new quadlet to be queued to the Tx FIFO with the unwritten bytes defaulting to zeroes.

#### 2.2.6 Embedded 8052 Processor

A high performance 8-bit 8052-type microcontroller, onboard the StorageLynx, performs RBC to ATA command translation. The firmware also pulls ATAPI commands from the receive FIFO and loads them into the ATAPI device taskfile registers (see section 3.2.14, Taskfile (0) Register). The embedded processor usually executes the program code contained in the on-chip internal ROM, but it can also execute customized program code stored in an external memory by switching the mode (see Table 2–5.). See the MacroWare Library description of the M8052 MegaMacro Design<sup>[2]</sup> for more information on the embedded processor.

The speed of the embedded processor can be customized. The UART\_RXD terminal is sampled at power up to select the embedded processor clock speed setting. When the signal is detected logic high, the internal clock is set to 50 MHz. A logic low on the UART\_RXD pin sets the processor clock to 25 MHz. The TSB42AA9 should be run at 50 MHz if an ATA device is attached, and at 25 MHz for an ATAPI device. Also, while optimal performance for ATA devices is obtained at 50 MHz, running the processor at 25 MHz (to accommodate slower flash memory devices) only causes a slight degradation in speed performance.

# 2.2.7 Internal ROM

StorageLynx contains on-board mask ROM of 16K to store program code for the embedded processor. This ROM is written during production and cannot be rewritten.

#### 2.2.8 Configuration ROM Fast Access Storage (Parameter RAM)

At power up some of the configuration ROM information required for implementation of a SBP-2 serial bus node is copied from external memory and written to the on-chip parameter RAM (internal configuration storage space). The configuration ROM stored in the EEPROM is accessed through the 2-wire serial bus interface and copied to the internal configuration storage space. The internal storage of configuration ROM information allows the device faster access to important configuration information as well as automatic responses to some read requests from the system host.

Both internal and external configuration storage spaces remain accessible to the embedded processor through the parameter access register @68h (see section 3.2.25) while StorageLynx is powered up. Read requests to a configuration ROM address outside of the data stored in the internal parameter RAM are routed through the 2-wire serial bus.

#### 2.2.9 ATA/ATAPI Interface

The ATA/ATAPI interface is responsible for movement of data between the ATA/ATAPI storage device and the data FIFO of StorageLynx. The StorageLynx firmware performs ATA command and status translation using the reduced block command (RBC)<sup>[3]</sup> set for ATA devices. However, the StorageLynx firmware acts mainly as a pass through for ATAPI devices pulling commands from the receive FIFO and loading the ATAPI device taskfile registers (see section 3.2.14). The ATA/ATAPI interface block hardware is responsible for transferring the ATAPI packets by generating PACKET commands.

The ATA/ATAPI interface meets the critical timing requirements for the PIO 0-4, DMA 0-2, and Ultra DMA 0-4 modes defined in the ATA/ATAPI-5 v3.0 spec<sup>[4]</sup>. The ATA/ATAPI interface terminals are all 5-Volt tolerant and 5-Volt failsafe, which means that StorageLynx can interface with an ATA/ATAPI device that is running the ATA/ATAPI interface at 5 Volts without damage, even if StorageLynx is powered down.

#### 2.2.10 Flash PROM/EPROM Interface

The Flash PROM/EPROM interface allows the embedded processor to execute external program code instead of the internal program code. This capability is useful for system debugging and testing purposes. This external memory

option can also be used to support custom commands and functionality desirable in storage applications. Sockets for parts are not needed because the memory interface also supports writes to the flash PROM/EPROM (even to blank devices), allowing for easy software downloads via the 1394 bus. An external flash memory can be used in applications where in-system reprogrammability is a requirement.

#### 2.2.11 2-Wire Serial EEPROM Bus Interface

The 2-wire serial bus interface allows configuration ROM (see section 4) information stored in an external serial EEPROM to be loaded into the StorageLynx parameter RAM to allow quicker responses to configuration ROM read requests from the system host and faster access to device parameters. On power-up, the logic stored in the serial EEPROM is loaded into parameter RAM via the 2-wire serial bus interface. The configuration ROM logic in the external serial EEPROM is also accessible to the embedded processor through the 2-wire serial bus. This 2-wire interface also allows changes and updates to be made easily to the configuration ROM information using the StorageLynx programming application via the 1394 bus, thus removing the need for preprogrammed and socketed parts. The TSB42AA9 also supports writes to blank serial EEPROMs.

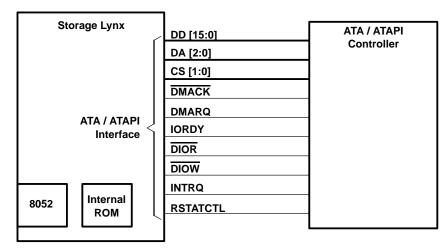

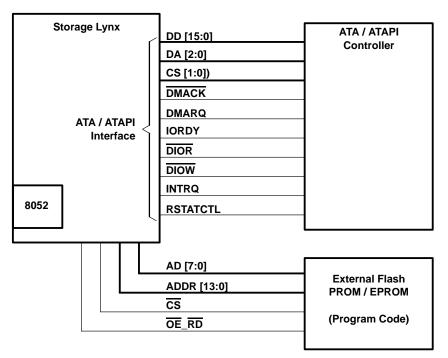

# 2.3 Operational Modes

StorageLynx supports two separate modes of operation shown in Table 2–4. The MODE0 and MODE1 signals are used to configure the mode of the device. These two signals must always be driven to just one state and cannot be dynamically switched during operation. Figures 2–3, 2–4, and 2–5 show block diagrams for each of the modes.

| MODE | MODE<br>[0:1] | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 00            | ATA/ATAPI bridge mode 1.<br>The embedded 8052 processor is enabled and executes program code loaded in the internal Program ROM. Storage-<br>Lynx can be in either ATA or ATAPI mode, depending on the setting of bit ATP at Register 28h. This register setting may<br>be overwritten by the firmware after accessing the external device to check its device type.                                             |

| 1    | 01            | ATA/ATAPI bridge mode 2 (development mode).<br>The embedded 8052 processor is enabled and executes program code loaded in external Flash PROM/EPROM. The<br>internal ROM is disabled. StorageLynx is in either ATA or ATAPI mode, depending on the setting of bit ATP at Register<br>28h. This register setting may be overwritten by the firmware after accessing the external device to check its device type. |

| 2-3  |               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 2–5. | Operational | Modes |

|------------|-------------|-------|

|------------|-------------|-------|

Figure 2–3. Mode 0, ATA/ATAPI Bridge, Internal ROM

Figure 2–4. Mode 1, ATA/ATAPI Bridge, External ROM

#### 2.4 Chapter References

- 1. Serial Bus Protocol 2 (SBP-2), T10 Project 1155D, Revision 4, May 19, 1998

- 2. Mentor Graphics, 3Soft M8042 MegaMacro Design

- 3. NCITS T10 1240D, Reduced Block Commands Revision 10 (RBC)

- 4. American National Standards Institute, ANSI NCITS 317-1998, AT Attachment with Packet Interface Extension – (ATA/ATAPI-5 v3.0)

# 3 Configuration Registers (CFR)

This section describes the layout and content of the TSB42AA9 configuration registers. The address space begins at 00h in the XDATA memory space of the embedded processor.

# 3.1 Register Map

Table 3-1 shows the StorageLynx register map.

|             | 0       | 1      | 2      | 3       | 4         | 5        | 6           | 7        | 8             | 9        | 10      | 11     | 12    | 13      | 14        | 15   | 16        | 17        | 18        | 19                  | 20    | 21         | 22       | 23       | 24     | 25   | 26    | 27           | 28    | 29           | 30         | 31   | Register Name       |

|-------------|---------|--------|--------|---------|-----------|----------|-------------|----------|---------------|----------|---------|--------|-------|---------|-----------|------|-----------|-----------|-----------|---------------------|-------|------------|----------|----------|--------|------|-------|--------------|-------|--------------|------------|------|---------------------|

| 00h         | 7       | •      | -      | •       | 3         | 0        |             | <i>.</i> | 1             | •        | 10      |        | 6     | 10      |           | 10   | 3         |           | 10        | 10                  | 0     |            |          | 20       | 0      | 20   | 20    | 21           | 0     | 120          | 00         | 101  | Version             |

| 00h         | Ľ       |        |        |         | 0         |          |             |          | 1             |          |         |        | 0     |         |           |      | 5         |           |           |                     | 0     |            |          |          | 0      |      |       |              | 0     |              |            |      | Reserved            |

| 0411<br>08h |         |        |        |         |           |          |             | _        |               |          |         |        |       |         | Q         | _    |           |           |           |                     |       |            |          |          |        |      |       |              |       |              |            |      | Control             |

| 0011        | ⊢⊢      |        |        | ╘       |           |          |             |          |               |          |         |        |       |         | ENA_LHOLD |      |           |           |           |                     |       |            |          | CLRSIDER |        |      |       | -            |       |              |            |      | Control             |

|             | RS.     |        |        | B       | С         | z        | z           |          |               |          | ¥       | X      |       |         | <u>–</u>  |      |           |           |           |                     |       |            |          | S S      |        |      |       | õ            |       |              |            |      |                     |

|             | SFTRST  |        |        | PAGEBIT | BSYCTL    | TXEN     | RXEN        |          |               |          | RSTTX   | RSTRX  |       |         | Å         |      |           |           |           |                     |       |            |          | Ľ        |        |      |       | PWRON        |       |              |            |      |                     |

| 0Ch         | 0       |        |        | а.      |           | -        | Ľ.          |          |               | -        | œ       | œ      |       |         | ш         | _    |           |           |           |                     |       |            |          | -        |        |      |       | а.           |       | 1            |            | -    | late must           |

| UCN         |         |        |        |         | SELFIDEND | RXGRFPKT | ⊢⊢          | К        |               | ATFEMPTY |         | ~      |       | ×       |           |      | F         |           |           |                     |       |            |          | ⊢        |        |      |       |              |       |              |            |      | Interrupt           |

|             |         | ⊢      | X      | ы       | <u> </u>  | RFF      | LSS         | ē        | ¥             | Ξ        | 2       | R.     | Ж     | AC      |           | _    | Ľ         |           |           |                     | ЪР    | 6          |          | 0        | Σ      |      | ~     | ъ            | R     | S            | S          |      |                     |

|             | INT     | PHINT  | PHRRX  | PHRST   |           | Ŭ        | CMDRST      | SELFIDER | ATSTK         | 삕        | SNTRJ   | HDRERR | TCERR | FIFOACK |           | CYST | RTRYLMT   |           |           |                     | ARBGP | SUBGP      |          | LIN/LOUT | NORM   | ABSY | AERR  | PIERR        | PDERR | SCMIS        | NDMIS      | AINT |                     |

|             | Ξ       | đ      | đ      | đ       |           |          | ō           | S        | A             | 2        | S       | Ξ      | Ĕ     | FI      |           | ΰ    | Ŕ         |           |           |                     | AI    | S          |          | Ξ        | ž      | Ā    | A     | P            | Ы     | õ            | Z          | A    |                     |

| 10h         |         |        |        |         | SELFIDEND | RXGRFPKT |             | 2        |               | ≿∣       |         |        |       |         |           |      | ⊢         |           |           |                     |       |            |          | _        |        |      |       |              |       |              |            |      | Interrupt Mask      |

|             |         | .      | ×      | ⊢       | Б         | ЧL       | CMDRST      | SELFIDER | $\overline{}$ | ATFEMPTY | _       | HDRERR | 2     | FIFOACK |           |      | RTRYLMT   |           |           |                     | ۲     | ٦          |          | LIN/LOUT | F      |      |       | ~            | 2     | 6            | 6          |      |                     |