# Single-Chip Fax/Data/Voice Modem

AD1801

#### **FEATURES**

Single-Chip Integrated Fax/Data/Voice Modem Two Channel  $\Sigma\Delta$  ADC and Three Channel  $\Sigma\Delta$  DAC Supports V.34+, V.17 and Fallback Modem/Fax Standards and V.70 DSVD

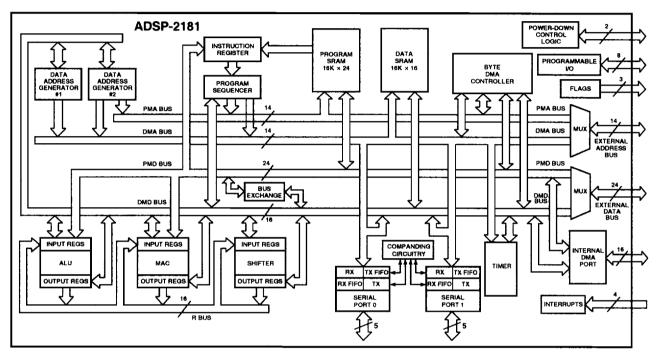

ADSP-21xx 34 MIPS DSP Core with SPORTs and IDMA Controller

16K Words Data Memory (RAM), 20K Words Program Memory (RAM and ROM), 512 Byte CIS RAM PC'97-Compliant Single Function Plug and Play ISA/Multifunction PCMCIA Parallel Interfaces Single 16.9344 MHz Clock Input Two Analog Inputs and Three Analog Outputs Eight Programmable I/O Pins Bidirectional Programmable Interrupt Structure

Three Pin Serial Memory Port Interface/ICE-Port™

Emulator Interface/JTAG Boundary Scan Test Interface

Programmable Gain, Attenuation and Mute

On-Chip Signal Filters

Digital Interpolation and Decimation

Analog Output Low Pass

1 Hz Resolution Programmable Audio (Handset) Sample Rates from 5.4 kHz to 48 kHz, Modem Sample Rates from 5.4 kHz to 48 kHz, with 1 Hz, 8/7 Hz and 10/7 Hz Resolution

128-Lead PQFP and 128-Lead TQFP Packages Operation from Single +5 V Supply Advanced Power Management

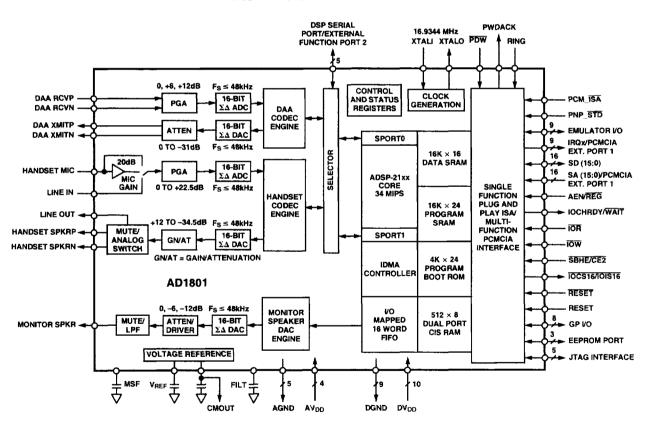

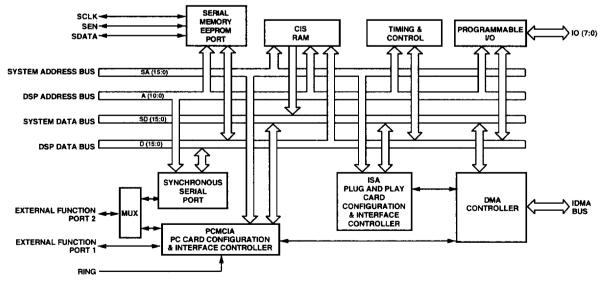

#### **FUNCTIONAL BLOCK DIAGRAM**

ICE-Port is a trademark of Analog Devices, Inc. All other trademarks are the property of their respective holders.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1998

# AD1801—SPECIFICATIONS

| STANDARD | TEST | CONDITIONS | UNLESS | OTHERWISE |

|----------|------|------------|--------|-----------|

| NOTED    |      |            |        |           |

2 mA

25°C Temperature 5.0 V Digital Supply (VDD) Analog Supply (V<sub>CC</sub>) 5.0 V 48 kHz Sample Rate (F<sub>S</sub>) Input Signal 1008 Hz Analog Output Passband 20 Hz to 20 kHz ADC FFT Size 2048 DAC FFT Size 8192  $V_{IH}$ 2.0 V  $V_{IL}$  $0.8 \, \mathrm{V}$  $V_{OH}$ 2.4 V 0.4 V  $V_{OL}$ -2 mA  $I_{OH}$

Output Conditions

Autocalibrated

0 dB Attenuation

0 dB Output Relative to Full Scale

16-Bit Linear Mode 600  $\Omega$  DAA Load 1 k $\Omega$  Handset Load 10 k $\Omega$  Line Out Load

Mute Off

All DAA Transmit and Handset Speaker Specifications

are Measured Differentially

Input Conditions

MIC 20 dB Gain Disabled

Autocalibrated

-1.0 dB Input Relative to Full Scale

16-Bit Linear Mode

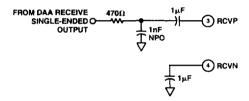

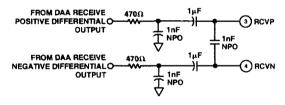

#### DAA RECEIVE PATH

$I_{OL}$

|                                                                             | Min   | Тур         | Max   | Units |

|-----------------------------------------------------------------------------|-------|-------------|-------|-------|

| Full-Scale Input Voltage (RMS Values Assume Sine Wave Input, PGA            |       |             |       |       |

| Gain = 0 dB, Offset Error = 0% of FS)                                       |       |             |       |       |

| DAA Receive Differential Input                                              |       | 2           |       | V rms |

|                                                                             | 4.523 | 5.656       | 6.787 | V p-p |

| Resistance—DAA RCV Input†                                                   | 40    |             |       | kΩ    |

| Capacitance—DAA RCV Input†                                                  |       | 15          |       | pF    |

| Programmable Gain Amplifier (Relative to Full-Scale Input Voltage)          |       | •           |       | Ρ.    |

| Gain = +6 dB                                                                | 5.5   | 6           | 6.5   | dB    |

| Gain = +12 dB                                                               | 11    | 12          | 13    | dB    |

| Analog-to-Digital Converter                                                 |       |             | • •   |       |

| Differential Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale,   |       |             |       |       |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz, PGA Gain = 0 dB)   | 81    | 84          |       | dB    |

| Differential Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale,   | •     | •           |       | 433   |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz, PGA Gain = +6 dB)  | 78    | 81          |       | dB    |

| Differential Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale,   | , ,   | •           |       | 1     |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz, PGA Gain = +12 dB) | 75    | 78          |       | dB    |

| Differential THD+N (-1.0 dB Referenced to Full Scale,                       |       | , ,         | 0.02  | %     |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz)                    |       | -80         | -74   | dB    |

| Differential Signal-to-Intermodulation Distortion† [CCIF Method]            |       | 90          | -80   | dB    |

| Single-Ended Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale,   |       | 20          | 00    | u.D   |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz, PGA Gain = 0 dB    |       |             |       |       |

| [Effectively -6 dB PGA Gain; See Below*])                                   | 81    | 84          |       | dВ    |

| Single-Ended Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale,   | 01    | 01          |       | , un  |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz, PGA Gain = +6 dB   |       |             |       |       |

| [Effectively 0 dB PGA Gain; See Below*])                                    | 78    | 81          |       | dB    |

| Single-Ended Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale,   | 10    | 01          |       | d.b   |

| 4 kHz Analog Output Passband, F <sub>S</sub> = 12.0 kHz, PGA Gain = +12 dB  |       |             |       |       |

| [Effectively +6 dB PGA Gain; See Below*])                                   | 75    | 78          |       | dB    |

| Single-Ended THD+N (-1.0 dB Referenced to Full Scale, 4 kHz                 | .,    | 10          | 0.02  | %     |

| Analog Output Passband, $F_S = 12.0 \text{ kHz}$                            |       | 80          | -74   | dB    |

| Single-Ended Signal-to-Intermodulation Distortion† [CCIF Method]            |       | -90         | -80   | dB    |

| Crosstalk* (DAA RCV Input to Handset MIC/Line Input)                        |       | -90         | -80   | dB    |

| Offset Error (0 V Differential Analog Input)                                |       |             | 60    | d D   |

| PGA Gain = 0 dB                                                             |       | 30          | 100   | LSBs  |

| PGA Gain = +6 dB†                                                           |       | 30          | 100   | LSBs  |

| PGA Gain = +12 dB†                                                          |       | 30          |       | LSBs  |

| run dam - +12 abt                                                           |       | <del></del> |       | Lobs  |

<sup>\*</sup>When the DAA Receive ADC is used in a single-ended input circuit configuration, the user would apply a full-scale input of 1 V rms to RCVP and connect RCVN via a 1 µF capacitor to ground. However, this will result in an output word that is -6 dB down from full scale when the PGA is set for 0 dB, because the ADC input sees half the signal swing compared to when the ADC is driven differentially. Therefore, the effective PGA gain of the ADC, when used single-ended, is 6 dB less than when used differentially. To get a full-scale output with a 1 V rms input, the PGA should be programmed for 6 dB gain, which is an effective single-ended gain of 0 dB.

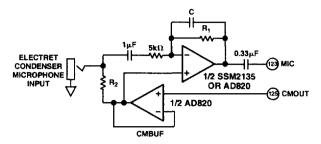

| HANDSET MIC/LINE INPUT PATH                                       |                                      | Min   | Тур           | Max   | Units          |

|-------------------------------------------------------------------|--------------------------------------|-------|---------------|-------|----------------|

| Full-Scale Input Voltage (RMS Values Assume                       | Sine Wave Input)                     |       | 0.1           |       | V rms          |

| Handset MIC Single-Ended Input with +230                          |                                      | 0.226 | 0.1<br>0.2828 | 0.339 | V p-p<br>V rms |

| Handset MIC Single-Ended Input with 0 and                         | Gain                                 | 2.26  | 2.828         | 3.39  | V p-p<br>V rms |

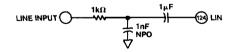

| Line Single-Ended Input                                           |                                      | 2.26  | 2.828         | 3.39  | V p-p<br>kΩ    |

| Resistance—Handset MIC Input                                      |                                      | 20    |               |       | kΩ             |

| Resistance—Line Input†                                            |                                      | 20    | 15            |       | pF             |

| Capacitance—Handset MIC, LINE Input†                              | - m 4)                               |       | 1.5           |       | dB             |

| Programmable Gain Amplifier Step Size (0 dB Gain Range Span†      | to 22.5 dB) (All Steps Tested)       | 21.5  | 22.5          | 23.5  | dB             |

| Analog-to-Digital Converter  Dynamic Range (-60 dB Input, THD+N & | eferenced to Full Scale, A-Weighted) | 70    | 83            | 0.03  | dB<br>%        |

| THD+N (-1.0 dB Referenced to Full Sca                             | (le)                                 | 1     | 80            | -70   | dB             |

|                                                                   | •                                    | }     | -100          | -80   | dB             |

| Signal-to-Intermodulation Distortion† [CC                         | IF Method]                           |       |               | -80   | dB             |

| Crosstalk† (Handset MIC/Line Input to D                           | A RCV Input)                         | {     | 400           | 2048  | LSBs           |

| Offset Error (Relative to Full-Scale Analog                       | Input, PGA Gain = 0 dB)              |       |               |       |                |

## DAA TRANSMIT PATH

|                                                                  |                                                    | TARKE |

|------------------------------------------------------------------|----------------------------------------------------|-------|

|                                                                  |                                                    |       |

| Digital-to-Analog Converter Dynamic Range (-60 dB Input, THD+N I | deferenced to Full Scale,                          |       |

| 4 kHz Analog Output Passband, Output                             | $C_{cin} = 0 dR$ $F_{c} = 12.0 \text{ kHz}$        | 81    |

| THD+N (-1.0 dB Referenced to Full Scale                          | e, 4 kHz Analog Output Passband,                   |       |

| Output Gain = 0 dB, $F_S = 12.0 \text{ kHz}$                     | <b>2,</b> 2 2                                      |       |

| Signal-to-Intermodulation Distortion ICI                         | IF Method]                                         |       |

| Crosstalk† (DAA XMIT Output to Handi                             | ci Speaker/Line Output)                            |       |

| Total Out-of-Band Energy† (Measured for                          | $\cdot$ ca $0.555 \times F_S$ to $100 \text{ kHz}$ |       |

| Audible Out-of-Band Energy†                                      | 0.01-IIr)                                          | 1     |

| (Measured from $0.555 \times F_S$ to 22 kHz,                     | Fested at $F_s = 8.0 \text{ kHz}$ )                | 1     |

| Common-Mode DC Offset (Referenced to                             | Coltage Reference [CMOUT] Output)                  | 1     |

| Differential DC Offset                                           |                                                    |       |

| Programmable Attenuator                                          | · 1\                                               | 0.4   |

| Step Size (0 dB to -31.0 dB) (All Steps                          | Tested)                                            | 30.   |

| Output Attenuation Span†                                         |                                                    | 1     |

| Full-Scale Output Voltage                                        | .t) DAA XMIT Differential Output                   |       |

| (RMS Values Assume Sine Wave Outp                                | (ii) DAN MILL Dan                                  | 5.1   |

| Output Source Impedance—DAA XMIT†                                |                                                    | 60    |

| External Load Impedance—DAA XMIT                                 |                                                    |       |

| Pin Capacitance—DAA XMIT†                                        |                                                    | 1     |

| Load Capacitance—DAA XMIT†                                       |                                                    |       |

|                                                                                                                                      | 3.51  | Тур                        | Max                               | Units                           |

|--------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|-----------------------------------|---------------------------------|

|                                                                                                                                      | Min   | 1 JP                       |                                   |                                 |

| eferenced to Full Scale, Gain = 0 dB, F <sub>S</sub> = 12.0 kHz) , 4 kHz Analog Output Passband, EIF Method] EI Speaker/Line Output) | 81    | 90<br>-78.5<br>-90<br>-100 | 0.016<br>-74<br>-80<br>-80<br>-60 | dB<br>%<br>dB<br>dB<br>dB<br>dB |

| Tested at $F_S = 8.0 \text{ kHz}$ )  Tested at $F_S = 8.0 \text{ kHz}$ )  Tologogy Reference [CMOUT] Output)                         |       | 20<br>10                   | -80<br>50                         | dB<br>mV<br>mV                  |

| Tested)                                                                                                                              | 0.487 | 1.0<br>31.0                | 1.513<br>31.513                   | dB<br>dB                        |

| .t) DAA XMIT Differential Output                                                                                                     | 5.1   | 2.121<br>6.0               | 6.9<br><2                         | V rms<br>V p-p<br>Ω             |

|                                                                                                                                      | 600   |                            | 15<br>100                         | pF<br>pF                        |

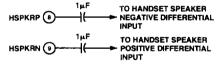

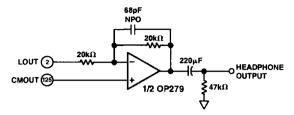

## HANDSET SPEAKER/LINE OUTPUT PATH

|                                                                          | Min  | Тур   | Max  | Units    |

|--------------------------------------------------------------------------|------|-------|------|----------|

| Digital-to-Analog Converter                                              |      |       |      |          |

| Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale, A-Weighted) | 78   | 86    |      | dB       |

| THD+N (-1.0 dB Referenced to Full Scale)                                 |      |       | 0.03 | %        |

|                                                                          |      | 83    | -70  | dB       |

| Signal-to-Intermodulation Distortion† [CCIF Method]                      |      | -90   | -80  | dB       |

| DAC Crosstalk† (Handset Speaker/Line Output to DAA XMIT Output)          |      | -100  | -80  | dB       |

| Total Out-of-Band Energy† (Measured from $0.6 \times F_S$ to 100 kHz)    |      |       | -60  | dB       |

| Audible Out-of-Band Energy†                                              |      |       |      |          |

| (Measured from $0.6 \times F_S$ to 22 kHz, Tested at $F_S = 8.0$ kHz)    |      |       | -80  | dB       |

| Handset Speaker Common-Mode DC Offset (Relative to Voltage Reference     |      |       |      |          |

| [CMOUT] Output)                                                          |      | 20    |      | mV       |

| Line Output Common-Mode DC Offset (Relative to Voltage Reference         | 1    |       |      |          |

| [CMOUT] Output)                                                          |      | 40    |      | mV       |

| Differential DC Offset                                                   |      | 10    | 50   | mV       |

| Programmable Amplifier/Attenuator                                        |      |       |      |          |

| Step Size (+12.0 dB to -34.5 dB) (All Steps Tested)                      | 1.0  | 1.5   | 2.0  | dB       |

| Output Attenuation Span†                                                 | 43.5 | 46.5  | 49.5 | dB       |

| Mute Attenuation†                                                        | İ    | -100  |      | dB       |

| Full-Scale Output Voltage                                                |      |       |      |          |

| (RMS Values Assume Sine Wave Output)                                     |      |       |      |          |

| Handset Speaker Differential Output                                      |      | 1.414 |      | V rms    |

| •                                                                        | 3.1  | 4.0   | 4.8  | V p-p    |

| Line Out Single-Ended Output (10 kΩ Load)                                |      | 0.707 |      | Vrms     |

| • ( )                                                                    | 1.56 | 2.0   | 2.44 | V p-p    |

| Output Source Impedance—Handset Speaker†                                 |      |       | <2   | $\Omega$ |

| Output Source Impedance—Line Out†                                        |      | 400   | 600  | Ω        |

| External Load Impedance—Handset Speaker                                  | 1    | 1.2   |      | kΩ       |

| External Load Impedance—Line Out†                                        | 10   |       |      | kΩ       |

| Pin Capacitance—Handset Speaker                                          |      |       | 15   | pF       |

| Pin Capacitance—Line Out†                                                |      |       | 15   | pF       |

| Load Capacitance—Handset Speaker†                                        |      |       | 100  | pF       |

| Load Capacitance—Line Out†                                               |      |       | 100  | pF       |

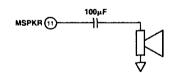

## MONITOR SPEAKER PATH

|                                                                          | Min     | Typ   | Max     | Units |

|--------------------------------------------------------------------------|---------|-------|---------|-------|

| Digital-to-Analog Converter                                              |         |       |         |       |

| THD+N (Referenced to Full Scale)                                         |         | 0.316 | 1.0     | %     |

|                                                                          |         | -50   | -40     | dB    |

| Dynamic Range (-60 dB Input, THD+N Referenced to Full Scale, A-Weighted) |         | 50    |         | dB    |

| Programmable Attenuator                                                  |         |       |         |       |

| Step Size (0 dB, -6 dB, -12 dB) (All Steps Tested)                       | -6.513  | 6     | -5.487  | dB    |

| Output Attenuation Span†                                                 | -12.513 | -12   | -11.487 | dB    |

| Mute Attenuation†                                                        |         | -80   |         | dB    |

| Full-Scale Output Voltage                                                |         |       |         | j     |

| (RMS Values Assume Sine Wave Output) Monitor Speaker Output              |         | 0.707 |         | V rms |

|                                                                          | 1.7     | 2.0   | 2.3     | V p-p |

| Output Source Impedance-Monitor Speaker†                                 |         |       | <1      | Ω     |

| External Load Impedance—Monitor Speaker†                                 | 8       |       |         | Ω     |

| Pin Capacitance—Monitor Speaker†                                         |         |       | 15      | pF    |

| Load Capacitance—Monitor Speaker†                                        |         |       | 100     | pF    |

#### DIGITAL DECIMATION AND INTERPOLATION FILTERS-MODEM MODE 0†

|                                        | Min Typ              | Max                | Units |

|----------------------------------------|----------------------|--------------------|-------|

| Passband Edge (-0.220 dB Point)        | 0                    | $0.445 \times F_S$ | Hz    |

| Passband (-3.0 dB Point)               | 0                    | $0.490 \times F_S$ | Hz    |

| Passband Ripple                        | 0                    | -0.17              | dB    |

| Transition Band                        | $0.445 \times F_S$   | $0.555 \times F_S$ | Hz    |

| Stopband Edge <sup>1</sup>             | $0.555 \times F_{S}$ |                    | Hz    |

| Stopband Rejection (Plus 3 dB Rolloff) | 78.0                 |                    | dB    |

| Group Delay                            |                      | 19/F <sub>S</sub>  | s     |

| Group Delay Variation Over Passband    |                      | 0.0                | μs    |

| Sample Rate                            |                      | 48                 | kHz   |

#### DIGITAL DECIMATION AND INTERPOLATION FILTERS-MODEM MODE 1†

|                                        | Min Typ              | Max                | Units |

|----------------------------------------|----------------------|--------------------|-------|

| Passband Edge (-0.24 dB Point)         | 0                    | $0.400 \times F_S$ | Hz    |

| Passband (-3.0 dB Point)               | 0                    | $0.453 \times F_S$ | Hz    |

| Passband Ripple                        | 0                    | -0.24              | dB    |

| Transition Band                        | $0.400 \times F_{S}$ | $0.555 \times F_S$ | Hz    |

| Stopband Edge <sup>2</sup>             | $0.555 \times F_{S}$ |                    | Hz    |

| Stopband Rejection (Plus 3 dB Rolloff) | 52.8                 |                    | dB    |

| Group Delay                            |                      | $10/\mathbf{F_S}$  | s     |

| Group Delay Variation Over Passband    |                      | 0.0                | μs    |

| Sample Rate                            |                      | 48                 | kHz   |

#### DIGITAL DECIMATION AND INTERPOLATION FILTERS—AUDIO MODE†

|                                        | Min Typ              | Max                | Units |

|----------------------------------------|----------------------|--------------------|-------|

| Passband Edge (-0.18 dB Point)         | 0                    | $0.400 \times F_S$ | Hz    |

| Passband (-3.0 dB Point)               | 0                    | $0.462 \times F_S$ | Hz    |

| Passband Ripple                        | 0 .                  | -0.18              | dB    |

| Transition Band                        | $0.400 \times F_S$   | $0.600 \times F_S$ | Hz    |

| Stopband Edge <sup>3</sup>             | $0.600 \times F_{S}$ |                    | Hz    |

| Stopband Rejection (Plus 3 dB Rolloff) | 78.0                 |                    | dB    |

| Group Delay                            |                      | $11/F_S$           | s     |

| Group Delay Variation Over Passband    |                      | 0.0                | μs    |

| Sample Rate                            |                      | 48                 | kHz   |

#### DIGITAL INTERPOLATION FILTERS—MONITOR SPEAKER†

|                                         | Min Typ            | Max                | Units |  |

|-----------------------------------------|--------------------|--------------------|-------|--|

| Passband Edge (-0.74 dB Point)          | 0                  | $0.350 \times F_S$ | Hz    |  |

| Passband (-3.0 dB Point)                | 0                  | $0.412 \times F_S$ | Hz    |  |

| Passband Ripple                         | 0                  | -0.74              | dB    |  |

| Transition Band                         | $0.350 \times F_S$ | $0.650 \times F_S$ | Hz    |  |

| Stopband Edge <sup>4</sup>              | $0.650 \times F_S$ |                    | Hz    |  |

| Stopband Rejection (Plus 12 dB Rolloff) | 55.5               |                    | dB    |  |

| Group Delay                             |                    | $10/F_S$           | s     |  |

| Group Delay Variation Over Passband     |                    | 0.0                | μs    |  |

| Sample Rate                             |                    | 48                 | kHz   |  |

### NOTES

Specifications subject to change without notice.

REV. 0 -5-

<sup>&</sup>lt;sup>1</sup>The stopband repeats itself at multiples of  $64 \times F_S$  where  $F_S$  is the sampling frequency. Thus the modem mode 0 digital filter will attenuate to -78.0 dB or better across the frequency spectrum, except for a range  $\pm 0.555 \times F_S$  wide at multiples of  $64 \times F_S$ .

<sup>&</sup>lt;sup>2</sup>The stopband repeats itself at multiples of  $64 \times F_S$  where  $F_S$  is the sampling frequency. Thus the modem mode 1 digital filter will attenuate to -52.8 dB or better across the frequency spectrum, except for a range  $\pm 0.555 \times F_S$  wide at multiples of  $64 \times F_S$ .

The stopband repeats itself at multiples of  $64 \times F_5$  where  $F_5$  is the sampling frequency. Thus the audio mode digital filter will attenuate to -78.0 dB or better across the frequency spectrum, except for a range  $\pm 0.600 \times F_5$  wide at multiples of  $64 \times F_5$ .

The stopband repeats itself at multiples of  $64 \times F_S$  where  $F_S$  is the sampling frequency. Thus the audio mode digital filter will attenuate to -55.5 dB or better across the frequency spectrum, except for a range  $\pm 0.650 \times F_S$  wide at multiples of  $64 \times F_S$ .

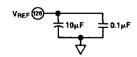

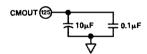

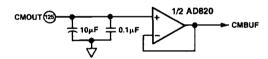

## **VOLTAGE REFERENCE**

|                              | Min | Typ  | Max | Units |

|------------------------------|-----|------|-----|-------|

| CMOUT                        | 2.0 | 2.45 | 2.7 | V     |

| External CMOUT Load Current† |     |      | 10  | μA    |

| CMOUT Output Impedance†      |     | 4    |     | kΩ    |

## SYSTEM SPECIFICATIONS

|                                                         | Min | Typ | Max  | Units   |

|---------------------------------------------------------|-----|-----|------|---------|

| System Frequency Response Ripple† (Line In to Line Out) |     |     | ±0.5 | dB      |

| Differential Nonlinearity†                              |     |     | ±1   | Bit     |

| Phase Linearity Deviation†                              |     |     | 5    | Degrees |

## STATIC DIGITAL SPECIFICATIONS

|                                              | Min  | Typ | Max             | Units |

|----------------------------------------------|------|-----|-----------------|-------|

| High-Level Input Voltage (VIH)               |      |     |                 |       |

| Digital Inputs, Except XTALI                 | 2.0  |     | $DV_{DD} + 0.3$ | V     |

| XTALI                                        | 3.5  |     | $DV_{DD} + 0.3$ | V     |

| Low-Level Input Voltage (VIL)                | ļ    |     |                 |       |

| Digital Inputs, Except XTALI                 | -0.3 |     | 0.8             | V     |

| XTALI                                        | -0.3 |     | 1.5             | V     |

| High-Level Output Voltage (V <sub>OH</sub> ) | 2.4  |     |                 | V     |

| Low-Level Output Voltage (VOL)               |      |     | 0.4             | V     |

| Input Leakage Current (GO/NOGO Tested)       | -10  |     | 10              | μΑ    |

| Output Leakage Current (GO/NOGO Tested)      | -10  |     | 10              | μA    |

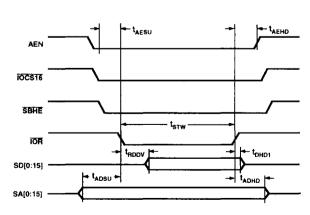

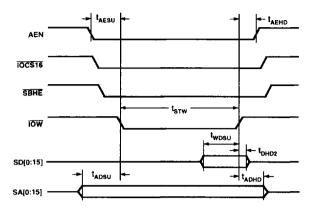

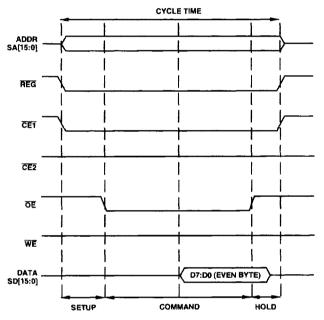

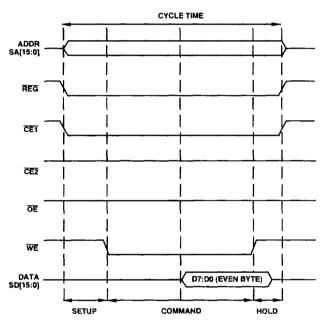

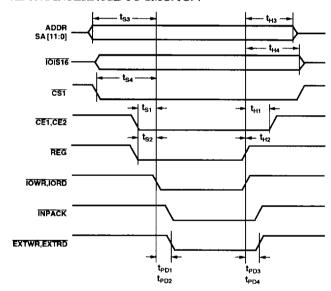

TIMING PARAMETERS (Guaranteed Over Operating Temperature and Digital Supply Range)

|                                                              | Min | Typ | Max | Units |

|--------------------------------------------------------------|-----|-----|-----|-------|

| RESET LO Pulse Width (t <sub>RPWL</sub> )                    | 100 |     |     | ns    |

| IOR/IOW Strobe Width (t <sub>STW</sub> )                     | 100 |     |     | ns    |

| AEN Setup to <del>IOR/IOW</del> Falling (t <sub>AESU</sub> ) | 10  |     |     | ns    |

| AEN Hold from IOR/IOW Rising (t <sub>AEHD</sub> )            | 0   |     |     | ns    |

| Address Setup to IOR/IOW Falling (t <sub>ADSU</sub> )        | 10  |     |     | ns    |

| Address Hold from IOR/IOW Rising (t <sub>ADHD</sub> )        | 0   |     |     | ns    |

| Data Hold from IOR Rising (t <sub>DHD1</sub> )               |     |     | 20  | ns    |

| Data Hold from IOW Rising (t <sub>DHD2</sub> )               | 15  |     |     | ns    |

| IOR Falling to Valid Read Data (t <sub>RDDV</sub> )          | į   |     | 40  | ns    |

| Write Data Setup to IOW Rising (twosu)                       | 10  |     |     | ns    |

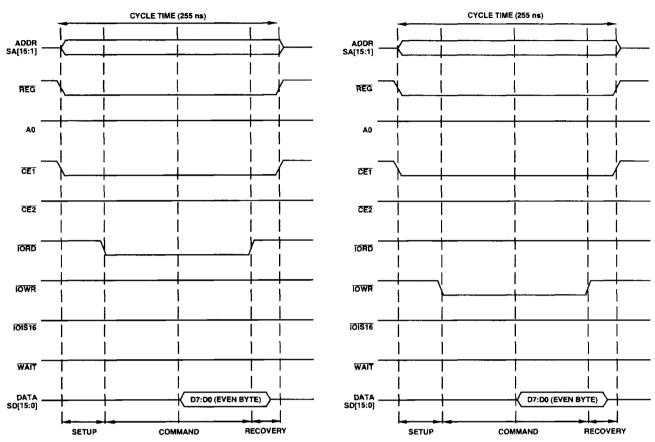

Figure 2. ISA PIO Read Cycle

Figure 3. ISA PIO Write Cycle

## POWER SUPPLY

|                                                                                                   | Min  | Тур | Max  | Units |

|---------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Power Supply Range—AV <sub>DD</sub> and DV <sub>DD</sub>                                          | 4.75 |     | 5.25 | V     |

| Power Supply Current—5.0 AV <sub>DD</sub> and DV <sub>DD</sub> Operating                          |      | 175 | 250  | mA    |

| Power Supply Current—5.0 AV <sub>DD</sub> and DV <sub>DD</sub> Power-Down                         |      |     | 40   | mA    |

| Power Dissipation—5.0 AV <sub>DD</sub> and DV <sub>DD</sub> Operating (Current × Nominal Supply)  |      |     | 1000 | mW    |

| Power Dissipation—5.0 AV <sub>DD</sub> and DV <sub>DD</sub> Power-Down (Current × Nominal Supply) |      |     | 200  | mW    |

| Power Supply Rejection (100 mV p-p Signal @ 1 kHz)†                                               |      |     |      | ľ     |

| (At Both Analog and Digital Supply Pins, for ADC and DAC)                                         | 40   |     |      | dB    |

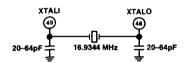

## **CLOCK SPECIFICATIONS**†

|                                                                                   | Min   | Тур     | Max   | Units |

|-----------------------------------------------------------------------------------|-------|---------|-------|-------|

| Input Crystal/Clock Frequency                                                     | ,     | 16.9344 |       | MHz   |

| Input Clock Duty Cycle (When an External Clock Is Used Instead of a Crystal)      | 25/75 |         | 75/25 | %     |

| Initialization Sample Rate Change Time (Neglecting Pipeline Delay of ≈ 1/4 Sample |       |         |       |       |

| Period)                                                                           |       |         | 0     | ms    |

REV. 0 -7-

<sup>†</sup>Guaranteed, not tested.

Specifications subject to change without notice.

#### PACKAGE CHARACTERISTICS

|                                          | Тур  | Units |

|------------------------------------------|------|-------|

| PQFP θ <sub>IA</sub> (Thermal Resistance |      |       |

| [Junction-to-Ambient])                   | 35.9 | °C/W  |

| PQFP θ <sub>IC</sub> (Thermal Resistance |      |       |

| [Junction-to-Case])                      | 8.38 | °C/W  |

| TQFP θ <sub>IA</sub> (Thermal Resistance |      |       |

| [Junction-to-Ambient])                   | 36.1 | °C/W  |

| TQFP θ <sub>IC</sub> (Thermal Resistance |      |       |

| [Junction-to-Case])                      | 3.81 | °C/W  |

#### **ABSOLUTE MAXIMUM RATINGS\***

The AD1801 analog and digital power pins (AV $_{\rm DD}$ ) and DV $_{\rm DD}$ ) must be powered by the same supply. The analog and digital power pins must always be at the same dc potential, or the AD1801 could be permanently damaged.

|                                     | Min          | Max             | Units |

|-------------------------------------|--------------|-----------------|-------|

| Power Supply                        |              |                 |       |

| Digital (V <sub>DD</sub> )          | -0.3         | 6.0             | V     |

| Analog (V <sub>CC</sub> )           | -0.3<br>-0.3 | 6.0             | V     |

| Input Current                       |              |                 |       |

| (Except Supply Pins)                |              | ±10.0           | mA    |

| Analog Input Voltage (Signal Pins)  | -0.3         | $AV_{DD} + 0.3$ | V     |

| Digital Input Voltage (Signal Pins) | -0.3         | $DV_{DD} + 0.3$ | V     |

| Ambient Temperature (Operating)     | 0            | +85             | °C    |

| Storage Temperature                 | -65          | +150            | °C    |

<sup>\*</sup>Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

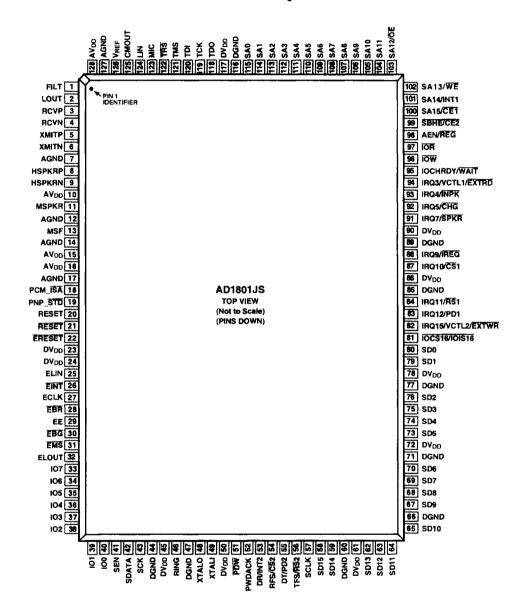

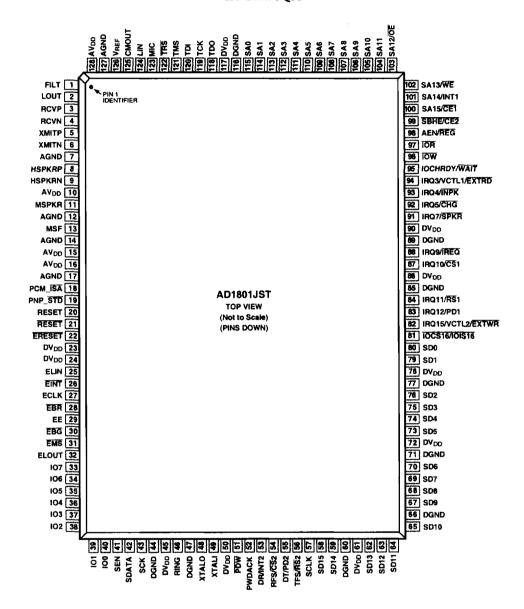

#### **ORDERING GUIDE**

| Model          | Temperature  | Package       | Package              |

|----------------|--------------|---------------|----------------------|

|                | Range        | Description   | Options*             |

| AD1801JS       | 0°C to +85°C | 128-Lead PQFP | S-128A               |

| AD1801JST      | 0°C to +85°C | 128-Lead TQFP | ST-128               |

| AD1801JST-REEL | 0°C to +85°C | 128-Lead TQFP | ST-128 Tape and Reel |

<sup>\*</sup>S = Plastic Quad Flatpack; ST = Thin Quad Flatpack.

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1801 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

\_8\_ REV. 0

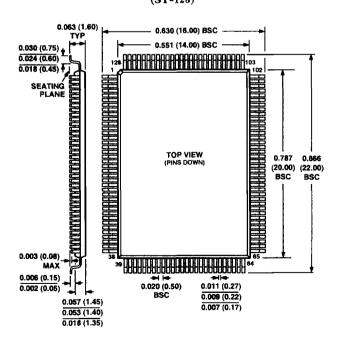

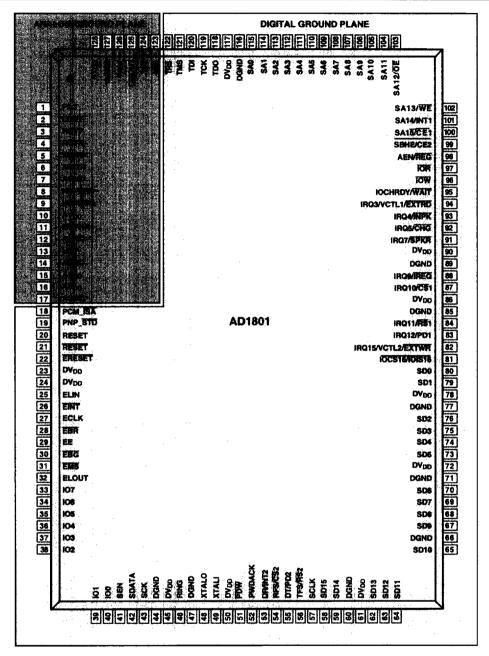

#### PIN CONFIGURATION

#### S-128A 128-Lead PQFP

REV. 0 -9-

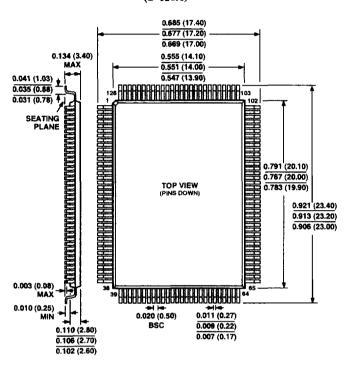

#### PIN CONFIGURATION

#### ST-128 128-Lead TQFP

## PIN FUNCTION DESCRIPTIONS

| Device | Configuration | Signals |

|--------|---------------|---------|

|        |               |         |

| Pin Name | PQFP | TQFP | I/O | Description                                                                                                                                                                                                                                                                                                                                                                      |

|----------|------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCM_ISA  | 18   | 18   | I   | PCMCIA or ISA Host PC Bus Select Control. This pin has a weak internal pull-up device. See below for more information.                                                                                                                                                                                                                                                           |

| PNP_STD  | 19   | 19   | I   | PnP or Standard Mode Select Control. When the AD1801 is configured in PCMCIA mode (i.e., when the PCM_ISA pin is HI), then the PNP_STD pin can be used as a general purpose input. The PNP_STDZ register bit can be used to monitor the state of this general purpose input under those conditions. This pin has a weak internal pull-up device. See below for more information. |

## DSP Core ICE-Port Emulator Interface

| Pin Name      | PQFP | TQFP | I/O | Description             |

|---------------|------|------|-----|-------------------------|

| EE            | 29   | 29   | I   | Emulator Enable.        |

| EBR           | 28   | 28   | I   | Emulator Bus Request.   |

| <b>EBG</b>    | 30   | 30   | 0   | Emulator Bus Grant.     |

| <b>ERESET</b> | 22   | 22   | I   | Emulator Reset.         |

| <b>EMS</b>    | 31   | 31   | 0   | Emulator Memory Select. |

| <b>EINT</b>   | 26   | 26   | I   | Emulator Interrupt.     |

| ECLK          | 27   | 27   | I   | Emulator Clock.         |

| ELIN          | 25   | 25   | I   | Emulator Input.         |

| ELOUT         | 32   | 32   | 0   | Emulator Output.        |

## **Ring Indicator**

| Pin Name | PQFP | TQFP | I/O | Description           |

|----------|------|------|-----|-----------------------|

| RING     | 46   | 46   | I   | Phone Ring Indicator. |

#### I/O Port

| Pin Name | PQFP | TQFP | I/O   | Description                                                                                                         |

|----------|------|------|-------|---------------------------------------------------------------------------------------------------------------------|

| IO7      | 33   | 33   | I/O/Z | DSP Controlled Programmable I/O Bit 7. This pin has a weak internal pull-up device. See below for more information. |

| IO6      | 34   | 34   | I/O/Z | DSP Controlled Programmable I/O Bit 6. This pin has a weak internal pull-up device. See below for more information. |

| IO5      | 35   | 35   | I/O/Z | DSP Controlled Programmable I/O Bit 5. This pin has a weak internal pull-up device. See below for more information. |

| IO4      | 36   | 36   | I/O/Z | DSP Controlled Programmable I/O Bit 4. This pin has a weak internal pull-up device. See below for more information. |

| IO3      | 37   | 37   | I/O/Z | DSP Controlled Programmable I/O Bit 3. This pin has a weak internal pull-up device. See below for more information. |

| IO2      | 38   | 38   | I/O/Z | DSP Controlled Programmable I/O Bit 2. This pin has a weak internal pull-up device. See below for more information. |

| 101      | 39   | 39   | I/O/Z | DSP Controlled Programmable I/O Bit 1. This pin has a weak internal pull-up device. See below for more information. |

| IO0      | 40   | 40   | I/O/Z | DSP Controlled Programmable I/O Bit 0. This pin has a weak internal pull-up device. See below for more information. |

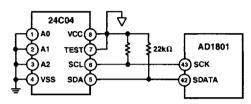

## Serial Memory (EEPROM) Port

| Pin Name | PQFP | TQFP | 1/0   | Description                                                                                              |

|----------|------|------|-------|----------------------------------------------------------------------------------------------------------|

| SCK      | 43   | 43   | I/O/Z | Serial Data Clock. This pin has a weak internal pull-up device. See below for more information.          |

| SEN      | 41   | 41   | I/O/Z | Serial Data Enable Control. This pin has a weak internal pull-up device. See below for more information. |

| SDATA    | 42   | 42   | I/O/Z | Bidirectional Serial Data. This pin has a weak internal pull-up device. See below for more information.  |

REV. 0 -11-

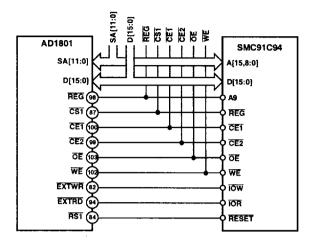

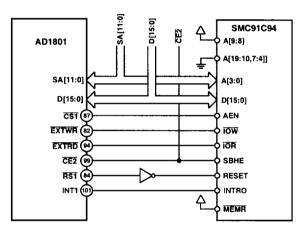

ISA Interface/PCMCIA Interface

| Pin Name                                                                      | PQFP                                             | TQFP                                     | 1/0                              | Description                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD15                                                                          | 58                                               | 58                                       | I/O/Z                            | System Data Bus Bit 15.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD14                                                                          | 59                                               | 59                                       | I/O/Z                            | System Data Bus Bit 14.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD13                                                                          | 62                                               | 62                                       | I/O/Z                            | System Data Bus Bit 13.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD12                                                                          | 63                                               | 63                                       | I/O/Z                            | System Data Bus Bit 12.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD11                                                                          | 64                                               | 64                                       | I/O/Z                            | System Data Bus Bit 11.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD10                                                                          | 65                                               | 65                                       | I/O/Z                            | System Data Bus Bit 10.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD9                                                                           | 67                                               | 67                                       | I/O/Z                            | System Data Bus Bit 9.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD8                                                                           | 68                                               | 68                                       | I/O/Z                            | System Data Bus Bit 8.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD7                                                                           | 69                                               | 69                                       | I/O/Z                            | System Data Bus Bit 7.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD6                                                                           | 70                                               | 70                                       | I/O/Z                            | System Data Bus Bit 6.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD5                                                                           | 73                                               | 73                                       | I/O/Z                            | System Data Bus Bit 5.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD4                                                                           | 74                                               | 74                                       | I/O/Z                            | System Data Bus Bit 4                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD3                                                                           | 75                                               | 75                                       | I/O/Z                            | System Data Bus Bit 3.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD2                                                                           | 76                                               | 76                                       | I/O/Z                            | System Data Bus Bit 2.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD1                                                                           | 79                                               | 79                                       | I/O/Z                            | System Data Bus Bit 1.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SD0                                                                           | 80                                               | 80                                       | I/O/Z                            | System Data Bus Bit 0.                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA11                                                                          | 104                                              | 104                                      | I                                | System Address Bus Bit 11.                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA10                                                                          | 105                                              | 105                                      | Ĭ                                | System Address Bus Bit 11.                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA9                                                                           | 106                                              | 106                                      | Ī                                | System Address Bus Bit 9.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA8                                                                           | 107                                              | 107                                      | Ī                                | System Address Bus Bit 8.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA7                                                                           | 108                                              | 108                                      | Î                                | System Address Bus Bit 7.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA6                                                                           | 109                                              | 109                                      | I                                | System Address Bus Bit 6.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA5                                                                           | 110                                              | 110                                      | Ï                                | System Address Bus Bit 5.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA4                                                                           | 111                                              | 111                                      | Ĭ                                | System Address Bus Bit 4.                                                                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SA3                                                                           | 1112                                             | 112                                      | I                                | System Address Bus Bit 4.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA2                                                                           | 113                                              | 113                                      | I                                | System Address Bus Bit 2.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SAI                                                                           | 114                                              | 114                                      | I                                | System Address Bus Bit 1.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SA0                                                                           | 115                                              | 115                                      | I                                | System Address Bus Bit 1.                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IOR                                                                           | 97                                               | 97                                       | I                                | System I/O Read Strobe.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IOW                                                                           | 96                                               | 96                                       | I                                | System I/O Write Strobe.                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin Name                                                                      | PQFP                                             | TQFP                                     | I/O                              |                                                                                                                                                                                                                                                                                                                                                                  | DCMCIA Decembrian                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IOCS16/IOIS16                                                                 | <del>                                     </del> |                                          |                                  | ISA Description                                                                                                                                                                                                                                                                                                                                                  | PCMCIA Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                               | 81                                               | 81                                       | O/Z                              | System 16-Bit I/O Card<br>Indicator.                                                                                                                                                                                                                                                                                                                             | System 16-Bit I/O Card Indicator.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SA12/OE                                                                       | 103                                              | 103                                      | I                                | System Address Bus Bit 12.                                                                                                                                                                                                                                                                                                                                       | System Attribute Space Read Control.                                                                                                                                                                                                                                                                                                                                                                                                                                    |