# 512K x 24 Static RAM

#### **Features**

- · High speed

- $-t_{AA} = 8 \text{ ns}$

- · Low active power

- 1080 mW (max.)

- Operating voltages of 3.3 ± 0.3V

- · 2.0V data retention

- Automatic power-down when deselected

- · TTL-compatible inputs and outputs

- Easy memory expansion with CE<sub>0</sub>, CE<sub>1</sub> and CE<sub>2</sub> features

- Available in non Pb-free 119 ball PBGA.

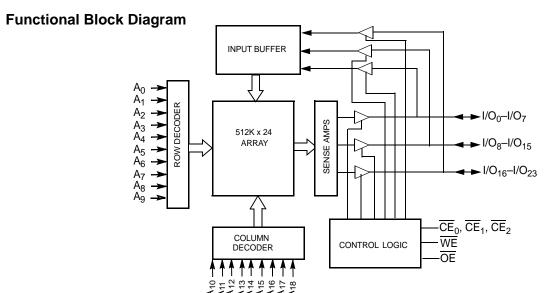

#### **Functional Description**

The CY7C1012AV33 is a high-performance CMOS static RAM organized as 512K words by 24 bits. Each data byte is separately controlled by the individual chip selects (CE $_0$ , CE $_1$ , CE $_2$ ). CE $_0$  controls the data on the I/O $_0$ –I/O $_7$ , while CE $_1$  controls the data on I/O $_8$ –I/O $_1$ , and CE $_2$  controls the data on the data on the data on automatic

power-down feature that significantly reduces power consumption when deselected.

Writing the data bytes into the SRAM is accomplished when the chip select controlling that byte is LOW and the write enable input (WE) input is LOW. Data on the respective input/output (I/O) pins is then written into the location specified on the address pins ( $A_0$ – $A_{18}$ ). Asserting all of the chip selects LOW and write enable LOW will write all 24 bits of data into the SRAM. Output enable ( $\overline{OE}$ ) is ignored while in WRITE mode.

Data bytes can also be individually read from the device. Reading a byte is accomplished when the chip select controlling that byte is LOW and write enable (WE) HIGH while output enable (OE) remains LOW. Under these conditions, the contents of the memory location specified on the address pins will appear on the specified data input/output (I/O) pins. Asserting all the chip selects LOW will read all 24 bits of data from the SRAM.

The 24 I/O pins (I/O $_0$ –I/O $_2$ 3) are placed in a high-impedance state when all the chip selects are HIGH or when the output enable ( $\overline{\text{OE}}$ ) is HIGH during a READ mode. For further details, refer to the truth table of this data sheet.

The CY7C1012AV33 is available in a standard 119-ball PBGA.

#### **Selection Guide**

|                              |                       | -8  | <b>–10</b> | Unit |

|------------------------------|-----------------------|-----|------------|------|

| Maximum Access Time          |                       | 8   | 10         | ns   |

| Maximum Operating Current    | Commercial            | 300 | 275        | mA   |

|                              | Industrial            | 300 | 275        |      |

| Maximum CMOS Standby Current | Commercial/Industrial | 50  | 50         | mA   |

# Pin Configurations<sup>[1, 2]</sup>

#### **119 PBGA Top View**

|   | 1                 | 2        | 3               | 4               | 5               | 6        | 7                 |

|---|-------------------|----------|-----------------|-----------------|-----------------|----------|-------------------|

| Α | NC                | Α        | А               | Α               | А               | Α        | NC                |

| В | NC                | Α        | А               | CE <sub>0</sub> | А               | Α        | NC                |

| С | I/O <sub>12</sub> | NC       | CE <sub>1</sub> | NC              | CE <sub>2</sub> | NC       | I/O <sub>0</sub>  |

| D | I/O <sub>13</sub> | $V_{DD}$ | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | $V_{DD}$ | I/O <sub>1</sub>  |

| E | I/O <sub>14</sub> | $V_{SS}$ | $V_{DD}$        | V <sub>SS</sub> | $V_{DD}$        | $V_{SS}$ | I/O <sub>2</sub>  |

| F | I/O <sub>15</sub> | $V_{DD}$ | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | $V_{DD}$ | I/O <sub>3</sub>  |

| G | I/O <sub>16</sub> | $V_{SS}$ | $V_{DD}$        | V <sub>SS</sub> | $V_{DD}$        | $V_{SS}$ | I/O <sub>4</sub>  |

| Н | I/O <sub>17</sub> | $V_{DD}$ | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | $V_{DD}$ | I/O <sub>5</sub>  |

| J | NC                | $V_{SS}$ | $V_{DD}$        | V <sub>SS</sub> | $V_{DD}$        | $V_{SS}$ | DNU               |

| K | I/O <sub>18</sub> | $V_{DD}$ | $V_{SS}$        | $V_{SS}$        | $V_{SS}$        | $V_{DD}$ | I/O <sub>6</sub>  |

| L | I/O <sub>19</sub> | $V_{SS}$ | $V_{DD}$        | V <sub>SS</sub> | $V_{DD}$        | $V_{SS}$ | I/O <sub>7</sub>  |

| М | I/O <sub>20</sub> | $V_{DD}$ | V <sub>SS</sub> | V <sub>SS</sub> | V <sub>SS</sub> | $V_{DD}$ | I/O <sub>8</sub>  |

| N | I/O <sub>21</sub> | $V_{SS}$ | $V_{DD}$        | $V_{SS}$        | $V_{DD}$        | $V_{SS}$ | I/O <sub>9</sub>  |

| Р | I/O <sub>22</sub> | $V_{DD}$ | $V_{SS}$        | V <sub>SS</sub> | V <sub>SS</sub> | $V_{DD}$ | I/O <sub>10</sub> |

| R | I/O <sub>23</sub> | Α        | NC              | NC              | NC              | Α        | I/O <sub>11</sub> |

| Т | NC                | Α        | Α               | WE              | Α               | Α        | NC                |

| U | NC                | Α        | А               | ŌĒ              | А               | Α        | NC                |

- Notes:

1. NC pins are not connected on the die.

2. DNU pins have to be left floating or tied to VSS to ensure proper application.

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature ......-65°C to +150°C

Ambient Temperature with

Power Applied.....-55°C to +125°C

Supply Voltage on  $V_{CC}$  to Relative  $GND^{[3]}$  .... -0.5V to +4.6V

DC Voltage Applied to Outputs

in High-Z State<sup>[3]</sup>.....-0.5V to V<sub>CC</sub> + 0.5V

| DC Input Voltage <sup>[3]</sup> | .–0.5V to V <sub>CC</sub> + 0.5V |

|---------------------------------|----------------------------------|

| Current into Outputs (LOW)      | 20 mA                            |

#### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>cc</sub>               |

|------------|------------------------|-------------------------------|

| Commercial | 0°C to +70°C           | $3.3\text{V} \pm 0.3\text{V}$ |

| Industrial | –40°C to +85°C         |                               |

### **DC Electrical Characteristics** Over the Operating Range

|                     |                           |                                                                                                                                                                                                                     |                           | -          | -8             | _          | 10             |      |

|---------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|----------------|------------|----------------|------|

| Parameter           | Description               | Test Conditi                                                                                                                                                                                                        | ions <sup>[4]</sup>       | Min.       | Max.           | Min.       | Max.           | Unit |

| V <sub>OH</sub>     | Output HIGH Voltage       | $V_{CC} = Min., I_{OH} = -4$                                                                                                                                                                                        | 4.0 mA                    | 2.4        |                | 2.4        |                | V    |

| V <sub>OL</sub>     | Output LOW Voltage        | $V_{CC} = Min., I_{OL} = 8.$                                                                                                                                                                                        | 0 mA                      |            | 0.4            |            | 0.4            | V    |

| V <sub>IH</sub>     | Input HIGH Voltage        |                                                                                                                                                                                                                     |                           | 2.0        | $V_{CC} + 0.3$ | 2.0        | $V_{CC} + 0.3$ | V    |

| Λ <sup>IΓ</sup> [3] | Input LOW Voltage         |                                                                                                                                                                                                                     |                           | -0.3       | 0.8            | -0.3       | 0.8            | V    |

| I <sub>IX</sub>     | Input Leakage Current     | $GND \le V_I \le V_{CC}$                                                                                                                                                                                            |                           | <b>–</b> 1 | +1             | <b>–</b> 1 | +1             | μΑ   |

| I <sub>OZ</sub>     | Output Leakage Current    | $GND \le V_{OUT} \le V_{CC}$<br>Disabled                                                                                                                                                                            | , Output                  | <b>–</b> 1 | +1             | <b>–</b> 1 | +1             | μА   |

| I <sub>CC</sub>     | V <sub>CC</sub> Operating | V <sub>CC</sub> = Max.,                                                                                                                                                                                             | Commercial                |            | 300            |            | 275            | mA   |

|                     | Supply Current            | $f = f_{MAX} = 1/t_{RC}$                                                                                                                                                                                            | Industrial                |            | 300            |            | 275            | mA   |

| I <sub>SB1</sub>    | Power-down Current        | $\begin{aligned} &\text{Max. } V_{\text{CC}}, \overline{\text{CE}} \geq V_{\text{IH}} \\ &V_{\text{IN}} \geq V_{\text{IH}} \text{ or } \\ &V_{\text{IN}} \leq V_{\text{IL}}, f = f_{\text{MAX}} \end{aligned}$      |                           |            | 100            |            | 100            | mA   |

| I <sub>SB2</sub>    |                           | $\begin{split} & \underline{\text{Max}}. \ V_{CC}, \\ & \text{CE} \geq V_{CC} - 0.3 \text{V}, \\ & V_{\text{IN}} \geq V_{CC} - 0.3 \text{V}, \\ & \text{or} \ V_{\text{IN}} \leq 0.3 \text{V}, \ f = 0 \end{split}$ | Commercial<br>/Industrial |            | 50             |            | 50             | mA   |

#### Capacitance<sup>[5]</sup>

| Parameter        | Description       | Test Conditions                                    | Max. | Unit |

|------------------|-------------------|----------------------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance | $T_A = 25^{\circ}C$ , $f = 1$ MHz, $V_{CC} = 3.3V$ | 8    | pF   |

| C <sub>OUT</sub> | I/O Capacitance   |                                                    | 10   | pF   |

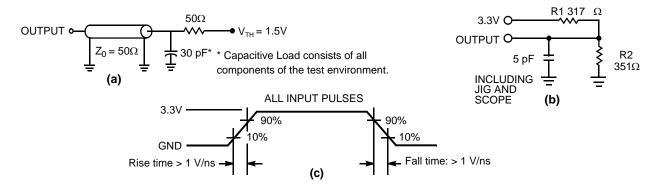

## AC Test Loads and Waveforms<sup>[6]</sup>

- 3.  $V_{IL}$  (min.) = -2.0V for pulse durations of less than 20 ns.4.  $\overline{\text{CE}}$  refers to a combination of  $\overline{\text{CE}}_0$ ,  $\overline{\text{CE}}_1$ , and  $\overline{\text{CE}}_2$ .  $\overline{\text{CE}}$  is active LOW when all three of these signals are active LOW at the same time.

5. Tested initially and after any design or process changes that may affect these parameters.

## AC Switching Characteristics Over the Operating Range<sup>[7]</sup>

|                                   |                                                                                           | _    | -8   | _    | -10  |      |  |

|-----------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|------|--|

| Parameter                         | Description                                                                               | Min. | Max. | Min. | Max. | Unit |  |

| Read Cycle                        |                                                                                           | •    | -    | 1    |      |      |  |

| t <sub>power</sub> <sup>[8]</sup> | V <sub>CC</sub> (typical) to the first access                                             | 1    |      | 1    |      | ms   |  |

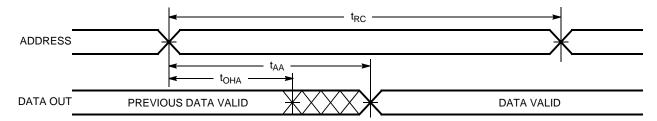

| t <sub>RC</sub>                   | Read Cycle Time                                                                           | 8    |      | 10   |      | ns   |  |

| t <sub>AA</sub>                   | Address to Data Valid                                                                     |      | 8    |      | 10   | ns   |  |

| t <sub>OHA</sub>                  | Data Hold from Address Change                                                             | 3    |      | 3    |      | ns   |  |

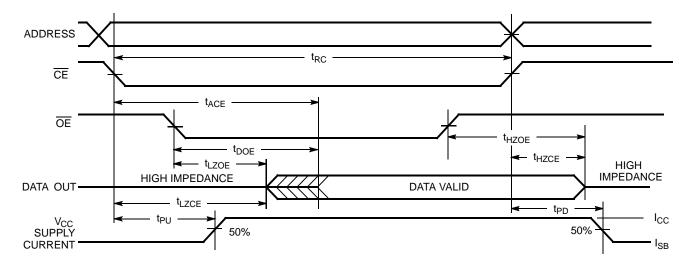

| t <sub>ACE</sub>                  | CE <sub>1</sub> , CE <sub>2</sub> , and CE <sub>3</sub> LOW to Data Valid                 |      | 8    |      | 10   | ns   |  |

| t <sub>DOE</sub>                  | OE LOW to Data Valid                                                                      |      | 5    |      | 5    | ns   |  |

| t <sub>LZOE</sub>                 | OE LOW to Low-Z <sup>[9]</sup>                                                            | 1    |      | 1    |      | ns   |  |

| t <sub>HZOE</sub>                 | OE HIGH to High-Z <sup>[9]</sup>                                                          |      | 5    |      | 5    | ns   |  |

| t <sub>LZCE</sub>                 | CE <sub>1</sub> , CE <sub>2</sub> , and CE <sub>3</sub> LOW to Low-Z <sup>[9]</sup>       | 3    |      | 3    |      | ns   |  |

| t <sub>HZCE</sub>                 | CE <sub>1</sub> , CE <sub>2</sub> , or CE <sub>3</sub> HIGH to High-Z <sup>[9]</sup>      |      | 5    |      | 5    | ns   |  |

| t <sub>PU</sub>                   | CE <sub>1</sub> , CE <sub>2</sub> , and CE <sub>3</sub> LOW to Power-up <sup>[10]</sup>   | 0    |      | 0    |      | ns   |  |

| t <sub>PD</sub>                   | CE <sub>1</sub> , CE <sub>2</sub> , or CE <sub>3</sub> HIGH to Power-down <sup>[10]</sup> |      | 8    |      | 10   | ns   |  |

| t <sub>DBE</sub>                  | Byte Enable to Data Valid                                                                 |      | 5    |      | 5    | ns   |  |

| t <sub>LZBE</sub>                 | Byte Enable to Low-Z <sup>[9]</sup>                                                       | 1    |      | 1    |      | ns   |  |

| t <sub>HZBE</sub>                 | Byte Disable to High-Z <sup>[9]</sup>                                                     |      | 5    |      | 5    | ns   |  |

| Write Cycle <sup>[11, 12]</sup>   |                                                                                           | •    | -    | 1    |      |      |  |

| t <sub>WC</sub>                   | Write Cycle Time                                                                          | 8    |      | 10   |      | ns   |  |

| t <sub>SCE</sub>                  | CE <sub>1</sub> , CE <sub>2</sub> , and CE <sub>3</sub> LOW to Write End                  | 6    |      | 7    |      | ns   |  |

| t <sub>AW</sub>                   | Address Set-up to Write End                                                               | 6    |      | 7    |      | ns   |  |

| t <sub>HA</sub>                   | Address Hold from Write End                                                               | 0    |      | 0    |      | ns   |  |

| t <sub>SA</sub>                   | Address Set-up to Write Start                                                             | 0    |      | 0    |      | ns   |  |

| t <sub>PWE</sub>                  | WE Pulse Width                                                                            | 6    |      | 7    |      | ns   |  |

| t <sub>SD</sub>                   | Data Set-up to Write End                                                                  | 5    |      | 5.5  |      | ns   |  |

| t <sub>HD</sub>                   | Data Hold from Write End                                                                  | 0    |      | 0    |      | ns   |  |

| t <sub>LZWE</sub>                 | WE HIGH to Low-Z <sup>[9]</sup>                                                           | 3    |      | 3    |      | ns   |  |

| t <sub>HZWE</sub>                 | WE LOW to High-Z <sup>[9]</sup>                                                           |      | 5    |      | 5    | ns   |  |

| t <sub>BW</sub>                   | Byte Enable to End of Write                                                               | 6    |      | 7    |      | ns   |  |

#### Notes:

Valid SRAM operation does not occur until the power supplies have reached the minimum operating V<sub>DD</sub> (3.0V). As soon as 1 ms (T<sub>power</sub>) after reaching the minimum operating V<sub>DD</sub>, normal SRAM operation can begin including reduction in V<sub>DD</sub> to the data retention (V<sub>CCDR</sub>, 2.0V) voltage.

Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified I<sub>DL</sub>/I<sub>OH</sub> and transmission line loads. Test conditions for the read cycle use output loading as shown in part a) of the AC test loads, unless specified otherwise. 8. This part has a voltage regulator which steps down the voltage from 3V to 2V internally. tpower time has to be provided initially before a read/write operation is started.

<sup>9.</sup> thzce, thzce, thzwe, thzbe, and tlzce, tl

<sup>10.</sup> These parameters are guaranteed by design and are not tested.

## **Switching Waveforms**

# Read Cycle No. $\mathbf{1}^{[13,\ 14]}$

# Read Cycle No. 2 (OE Controlled)[4, 14, 15]

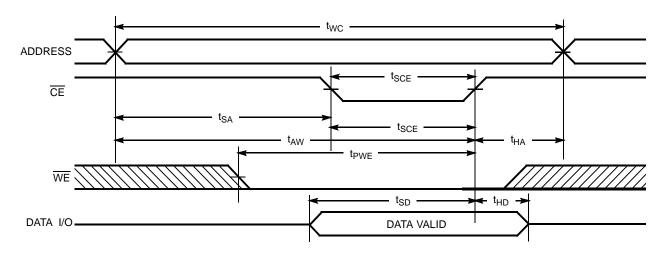

## Write Cycle No. 1 (CE Controlled)[4, 16, 17]

#### Notes:

- 11. The internal write time of the memory is defined by the overlap of  $\overline{CE}_1$ ,  $\overline{CE}_2$ , and  $\overline{CE}_3$  LOW and  $\overline{WE}$  LOW. The chip enables must be active and  $\overline{WE}$  must be LOW to initiate a write, and the transition of any of these signals can terminate the write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the write.

- 12. The minimum write cycle time for Write Cycle No. 3 ( $\overline{\text{WE}}$  controlled,  $\overline{\text{OE}}$  LOW) is the sum of  $t_{\text{HZWE}}$  and  $t_{\text{SD}}$ .

13. Device is continuously selected.  $\overline{\text{OE}}$ ,  $\overline{\text{CE}} = V_{\text{IL}}$ .

- 14. WE is HIGH for read cycle.

- 15. Address valid prior to or coincident with  $\overline{\text{CE}}$  transition LOW.

# Switching Waveforms (continued)

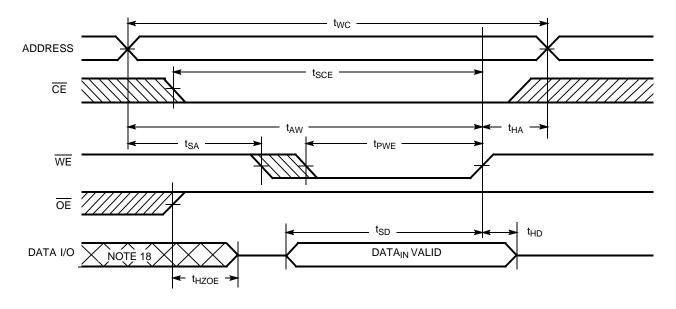

# Write Cycle No. 2 (WE Controlled, OE HIGH During Write)[16, 17]

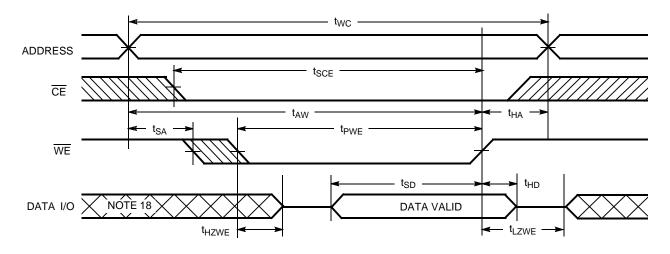

# Write Cycle No. 3 (WE Controlled, OE LOW)[4, 17]

#### Notes:

16. Data I/O is high impedance if \(\overline{OE} = \bullet\_{IH}\).

17. If \(\overline{CE}\) goes HIGH simultaneously with \(\overline{WE}\) going HIGH, the output remains in a high-impedance state.

18. During this period the I/Os are in the output state and input signals should not be applied.

# **Truth Table**

| CE <sub>0</sub> | CE <sub>1</sub> | CE <sub>2</sub> | OE | WE | I/O <sub>0</sub> -I/O <sub>23</sub>           | Mode                       | Power                      |

|-----------------|-----------------|-----------------|----|----|-----------------------------------------------|----------------------------|----------------------------|

| Н               | Н               | Н               | Х  | Х  | High-Z                                        | Power-down                 | Standby (I <sub>SB</sub> ) |

| L               | Н               | Н               | L  | Н  | I/O <sub>0</sub> -I/O <sub>7</sub> Data Out   | Read                       | Active (I <sub>CC</sub> )  |

| Н               | L               | Н               | L  | Н  | I/O <sub>8</sub> –I/O <sub>15</sub> Data Out  | Read                       | Active (I <sub>CC</sub> )  |

| Н               | Н               | L               | L  | Н  | I/O <sub>16</sub> -I/O <sub>23</sub> Data Out | Read                       | Active (I <sub>CC</sub> )  |

| L               | L               | L               | L  | Н  | Full Data Out                                 | Read                       | Active (I <sub>CC</sub> )  |

| L               | Н               | Н               | Х  | L  | I/O <sub>0</sub> –I/O <sub>7</sub> Data In    | Write                      | Active (I <sub>CC</sub> )  |

| Н               | L               | Н               | Х  | L  | I/O <sub>8</sub> –I/O <sub>15</sub> Data In   | Write                      | Active (I <sub>CC</sub> )  |

| Н               | Н               | L               | Х  | L  | I/O <sub>16</sub> -I/O <sub>23</sub> Data In  | Write                      | Active (I <sub>CC</sub> )  |

| L               | L               | L               | Х  | L  | Full Data In                                  | Write                      | Active (I <sub>CC</sub> )  |

| L               | L               | L               | Н  | Н  | High-Z                                        | Selected, Outputs Disabled | Active (I <sub>CC</sub> )  |

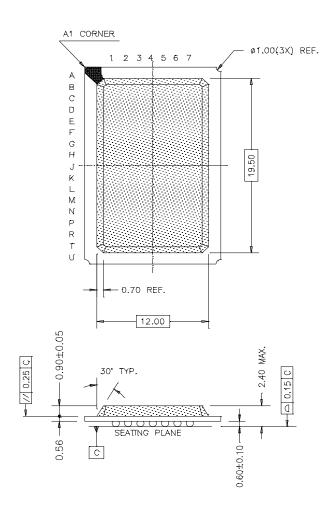

# **Ordering Information**

| Speed<br>(ns) | Ordering Code      | Package<br>Diagram | Package Type                     | Operating<br>Range |

|---------------|--------------------|--------------------|----------------------------------|--------------------|

| 8             | CY7C1012AV33-8BGC  | 51-85115           | 119-ball (14 x 22 x 2.4 mm) PBGA | Commercial         |

|               | CY7C1012AV33-8BGI  |                    |                                  | Industrial         |

| 10            | CY7C1012AV33-10BGC |                    |                                  | Commercial         |

|               | CY7C1012AV33-10BGI |                    |                                  | Industrial         |

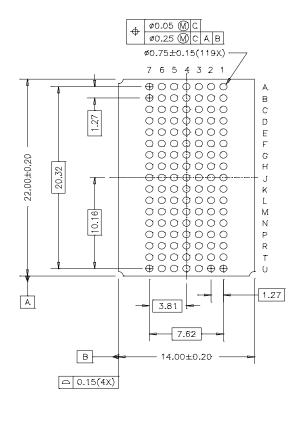

### **Package Diagram**

#### 119-ball PBGA (14 x 22 x 2.4 mm) (51-85115)

51-85115-\*B

All product and company names mentioned in this document may be the trademarks of their respective holders.

# **Document History Page**

| REV. | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                 |

|------|---------|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 113711  | 03/11/02      | NSL                | New Data Sheet                                                                                                                                                                                                                                        |

| *A   | 117057  | 07/31/02      | DFP                | Removed 15-ns bin                                                                                                                                                                                                                                     |

| *B   | 117988  | 09/03/02      | DFP                | Added 8-ns bin                                                                                                                                                                                                                                        |

| *C   | 118992  | 09/19/02      | DFP                | Change Cin - input capacitance -from 6 pF to 8 pF<br>Change Cout -output capacitance from 8 pF to 10 pF                                                                                                                                               |

| *D   | 120382  | 11/15/02      | DFP                | Final data sheet. Added note 4 to "AC Test Loads and Waveforms"                                                                                                                                                                                       |

| *E   | 492137  | See ECN       | NXR                | Removed 12 ns speed bin from product offering Included note #1 and 2 on page #2 Changed the description of I <sub>IX</sub> from Input Load Current to Input Leakage Current in DC Electrical Characteristics table Updated Ordering Information Table |