# Am29C985

# Advanced Micro Devices

# 9-Bit x 4-Port Multiple Bus Exchange with Parity

### DISTINCTIVE CHARACTERISTICS

- Four bidirectional I/O ports

- Replaces several bidirectional latched transceivers

- Permits multiple bus communication

- Allows two independent communication channels

- TTL compatibility

- 9 bit-wide ports to handle byte parity

- Parity check/generate at all ports

- Odd parity

- Additional output bus check

- Compares bus with driver inputs

- Two selection inputs per port

- independent port interconnect control

- Increased flexibility in data routing

- Matched port decoding

- Simplifies external decode logic

- Easily cascadable for wider buses

#### ■ Power-Up/Down disable

- No power-up sequencing needed

- Ideal for card-edge interface

- 48 mA output drive

- High-capacitance bus driving

- High-performance CMOS

- Low stand-by power consumption

- 6 ns (typ.) port-to-port delay

- 7 ns (typ.) select-to-port delay

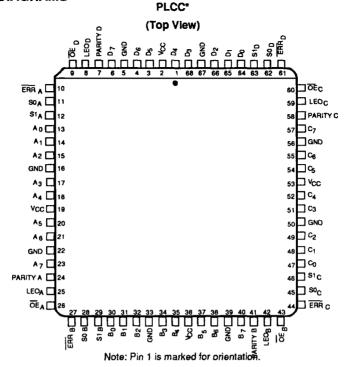

- Available in 68-pin PLCC, LCC and PGA packages

- Significant savings in board space

- Proprietary output circuit minmizes ground bounce

- 3-State during power off condition

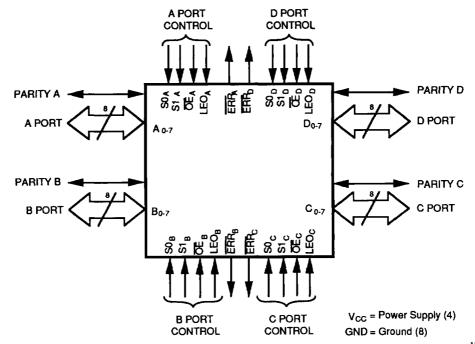

## **GENERAL DESCRIPTION**

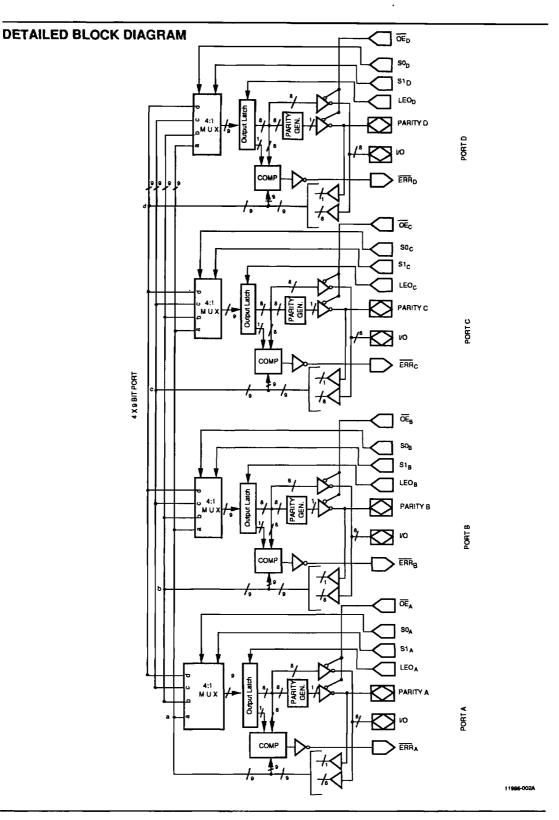

The Am29C985 is a high-speed Multiple Bus Exchange device. It is organized as four 9-bit wide TTL-compatible I/O ports with Output Enable control for each port. Any port can serve either as a source (Input) port or as a destination (Output) port. When the output drivers of a port are disabled (high-impedance state), the port serves as a source port. When the drivers are enabled, the port serves as a destination port. Source port selection is made by two independent Select inputs at each port. This organization offers flexibility in implementing the Am29C985 as a digital cross-point switch for multiple bus communication in a multiprocessing environment.

The Am29C985 incorporates parity check and generation capabilities on all four output ports. Each output port is capable of generating odd parity on byte-wide input data.

Accordingly, parity check is accomplished at each output on incoming 9 bit parity data. A unique comparison scheme also performs a bus check by comparing the data driven onto the bus with the input data received at the internal multiplexers thus detecting stuck bus bits.

Each I/O port has an output latch to capture outgoing data. All output latches are independently controlled by active HIGH Output Latch Enable inputs. This feature can be used to perform stored operation for byte-word compression and expansion to communicate between buses of different widths. Independent port control permits cascading of Am29C985s for wide buses. All I/O ports go into high impedance state upon power down. This feature makes the device ideally suited for card-edge applications.

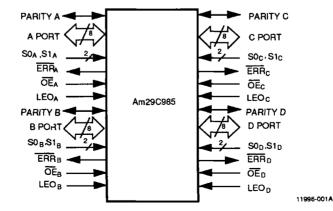

## SIMPLIFIED BLOCK DIAGRAM

Publication # 11996 Rev. A Amendment /0/ Issue Date: January 1990

6-292

\*Also available in 68-pin LCC; pinout identical to PLCC.

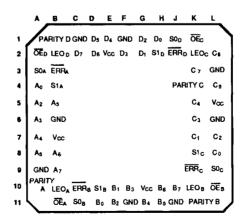

PGA (Bottom View)

Note: Notch indicates orientation.

11996A-004A

11996A-003A

## **PGA PACKAGE**

# PIN DESIGNATIONS (Sorted by Pin Name)

| PIN NO. | PIN NAME       | PIN NO. | PIN NAME       | PIN NO. | PIN NAME         | PIN NO.     | PIN NAME        |

|---------|----------------|---------|----------------|---------|------------------|-------------|-----------------|

| A-4     | A <sub>n</sub> | K-11    | PARITY B       | C-2     | D,               | B-2         | LEO,            |

| B-5     | A,             | L-8     | C <sub>0</sub> | B-1     | PARITY D         | B-11        | ŌĒ              |

| A-5     | Ą              | K-7     | C,             | A-9     | GND              | L-10        | OE,             |

| A-6     | A <sub>3</sub> | L-7     | C <sub>2</sub> | B-6     | GND              | <b>K</b> -1 | ŌĒc             |

| A-7     | A,             | K-6     | C,             | C-1     | GND              | A-2         | ŌE,             |

| A-8     | As             | K-5     | C,             | F-1     | GND              | A-3         | SO,             |

| B-8     | A <sub>s</sub> | L-4     | C <sub>s</sub> | F-11    | GND              | C-11        | S0 <sub>s</sub> |

| B-9     | A,             | K-4     | C <sub>6</sub> | J-11    | GND              | L-9         | SO <sub>c</sub> |

| A-10    | PARITY A       | K-3     | C,             | L-3     | GND              | J-1         | SO <sub>D</sub> |

| D-11    | B <sub>o</sub> | L-2     | PARITY C       | L-6     | GND              | B-4         | S1 <sub>A</sub> |

| E-10    | B <sub>1</sub> | H-1     | D <sub>o</sub> | B-3     | ERR              | D-10        | S1 <sub>B</sub> |

| E-11    | B <sub>2</sub> | G-2     | D,             | C-10    | ERR <sub>8</sub> | K-8         | S1 <sub>c</sub> |

| F-10    | B <sub>3</sub> | G-1     | D <sub>2</sub> | K-9     | ERR <sub>c</sub> | H-2         | S1 <sub>D</sub> |

| G-11    | B <sub>4</sub> | F-2     | D <sub>3</sub> | J-2     | ERR <sub>o</sub> | B-7         | V <sub>cc</sub> |

| H-11    | B <sub>s</sub> | E-1     | D <sub>4</sub> | B-10    | LEO              | E-2         | V <sub>cc</sub> |

| H-10    | B <sub>e</sub> | D-1     | $D_s$          | K-10    | LEO <sub>s</sub> | G-10        | V <sub>cc</sub> |

| J-10    | В,             | D-2     | D <sub>e</sub> | K-2     | LEO <sub>c</sub> | L-5         | V <sub>cc</sub> |

### (Sorted by Pin Number)

| PIN NO.      | PIN NAME         | PIN NO. | PIN NAME         | PIN NO. | PIN NAME         | PIN NO. | PIN NAME         |

|--------------|------------------|---------|------------------|---------|------------------|---------|------------------|

| A-2          | OE <sub>D</sub>  | B-9     | Α,               | F-10    | B <sub>3</sub>   | K-4     | C <sub>6</sub>   |

| A-3          | SO <sub>A</sub>  | B-10    | LEO              | F-11    | GND              | K-5     | C_               |

| A-4          | A <sub>o</sub>   | B-11    | ŌE,              | G-1     | D <sub>2</sub>   | K-6     | C <sub>3</sub>   |

| A-5          | Ą                | C-1     | GND              | G-2     | D,               | K-7     | C,               |

| A-6          | A <sub>3</sub>   | C-2     | D,               | G-10    | V <sub>cc</sub>  | K-8     | S1 <sub>c</sub>  |

| A-7          | A <sub>4</sub>   | C-10    | ERR <sub>B</sub> | G-11    | B <sub>4</sub>   | K-9     | ERR <sub>c</sub> |

| A-8          | Ą                | C-11    | SO <sub>8</sub>  | H-1     | D <sub>o</sub>   | K-10    | LEO <sub>B</sub> |

| A-9          | GND              | D-1     | D <sub>5</sub>   | H-2     | S1 <sub>p</sub>  | K-11    | PARITY B         |

| <b>A</b> -10 | PARITY A         | D-2     | D <sub>6</sub>   | H-10    | B <sub>6</sub>   | L-2     | PARITY C         |

| B-1          | PARITY D         | D-10    | S1 <sub>B</sub>  | H-11    | B <sub>s</sub>   | L-3     | GND              |

| B-2          | LEO <sub>D</sub> | D-11    | B <sub>o</sub>   | J-1     | SO <sub>D</sub>  | L-4     | C <sub>s</sub>   |

| B-3          | ERR              | E-1     | D <sub>4</sub>   | J-2     | ERR <sub>o</sub> | L-5     | V <sub>cc</sub>  |

| B-4          | S1 <sub>A</sub>  | E-2     | V <sub>cc</sub>  | J-10    | B,               | L-6     | GND              |

| B-5          | A,               | E-10    | В,               | J-11    | GND              | L-7     | C <sub>2</sub>   |

| B-6          | GND              | E-11    | B <sub>2</sub>   | K-1     | ŌĒc              | L-8     | C <sub>o</sub>   |

| B-7          | V <sub>cc</sub>  | F-1     | GND              | K-2     | LEO <sub>c</sub> | L-9     | S0 <sub>c</sub>  |

| B-8          | Ą                | F-2     | D <sub>3</sub>   | K-3     | C,               | L-10    | OE <sub>B</sub>  |

# **LOGIC SYMBOL**

11996-005A

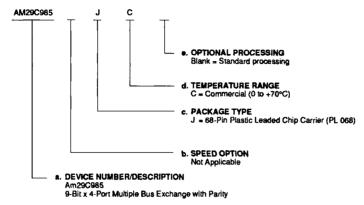

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

#### **Valid Combinations**

| Valid Combinations |     |  |  |  |  |  |

|--------------------|-----|--|--|--|--|--|

| AM29C985           | -JC |  |  |  |  |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products

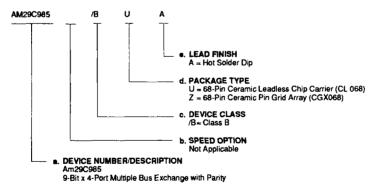

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- - b. Speed Option (if applicable)

- c. Device Class

- d. Package Type e. Lead Finish

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

# A, B, $C_{\mu}$ and $D_{\mu}$ (I = 0 through 7) Data Bus I/O Ports (Input/Output)

These four groups of eight I/O pins are defined as the A, B, C, and D ports respectively. Each port serves as a source (Input) or as a destination (Output).

# PARITY A, PARITY B, PARITY C and PARITY D Parity Flag (Input/Output, Three-state)

As an input, parity and port are combined and checked for odd parity. As an output, parity is an active output indicating odd parity for port.

### Si<sub>A</sub>, Si<sub>B</sub>, Si<sub>C</sub>, and Si<sub>D</sub> (i = 0, 1) Source Port Select (Inputs)

Each pair of inputs determines the source of data for the corresponding I/O port when used as a destination port.

#### ERRA, ERR<sub>e</sub>, ERR<sub>c</sub> and ERR<sub>p</sub> ERROR (Output, open drain)

Each output pin is used to flag Parity/Bus errors. Error is indicated by a LOW output.

# LEO<sub>A</sub>, LEO<sub>B</sub>, LEO<sub>C</sub>, and LEO<sub>D</sub> Output Latch Enable (Inputs; Active HIGH)

Each LEO input controls a 9-bit wide latch on the output side of the corresponding I/O port. The latches are transparent when LEO is HIGH and are latched when LEO is LOW.

# $\overline{\text{OE}}_{\text{A}}, \overline{\text{OE}}_{\text{B}}, \overline{\text{OE}}_{\text{C}}$ , and $\overline{\text{OE}}_{\text{D}}$ Output Enable (Inputs; Active LOW)

Each  $\overline{OE}$  input controls the bus drivers of the corresponding I/O port. When  $\overline{OE}$  is LOW, data at the output of the Output latches is passed to the bus. When  $\overline{OE}$  is HIGH, the bus outputs are in high-impedance state.

### **Am29C985 OPERATIONAL DESCRIPTION**

Parity and bus checking are provided on the Am29C985. Parity checking and generation are both performed at the output. In order to preserve parity coverage through the part, the data driven onto the bus, including the generated parity, is compared to the data passing through the multiplexer, including the old parity. This has two effects: The comparison of the parity bits acts as a parity check. Also bus errors will be detected if the bus data does not agree with the data being driven.

# Minimization of Ground Bounce through Output Edge-Rate Control

The Am29C985 incorporates AMD's proprietary edge controlled outputs in order to minimize simultaneous switching noise (ground bounce). By controlling the output transient currents, ground bounce and output ringing have been greatly reduced. A modified AMD output provides a stable, usable voltage level in less time than a controlled output.

Additionally, speed degradation due to increasing number of outputs switching is reduced. Together, these benefits of edge-rate control result in significant increase in system performance despite a minor increase in specified device propagation delay.

#### Power-Up/Down Disable

The Am29C985 contains a unique power up/down circuit to provide glitch free outputs during power-supply sequencing. This power-up circuit ensures that at low  $V_{\rm cc}$  values (typically 0–2.0 V), the outputs are disabled and in 3-state. At  $V_{\rm cc}$  values above this threshold, the outputs will remain disabled and not glitch to an active state if the appropriate output-

enable inputs are conditioned for 3-state functionality. At  $\rm V_{cc}$  values above the disable circuitry threshold, if the outputenable inputs are conditioned active (outputs enabled), the outputs will respond to a steady state input value. Additionally, the outputs will exhibit high impedance characteristics under power conditioning.

#### Input/Output Structures

Typical CMOS devices on the market today have maximum DC I/O voltage ratings that prevent some card edge applications, due to the uncertainty of the I/O voltage with respect to  $\rm V_{cc}$ . This uncertainty occurs when extracting or replacing a card into a powered-on connector or when a powered-off device is sitting on an active bus. Under these conditions, the maximum rating of -0.5 V to  $\rm V_{cc}+0.5$  V may be violated. This rating is derived from the presence of a parasitic diode from the input or output to  $\rm V_{cc}$ . To prevent forward biasing the diode with an active signal, the 0.5 V limit above  $\rm V_{cc}$  was adopted.

AMD has addressed this situation with unique input and output structures. These structures on the Am29C985 use an n-channel pull-up transistor. This results in a stacked n-channel output buffer and a proprietary ESD input cell.

These circuit modifications result in a maximum DC VO voltage rating of -0.5 V to 7.0 V. The maximum rating is no longer a function of the  $V_{\rm CC}$  voltage, thus allowing 3-state functionality under power off condition.

In addition, another benefit gained is that the n-channel pull-up reduces the output HIGH-level voltage for a lightly loaded output to 4.0 V, at  $V_{\rm cc}$  = 5.0 Volts. This reduces switching noise and cross-talk associated with typical CMOS full rail-to-rail travel.

#### **FUNCTIONAL DESCRIPTION**

The Am29C985 Multiple Bus Exchange consists of four 9-bit I/O ports. Each port has a 9-bit output latch to capture outgoing data. There are four control pins associated with each port: two Select inputs for source port selection, one Output Latch Enable input (active HIGH) to control Output latches, and an active LOW Output Enable line to control the bus driver at the I/O port.

#### Port Selection and Control

Each port is independently controlled by these four control inputs. If the output drivers of a port are disabled (high-impedance state), that port is an input and can be used as a source port. At the same time, the data at one of the four internal buses can be transferred to the Output latch under the control of the appropriate Select inputs. If the output drivers are enabled, the port serves as a destination port, transporting the data at the output of its Output latch to the external bus connected to the I/O port. Independent control of the Output latch permits stored operation at any port.

#### Parity and Bus checking

In the Am29C985, parity checking and recognition are both performed at the output. To preserve parity coverage through the part, the data driven onto the bus, including the regenerated

parity, is compared to the data passing through the switch, including the old parity. This has two effects: the comparison of parity bits acts as a parity check. Also bus errors will be detected if the bus data does not agree with data being driven to the output buffer.

#### **Error Outputs**

ERR pins are active LOW, open drain outputs. This allows easy combination of multiple bytes. When passing non-parity data through the part the output will have correct odd parity, but an error may be indicated due to the uncertainty of the 9th bit. Under this condition it is up to the user to ignore the error.

#### **Multiple Bus Communication**

Four internal buses serve as pathways for port-to-port connection. By proper choice of source select codes for the ports, the Am29C985 can be configured in different modes for multiple bus communication. In one mode of operation, two ports can be selected as source ports and the other two as destination ports; thus, two independent bidirectional communication channels are established. In another mode, one port can be selected as the source, and one or more of the other ports can serve as destination ports. Any port not intended as a destination port can be disabled (high-impedance state) by its Output Enable control.

#### TRUTH TABLES

#### A. Port Source Selection

| S1 <sub>n</sub> | SO <sub>n</sub> | Source |

|-----------------|-----------------|--------|

| L               | L               | A Bus  |

| L               | H               | B Bus  |

| н               | L               | C Bus  |

| Н               | Н               | D Bus  |

### B. Output Latch Operation

| LEO | Mode        |

|-----|-------------|

| Н   | Transparent |

| L   | Latched     |

#### C. I/O Port Controls

| LEO | ŌĒ | 1/0 | Source of Data           |

|-----|----|-----|--------------------------|

| L   | L  | Out | Contents of Output Latch |

| Н   | L  | Out | Selected Source Port     |

| Х   | н  | ln  |                          |

Key: n = A, B, C, or D L = LOW

H = HIGH

X = Don't Care

## **ABSOLUTE MAXIMUM RATINGS**

### **OPERATING RANGES**

| Supply Voltage (V <sub>cc</sub> ) DC Input Diode Current | -0.5 to 6.0 V  |

|----------------------------------------------------------|----------------|

| $(I_{iK})$ $(V_{iN} < 0 \text{ V})$                      | -20 mA         |

| $(V_{IN} > V_{CC})$ if applicable)                       | +20 mA         |

| DC Input Voltage (V <sub>IN</sub> )                      | -0.5 to 7.0 V  |

| DC Output Diode Current                                  |                |

| $(I_{OK})$ $(V_{OUT} < 0 \text{ V})$                     | -50 m <b>A</b> |

| $(V_{out} > V_{cc})$ if applicable                       | +50 mA         |

| DC Output Current per Output Pin:                        |                |

| I <sub>SINK</sub>                                        | +70 mA         |

| SOURCE                                                   | -30 mA         |

| DC Output Voltage (V <sub>out</sub> )                    | -0.5 to 7.0 V  |

| Total DC Ground Current (I <sub>GND</sub> )              | 1750 mA        |

| Total DC V <sub>cc</sub> Current (I <sub>cc</sub> )      | 575 mA         |

| Storage Temperature                                      | -65 to +150°C  |

$\begin{array}{lll} \mbox{Commercial (C) Devices} \\ \mbox{Temperature } (\mbox{T}_{\mbox{\tiny A}}) & 0 \mbox{ to } +70^{\circ}\mbox{C} \\ \mbox{Supply Voltage } (\mbox{V}_{\mbox{\tiny CC}}) & +4.5 \mbox{ to } +5.5 \mbox{ V} \\ \end{array}$

Operating ranges define those limits between which the functionality of the device is guaranteed.

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **DC CHARACTERISTICS** over operating range unless otherwise specified (for APL products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description                        | Test Cor                                                         | Min.                                                         | Max. | Unit<br>V |      |

|---------------------|-------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------|------|-----------|------|

| V <sub>OH</sub>     | Output HIGH Voltage                             | $V_{CC} = 4.5 \text{ V}$ $V_{IN} = V_{IL} \text{ or } V_{IH}$    |                                                              |      |           | 2.4  |

| V <sub>ol</sub>     | Output LOW Voltage                              | $V_{CC} = 4.5 \text{ V}$<br>$V_{IN} = V_{IL} \text{ or } V_{IH}$ | I <sub>OL</sub> = 48 mA COM'L<br>I <sub>OL</sub> = 32 mA MIL |      | 0.5       | ٧    |

| V <sub>IH</sub>     | Input HIGH Voltage                              | (Note 1)                                                         |                                                              | 2.0  |           | ٧    |

| V <sub>IL</sub>     | Input LOW Voltage                               | (Note 1)                                                         |                                                              |      | 0.8       | ν    |

| V <sub>IC</sub>     | Input Clamp Voltage                             | V <sub>cc</sub> = 4.5 V, I <sub>IN</sub> = -18                   | mA                                                           |      | -1.2      | ٧    |

| I <sub>IL</sub>     | Input LOW Current                               | V <sub>cc</sub> = 5.5 V, V <sub>IN</sub> = 0 V                   |                                                              | -10  | μА        |      |

| IL                  | (Select Inputs)                                 | V <sub>cc</sub> = 5.5 V, V <sub>IN</sub> = 0.4                   |                                                              | -5   | μА        |      |

| ļ <sub>H</sub>      | Input HIGH Current                              | $V_{cc} = 5.5 \text{ V}, V_{in} = 2.7$                           |                                                              | 5    | μΑ        |      |

| 114                 | (Select Inputs)                                 | $V_{cc} = 5.5 \text{ V}, V_{IN} = 5.5$                           |                                                              | 10   | μΑ        |      |

| l <sub>ozı</sub>    | Off-State Leakage Current                       | $V_{cc} = 5.5 \text{ V}, V_{out} = 0$                            | $V_{cc} = 5.5 \text{ V}, V_{OUT} = 0.4 \text{ V}$            |      | -15       | μА   |

| OZL                 | (I/O Ports)                                     | V <sub>cc</sub> = 5.5 V, V <sub>out</sub> = 0                    |                                                              | -20  | μΑ        |      |

| 1                   | Off-State Leakage Current                       | $V_{cc} = 5.5 \text{ V}, V_{out} = 2$                            | .7 V                                                         |      | 15        | μА   |

| l <sub>OZH</sub>    | (I/O Ports)                                     | $V_{cc} = 5.5 \text{ V}, V_{out} = 5$                            | 5 V                                                          |      | 20        | μΑ   |

| I <sub>sc</sub>     | Output Short-Circuit Current                    | V <sub>cc</sub> = 5.5 V, V <sub>out</sub> = (<br>(Note 2)        | V                                                            | -60  |           | mA   |

| Icca                | Quiescent Power Supply                          | V <sub>cc</sub> = 5.5 V,                                         | MIL                                                          |      | TBD       | m/   |

|                     | Current (Note 4)                                | V <sub>IN</sub> = 5.5 V or<br>GND Outputs Open                   | COM'L                                                        |      | TBD       | m/   |

| I <sub>ccT</sub>    | Power Supply Current TTL<br>Input HIGH (Note 4) | $V_{cc} = 5.5 \text{ V},$<br>$V_{in} = 3.4 \text{ V}$            | MIL                                                          |      | TBD       | mA   |

| 30,                 | mpar mon (note 4)                               | Other Inputs at<br>V <sub>cc</sub> or GND                        | COM'L                                                        |      | TBD       | Inpu |

## DC CHARACTERISTICS (Cont'd.)

| Parameter<br>Symbol          | Parameter<br>Description                 | Test Conditions                                                       | Min. | Max. | Unit          |

|------------------------------|------------------------------------------|-----------------------------------------------------------------------|------|------|---------------|

| l <sub>ccn</sub> †           | Dynamic Power Supply<br>Current (Note 4) | V <sub>cc</sub> = 5.5 V, Outputs Open<br>One Output Toggling (Note 3) |      | TBD  | μΑ<br>MHz/Bit |

| C <sub>PD</sub> <sup>†</sup> | Power Dissipation<br>Capacitance         | V <sub>cc</sub> = 5.5 V (Note 5)                                      |      | TBD  | pF/bit        |

SWITCHING CHARACTERISTICS over operating range unless other specified (for APL products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|     | Parameter                     | Parameter                              | Test<br>Conditions                                  | CC   | OM'L. | N N  | AIL. |      |

|-----|-------------------------------|----------------------------------------|-----------------------------------------------------|------|-------|------|------|------|

| No. | Symbol                        | Description                            |                                                     | Min. | Max.  | Min. | Max. | Unit |

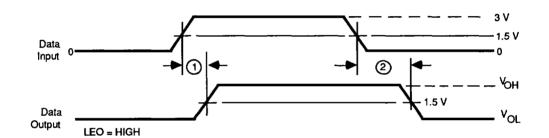

| 1   | t <sub>PLH</sub>              | Propagation Delay<br>Port to Port      |                                                     | 3    | 11    | 2    | 13   | ns   |

| 2   | t <sub>PHL</sub>              | LEO = HIGH                             |                                                     | 3    | 11    | 2    | 13   | ns   |

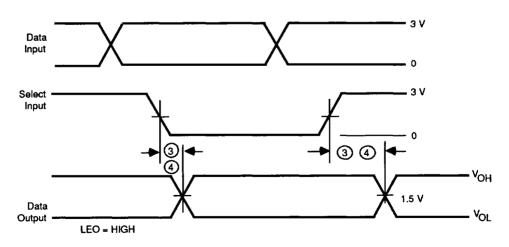

| 3   | t <sub>PLH</sub>              | Propagation Delay Select Input to Port |                                                     | 4    | 11    | 3    | 13   | ns   |

| 4   | t <sub>PHL</sub>              | LEO = HIGH                             |                                                     | 4    | 11    | 3    | 13   | ns   |

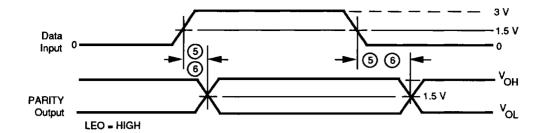

| 5   | t <sub>PLH</sub>              | Propagation Delay<br>Port to Parity    |                                                     | 4    | 14    | 3    | 16   | ns   |

| 6   | t <sub>erl</sub>              | LEO = HIGH                             |                                                     | 4    | 14    | 3    | 16   | ns   |

| 7   | t <sub>PLH</sub>              | Propagation Delay                      |                                                     | 3    | 9     | 2    | 11   | ns   |

| 8   | t <sub>PHL</sub>              | LEO to Port                            |                                                     | 3    | 9     | 2    | 11   | ns   |

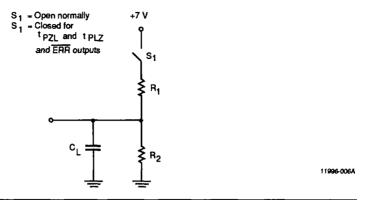

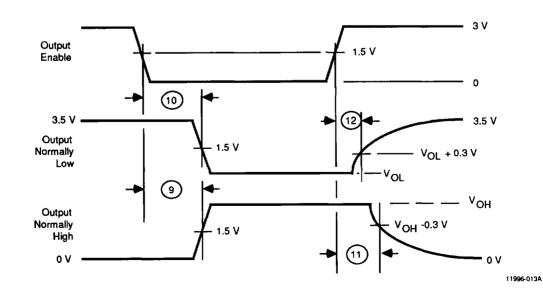

| 9   | t <sub>PZH</sub>              | Output Enable Time                     | C <sub>L</sub> = 50 pF<br>R <sub>1</sub> = 500 Ohms | 3    | 8     | 2    | 10   | ns   |

| 10  | tpzi                          | OE to Port                             | R <sub>2</sub> = 500 Ohms                           | 3    | 8     | _2   | 10   | ns   |

| 11  | t <sub>PHZ</sub>              | Output Disable Time                    | _                                                   | 3    | 6     | 2    | 8    | ns   |

| 12  | t <sub>PLZ</sub>              | OE to Port                             |                                                     | 3    | 6     | 2    | 8    | ns   |

| 13  | t <sub>pLH</sub> †            | Propagation Delay                      |                                                     | 3    | 14    | 2    | 16   | ns   |

| 14  | t <sub>PHL</sub> †            | Port to ERR                            |                                                     | 3    | 9     | 2    | 11   | ns   |

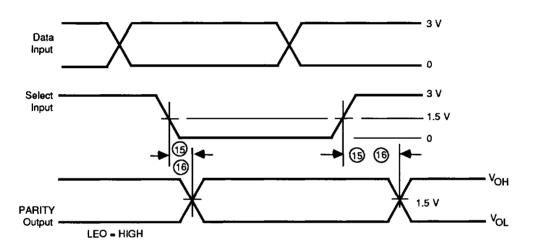

| 15  | t <sub>PLH</sub>              | Propagation Delay                      |                                                     | 5    | 15    | 4    | 17   | ns   |

| 16  | t <sub>PHL</sub>              | Select to Parity                       |                                                     | 5    | 15    | 4    | 17   | ns   |

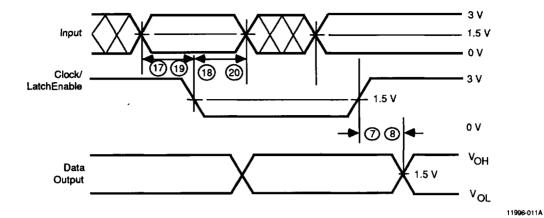

| 17  | t,                            | Port to LEO Setup                      |                                                     | 4.5  |       | 5.5  |      | ns   |

| 18  | t <sub>h</sub>                | Port to LEO Hold                       |                                                     | 0    |       | 1    |      | ns   |

| 19  | 1.                            | Select to LEO Setup                    |                                                     | 6.0  |       | 7.0  |      | ns   |

| 20  | t,                            | Select to LEO Hold                     |                                                     | 0    |       | 1    |      | ns   |

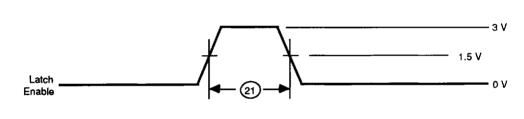

| 21  | t <sub>PWH</sub> <sup>†</sup> | LEO Pulse<br>Width HIGH                |                                                     | 3    |       | 4    |      | ns   |

Notes: 1. Input thresholds are tested in combination with other DC parameters or by correlation.

Where: D<sub>H</sub> = Duty cycle for each TTL input HIGH

D<sub>H</sub> = Duty cycle to each The input file.

T = Number of inputs at D<sub>H</sub>

f<sub>cp</sub> = Clock frequency for clocked devices (Zero for non-clocked devices)

f<sub>c</sub> = Input frequency of the i<sup>th</sup> input

N<sub>i</sub> = Number of inputs at f<sub>i</sub>

5.  $C_{\rm pp}$  in pF is calculated from  $I_{\rm cco}$  measurements using the formula

$C_{PD} = \frac{1}{c_{CD}} V_{CC}$ where  $I_{CCD}$  is expressed in  $\mu$ A/MHz/bit.

†Not included in Group A tests.

<sup>2.</sup> Not more than one output shorted at a time. Duration of short-circuit test not to exceed 100 ms.

<sup>3.</sup> Measured at a frequency of < 10 MHz with 50% duty cycle. Unused inputs are at V<sub>cc</sub> or GND.

<sup>4.</sup> Calculation of total device  $I_{cc}$ :  $I_{cc} = I_{cco} + I_{ccr}D_HN_T + I_{cco}(f_{cr}/2 + f_iN_i)$

## **SWITCHING TEST CIRCUIT**

### **SWITCHING TEST WAVEFORMS**

### Propagation Delay—Port-to-Port

11996-007A

Propagation Delay—Select-to-Port

11996-008A

Am29C985

# SWITCHING TEST WAVEFORMS (Cont'd.)

# Propagation Delay — Port to Parity

11996-009A

Propagation Delay — Select to Parity

11996-010A

6-302 Am29C985

# SWITCHING TEST WAVEFORMS (Cont'd.)

# **Output Latch Propagation Delay, Setup and Hold Times**

Minimum Latch Enable

11996-012A

### **Enable and Disable Times**

# **SWITCHING TEST WAVEFORMS** (Cont'd.)

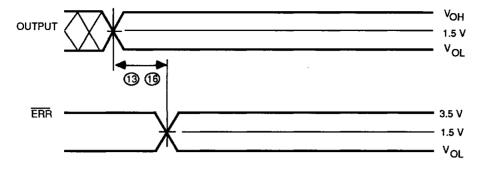

Propagation Delay — Output Port to ERR

11996-014A